Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 454 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Data Converters            |                                                                          |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 44-LCC (J-Lead)                                                          |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44-16e-l |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

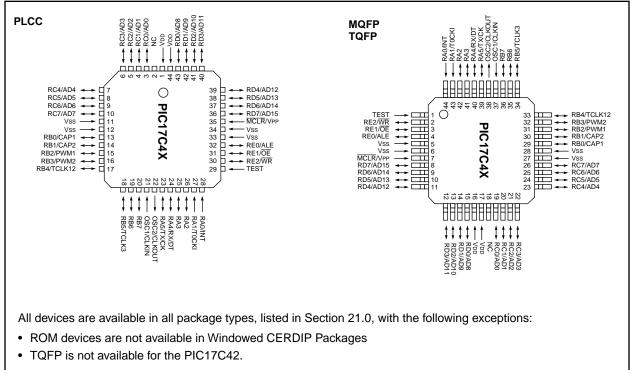

## Pin Diagrams Cont.'d

NOTES:

## 7.1 <u>Table Writes to Internal Memory</u>

A table write operation to internal memory causes a long write operation. The long write is necessary for programming the internal EPROM. Instruction execution is halted while in a long write cycle. The long write will be terminated by any enabled interrupt. To ensure that the EPROM location has been well programmed, a minimum programming time is required (see specification #D114). Having only one interrupt enabled to terminate the long write ensures that no unintentional interrupts will prematurely terminate the long write.

The sequence of events for programming an internal program memory location should be:

- 1. Disable all interrupt sources, except the source to terminate EPROM program write.

- 2. Raise MCLR/VPP pin to the programming voltage.

- 3. Clear the WDT.

- 4. Do the table write. The interrupt will terminate the long write.

- 5. Verify the memory location (table read).

- **Note:** Programming requirements must be met. See timing specification in electrical specifications for the desired device. Violating these specifications (including temperature) may result in EPROM locations that are not fully programmed and may lose their state over time.

## 7.1.1 TERMINATING LONG WRITES

An interrupt source or reset are the only events that terminate a long write operation. Terminating the long write from an interrupt source requires that the interrupt enable and flag bits are set. The GLINTD bit only enables the vectoring to the interrupt address.

If the TOCKI, RA0/INT, or TMR0 interrupt source is used to terminate the long write; the interrupt flag, of the highest priority enabled interrupt, will terminate the long write and automatically be cleared.

- **Note 1:** If an interrupt is pending, the TABLWT is aborted (an NOP is executed). The highest priority pending interrupt, from the TOCKI, RA0/INT, or TMR0 sources that is enabled, has its flag cleared.

- **Note 2:** If the interrupt is not being used for the program write timing, the interrupt should be disabled. This will ensure that the interrupt is not lost, nor will it terminate the long write prematurely.

If a peripheral interrupt source is used to terminate the long write, the interrupt enable and flag bits must be set. The interrupt flag will not be automatically cleared upon the vectoring to the interrupt vector address.

If the GLINTD bit is cleared prior to the long write, when the long write is terminated, the program will branch to the interrupt vector.

If the GLINTD bit is set prior to the long write, when the long write is terminated, the program will not vector to the interrupt address.

| Interrupt<br>Source     | GLINTD | Enable<br>Bit | Flag<br>Bit | Action                                                                                                              |

|-------------------------|--------|---------------|-------------|---------------------------------------------------------------------------------------------------------------------|

| RA0/INT, TMR0,<br>T0CKI | 0      | 1             | 1           | Terminate long table write (to internal program<br>memory), branch to interrupt vector (branch clears<br>flag bit). |

|                         | 0      | 1             | 0           | None                                                                                                                |

|                         | 1      | 0             | x           | None                                                                                                                |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is automatically cleared).                           |

| Peripheral              | 0      | 1             | 1           | Terminate table write, branch to interrupt vector.                                                                  |

| •                       | 0      | 1             | 0           | None                                                                                                                |

|                         | 1      | 0             | x           | None                                                                                                                |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is set).                                             |

## TABLE 7-1: INTERRUPT - TABLE WRITE INTERACTION

Example 8-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in 4 registers RES3:RES0.

#### **EQUATION 8-1:** 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

=

- ARG1H:ARG1L \* ARG2H:ARG2L RES3:RES0 =

- (ARG1H \* ARG2H \* 2<sup>16</sup>) +

(ARG1H \* ARG2L \* 2<sup>8</sup>) +

(ARG1L \* ARG2H \* 2<sup>8</sup>) (ARG1L \* ARG2L)

+

## EXAMPLE 8-3: 16 x 16 MULTIPLY ROUTINE

|   |                                  |                            | ; ARG1L * ARG2L -<br>; PRODH:PRODL  | > |

|---|----------------------------------|----------------------------|-------------------------------------|---|

| ; |                                  | PRODH, RES1<br>PRODL, RES0 | ;                                   |   |

| , |                                  |                            | ; ARG1H * ARG2H -<br>; PRODH:PRODL  | > |

| ; |                                  | PRODH, RES3<br>PRODL, RES2 |                                     |   |

| - | MOVFP<br>MULWF                   |                            | ; ARG1L * ARG2H -<br>; PRODH:PRODL  | > |

|   | ADDWF<br>MOVFP<br>ADDWFC         |                            | ; Add cross<br>; products<br>;      |   |

| ; | ADDWFC                           | RES3, F<br>ARG1H, WREG     | ;                                   |   |

|   | MULWF                            | ARG2L                      | ; ARG1H * ARG2L -<br>; PRODH:PRODL  | > |

|   | ADDWF<br>MOVFP<br>ADDWFC<br>CLRF |                            | ; Add cross<br>; products<br>;<br>; |   |

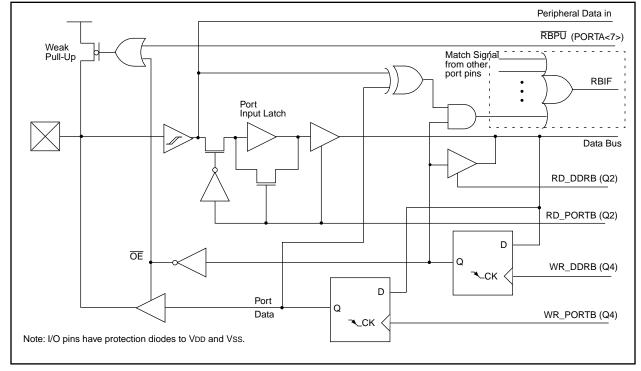

## 9.2 PORTB and DDRB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is DDRB. A '1' in DDRB configures the corresponding port pin as an input. A '0' in the DDRB register configures the corresponding port pin as an output. Reading PORTB reads the status of the pins, whereas writing to it will write to the port latch.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{\text{RBPU}}$  (PORTA<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are enabled on any reset.

PORTB also has an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB0 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB0) are compared with the value in the PORTB data latch. The "mismatch" outputs of RB7:RB0 are OR'ed together to generate the PORTB Interrupt Flag RBIF (PIR<7>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt by:

- a) Read-Write PORTB (such as; MOVPF PORTB, PORTB). This will end mismatch condition.

- b) Then, clear the RBIF bit.

A mismatch condition will continue to set the RBIF bit. Reading then writing PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on this port, allows easy interface to a key pad and make it possible for wake-up on key-depression. For an example, refer to AN552 in the *Embedded Control Handbook*.

The interrupt on change feature is recommended for wake-up on operations where PORTB is only used for the interrupt on change feature and key depression operation.

FIGURE 9-4: BLOCK DIAGRAM OF RB<7:4> AND RB<1:0> PORT PINS

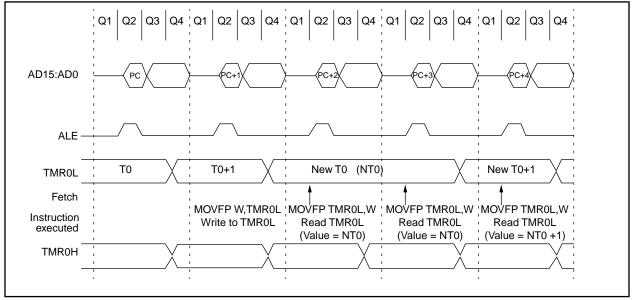

## 11.3 Read/Write Consideration for TMR0

Although TMR0 is a 16-bit timer/counter, only 8-bits at a time can be read or written during a single instruction cycle. Care must be taken during any read or write.

#### 11.3.1 READING 16-BIT VALUE

The problem in reading the entire 16-bit value is that after reading the low (or high) byte, its value may change from FFh to 00h.

Example 11-1 shows a 16-bit read. To ensure a proper read, interrupts must be disabled during this routine.

## EXAMPLE 11-1: 16-BIT READ

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

|--------|--------|-------|-----------------|

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| MOVFP  | TMPLO, | WREG  | ;tmplo -> wreg  |

| CPFSLT | TMR0L  |       | ;tmr0l < wreg?  |

| RETURN |        |       | ;no then return |

| MOVPF  | TMROL, | TMPLO | ;read low tmr0  |

| MOVPF  | TMROH, | TMPHI | ;read high tmr0 |

| RETURN |        |       | ;return         |

### 11.3.2 WRITING A 16-BIT VALUE TO TMR0

Since writing to either TMR0L or TMR0H will effectively inhibit increment of that half of the TMR0 in the next cycle (following write), but not inhibit increment of the other half, the user must write to TMR0L first and TMR0H next in two consecutive instructions, as shown in Example 11-2. The interrupt must be disabled. Any write to either TMR0L or TMR0H clears the prescaler.

### EXAMPLE 11-2: 16-BIT WRITE

BSF CPUSTA, GLINTD ; Disable interrupt MOVFP RAM\_L, TMROL ; MOVFP RAM\_H, TMROH ; BCF CPUSTA, GLINTD ; Done, enable interrupt

## 11.4 Prescaler Assignments

Timer0 has an 8-bit prescaler. The prescaler assignment is fully under software control; i.e., it can be changed "on the fly" during program execution. When changing the prescaler assignment, clearing the prescaler is recommended before changing assignment. The value of the prescaler is "unknown," and assigning a value that is less then the present value makes it difficult to take this unknown time into account.

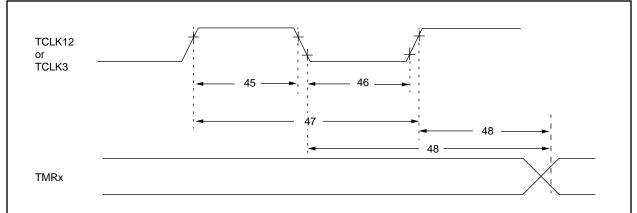

## FIGURE 11-4: TMR0 TIMING: WRITE HIGH OR LOW BYTE

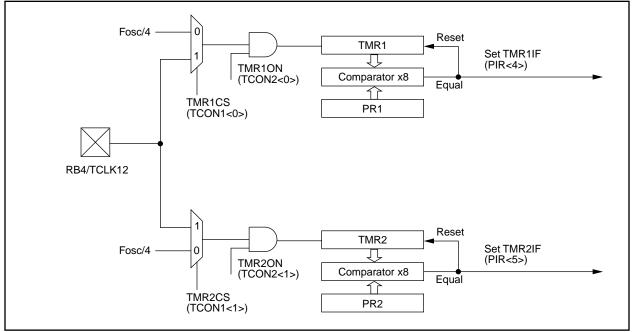

## 12.1 <u>Timer1 and Timer2</u>

### 12.1.1 TIMER1, TIMER2 IN 8-BIT MODE

Both Timer1 and Timer2 will operate in 8-bit mode when the T16 bit is clear. These two timers can be independently configured to increment from the internal instruction cycle clock or from an external clock source on the RB4/TCLK12 pin. The timer clock source is configured by the TMRxCS bit (x = 1 for Timer1 or = 2 for Timer2). When TMRxCS is clear, the clock source is internal and increments once every instruction cycle (Fosc/4). When TMRxCS is set, the clock source is the RB4/TCLK12 pin, and the timer will increment on every falling edge of the RB4/TCLK12 pin.

The timer increments from 00h until it equals the Period register (PRx). It then resets to 00h at the next increment cycle. The timer interrupt flag is set when the timer is reset. TMR1 and TMR2 have individual interrupt flag bits. The TMR1 interrupt flag bit is latched into TMR1IF, and the TMR2 interrupt flag bit is latched into TMR2IF.

Each timer also has a corresponding interrupt enable bit (TMRxIE). The timer interrupt can be enabled by setting this bit and disabled by clearing this bit. For peripheral interrupts to be enabled, the Peripheral Interrupt Enable bit must be enabled (PEIE is set) and global interrupts must be enabled (GLINTD is cleared).

The timers can be turned on and off under software control. When the Timerx On control bit (TMRxON) is set, the timer increments from the clock source. When TMRxON is cleared, the timer is turned off and cannot cause the timer interrupt flag to be set.

#### 12.1.1.1 EXTERNAL CLOCK INPUT FOR TIMER1 OR TIMER2

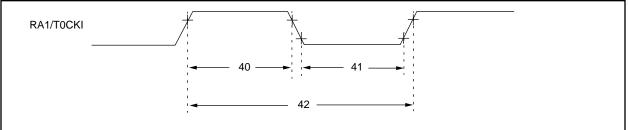

When TMRxCS is set, the clock source is the RB4/TCLK12 pin, and the timer will increment on every falling edge on the RB4/TCLK12 pin. The TCLK12 input is synchronized with internal phase clocks. This causes a delay from the time a falling edge appears on TCLK12 to the time TMR1 or TMR2 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

## FIGURE 12-3: TIMER1 AND TIMER2 IN TWO 8-BIT TIMER/COUNTER MODE

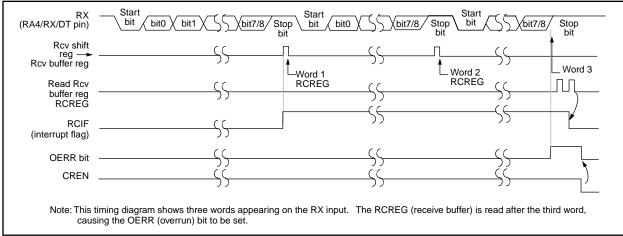

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

## FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6</b> : | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|---------------------|---------------------------------------------------------|

|                     |                                                         |

| Address                                        | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2     | Bit 1     | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|--------|--------|--------|-------|-----------|-----------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF     | TXIF      | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   | _     | FERR      | OERR      | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0                                    | RCREG | RX7   | RX6    | RX5    | RX4    | RX3   | RX2       | RX1       | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE     | TXIE      | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9    | TXEN   | SYNC   | _     | —         | TRMT      | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |        |        |        |       | xxxx xxxx | uuuu uuuu |       |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

# PIC17C4X

| BSF                                                                                                     | Bit Set f                                                          |                                                                     |      |   |                     |  |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------------------------------|------|---|---------------------|--|

| Syntax:                                                                                                 | [ <i>label</i> ] E                                                 | BSF f,b                                                             | )    |   |                     |  |

| Operands:                                                                                               | $\begin{array}{l} 0 \leq f \leq 25 \\ 0 \leq b \leq 7 \end{array}$ | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$ |      |   |                     |  |

| Operation:                                                                                              | peration: $1 \rightarrow (f < b >)$                                |                                                                     |      |   |                     |  |

| Status Affected: None                                                                                   |                                                                    |                                                                     |      |   |                     |  |

| Encoding:                                                                                               | 1000                                                               | 0bbb                                                                | fff  | f | ffff                |  |

| Description:                                                                                            | Bit 'b' in register 'f' is set.                                    |                                                                     |      |   |                     |  |

| Words:                                                                                                  | 1                                                                  |                                                                     |      |   |                     |  |

| Cycles:                                                                                                 | 1                                                                  |                                                                     |      |   |                     |  |

| Q Cycle Activity:                                                                                       |                                                                    |                                                                     |      |   |                     |  |

| Q1                                                                                                      | Q2                                                                 | Q3                                                                  | 3    |   | Q4                  |  |

| Decode                                                                                                  | Read<br>register 'f'                                               | Execu                                                               |      |   | Write<br>gister 'f' |  |

| Example:                                                                                                | BSF                                                                | FLAG_RE                                                             | G, 7 |   |                     |  |

| Example: BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG= 0x0A<br>After Instruction<br>FLAG_REG= 0x8A |                                                                    |                                                                     |      |   |                     |  |

| BTF                                       | SC                                                    | Bit Test, s                                                                                                                                                                                                                                                             | skip if Cle | ear    |      |

|-------------------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|------|

| Synt                                      | tax:                                                  | [ <i>label</i> ] B                                                                                                                                                                                                                                                      | TFSC f,I    | b      |      |

| Ope                                       | rands:                                                | $0 \le f \le 253$ $0 \le b \le 7$                                                                                                                                                                                                                                       | 5           |        |      |

| Ope                                       | ration:                                               | skip if (f <t< td=""><td>o&gt;) = 0</td><td></td><td></td></t<>                                                                                                                                                                                                         | o>) = 0     |        |      |

| Stat                                      | us Affected:                                          | None                                                                                                                                                                                                                                                                    |             |        |      |

| Enc                                       | oding:                                                | 1001                                                                                                                                                                                                                                                                    | 1bbb        | ffff   | ffff |

| Des                                       | cription:                                             | If bit 'b' in register 'f' is 0 then the next<br>instruction is skipped.<br>If bit 'b' is 0 then the next instruction<br>fetched during the current instruction exe<br>cution is discarded, and a NOP is exe-<br>cuted instead, making this a two-cycle<br>instruction. |             |        |      |

| Wor                                       | ds:                                                   | 1                                                                                                                                                                                                                                                                       |             |        |      |

| Cycl                                      | les:                                                  | 1(2)                                                                                                                                                                                                                                                                    |             |        |      |

| QC                                        | ycle Activity:                                        |                                                                                                                                                                                                                                                                         |             |        |      |

|                                           | Q1                                                    | Q2                                                                                                                                                                                                                                                                      | Q3          |        | Q4   |

|                                           | Decode                                                | Read<br>register 'f'                                                                                                                                                                                                                                                    | Execu       | ite    | NOP  |

| lf sk                                     | ip:                                                   |                                                                                                                                                                                                                                                                         |             |        |      |

|                                           | Q1                                                    | Q2                                                                                                                                                                                                                                                                      | Q3          |        | Q4   |

|                                           | Forced NOP                                            | NOP                                                                                                                                                                                                                                                                     | Execu       | ite    | NOP  |

| <u>Exa</u>                                | mple:                                                 | FALSE                                                                                                                                                                                                                                                                   | BTFSC<br>:  | FLAG,1 |      |

| Before Instruction<br>PC = address (HERE) |                                                       |                                                                                                                                                                                                                                                                         |             |        |      |

|                                           | After Instructi<br>If FLAG<7<br>PC<br>If FLAG<7<br>PC | l> = 0;<br>= ac<br>l> = 1;                                                                                                                                                                                                                                              | ldress (TR  |        |      |

| MULLW                                                     | Multiply I                                                                                                                         | _iteral with V                                                                                                                                                                            | VREG                                                                                      | MULWF                                         | Multiply V                                                                                                                  | VREG with                                                                                                                                                                                                         | f                                                                                                              |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Syntax:                                                   | [ label ]                                                                                                                          | MULLW k                                                                                                                                                                                   |                                                                                           | Syntax:                                       | [ label ]                                                                                                                   | MULWF f                                                                                                                                                                                                           |                                                                                                                |

| Operands:                                                 | $0 \le k \le 25$                                                                                                                   | 5                                                                                                                                                                                         |                                                                                           | Operands:                                     | $0 \le f \le 25$                                                                                                            | 5                                                                                                                                                                                                                 |                                                                                                                |

| Operation:                                                | (k x WRE                                                                                                                           | G) $\rightarrow$ PRODI                                                                                                                                                                    | H:PRODL                                                                                   | Operation:                                    | (WREG x                                                                                                                     | f) $\rightarrow$ PRODI                                                                                                                                                                                            | H:PRODL                                                                                                        |

| Status Affected:                                          | None                                                                                                                               |                                                                                                                                                                                           |                                                                                           | Status Affected                               | : None                                                                                                                      |                                                                                                                                                                                                                   |                                                                                                                |

| Encoding:                                                 | 1011                                                                                                                               | 1100 kk                                                                                                                                                                                   | kk kkkk                                                                                   | Encoding:                                     | 0011                                                                                                                        | 0100 ff                                                                                                                                                                                                           | Ef ffff                                                                                                        |

| Description:                                              | out betwee<br>and the 8-b<br>result is pla<br>register pai<br>high byte.<br>WREG is u<br>None of the<br>Note that n<br>is possible | ed multiplicatio<br>n the contents<br>bit literal 'k'. The<br>aced in PRODH<br>ir. PRODH con<br>unchanged.<br>e status flags a<br>either overflow<br>in this operatio<br>ssible but not o | of WREG<br>e 16-bit<br>H:PRODL<br>tains the<br>are affected.<br>y nor carry<br>on. A zero | Description:                                  | out betwee<br>and the reg<br>16-bit resul<br>PRODH:PF<br>PRODH co<br>Both WREC<br>None of the<br>Note that n<br>is possible | d multiplication<br>n the contents<br>jister file locat<br>t is stored in t<br>RODL register<br>ntains the hig<br>G and 'f' are un<br>e status flags a<br>either overflow<br>in this operations<br>ssible but not | s of WREG<br>ion 'f'. The<br>he<br>pair.<br>h byte.<br>nchanged.<br>are affected.<br>v nor carry<br>on. A zero |

| Words:                                                    | 1                                                                                                                                  |                                                                                                                                                                                           |                                                                                           | Words:                                        | 1                                                                                                                           |                                                                                                                                                                                                                   |                                                                                                                |

| Cycles:                                                   | 1                                                                                                                                  |                                                                                                                                                                                           |                                                                                           | Cycles:                                       | 1                                                                                                                           |                                                                                                                                                                                                                   |                                                                                                                |

| Q Cycle Activity:                                         |                                                                                                                                    |                                                                                                                                                                                           |                                                                                           | Q Cycle Activity                              | :                                                                                                                           |                                                                                                                                                                                                                   |                                                                                                                |

| Q1                                                        | Q2                                                                                                                                 | Q3                                                                                                                                                                                        | Q4                                                                                        | Q1                                            | Q2                                                                                                                          | Q3                                                                                                                                                                                                                | Q4                                                                                                             |

| Decode                                                    | Read<br>literal 'k'                                                                                                                | Execute                                                                                                                                                                                   | Write<br>registers<br>PRODH:<br>PRODL                                                     | Decode                                        | Read<br>register 'f'                                                                                                        | Execute                                                                                                                                                                                                           | Write<br>registers<br>PRODH:<br>PRODL                                                                          |

| Example:                                                  | MULLW                                                                                                                              | 0xC4                                                                                                                                                                                      |                                                                                           | Example:                                      | MULWF                                                                                                                       | REG                                                                                                                                                                                                               | 1                                                                                                              |

| Before Instru<br>WREG<br>PRODH<br>PRODL<br>After Instruct | = 0><br>= ?<br>= ?                                                                                                                 | κE2                                                                                                                                                                                       |                                                                                           | Before Inst<br>WREG<br>REG<br>PRODI<br>PRODI  | = 0x<br>= 0x<br>H = ?                                                                                                       | (C4<br>(B5                                                                                                                                                                                                        |                                                                                                                |

| WREG<br>PRODH<br>PRODL                                    | = 0><br>= 0><br>= 0>                                                                                                               | (C4<br>(AD<br>(08<br>is not avail                                                                                                                                                         | able in the                                                                               | After Instru<br>WREG<br>REG<br>PRODI<br>PRODI | $\begin{array}{rcl} = & 0 \\ = & 0 \\ + & = & 0 \end{array}$                                                                | xC4<br>xB5<br>x8A<br>x94                                                                                                                                                                                          |                                                                                                                |

| PIC17                                                     | C42 device                                                                                                                         |                                                                                                                                                                                           |                                                                                           |                                               | instruction<br>17C42 device                                                                                                 |                                                                                                                                                                                                                   | lable in th                                                                                                    |

# PIC17C4X

| RRNCF                                                                                                        | Rotate F                                                                                                                                                                                    | Right f (no                                                                                                                                                              | carry)               |  |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Syntax:                                                                                                      | [ label ]                                                                                                                                                                                   | RRNCF 1                                                                                                                                                                  | i,d                  |  |  |

| Operands:                                                                                                    | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                                                                                                                                     |                                                                                                                                                                          |                      |  |  |

| Operation:                                                                                                   | $f < n > \rightarrow 0$<br>$f < 0 > \rightarrow 0$                                                                                                                                          | ,                                                                                                                                                                        |                      |  |  |

| Status Affected:                                                                                             | None                                                                                                                                                                                        |                                                                                                                                                                          |                      |  |  |

| Encoding:                                                                                                    | 0010                                                                                                                                                                                        | 000d                                                                                                                                                                     | ffff ffff            |  |  |

| Description:                                                                                                 | one bit to<br>placed in                                                                                                                                                                     | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is 0 the result is<br>placed in WREG. If 'd' is 1 the result is<br>placed back in register 'f'. |                      |  |  |

|                                                                                                              | Г                                                                                                                                                                                           | ► regis                                                                                                                                                                  | ster f               |  |  |

| Words:                                                                                                       | 1                                                                                                                                                                                           |                                                                                                                                                                          |                      |  |  |

| Cycles:                                                                                                      | 1                                                                                                                                                                                           |                                                                                                                                                                          |                      |  |  |

| Q Cycle Activity:                                                                                            |                                                                                                                                                                                             |                                                                                                                                                                          |                      |  |  |

| Q1                                                                                                           | Q2                                                                                                                                                                                          | Q3                                                                                                                                                                       | Q4                   |  |  |

| Decode                                                                                                       | Read<br>register 'f'                                                                                                                                                                        | Execute                                                                                                                                                                  | Write to destination |  |  |

| Example 1:                                                                                                   | RRNCF                                                                                                                                                                                       | REG, 1                                                                                                                                                                   |                      |  |  |

|                                                                                                              | Induced                                                                                                                                                                                     | KEG, I                                                                                                                                                                   |                      |  |  |

| Before Instru                                                                                                |                                                                                                                                                                                             | KEG, I                                                                                                                                                                   |                      |  |  |

| -                                                                                                            | iction<br>= ?                                                                                                                                                                               | 0111                                                                                                                                                                     |                      |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct                                                               | iction<br>= ?<br>= 1101                                                                                                                                                                     |                                                                                                                                                                          |                      |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG                                                       | tion<br>= ?<br>= 1101<br>tion<br>= 0                                                                                                                                                        | 0111                                                                                                                                                                     |                      |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct                                                               | iction<br>= ?<br>= 1101<br>tion                                                                                                                                                             |                                                                                                                                                                          |                      |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG                                                       | tion<br>= ?<br>= 1101<br>tion<br>= 0                                                                                                                                                        | 0111                                                                                                                                                                     |                      |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG<br>REG<br><u>Example 2</u> :<br>Before Instru<br>WREG | inction       =     ?       =     1101       tion        =     0       =     1110       RRNCF       inction       =     ?                                                                   | 0111<br>1011<br>REG, 0                                                                                                                                                   |                      |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG<br>REG<br>Example 2:<br>Before Instru                 | Initial       ?         =       1101         tion       =         =       0         =       1110         RRNCF       Initial         Initial       ?         =       ?         =       1101 | 0111<br>1011                                                                                                                                                             |                      |  |  |

| SETF                       | Set f                                                    |            |                |                                                        |

|----------------------------|----------------------------------------------------------|------------|----------------|--------------------------------------------------------|

| Syntax:                    | [ label ]                                                | SETF f,    | S              |                                                        |

| Operands:                  | 0 ≤ f ≤ 25<br>s ∈ [0,1]                                  | 5          |                |                                                        |

| Operation:                 | $\begin{array}{l} FFh \to f;\\ FFh \to d \end{array}$    |            |                |                                                        |

| Status Affected            | : None                                                   |            |                |                                                        |

| Encoding:                  | 0010                                                     | 101s       | ffff           | ffff                                                   |

| Description:               | If 's' is 0, bo<br>'f' and WRI<br>only the da<br>to FFh. | EG are set | to FFh. I      | f 's' is 1                                             |

| Words:                     | 1                                                        |            |                |                                                        |

| Cycles:                    | 1                                                        |            |                |                                                        |

| Q Cycle Activity           | /:                                                       |            |                |                                                        |

| Q1                         | Q2                                                       | Q3         |                | Q4                                                     |

| Decode                     | Read<br>register 'f'                                     | Execut     | re<br>ar<br>sp | Write<br>gister 'f'<br>id other<br>becified<br>egister |

| Example1:                  | SETF                                                     | REG, O     |                |                                                        |

| Before Inst<br>REG<br>WREG | = 0xDA                                                   |            |                |                                                        |

| After Instru               | iction                                                   |            |                |                                                        |

| REG<br>WREG                | = 0xFF<br>= 0xFF                                         | PFC 1      |                |                                                        |

| REG                        | = 0xFF<br>= 0xFF<br>SETF<br>ruction<br>= 0xDA            | REG, 1     |                |                                                        |

| SLEEP                                                            | Enter SI                                                                                                                            | EEP mod                                                                          | de                               |                                              |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------------------------|----------------------------------------------|

| Syntax:                                                          | [ label ]                                                                                                                           | SLEEP                                                                            |                                  |                                              |

| Operands:                                                        | None                                                                                                                                |                                                                                  |                                  |                                              |

| Operation:                                                       | $\begin{array}{l} 00h \rightarrow W \\ 0 \rightarrow WD \\ 1 \rightarrow \overline{TO}; \\ 0 \rightarrow \overline{PD} \end{array}$ | /DT;<br>T postsca                                                                | ler;                             |                                              |

| Status Affected                                                  | I: TO, PD                                                                                                                           |                                                                                  |                                  |                                              |

| Encoding:                                                        | 0000                                                                                                                                | 0000                                                                             | 0000                             | 0011                                         |

| Description:                                                     | cleared. T<br>set. Watch<br>are cleare<br>The proce                                                                                 | r down stat<br>he time-out<br>ndog Timer<br>nd.<br>essor is put<br>n the oscilla | t status I<br>and its<br>into SL | bit ( <del>TO</del> ) is<br>prescaler<br>EEP |

| Words:                                                           | 1                                                                                                                                   |                                                                                  |                                  |                                              |

| Cycles:                                                          | 1                                                                                                                                   |                                                                                  |                                  |                                              |

| Q Cycle Activit                                                  | y:                                                                                                                                  |                                                                                  |                                  |                                              |

| Q1                                                               | Q2                                                                                                                                  | Q3                                                                               |                                  | Q4                                           |

| Decode                                                           | Read<br>register<br>PCLATH                                                                                                          | Execute                                                                          | e                                | NOP                                          |

| Example:                                                         | SLEEP                                                                                                                               |                                                                                  |                                  |                                              |

| Before Instruction<br>$\overline{TO} = ?$<br>$\overline{PD} = ?$ |                                                                                                                                     |                                                                                  |                                  |                                              |

| After Instru<br>TO =<br>PD =<br>† If WDT caus                    | uction<br>1 †<br>0<br>ses wake-up, t                                                                                                | his bit is c                                                                     | leared                           |                                              |

† If WDT causes wake-up, this bit is cleared

| SUE                                                             | BLW                                                  | S                   | Subtract WREG from Literal                                                             |                    |                          |     |    |                  |  |  |

|-----------------------------------------------------------------|------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------|--------------------|--------------------------|-----|----|------------------|--|--|

| Syntax:                                                         |                                                      |                     | [ label ] SUBLW k                                                                      |                    |                          |     |    |                  |  |  |

| Operands:                                                       |                                                      |                     | 0 ≤ k ≤ 255                                                                            |                    |                          |     |    |                  |  |  |

| Ope                                                             | ration:                                              | k                   | k – (WREG) → (WREG)                                                                    |                    |                          |     |    |                  |  |  |

| Stat                                                            | us Affected:                                         | C                   | OV, C, DC, Z                                                                           |                    |                          |     |    |                  |  |  |

| Enc                                                             | oding:                                               | Γ                   | 1011 0010 kkkk kk                                                                      |                    |                          |     |    |                  |  |  |

| Des                                                             | cription:                                            | li                  | WREG is subtracted from the eight bit<br>literal 'k'. The result is placed in<br>WREG. |                    |                          |     |    |                  |  |  |

| Wor                                                             | ds:                                                  | 1                   |                                                                                        |                    |                          |     |    |                  |  |  |

| Cycl                                                            | les:                                                 | 1                   |                                                                                        |                    |                          |     |    |                  |  |  |

| QC                                                              | ycle Activity:                                       |                     |                                                                                        |                    |                          |     |    |                  |  |  |

|                                                                 | Q1                                                   |                     | Q2                                                                                     |                    | Q3                       |     | Q4 |                  |  |  |

|                                                                 | Decode                                               | -                   | Read<br>eral 'k                                                                        | ۲'                 | Execu                    | ite |    | Write to<br>WREG |  |  |

| Exa                                                             | <u>mple 1</u> :                                      | S                   | UBLW                                                                                   | 1 (                | Ox02                     |     |    |                  |  |  |

|                                                                 | Before Instru<br>WREG<br>C<br>After Instruct<br>WREG | =<br>=              | 1<br>?<br>n                                                                            |                    |                          |     |    |                  |  |  |

| C =<br>Z =<br>Example 2:                                        |                                                      |                     | 1 ; result is positive<br>0                                                            |                    |                          |     |    |                  |  |  |

|                                                                 | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>2<br>?                                                                            |                    |                          |     |    |                  |  |  |

| After Instruction<br>WREG =<br>C =<br>Z =<br><u>Example 3</u> : |                                                      |                     | 0<br>1<br>1                                                                            | 1 ; result is zero |                          |     |    |                  |  |  |

|                                                                 | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>3<br>?                                                                            |                    |                          |     |    |                  |  |  |

|                                                                 | After Instruct<br>WREG<br>C<br>Z                     | tion<br>=<br>=<br>= | FF<br>0<br>1                                                                           |                    | 's comple<br>esult is ne |     | ·  |                  |  |  |

| XORLW             | Exclusive OR Literal with                                                                       | XORWF                                                                                                                                                                                                                                                      | Exclusive OR WREG with f                                                                                                                                           |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                   | WREG                                                                                            | Syntax:                                                                                                                                                                                                                                                    | [label] XORWF f,d                                                                                                                                                  |  |  |  |  |  |

| Syntax:           | [ <i>label</i> ] XORLW k                                                                        | Operands:                                                                                                                                                                                                                                                  | $0 \le f \le 255$                                                                                                                                                  |  |  |  |  |  |

| Operands:         | $0 \le k \le 255$                                                                               |                                                                                                                                                                                                                                                            | d ∈ [0,1]                                                                                                                                                          |  |  |  |  |  |

| Operation:        | (WREG) .XOR. $k \rightarrow (WREG)$                                                             | Operation:                                                                                                                                                                                                                                                 | (WREG) .XOR. (f) $\rightarrow$ (dest)                                                                                                                              |  |  |  |  |  |

| Status Affected:  | Z                                                                                               | Status Affected:                                                                                                                                                                                                                                           | Z                                                                                                                                                                  |  |  |  |  |  |