#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 16MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 454 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

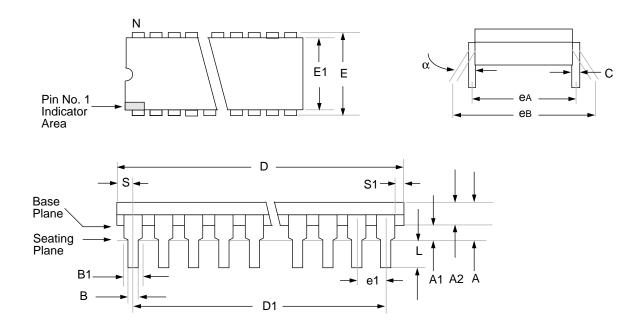

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44-16i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

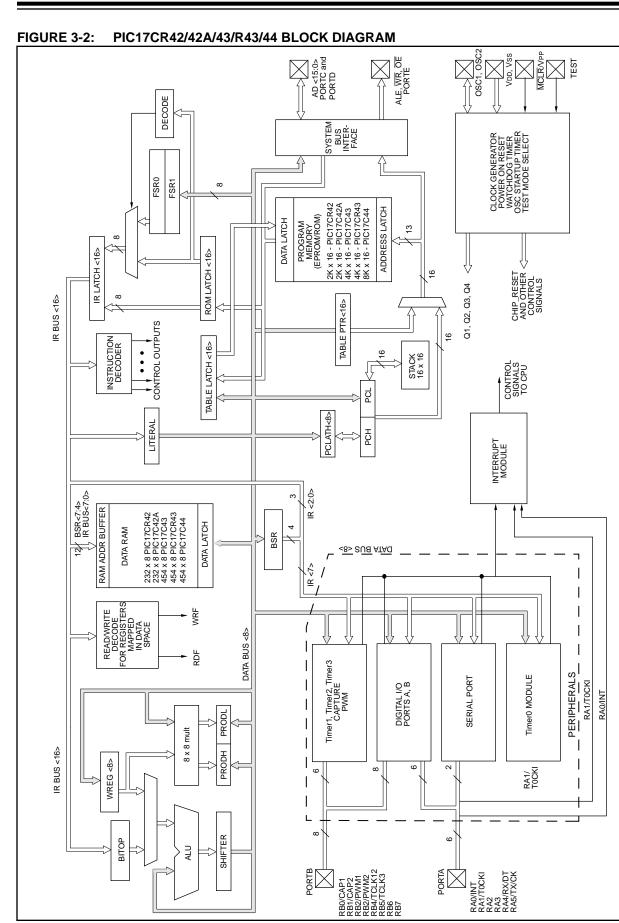

## 2.0 PIC17C4X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC17C4X Product Selection System section at the end of this data sheet. When placing orders, please use the "PIC17C4X Product Identification System" at the back of this data sheet to specify the correct part number.

For the PIC17C4X family of devices, there are four device "types" as indicated in the device number:

- C, as in PIC17C42. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC17LC42. These devices have EPROM type memory, operate over an extended voltage range, and reduced frequency range.

- 3. **CR**, as in PIC17**CR**42. These devices have ROM type memory and operate over the standard voltage range.

- 4. LCR, as in PIC17LCR42. These devices have ROM type memory, operate over an extended voltage range, and reduced frequency range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Microchip's PRO MATE<sup>TM</sup> programmer supports programming of the PIC17C4X. Third party programmers also are available; refer to the *Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers expecting frequent code changes and updates.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

ROM devices do not allow serialization information in the program memory space.

For information on submitting ROM code, please contact your regional sales office.

#### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

For information on submitting ROM code, please contact your regional sales office.

NOTES:

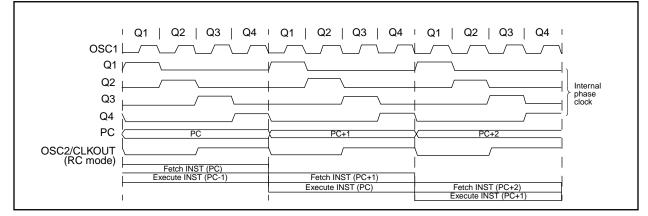

#### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-3.

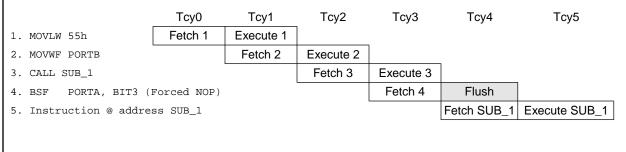

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g.GOTO) then two cycles are required to complete the instruction (Example 3-2).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

#### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

#### 4.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay after  $\overline{\text{MCLR}}$  is detected high or a wake-up from SLEEP event occurs.

The OST time-out is invoked only for XT and LF oscillator modes on a Power-on Reset or a Wake-up from SLEEP.

The OST counts the oscillator pulses on the OSC1/CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits reset. The length of time-out is a function of the crystal/resonator frequency.

#### 4.1.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First the internal POR signal goes high when the POR trip point is reached. If MCLR is high, then both the OST and PWRT timers start. In general the PWRT time-out is longer, except with low frequency crystals/resonators. The total time-out also varies based on oscillator configuration. Table 4-1 shows the times that are associated with the oscillator configuration. Figure 4-2 and Figure 4-3 display these time-out sequences.

If the device voltage is not within electrical specification at the end of a time-out, the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be held low until the voltage is within the device specification. The use of an external RC delay is sufficient for many of these applications.

## TABLE 4-1:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator<br>Configuration | Power-up                            | Wake up<br>from<br>SLEEP | MCLR<br>Reset |

|-----------------------------|-------------------------------------|--------------------------|---------------|

| XT, LF                      | Greater of:<br>96 ms or<br>1024Tosc | 1024Tosc                 | —             |

| EC, RC                      | Greater of:<br>96 ms or<br>1024Tosc |                          | —             |

The time-out sequence begins from the first rising edge of  $\overline{\text{MCLR}}$ .

Table 4-3 shows the reset conditions for some special registers, while Table 4-4 shows the initialization conditions for all the registers. The shaded registers (in Table 4-4) are for all devices except the PIC17C42. In the PIC17C42, the PRODH and PRODL registers are general purpose RAM.

## TABLE 4-2:STATUS BITS AND THEIR<br/>SIGNIFICANCE

| TO | PD | Event                                                                              |

|----|----|------------------------------------------------------------------------------------|

| 1  | 1  | Power-on Reset, MCLR Reset during normal operation, or CLRWDT instruction executed |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP                            |

| 0  | 1  | WDT Reset during normal operation                                                  |

| 0  | 0  | WDT Reset during SLEEP                                                             |

In Figure 4-2, Figure 4-3 and Figure 4-4, TPWRT > TOST, as would be the case in higher frequency crystals. For lower frequency crystals, (i.e., 32 kHz) TOST would be greater.

#### TABLE 4-3: RESET CONDITION FOR THE PROGRAM COUNTER AND THE CPUSTA REGISTER

| Event                             |                 | PCH:PCL               | CPUSTA | OST Active |  |

|-----------------------------------|-----------------|-----------------------|--------|------------|--|

| Power-on Reset                    |                 | 0000h                 | 11 11  | Yes        |  |

| MCLR Reset during normal ope      | ration          | 0000h                 | 11 11  | No         |  |

| MCLR Reset during SLEEP           |                 | 0000h                 | 11 10  | Yes (2)    |  |

| WDT Reset during normal operation | ation           | 0000h                 | 11 01  | No         |  |

| WDT Reset during SLEEP (3)        |                 | 0000h                 | 11 00  | Yes (2)    |  |

| Interrupt wake-up from SLEEP      | GLINTD is set   | PC + 1                | 11 10  | Yes (2)    |  |

|                                   | GLINTD is clear | PC + 1 <sup>(1)</sup> | 10 10  | Yes (2)    |  |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

Note 1: On wake-up, this instruction is executed. The instruction at the appropriate interrupt vector is fetched and then executed.

2: The OST is only active when the Oscillator is configured for XT or LF modes.

3: The Program Counter = 0, that is the device branches to the reset vector. This is different from the mid-range devices.

#### 6.4.1 INDIRECT ADDRESSING REGISTERS

The PIC17C4X has four registers for indirect addressing. These registers are:

- INDF0 and FSR0

- INDF1 and FSR1

Registers INDF0 and INDF1 are not physically implemented. Reading or writing to these registers activates indirect addressing, with the value in the corresponding FSR register being the address of the data. The FSR is an 8-bit register and allows addressing anywhere in the 256-byte data memory address range. For banked memory, the bank of memory accessed is specified by the value in the BSR.

If file INDF0 (or INDF1) itself is read indirectly via an FSR, all '0's are read (Zero bit is set). Similarly, if INDF0 (or INDF1) is written to indirectly, the operation will be equivalent to a NOP, and the status bits are not affected.

#### 6.4.2 INDIRECT ADDRESSING OPERATION

The indirect addressing capability has been enhanced over that of the PIC16CXX family. There are two control bits associated with each FSR register. These two bits configure the FSR register to:

- Auto-decrement the value (address) in the FSR after an indirect access

- Auto-increment the value (address) in the FSR after an indirect access

- No change to the value (address) in the FSR after an indirect access

These control bits are located in the ALUSTA register. The FSR1 register is controlled by the FS3:FS2 bits and FSR0 is controlled by the FS1:FS0 bits.

When using the auto-increment or auto-decrement features, the effect on the FSR is not reflected in the ALUSTA register. For example, if the indirect address causes the FSR to equal '0', the Z bit will not be set.

If the FSR register contains a value of 0h, an indirect read will read 0h (Zero bit is set) while an indirect write will be equivalent to a NOP (status bits are not affected).

Indirect addressing allows single cycle data transfers within the entire data space. This is possible with the use of the MOVPF and MOVFP instructions, where either 'p' or 'f' is specified as INDF0 (or INDF1).

If the source or destination of the indirect address is in banked memory, the location accessed will be determined by the value in the BSR. A simple program to clear RAM from 20h - FFh is shown in Example 6-1.

#### EXAMPLE 6-1: INDIRECT ADDRESSING

|    | MOVLW  | 0x20        | ;           |           |

|----|--------|-------------|-------------|-----------|

|    | MOVWF  | FSR0        | ; FSR0 = 20 | h         |

|    | BCF    | ALUSTA, FS1 | ; Increment | FSR       |

|    | BSF    | ALUSTA, FSO | ; after acc | ess       |

|    | BCF    | ALUSTA, C   | ; C = 0     |           |

|    | MOVLW  | END_RAM + 1 | ;           |           |

| LP | CLRF   | INDF0       | ; Addr(FSR) | = 0       |

|    | CPFSEQ | FSR0        | ; FSRO = EN | ID_RAM+1? |

|    | GOTO   | LP          | ; NO, clear | next      |

|    | :      |             | ; YES, All  | RAM is    |

|    | :      |             | ; cleared   |           |

|    |        |             |             |           |

#### 6.5 <u>Table Pointer (TBLPTRL and</u> <u>TBLPTRH)</u>

File registers TBLPTRL and TBLPTRH form a 16-bit pointer to address the 64K program memory space. The table pointer is used by instructions TABLWT and TABLRD.

The TABLRD and the TABLWT instructions allow transfer of data between program and data space. The table pointer serves as the 16-bit address of the data word within the program memory. For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

#### 6.6 <u>Table Latch (TBLATH, TBLATL)</u>

The table latch (TBLAT) is a 16-bit register, with TBLATH and TBLATL referring to the high and low bytes of the register. It is not mapped into data or program memory. The table latch is used as a temporary holding latch during data transfer between program and data memory (see descriptions of instructions TABLRD, TABLWT, TLRD and TLWT). For a more complete description of these registers and the operation of Table Reads and Table Writes, see Section 7.0.

Example 9-1 shows the instruction sequence to initialize PORTB. The Bank Select Register (BSR) must be selected to Bank 0 for the port to be initialized.

#### EXAMPLE 9-1: INITIALIZING PORTB

| MOVLB | 0     | ; | Select Bank 0                |

|-------|-------|---|------------------------------|

| CLRF  | PORTB | ; | Initialize PORTB by clearing |

|       |       | ; | output data latches          |

| MOVLW | 0xCF  | ; | Value used to initialize     |

|       |       | ; | data direction               |

| MOVWF | DDRB  | ; | Set RB<3:0> as inputs        |

|       |       | ; | RB<5:4> as outputs           |

|       |       | ; | RB<7:6> as inputs            |

|       |       |   |                              |

| Name       | Bit  | Buffer Type | Function                                                                                                                                 |

|------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/CAP1   | bit0 | ST          | Input/Output or the RB0/CAP1 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB1/CAP2   | bit1 | ST          | Input/Output or the RB1/CAP2 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB2/PWM1   | bit2 | ST          | Input/Output or the RB2/PWM1 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB3/PWM2   | bit3 | ST          | Input/Output or the RB3/PWM2 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB4/TCLK12 | bit4 | ST          | Input/Output or the external clock input to Timer1 and Timer2. Software pro-<br>grammable weak pull-up and interrupt on change features. |

| RB5/TCLK3  | bit5 | ST          | Input/Output or the external clock input to Timer3. Software programmable weak pull-up and interrupt on change features.                 |

| RB6        | bit6 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

| RB7        | bit7 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

#### TABLE 9-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger input.

#### TABLE 9-4: REGISTERS/BITS ASSOCIATED WITH PORTB

| Address       | Name   | Bit 7      | Bit 6         | Bit 5        | Bit 4  | Bit 3   | Bit 2  | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|---------------|--------------|--------|---------|--------|-----------|---------|-------------------------------|--------------------------------------------|

| 12h, Bank 0   | PORTB  | PORTB d    | ata latch     |              |        |         |        |           |         | xxxx xxxx                     | uuuu uuuu                                  |

| 11h, Bank 0   | DDRB   | Data dired | ction registe | er for PORTE | 5      |         |        |           |         | 1111 1111                     | 1111 1111                                  |

| 10h, Bank 0   | PORTA  | RBPU       | _             | RA5          | RA4    | RA3     | RA2    | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                                  |

| 06h, Unbanked | CPUSTA | _          | _             | STKAV        | GLINTD | TO      | PD     | _         | _       | 11 11                         | 11 qq                                      |

| 07h, Unbanked | INTSTA | PEIF       | <b>T0CKIF</b> | T0IF         | INTF   | PEIE    | T0CKIE | T0IE      | INTE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF        | TMR2IF       | TMR1IF | CA2IF   | CA1IF  | TXIF      | RCIF    | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE        | TMR2IE       | TMR1IE | CA2IE   | CA1IE  | TXIE      | RCIE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0        | CA1ED1       | CA1ED0 | T16     | TMR3CS | TMR2CS    | TMR1CS  | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF        | PWM2ON       | PWM10N | CA1/PR3 | TMR3ON | TMR2ON    | TMR10N  | 0000 0000                     | 0000 0000                                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = Value depends on condition.

Shaded cells are not used by PORTB.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

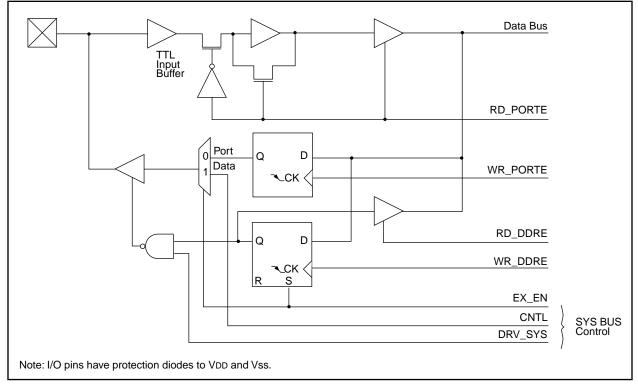

#### 9.4.1 PORTE AND DDRE REGISTER

PORTE is a 3-bit bi-directional port. The corresponding data direction register is DDRE. A '1' in DDRE configures the corresponding port pin as an input. A '0' in the DDRE register configures the corresponding port pin as an output. Reading PORTE reads the status of the pins, whereas writing to it will write to the port latch. PORTE is multiplexed with the system bus. When operating as the system bus, PORTE contains the control signals for the address/data bus (AD15:AD0). These control signals are Address Latch Enable (ALE), Output Enable ( $\overline{OE}$ ), and Write ( $\overline{WR}$ ). The control signals  $\overline{OE}$  and  $\overline{WR}$  are active low signals. The timing for the system bus is shown in the Electrical Characteristics section.

Note: This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-4 shows the instruction sequence to initialize PORTE. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-4: INITIALIZING PORTE

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTE | ; | Initialize PORTE data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0x03  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRE  | ; | Set RE<1:0> as inputs    |

|       |       | ; | RE<2> as outputs         |

|       |       | ; | RE<7:3> are always       |

|       |       | ; | read as '0'              |

#### FIGURE 9-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

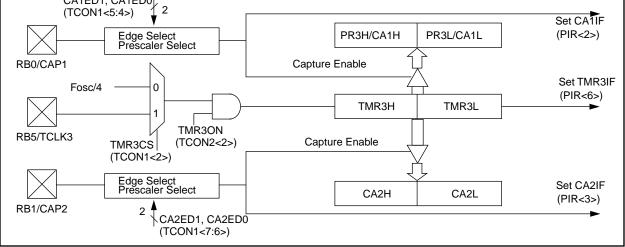

#### 12.2.2 DUAL CAPTURE REGISTER MODE

This mode is selected by setting CA1/PR3. A block diagram is shown in Figure 12-8. In this mode, TMR3 runs without a period register and increments from 0000h to FFFFh and rolls over to 0000h. The TMR3 interrupt Flag (TMR3IF) is set on this roll over. The TMR3IF bit must be cleared in software.

Registers PR3H/CA1H and PR3L/CA1L make a 16-bit capture register (Capture1). It captures events on pin RB0/CAP1. Capture mode is configured by the CA1ED1 and CA1ED0 bits. Capture1 Interrupt Flag bit (CA1IF) is set on the capture event. The corresponding interrupt mask bit is CA1IE. The Capture1 Overflow Status bit is CA1OVF.

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the TMR3 value to the capture register which protects the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The operation of the Capture1 feature is identical to Capture2 (as described in Section 12.2.1).

#### TABLE 12-5: REGISTERS ASSOCIATED WITH CAPTURE

| Address       | Name      | Bit 7     | Bit 6         | Bit 5          | Bit 4         | Bit 3         | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-----------|-----------|---------------|----------------|---------------|---------------|--------|--------|--------|-------------------------------|-----------------------------------------|

| 16h, Bank 3   | TCON1     | CA2ED1    | CA2ED0        | CA1ED1         | CA1ED0        | T16           | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3   | TCON2     | CA2OVF    | CA10VF        | PWM2ON         | PWM10N        | CA1/PR3       | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                               |

| 12h, Bank 2   | TMR3L     | TMR3 reg  | ister; low by | /te            |               |               |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 2   | TMR3H     | TMR3 reg  | ister; high b | oyte           |               |               |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 16h, Bank 1   | PIR       | RBIF      | TMR3IF        | TMR2IF         | TMR1IF        | CA2IF         | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1   | PIE       | RBIE      | TMR3IE        | TMR2IE         | TMR1IE        | CA2IE         | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked | INTSTA    | PEIF      | T0CKIF        | T0IF           | INTF          | PEIE          | T0CKIE | T0IE   | INTE   | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked | CPUSTA    | —         | _             | STKAV          | GLINTD        | TO            | PD     | —      | —      | 11 11                         | 11 qq                                   |

| 16h, Bank 2   | PR3L/CA1L | Timer3 pe | riod registe  | r, low byte/ca | apture1 regis | ter, low byte | e      |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 2   | PR3H/CA1H | Timer3 pe | riod registe  | r, high byte/c | apture1 regi  | ster, high b  | yte    |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 14h, Bank 3   | CA2L      | Capture2  | low byte      |                |               |               |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 3   | CA2H      | Capture2  | high byte     |                |               |               |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition, shaded cells are not used by Capture.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

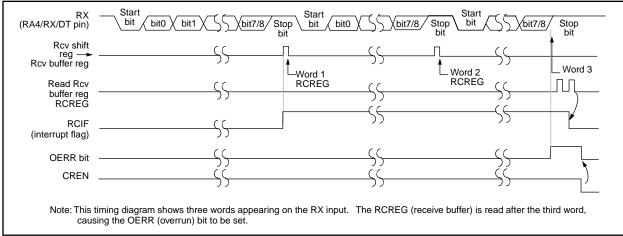

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

#### FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6</b> : | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|---------------------|---------------------------------------------------------|

|                     |                                                         |

| Address     | Name                                           | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|------------------------------------------------|-------|--------|--------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR                                            | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA                                          | SPEN  | RX9    | SREN   | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0 | RCREG                                          | RX7   | RX6    | RX5    | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE                                            | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA                                          | CSRC  | TX9    | TXEN   | SYNC   | _     | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | 17h, Bank 0 SPBRG Baud rate generator register |       |        |        |        |       |       |       |       |                               | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

| Address     | Name  | Bit 7     | Bit 6     | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-----------|-----------|----------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR   | RBIF      | TMR3IF    | TMR2IF   | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA | SPEN      | RX9       | SREN     | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0 | RCREG | RX7       | RX6       | RX5      | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE   | RBIE      | TMR3IE    | TMR2IE   | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA | CSRC      | TX9       | TXEN     | SYNC   |       | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | SPBRG | Baud rate | generator | register |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous master reception.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

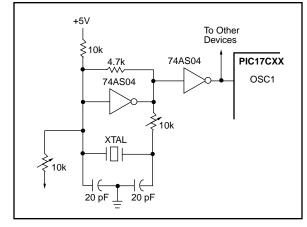

#### 14.2.4 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

Figure 14-5 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 14-5: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

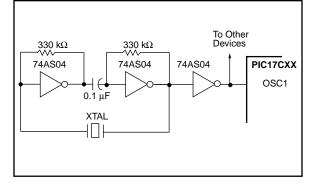

Figure 14-6 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 14-6: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

#### 14.2.5 RC OSCILLATOR

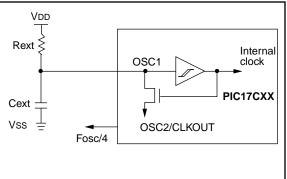

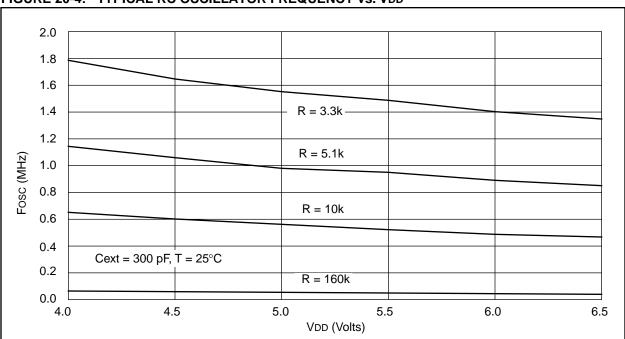

For timing insensitive applications, the RC device option offers additional cost savings. RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 14-6 shows how the R/C combination is connected to the PIC17CXX. For Rext values below 2.2 kQ, the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3  $k\Omega$  and 100  $k\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With little or no external capacitance, oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 18.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 18.0 for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-2 for waveform).

#### FIGURE 14-7: RC OSCILLATOR MODE

| BSF                                                                                                     | Bit Set f                                                          |                                   |                       |    |      |  |

|---------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------|-----------------------|----|------|--|

| Syntax: [label] BSF f,b                                                                                 |                                                                    |                                   |                       |    |      |  |

| Operands:                                                                                               | $\begin{array}{l} 0 \leq f \leq 25 \\ 0 \leq b \leq 7 \end{array}$ | $0 \le f \le 255$ $0 \le b \le 7$ |                       |    |      |  |

| Operation:                                                                                              | $1 \rightarrow (f < b >$                                           | -)                                |                       |    |      |  |

| Status Affected:                                                                                        | None                                                               |                                   |                       |    |      |  |

| Encoding:                                                                                               | 1000                                                               | 0bbb                              | fff                   | f  | ffff |  |

| Description:                                                                                            | Bit 'b' in re                                                      | gister 'f' is                     | s set.                |    |      |  |

| Words:                                                                                                  | 1                                                                  |                                   |                       |    |      |  |

| Cycles:                                                                                                 | 1                                                                  |                                   |                       |    |      |  |

| Q Cycle Activity:                                                                                       |                                                                    |                                   |                       |    |      |  |

| Q1                                                                                                      | Q2                                                                 | Q3                                |                       | Q4 |      |  |

| Decode                                                                                                  | Read<br>register 'f'                                               | Execu                             | ute Write<br>register |    |      |  |

| Example:                                                                                                | BSF                                                                | FLAG_RE                           | G, 7                  |    |      |  |

| Example: BSF FLAG_REG, 7<br>Before Instruction<br>FLAG_REG= 0x0A<br>After Instruction<br>FLAG_REG= 0x8A |                                                                    |                                   |                       |    |      |  |

| BTF        | SC                                                    | Bit Test, s                                                                 | Bit Test, skip if Clear                                                                                                                                                                                                                               |        |      |  |  |  |

|------------|-------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--|--|--|

| Synt       | tax:                                                  | [ <i>label</i> ] B                                                          | [label] BTFSC f,b                                                                                                                                                                                                                                     |        |      |  |  |  |

| Ope        | rands:                                                | $0 \le f \le 253$ $0 \le b \le 7$                                           | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                                                   |        |      |  |  |  |

| Ope        | ration:                                               | skip if (f <t< td=""><td>o&gt;) = 0</td><td></td><td></td></t<>             | o>) = 0                                                                                                                                                                                                                                               |        |      |  |  |  |

| Stat       | us Affected:                                          | None                                                                        |                                                                                                                                                                                                                                                       |        |      |  |  |  |

| Enc        | oding:                                                | 1001                                                                        | 1bbb                                                                                                                                                                                                                                                  | ffff   | ffff |  |  |  |

| Des        | cription:                                             | instruction<br>If bit 'b' is 0<br>fetched du<br>cution is di<br>cuted inste | If bit 'b' in register 'f' is 0 then the next instruction is skipped.<br>If bit 'b' is 0 then the next instruction fetched during the current instruction execution is discarded, and a NOP is executed instead, making this a two-cycle instruction. |        |      |  |  |  |

| Wor        | ds:                                                   | 1                                                                           | 1                                                                                                                                                                                                                                                     |        |      |  |  |  |

| Cycl       | les:                                                  | 1(2)                                                                        | 1(2)                                                                                                                                                                                                                                                  |        |      |  |  |  |

| QC         | ycle Activity:                                        |                                                                             |                                                                                                                                                                                                                                                       |        |      |  |  |  |

|            | Q1                                                    | Q2                                                                          | Q3                                                                                                                                                                                                                                                    |        | Q4   |  |  |  |

|            | Decode                                                | Read<br>register 'f'                                                        | Execu                                                                                                                                                                                                                                                 | ite    | NOP  |  |  |  |

| lf sk      | ip:                                                   |                                                                             |                                                                                                                                                                                                                                                       |        |      |  |  |  |

|            | Q1                                                    | Q2                                                                          | Q3                                                                                                                                                                                                                                                    |        | Q4   |  |  |  |

|            | Forced NOP                                            | NOP                                                                         | Execu                                                                                                                                                                                                                                                 | ite    | NOP  |  |  |  |

| <u>Exa</u> | mple:                                                 | FALSE                                                                       | BTFSC<br>:                                                                                                                                                                                                                                            | FLAG,1 |      |  |  |  |

|            | Before Instru<br>PC                                   |                                                                             | dress (HE                                                                                                                                                                                                                                             | RE)    |      |  |  |  |

|            | After Instructi<br>If FLAG<7<br>PC<br>If FLAG<7<br>PC | l> = 0;<br>= ac<br>l> = 1;                                                  | ldress (TR                                                                                                                                                                                                                                            |        |      |  |  |  |

| CPFS             | SLT                                            | Compare<br>skip if f <                                               | f with WREG                                                                                                                                                                                                                                                                                          | G,      |  |  |  |  |  |

|------------------|------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| Synta            | ax:                                            | [label]                                                              | [label] CPFSLT f                                                                                                                                                                                                                                                                                     |         |  |  |  |  |  |

| Opera            | ands:                                          | $0 \le f \le 25$                                                     | 5                                                                                                                                                                                                                                                                                                    |         |  |  |  |  |  |

| Operation:       |                                                | skip if (f) <                                                        | (f) – (WREG),<br>skip if (f) < (WREG)<br>(unsigned comparison)                                                                                                                                                                                                                                       |         |  |  |  |  |  |

| Status Affected: |                                                | None                                                                 | None                                                                                                                                                                                                                                                                                                 |         |  |  |  |  |  |

| Enco             | ding:                                          | 0011                                                                 | 0000 ffi                                                                                                                                                                                                                                                                                             | ff ffff |  |  |  |  |  |

| Desc             | ription:                                       | location 'f'<br>performing<br>If the conte<br>WREG, the<br>discarded | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If the contents of 'f' < the contents of<br>WREG, then the fetched instruction is<br>discarded and an NOP is executed<br>instead making this a two-cycle instruc-<br>tion. |         |  |  |  |  |  |

| Word             | s:                                             | 1                                                                    |                                                                                                                                                                                                                                                                                                      |         |  |  |  |  |  |

| Cycle            | es:                                            | 1 (2)                                                                | 1 (2)                                                                                                                                                                                                                                                                                                |         |  |  |  |  |  |

| Q Cy             | cle Activity:                                  |                                                                      |                                                                                                                                                                                                                                                                                                      |         |  |  |  |  |  |

|                  | Q1                                             | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                   | Q4      |  |  |  |  |  |

|                  | Decode                                         | Read<br>register 'f'                                                 | Execute                                                                                                                                                                                                                                                                                              | NOP     |  |  |  |  |  |

| lf skip          | o:                                             |                                                                      |                                                                                                                                                                                                                                                                                                      |         |  |  |  |  |  |

| -                | Q1                                             | Q2                                                                   | Q3                                                                                                                                                                                                                                                                                                   | Q4      |  |  |  |  |  |

|                  | Forced NOP                                     | NOP                                                                  | Execute                                                                                                                                                                                                                                                                                              | NOP     |  |  |  |  |  |

| <u>Exarr</u>     | nple:                                          | HERE<br>NLESS<br>LESS                                                | CPFSLT REG<br>:<br>:                                                                                                                                                                                                                                                                                 |         |  |  |  |  |  |

| E                | Before Instru<br>PC<br>W                       |                                                                      | ddress (HERE)                                                                                                                                                                                                                                                                                        |         |  |  |  |  |  |

| F                | After Instruct<br>If REG<br>PC<br>If REG<br>PC | < W<br>= Ac<br>≥ W                                                   | REG;<br>ddress (LESS)<br>REG;<br>ddress (NLESS                                                                                                                                                                                                                                                       |         |  |  |  |  |  |

| DAW                 |                                                | Decimal                                                      | Adjust WRE                                                                                                                                                                                                        | G Register                                         |  |  |  |

|---------------------|------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| Syntax              | K:                                             | [ <i>label</i> ] D                                           | AW f,s                                                                                                                                                                                                            |                                                    |  |  |  |

| Opera               | nds:                                           | $0 \le f \le 25$<br>s $\in [0,1]$                            | 5                                                                                                                                                                                                                 |                                                    |  |  |  |

| Opera               | tion:                                          | <sup>-</sup> WREG<br>else                                    | If [WREG<3:0> >9] .OR. [DC = 1] then<br>WREG<3:0> + 6 $\rightarrow$ f<3:0>, s<3:0>;<br>else<br>WREG<3:0> $\rightarrow$ f<3:0>, s<3:0>;                                                                            |                                                    |  |  |  |

|                     |                                                | WREG                                                         |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Status              | Affected:                                      | C                                                            | $<7:4> \rightarrow f<7:$                                                                                                                                                                                          | 4>, S<7:4>                                         |  |  |  |

| Encoding:           |                                                | 0010                                                         | 111s ff                                                                                                                                                                                                           | ff ffff                                            |  |  |  |

| Descri              | U                                              |                                                              | ts the eight bi                                                                                                                                                                                                   |                                                    |  |  |  |

|                     |                                                | tion of two<br>BCD forma<br>packed BC<br>s = 0: Ro<br>m<br>W | WREG resulting from the earlier addi-<br>tion of two variables (each in packed<br>BCD format) and produces a correct<br>packed BCD result.<br>s = 0: Result is placed in Data<br>memory location 'f' and<br>WREG. |                                                    |  |  |  |

|                     |                                                |                                                              | s = 1: Result is placed in Data<br>memory location 'f'.                                                                                                                                                           |                                                    |  |  |  |

| Words               | :                                              | 1                                                            |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Cycles              | 8:                                             | 1                                                            |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Q Cyc               | le Activity:                                   |                                                              |                                                                                                                                                                                                                   | •                                                  |  |  |  |

|                     | Q1<br>Decode                                   | Q2<br>Read                                                   | Q3<br>Execute                                                                                                                                                                                                     | Q4<br>Write                                        |  |  |  |

|                     | Decode                                         | register 'f'                                                 | Execute                                                                                                                                                                                                           | register 'f'<br>and other<br>specified<br>register |  |  |  |

| Exam                | ole1:                                          | DAW RE                                                       | G1, 0                                                                                                                                                                                                             |                                                    |  |  |  |

| B                   | <br>efore Instru                               | iction                                                       |                                                                                                                                                                                                                   |                                                    |  |  |  |

|                     | WREG<br>REG1<br>C<br>DC                        | = 0xA5<br>= ??<br>= 0<br>= 0                                 |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Ai<br><u>Exam</u> t | fter Instruct<br>WREG<br>REG1<br>C<br>DC<br>DC | ion<br>= 0x05<br>= 0x05<br>= 1<br>= 0                        |                                                                                                                                                                                                                   |                                                    |  |  |  |

| В                   | efore Instru                                   |                                                              |                                                                                                                                                                                                                   |                                                    |  |  |  |

|                     | WREG<br>REG1<br>C                              | = 0xCE<br>= ??<br>= 0                                        |                                                                                                                                                                                                                   |                                                    |  |  |  |

| U             | -    | 0    |

|---------------|------|------|

| DC            | =    | 0    |

| After Instruc | tion |      |

| WREG          | =    | 0x24 |

| REG1          | =    | 0x24 |

| С             | =    | 1    |

| DC            | =    | 0    |

| RRNCF                                                                                                        | Rotate F                                                                                                                                                                                    | Right f (no                                                                                                                                                              | carry)               |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|--|

| Syntax:                                                                                                      | [ label ]                                                                                                                                                                                   | RRNCF 1                                                                                                                                                                  | i,d                  |  |  |  |  |

| Operands:                                                                                                    | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                                                                                                                                                     |                                                                                                                                                                          |                      |  |  |  |  |

| Operation:                                                                                                   |                                                                                                                                                                                             | $f < n > \rightarrow d < n-1 >;$<br>$f < 0 > \rightarrow d < 7 >$                                                                                                        |                      |  |  |  |  |

| Status Affected:                                                                                             | None                                                                                                                                                                                        |                                                                                                                                                                          |                      |  |  |  |  |

| Encoding:                                                                                                    | 0010                                                                                                                                                                                        | 000d                                                                                                                                                                     | ffff ffff            |  |  |  |  |

| Description:                                                                                                 | one bit to<br>placed in                                                                                                                                                                     | The contents of register 'f' are rotated<br>one bit to the right. If 'd' is 0 the result is<br>placed in WREG. If 'd' is 1 the result is<br>placed back in register 'f'. |                      |  |  |  |  |

|                                                                                                              | Г                                                                                                                                                                                           | ► regis                                                                                                                                                                  | ster f               |  |  |  |  |

| Words:                                                                                                       | 1                                                                                                                                                                                           |                                                                                                                                                                          |                      |  |  |  |  |

| Cycles:                                                                                                      | 1                                                                                                                                                                                           |                                                                                                                                                                          |                      |  |  |  |  |

| Q Cycle Activity:                                                                                            |                                                                                                                                                                                             |                                                                                                                                                                          |                      |  |  |  |  |

| Q1                                                                                                           | Q2                                                                                                                                                                                          | Q3                                                                                                                                                                       | Q4                   |  |  |  |  |

| Decode                                                                                                       | Read<br>register 'f'                                                                                                                                                                        | Execute                                                                                                                                                                  | Write to destination |  |  |  |  |

| Example 1:                                                                                                   | RRNCF                                                                                                                                                                                       | REG, 1                                                                                                                                                                   |                      |  |  |  |  |

|                                                                                                              | Induced                                                                                                                                                                                     | KEG, I                                                                                                                                                                   |                      |  |  |  |  |

| Before Instru                                                                                                |                                                                                                                                                                                             | KEG, I                                                                                                                                                                   |                      |  |  |  |  |

| -                                                                                                            | iction<br>= ?                                                                                                                                                                               | 0111                                                                                                                                                                     |                      |  |  |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct                                                               | iction<br>= ?<br>= 1101                                                                                                                                                                     |                                                                                                                                                                          |                      |  |  |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG                                                       | tion<br>= ?<br>= 1101<br>tion<br>= 0                                                                                                                                                        | 0111                                                                                                                                                                     |                      |  |  |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct                                                               | iction<br>= ?<br>= 1101<br>tion                                                                                                                                                             |                                                                                                                                                                          |                      |  |  |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG                                                       | tion<br>= ?<br>= 1101<br>tion<br>= 0                                                                                                                                                        | 0111                                                                                                                                                                     |                      |  |  |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG<br>REG<br><u>Example 2</u> :<br>Before Instru<br>WREG | Interview       ?         =       1101         tion       ?         =       0         =       1110         RRNCF         Interview         action         =       ?                         | 0111<br>1011<br>REG, 0                                                                                                                                                   |                      |  |  |  |  |