Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 25MHz                                                                   |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 454 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44-25-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay after  $\overline{\text{MCLR}}$  is detected high or a wake-up from SLEEP event occurs.

The OST time-out is invoked only for XT and LF oscillator modes on a Power-on Reset or a Wake-up from SLEEP.

The OST counts the oscillator pulses on the OSC1/CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits reset. The length of time-out is a function of the crystal/resonator frequency.

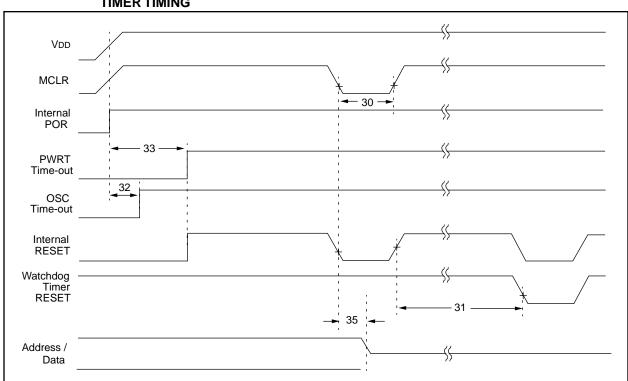

#### 4.1.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First the internal POR signal goes high when the POR trip point is reached. If MCLR is high, then both the OST and PWRT timers start. In general the PWRT time-out is longer, except with low frequency crystals/resonators. The total time-out also varies based on oscillator configuration. Table 4-1 shows the times that are associated with the oscillator configuration. Figure 4-2 and Figure 4-3 display these time-out sequences.

If the device voltage is not within electrical specification at the end of a time-out, the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be held low until the voltage is within the device specification. The use of an external RC delay is sufficient for many of these applications.

# TABLE 4-1:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator<br>Configuration | Power-up                            | Wake up<br>from<br>SLEEP | MCLR<br>Reset |

|-----------------------------|-------------------------------------|--------------------------|---------------|

| XT, LF                      | Greater of:<br>96 ms or<br>1024Tosc | 1024Tosc                 | —             |

| EC, RC                      | Greater of:<br>96 ms or<br>1024Tosc |                          | —             |

The time-out sequence begins from the first rising edge of  $\overline{\text{MCLR}}$ .

Table 4-3 shows the reset conditions for some special registers, while Table 4-4 shows the initialization conditions for all the registers. The shaded registers (in Table 4-4) are for all devices except the PIC17C42. In the PIC17C42, the PRODH and PRODL registers are general purpose RAM.

# TABLE 4-2:STATUS BITS AND THEIR<br/>SIGNIFICANCE

| TO | PD | Event                                                                              |

|----|----|------------------------------------------------------------------------------------|

| 1  | 1  | Power-on Reset, MCLR Reset during normal operation, or CLRWDT instruction executed |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP                            |

| 0  | 1  | WDT Reset during normal operation                                                  |

| 0  | 0  | WDT Reset during SLEEP                                                             |

In Figure 4-2, Figure 4-3 and Figure 4-4, TPWRT > TOST, as would be the case in higher frequency crystals. For lower frequency crystals, (i.e., 32 kHz) TOST would be greater.

#### TABLE 4-3: RESET CONDITION FOR THE PROGRAM COUNTER AND THE CPUSTA REGISTER

| Event                                 |                 | PCH:PCL               | CPUSTA | OST Active |

|---------------------------------------|-----------------|-----------------------|--------|------------|

| Power-on Reset                        |                 | 0000h                 | 11 11  | Yes        |

| MCLR Reset during normal ope          | ration          | 0000h                 | 11 11  | No         |

| MCLR Reset during SLEEP               |                 | 0000h                 | 11 10  | Yes (2)    |

| WDT Reset during normal operation     | ation           | 0000h                 | 11 01  | No         |

| WDT Reset during SLEEP <sup>(3)</sup> |                 | 0000h                 | 11 00  | Yes (2)    |

| Interrupt wake-up from SLEEP          | GLINTD is set   | PC + 1                | 11 10  | Yes (2)    |

|                                       | GLINTD is clear | PC + 1 <sup>(1)</sup> | 10 10  | Yes (2)    |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

Note 1: On wake-up, this instruction is executed. The instruction at the appropriate interrupt vector is fetched and then executed.

2: The OST is only active when the Oscillator is configured for XT or LF modes.

3: The Program Counter = 0, that is the device branches to the reset vector. This is different from the mid-range devices.

### 6.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC17C4X; program memory and data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into General Purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

#### 6.1 Program Memory Organization

PIC17C4X devices have a 16-bit program counter capable of addressing a 64K x 16 program memory space. The reset vector is at 0000h and the interrupt vectors are at 0008h, 0010h, 0018h, and 0020h (Figure 6-1).

#### 6.1.1 PROGRAM MEMORY OPERATION

The PIC17C4X can operate in one of four possible program memory configurations. The configuration is selected by two configuration bits. The possible modes are:

- Microprocessor

- Microcontroller

- Extended Microcontroller

- Protected Microcontroller

The microcontroller and protected microcontroller modes only allow internal execution. Any access beyond the program memory reads unknown data. The protected microcontroller mode also enables the code protection feature.

The extended microcontroller mode accesses both the internal program memory as well as external program memory. Execution automatically switches between internal and external memory. The 16-bits of address allow a program memory range of 64K-words.

The microprocessor mode only accesses the external program memory. The on-chip program memory is ignored. The 16-bits of address allow a program memory range of 64K-words. Microprocessor mode is the default mode of an unprogrammed device.

The different modes allow different access to the configuration bits, test memory, and boot ROM. Table 6-1 lists which modes can access which areas in memory. Test Memory and Boot Memory are not required for normal operation of the device. Care should be taken to ensure that no unintended branches occur to these areas.

#### FIGURE 6-1: PROGRAM MEMORY MAP AND STACK

|                               | AND STACK                         |                     |

|-------------------------------|-----------------------------------|---------------------|

|                               | PC<15:0>                          | ]                   |

| CALL,                         | RETURN 1 16                       | 1                   |

| RETFI                         |                                   |                     |

|                               | Stack Level 1                     | 1                   |

|                               | :                                 | 1                   |

|                               | •<br>Stack Level 16               | -                   |

|                               | Stack Level 10                    | ]                   |

| T T                           | Reset Vector                      | ] 0000h             |

|                               |                                   |                     |

|                               | INT Pin Interrupt Vector          | 0008h               |

|                               | Timer0 Interrupt Vector           | 0010h               |

|                               | T0CKI Pin Interrupt Vector        | 0018h               |

|                               | Peripheral Interrupt Vector       | 0020h               |

|                               |                                   | 0021h               |

|                               |                                   |                     |

|                               |                                   | 7FFh<br>(PIC17C42,  |

| <u>&gt;</u>                   |                                   | PIC17CR42,          |

| User Memory<br>Space (1)      |                                   | PIC17C42A)          |

| ace                           |                                   | FFFh                |

| Spe                           |                                   | (PIC17C43           |

| n ∣                           |                                   | PIC17CR43)          |

|                               |                                   |                     |

|                               |                                   |                     |

|                               |                                   | 1FFFh<br>(PIC17C44) |

|                               |                                   | (FIC17C44)          |

|                               |                                   |                     |

|                               |                                   | l                   |

| <u>+</u>                      | FOSC0                             | FDFFh               |

| > [                           | FOSC0                             | FE00h<br>FE01h      |

| Jor                           | WDTPS0                            | FE02h               |

| len                           | WDTPS1                            | FE03h               |

| ≥ e                           | PM0                               | FE04h               |

| pac                           | Reserved                          | FE05h               |

| S IB                          | PM1                               | FE06h               |

| figu                          | Reserved                          | FE07h               |

| Configuration Memory<br>Space | Reserved                          | FE08h               |

|                               |                                   | FE0Eh               |

| 📕                             | PM2 <sup>(2)</sup>                | FE0Fh               |

|                               | Test EPROM                        | FE10h<br>FF5Fh      |

|                               |                                   | FF60h               |

|                               | Boot ROM                          |                     |

|                               |                                   | FFFFh               |

| Note 1: U                     | ser memory space may be inter     | nal, external, or   |

|                               | oth. The memory configuration of  |                     |

|                               | rocessor mode.                    | ,                   |

|                               | his location is reserved on the F | PIC17C42.           |

| 1                             |                                   |                     |

#### 6.2 Data Memory Organization

Data memory is partitioned into two areas. The first is the General Purpose Registers (GPR) area, while the second is the Special Function Registers (SFR) area. The SFRs control the operation of the device.

Portions of data memory are banked, this is for both areas. The GPR area is banked to allow greater than 232 bytes of general purpose RAM. SFRs are for the registers that control the peripheral functions. Banking requires the use of control bits for bank selection. These control bits are located in the Bank Select Register (BSR). If an access is made to a location outside this banked region, the BSR bits are ignored. Figure 6-5 shows the data memory map organization for the PIC17C42 and Figure 6-6 for all of the other PIC17C4X devices.

Instructions MOVPF and MOVFP provide the means to move values from the peripheral area ("P") to any location in the register file ("F"), and vice-versa. The definition of the "P" range is from 0h to 1Fh, while the "F" range is 0h to FFh. The "P" range has six more locations than peripheral registers (eight locations for the PIC17C42 device) which can be used as General Purpose Registers. This can be useful in some applications where variables need to be copied to other locations in the general purpose RAM (such as saving status information during an interrupt).

The entire data memory can be accessed either directly or indirectly through file select registers FSR0 and FSR1 (Section 6.4). Indirect addressing uses the appropriate control bits of the BSR for accesses into the banked areas of data memory. The BSR is explained in greater detail in Section 6.8.

#### 6.2.1 GENERAL PURPOSE REGISTER (GPR)

All devices have some amount of GPR area. The GPRs are 8-bits wide. When the GPR area is greater than 232, it must be banked to allow access to the additional memory space.

Only the PIC17C43 and PIC17C44 devices have banked memory in the GPR area. To facilitate switching between these banks, the MOVLR bank instruction has been added to the instruction set. GPRs are not initialized by a Power-on Reset and are unchanged on all other resets.

#### 6.2.2 SPECIAL FUNCTION REGISTERS (SFR)

The SFRs are used by the CPU and peripheral functions to control the operation of the device (Figure 6-5 and Figure 6-6). These registers are static RAM.

The SFRs can be classified into two sets, those associated with the "core" function and those related to the peripheral functions. Those registers related to the "core" are described here, while those related to a peripheral feature are described in the section for each peripheral feature.

The peripheral registers are in the banked portion of memory, while the core registers are in the unbanked region. To facilitate switching between the peripheral banks, the MOVLB bank instruction has been provided.

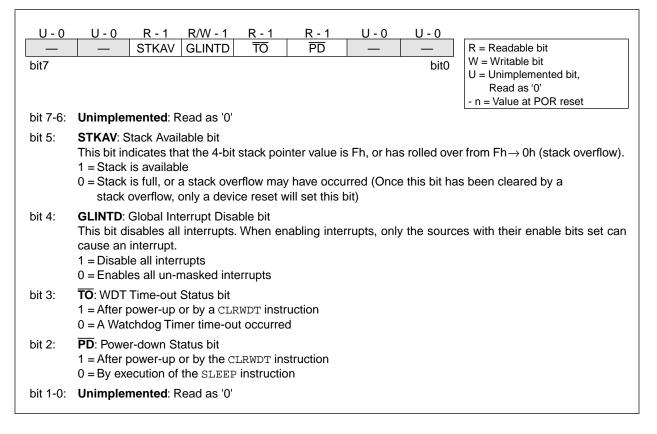

#### 6.2.2.2 CPU STATUS REGISTER (CPUSTA)

The CPUSTA register contains the status and control bits for the CPU. This register is used to globally enable/disable interrupts. If only a specific interrupt is desired to be enabled/disabled, please refer to the INTerrupt STAtus (INTSTA) register and the Peripheral Interrupt Enable (PIE) register. This register also indicates if the stack is available and contains the Power-down (PD) and Time-out (TO) bits. The TO, PD, and STKAV bits are not writable. These bits are set and cleared according to device logic. Therefore, the result of an instruction with the CPUSTA register as destination may be different than intended.

#### FIGURE 6-8: CPUSTA REGISTER (ADDRESS: 06h, UNBANKED)

Example 9-1 shows the instruction sequence to initialize PORTB. The Bank Select Register (BSR) must be selected to Bank 0 for the port to be initialized.

#### EXAMPLE 9-1: INITIALIZING PORTB

| MOVLB | 0     | ; | Select Bank 0                |

|-------|-------|---|------------------------------|

| CLRF  | PORTB | ; | Initialize PORTB by clearing |

|       |       | ; | output data latches          |

| MOVLW | 0xCF  | ; | Value used to initialize     |

|       |       | ; | data direction               |

| MOVWF | DDRB  | ; | Set RB<3:0> as inputs        |

|       |       | ; | RB<5:4> as outputs           |

|       |       | ; | RB<7:6> as inputs            |

|       |       |   |                              |

| Name       | Bit  | Buffer Type | Function                                                                                                                                 |

|------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/CAP1   | bit0 | ST          | Input/Output or the RB0/CAP1 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB1/CAP2   | bit1 | ST          | Input/Output or the RB1/CAP2 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB2/PWM1   | bit2 | ST          | Input/Output or the RB2/PWM1 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB3/PWM2   | bit3 | ST          | Input/Output or the RB3/PWM2 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB4/TCLK12 | bit4 | ST          | Input/Output or the external clock input to Timer1 and Timer2. Software pro-<br>grammable weak pull-up and interrupt on change features. |

| RB5/TCLK3  | bit5 | ST          | Input/Output or the external clock input to Timer3. Software programmable weak pull-up and interrupt on change features.                 |

| RB6        | bit6 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

| RB7        | bit7 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

#### TABLE 9-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger input.

#### TABLE 9-4: REGISTERS/BITS ASSOCIATED WITH PORTB

| Address       | Name   | Bit 7      | Bit 6         | Bit 5        | Bit 4  | Bit 3   | Bit 2  | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|---------------|--------------|--------|---------|--------|-----------|---------|-------------------------------|--------------------------------------------|

| 12h, Bank 0   | PORTB  | PORTB d    | ata latch     |              |        |         |        |           |         | xxxx xxxx                     | uuuu uuuu                                  |

| 11h, Bank 0   | DDRB   | Data dired | ction registe | er for PORTE | 5      |         |        |           |         | 1111 1111                     | 1111 1111                                  |

| 10h, Bank 0   | PORTA  | RBPU       | _             | RA5          | RA4    | RA3     | RA2    | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                                  |

| 06h, Unbanked | CPUSTA | _          | _             | STKAV        | GLINTD | TO      | PD     | _         | _       | 11 11                         | 11 qq                                      |

| 07h, Unbanked | INTSTA | PEIF       | <b>T0CKIF</b> | T0IF         | INTF   | PEIE    | T0CKIE | T0IE      | INTE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF        | TMR2IF       | TMR1IF | CA2IF   | CA1IF  | TXIF      | RCIF    | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE        | TMR2IE       | TMR1IE | CA2IE   | CA1IE  | TXIE      | RCIE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0        | CA1ED1       | CA1ED0 | T16     | TMR3CS | TMR2CS    | TMR1CS  | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF        | PWM2ON       | PWM10N | CA1/PR3 | TMR3ON | TMR2ON    | TMR10N  | 0000 0000                     | 0000 0000                                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = Value depends on condition.

Shaded cells are not used by PORTB.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

#### TABLE 9-5: PORTC FUNCTIONS

| Name    | Bit  | Buffer Type | Function                                     |

|---------|------|-------------|----------------------------------------------|

| RC0/AD0 | bit0 | TTL         | Input/Output or system bus address/data pin. |

| RC1/AD1 | bit1 | TTL         | Input/Output or system bus address/data pin. |

| RC2/AD2 | bit2 | TTL         | Input/Output or system bus address/data pin. |

| RC3/AD3 | bit3 | TTL         | Input/Output or system bus address/data pin. |

| RC4/AD4 | bit4 | TTL         | Input/Output or system bus address/data pin. |

| RC5/AD5 | bit5 | TTL         | Input/Output or system bus address/data pin. |

| RC6/AD6 | bit6 | TTL         | Input/Output or system bus address/data pin. |

| RC7/AD7 | bit7 | TTL         | Input/Output or system bus address/data pin. |

Legend: TTL = TTL input.

#### TABLE 9-6: REGISTERS/BITS ASSOCIATED WITH PORTC

| Address     | Name  | Bit 7       | Bit 6                            | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-------------|----------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------------------|-----------------------------------------|

| 11h, Bank 1 | PORTC | RC7/<br>AD7 | RC6/<br>AD6                      | RC5/<br>AD5 | RC4/<br>AD4 | RC3/<br>AD3 | RC2/<br>AD2 | RC1/<br>AD1 | RC0/<br>AD0 | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 1 | DDRC  | Data dired  | ata direction register for PORTC |             |             |             |             |             | 1111 1111   | 1111 1111                     |                                         |

Legend: x = unknown, u = unchanged.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

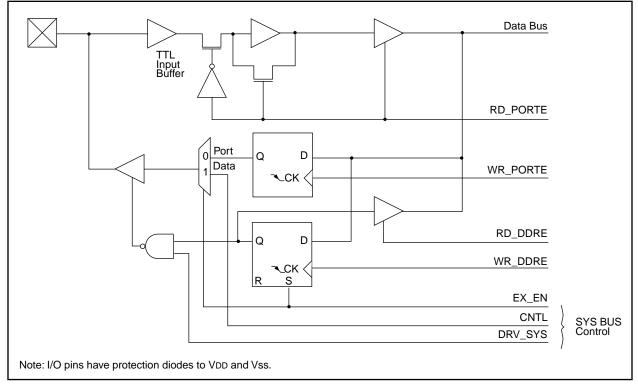

#### 9.4.1 PORTE AND DDRE REGISTER

PORTE is a 3-bit bi-directional port. The corresponding data direction register is DDRE. A '1' in DDRE configures the corresponding port pin as an input. A '0' in the DDRE register configures the corresponding port pin as an output. Reading PORTE reads the status of the pins, whereas writing to it will write to the port latch. PORTE is multiplexed with the system bus. When operating as the system bus, PORTE contains the control signals for the address/data bus (AD15:AD0). These control signals are Address Latch Enable (ALE), Output Enable ( $\overline{OE}$ ), and Write ( $\overline{WR}$ ). The control signals  $\overline{OE}$  and  $\overline{WR}$  are active low signals. The timing for the system bus is shown in the Electrical Characteristics section.

Note: This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-4 shows the instruction sequence to initialize PORTE. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-4: INITIALIZING PORTE

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTE | ; | Initialize PORTE data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0x03  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRE  | ; | Set RE<1:0> as inputs    |

|       |       | ; | RE<2> as outputs         |

|       |       | ; | RE<7:3> are always       |

|       |       | ; | read as '0'              |

#### FIGURE 9-8: PORTE BLOCK DIAGRAM (IN I/O PORT MODE)

#### 12.1.3.1 PWM PERIODS

The period of the PWM1 output is determined by Timer1 and its period register (PR1). The period of the PWM2 output can be software configured to use either Timer1 or Timer2 as the time-base. When TM2PW2 bit (PW2DCL<5>) is clear, the time-base is determined by TMR1 and PR1. When TM2PW2 is set, the time-base is determined by Timer2 and PR2.

Running two different PWM outputs on two different timers allows different PWM periods. Running both PWMs from Timer1 allows the best use of resources by freeing Timer2 to operate as an 8-bit timer. Timer1 and Timer2 can not be used as a 16-bit timer if either PWM is being used.

The PWM periods can be calculated as follows:

period of PWM1 =[(PR1) + 1] x 4Tosc

period of PWM2 =[(PR1) + 1] x 4Tosc or [(PR2) + 1] x 4Tosc

The duty cycle of PWMx is determined by the 10-bit value DCx<9:0>. The upper 8-bits are from register PWxDCH and the lower 2-bits are from PWxDCL<7:6> (PWxDCH:PWxDCL<7:6>). Table 12-3 shows the maximum PWM frequency (FPWM) given the value in the period register.

The number of bits of resolution that the PWM can achieve depends on the operation frequency of the device as well as the PWM frequency (FPWM).

Maximum PWM resolution (bits) for a given PWM frequency:

$$= \frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log\left(2\right)} \quad \text{bits}$$

The PWMx duty cycle is as follows:

PWMx Duty Cycle =  $(DCx) \times TOSC$

where DCx represents the 10-bit value from PWxDCH:PWxDCL.

If DCx = 0, then the duty cycle is zero. If PRx = PWxDCH, then the PWM output will be low for one to four Q-clock (depending on the state of the PWxDCL<7:6> bits). For a Duty Cycle to be 100%, the PWxDCH value must be greater then the PRx value.

The duty cycle registers for both PWM outputs are double buffered. When the user writes to these registers, they are stored in master latches. When TMR1 (or TMR2) overflows and a new PWM period begins, the master latch values are transferred to the slave latches and the PWMx pin is forced high.

| Note: | For PW1DCH, PW1DCL, PW2DCH and                |

|-------|-----------------------------------------------|

|       | PW2DCL registers, a write operation           |

|       | writes to the "master latches" while a read   |

|       | operation reads the "slave latches". As a     |

|       | result, the user may not read back what       |

|       | was just written to the duty cycle registers. |

The user should also avoid any "read-modify-write" operations on the duty cycle registers, such as: ADDWF PW1DCH. This may cause duty cycle outputs that are unpredictable.

| TABLE 12-3: | PWM FREQUENCY vs.           |

|-------------|-----------------------------|

|             | <b>RESOLUTION AT 25 MHz</b> |

| PWM                    | Frequency (kHz) |       |         |       |       |  |  |  |  |

|------------------------|-----------------|-------|---------|-------|-------|--|--|--|--|

| Frequency              | 24.4            | 48.8  | 65.104  | 97.66 | 390.6 |  |  |  |  |

| PRx Value              | 0xFF            | 0x7F  | 0x5F    | 0x3F  | 0x0F  |  |  |  |  |

| High<br>Resolution     | 10-bit          | 9-bit | 8.5-bit | 8-bit | 6-bit |  |  |  |  |

| Standard<br>Resolution | 8-bit           | 7-bit | 6.5-bit | 6-bit | 4-bit |  |  |  |  |

#### 12.1.3.2 PWM INTERRUPTS

The PWM module makes use of TMR1 or TMR2 interrupts. A timer interrupt is generated when TMR1 or TMR2 equals its period register and is cleared to zero. This interrupt also marks the beginning of a PWM cycle. The user can write new duty cycle values before the timer roll-over. The TMR1 interrupt is latched into the TMR1IF bit and the TMR2 interrupt is latched into the TMR2IF bit. These flags must be cleared in software.

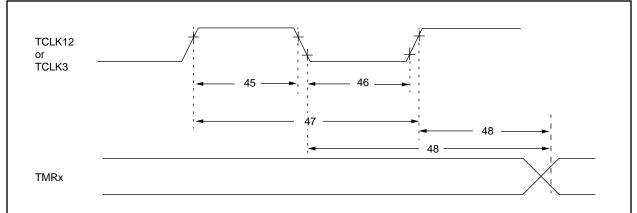

#### 12.1.3.3 EXTERNAL CLOCK SOURCE

The PWMs will operate regardless of the clock source of the timer. The use of an external clock has ramifications that must be understood. Because the external TCLK12 input is synchronized internally (sampled once per instruction cycle), the time TCLK12 changes to the time the timer increments will vary by as much as TCY (one instruction cycle). This will cause jitter in the duty cycle as well as the period of the PWM output.

This jitter will be  $\pm$ TCY, unless the external clock is synchronized with the processor clock. Use of one of the PWM outputs as the clock source to the TCLKx input, will supply a synchronized clock.

In general, when using an external clock source for PWM, its frequency should be much less than the device frequency (Fosc).

#### 12.1.3.3.1 MAX RESOLUTION/FREQUENCY FOR EXTERNAL CLOCK INPUT

The use of an external clock for the PWM time-base (Timer1 or Timer2) limits the PWM output to a maximum resolution of 8-bits. The PWxDCL<7:6> bits must be kept cleared. Use of any other value will distort the PWM output. All resolutions are supported when internal clock mode is selected. The maximum attainable frequency is also lower. This is a result of the timing requirements of an external clock input for a timer (see the Electrical Specification section). The maximum PWM frequency, when the timers clock source is the RB4/TCLK12 pin, is shown in Table 12-3 (standard resolution mode).

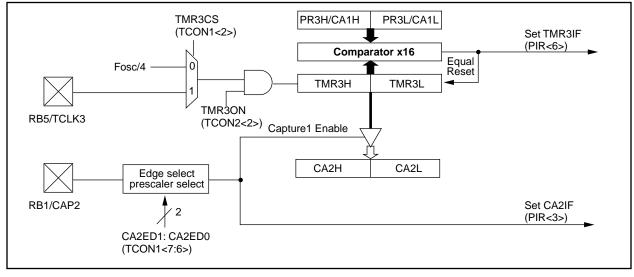

#### 12.2 <u>Timer3</u>

Timer3 is a 16-bit timer consisting of the TMR3H and TMR3L registers. TMR3H is the high byte of the timer and TMR3L is the low byte. This timer has an associated 16-bit period register (PR3H/CA1H:PR3L/CA1L). This period register can be software configured to be a second 16-bit capture register.

When the TMR3CS bit (TCON1<2>) is clear, the timer increments every instruction cycle (Fosc/4). When TMR3CS is set, the timer increments on every falling edge of the RB5/TCLK3 pin. In either mode, the TMR3ON bit must be set for the timer to increment. When TMR3ON is clear, the timer will not increment or set the TMR3IF bit.

Timer3 has two modes of operation, depending on the CA1/PR3 bit (TCON2<3>). These modes are:

- · One capture and one period register mode

- Dual capture register mode

The PIC17C4X has up to two 16-bit capture registers that capture the 16-bit value of TMR3 when events are detected on capture pins. There are two capture pins (RB0/CAP1 and RB1/CAP2), one for each capture register. The capture pins are multiplexed with PORTB pins. An event can be:

- · a rising edge

- a falling edge

- every 4th rising edge

- every 16th rising edge

Each 16-bit capture register has an interrupt flag associated with it. The flag is set when a capture is made. The capture module is truly part of the Timer3 block. Figure 12-7 and Figure 12-8 show the block diagrams for the two modes of operation.

| Address       | Name   | Bit 7      | Bit 6  | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|--------|--------|--------|---------|--------|--------|--------|-------------------------------|--------------------------------------------|

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0 | CA1ED1 | CA1ED0 | T16     | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF | PWM2ON | PWM10N | CA1/PR3 | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                                  |

| 10h, Bank 2   | TMR1   | Timer1 reg | ister  |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                                  |

| 11h, Bank 2   | TMR2   | Timer2 reg | ister  |        |        |         |        |        |        | XXXX XXXX                     | uuuu uuuu                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF | TMR2IF | TMR1IF | CA2IF   | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE | TMR2IE | TMR1IE | CA2IE   | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                                  |

| 07h, Unbanked | INTSTA | PEIF       | T0CKIF | T0IF   | INTF   | PEIE    | TOCKIE | TOIE   | INTE   | 0000 0000                     | 0000 0000                                  |

| 06h, Unbanked | CPUSTA | —          | _      | STKAV  | GLINTD | TO      | PD     | —      | _      | 11 11                         | 11 qq                                      |

| 10h, Bank 3   | PW1DCL | DC1        | DC0    | —      | —      | —       |        |        | _      | xx                            | uu                                         |

| 11h, Bank 3   | PW2DCL | DC1        | DC0    | TM2PW2 | _      | —       |        |        | _      | xx0                           | uu0                                        |

| 12h, Bank 3   | PW1DCH | DC9        | DC8    | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                                  |

| 13h, Bank 3   | PW2DCH | DC9        | DC8    | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | XXXX XXXX                     | uuuu uuuu                                  |

#### TABLE 12-4: REGISTERS/BITS ASSOCIATED WITH PWM

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on conditions, shaded cells are not used by PWM.

#### 12.2.1 ONE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 12-7. The timer increments until it equals the period register and then resets to 0000h. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

This mode is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode, and the corresponding Interrupt bit CA1IF is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h.

Capture2 is active in this mode. The CA2ED1 and CA2ED0 bits determine the event on which capture will occur. The possible events are:

- · Capture on every falling edge

- Capture on every rising edge

- · Capture every 4th rising edge

- · Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CA2IF bit. This interrupt can be enabled by setting the corresponding mask bit CA2IE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CA2IF interrupt flag bit must be cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip reset. Capture pin RB1/CAP2 is a multiplexed pin. When used as a port pin, Capture2 is not disabled. However, the user can simply disable the Capture2 interrupt by clearing CA2IE. If RB1/CAP2 is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt.

The input on capture pin RB1/CAP2 is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the Timer3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 12-1.

#### EXAMPLE 12-1: SEQUENCE TO READ CAPTURE REGISTERS

| MOVLB 3              | ;Select Bank 3          |

|----------------------|-------------------------|

| MOVPF CA2L,LO_BYTE   | ;Read Capture2 low      |

|                      | ;byte, store in LO_BYTE |

| MOVPF CA2H, HI_BYTE  | ;Read Capture2 high     |

|                      | ;byte, store in HI_BYTE |

| MOVPF TCON2,STAT_VAL | ;Read TCON2 into file   |

|                      | ;STAT_VAL               |

#### FIGURE 12-7: TIMER3 WITH ONE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

# PIC17C4X

| ADDLW                    | ADD Lite            | ADD Literal to WREG  |                         |                  |  |  |  |  |  |

|--------------------------|---------------------|----------------------|-------------------------|------------------|--|--|--|--|--|

| Syntax:                  | [label] A           | DLW                  | k                       |                  |  |  |  |  |  |

| Operands:                | $0 \le k \le 25$    | $0 \le k \le 255$    |                         |                  |  |  |  |  |  |

| Operation:               | (WREG) -            | + k $\rightarrow$ (V | VREG)                   |                  |  |  |  |  |  |

| Status Affected:         | OV, C, DC           | C, Z                 |                         |                  |  |  |  |  |  |

| Encoding:                | 1011                | 0001                 | kkkk                    | kkkk             |  |  |  |  |  |

| Description:             |                     |                      | ded to the<br>placed in |                  |  |  |  |  |  |

| Words:                   | 1                   |                      |                         |                  |  |  |  |  |  |

| Cycles:                  | 1                   |                      |                         |                  |  |  |  |  |  |

| Q Cycle Activity:        |                     |                      |                         |                  |  |  |  |  |  |

| Q1                       | Q2                  | Q3                   | 3                       | Q4               |  |  |  |  |  |

| Decode                   | Read<br>literal 'k' | Execu                |                         | Vrite to<br>WREG |  |  |  |  |  |

| Example: ADDLW 0x15      |                     |                      |                         |                  |  |  |  |  |  |

| Before Instruc<br>WREG = |                     |                      |                         |                  |  |  |  |  |  |

| ADDWF                         | ADD WRE                                                                                                                    | EG to f                                                           |       |                       |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|-----------------------|--|--|--|--|--|

| Syntax:                       | [ <i>label</i> ] A[                                                                                                        | DDWF 1                                                            | f,d   |                       |  |  |  |  |  |

| Operands:                     | $0 \le f \le 255$ $d \in [0,1]$                                                                                            | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |       |                       |  |  |  |  |  |

| Operation:                    | (WREG) +                                                                                                                   | - (f) $\rightarrow$ (de                                           | est)  |                       |  |  |  |  |  |

| Status Affected:              | OV, C, DC                                                                                                                  | OV, C, DC, Z                                                      |       |                       |  |  |  |  |  |

| Encoding:                     | 0000                                                                                                                       | 111d                                                              | ffff  | ffff                  |  |  |  |  |  |

| Description:                  | Add WREG to register 'f'. If 'd' is 0 the result is stored in WREG. If 'd' is 1 the result is stored back in register 'f'. |                                                                   |       |                       |  |  |  |  |  |

| Words:                        | 1                                                                                                                          |                                                                   |       |                       |  |  |  |  |  |

| Cycles:                       | 1                                                                                                                          |                                                                   |       |                       |  |  |  |  |  |

| Q Cycle Activity:             |                                                                                                                            |                                                                   |       |                       |  |  |  |  |  |

| Q1                            | Q2                                                                                                                         | Q3                                                                |       | Q4                    |  |  |  |  |  |

| Decode                        | Read<br>register 'f'                                                                                                       | Execute                                                           | ·   · | /rite to<br>stination |  |  |  |  |  |

| Example:                      | ADDWF                                                                                                                      | REG, 0                                                            |       |                       |  |  |  |  |  |

| Before Instru<br>WREG<br>REG  | iction<br>= 0x17<br>= 0xC2                                                                                                 |                                                                   |       |                       |  |  |  |  |  |

| After Instruct<br>WREG<br>REG | tion<br>= 0xD9<br>= 0xC2                                                                                                   |                                                                   |       |                       |  |  |  |  |  |

After Instruction WREG = 0x25

| MULLW                                                     | Multiply I                                                                                                                         | _iteral with V                                                                           | VREG                                                                                                                                                                                                                                                                                                   | MULWF                                         | Multiply V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VREG with                    | f                                                                                                                                                                                                                       |  |                                                                                                                                                                                                                                                                          |  |                                                                                                                               |  |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:                                                   | [ label ]                                                                                                                          | MULLW k                                                                                  |                                                                                                                                                                                                                                                                                                        | Syntax:                                       | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | MULWF f                      |                                                                                                                                                                                                                         |  |                                                                                                                                                                                                                                                                          |  |                                                                                                                               |  |

| Operands:                                                 | $0 \le k \le 25$                                                                                                                   | 5                                                                                        |                                                                                                                                                                                                                                                                                                        | Operands:                                     | $0 \le f \le 25$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5                            |                                                                                                                                                                                                                         |  |                                                                                                                                                                                                                                                                          |  |                                                                                                                               |  |

| Operation:                                                | (k x WRE                                                                                                                           | G) $\rightarrow$ PRODI                                                                   | H:PRODL                                                                                                                                                                                                                                                                                                | Operation:                                    | (WREG x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $(WREG x f) \to PRODH:PRODL$ |                                                                                                                                                                                                                         |  |                                                                                                                                                                                                                                                                          |  |                                                                                                                               |  |

| Status Affected:                                          | None                                                                                                                               |                                                                                          |                                                                                                                                                                                                                                                                                                        | Status Affected                               | Status Affected: None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                              |                                                                                                                                                                                                                         |  |                                                                                                                                                                                                                                                                          |  |                                                                                                                               |  |

| Encoding:                                                 | 1011                                                                                                                               | 1100 kk                                                                                  | kk kkkk                                                                                                                                                                                                                                                                                                | Encoding:                                     | 0011                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0100 ff                      | Ef ffff                                                                                                                                                                                                                 |  |                                                                                                                                                                                                                                                                          |  |                                                                                                                               |  |

| Description:                                              | out betwee<br>and the 8-b<br>result is pla<br>register pai<br>high byte.<br>WREG is u<br>None of the<br>Note that n<br>is possible | bit literal 'k'. The<br>aced in PRODI<br>ir. PRODH con<br>Inchanged.<br>e status flags a | tents of WREGout between the content'. The 16-bitand the register file locaCODH:PRODL16-bit result is stored inI contains thePRODH:PRODL registerI.Both WREG and 'f' areags are affected.None of the status flagsrflow nor carryNote that neither overfloeeration. A zerois possible in this operation |                                               | Description:       An unsigned multiplication out between the contents or and the register file location 16-bit result is stored in the PRODH: PRODL register properties of the status flags and Note that neither overflow is possible in this operation result is possible but not different to the status flags and the status flag |                              | and the register file loca<br>16-bit result is stored in<br>PRODH:PRODL registe<br>PRODH contains the hi<br>Both WREG and 'f' are<br>None of the status flags<br>Note that neither overflo<br>is possible in this opera |  | out between the contents<br>and the register file location<br>16-bit result is stored in the<br>PRODH:PRODL register<br>PRODH contains the high<br>Both WREG and 'f' are un<br>None of the status flags a<br>Note that neither overflow<br>is possible in this operation |  | tts of WREG<br>ation 'f'. The<br>the<br>er pair.<br>gh byte.<br>unchanged.<br>s are affected.<br>ow nor carry<br>tion. A zero |  |

| Words:                                                    | 1                                                                                                                                  |                                                                                          |                                                                                                                                                                                                                                                                                                        | Words:                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |                                                                                                                                                                                                                         |  |                                                                                                                                                                                                                                                                          |  |                                                                                                                               |  |

| Cycles:                                                   | 1                                                                                                                                  |                                                                                          |                                                                                                                                                                                                                                                                                                        | Cycles:                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                              |                                                                                                                                                                                                                         |  |                                                                                                                                                                                                                                                                          |  |                                                                                                                               |  |