Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| PetailsProduct StatusActiveCore ProcessorPICCore Size8-BitSpeed25MHzConnectivityUART/USARTPeripheralsPOR, PWM, WDTNumber of I/O33Program Memory Size16KB (8K x 16)Program Memory TypeOTPEEPROM Size-RAM Size454 x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 6VData Converters-Oscillator TypeExternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeThrough HolePackage / Case40-DIP (0.600", 15.24mm)Purchase URLhttps://www.e-xfl.com/product-detail/microchip-technology/pic17c44-25i-p                                                                                                                                                                                                                                                         |                            |                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------|

| Core Processor         PIC           Core Size         8-Bit           Speed         25MHz           Connectivity         UART/USART           Peripherals         POR, PWM, WDT           Number of I/O         33           Program Memory Size         16KB (8K x 16)           Program Memory Type         OTP           EEPROM Size         -           RAM Size         454 x 8           Voltage - Supply (Vcc/Vdd)         4.5V ~ 6V           Data Converters         -           Oscillator Type         External           Operating Temperature         -40°C ~ 85°C (TA)           Mounting Type         Through Hole           Package / Case         40-DIP (0.600", 15.24mm)           Supplier Device Package         40-PDIP | Details                    |                                                                          |

| Core Size         8-Bit           Speed         25MHz           Connectivity         UART/USART           Peripherals         POR, PWM, WDT           Number of I/O         33           Program Memory Size         16KB (8K x 16)           Program Memory Type         OTP           EEPROM Size         -           RAM Size         454 x 8           Voltage - Supply (Vcc/Vdd)         4.5V ~ 6V           Data Converters         -           Oscillator Type         External           Operating Temperature         -40°C ~ 85°C (TA)           Mounting Type         Through Hole           Package / Case         40-DIP (0.600", 15.24mm)           Supplier Device Package         40-PDIP                                      | Product Status             | Active                                                                   |

| Speed 25MHz Connectivity UART/USART Peripherals POR, PWM, WDT Number of I/O 33 Program Memory Size 16KB (8K x 16) Program Memory Type OTP EEPROM Size - RAM Size 454 x 8 Voltage - Supply (Vcc/Vdd) 4.5V ~ 6V Data Converters - Oscillator Type External Operating Temperature -40°C ~ 85°C (TA) Mounting Type Through Hole Package / Case 40-DIP (0.600", 15.24mm) Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                            | Core Processor             | PIC                                                                      |

| Connectivity UART/USART  Peripherals POR, PWM, WDT  Number of I/O 33  Program Memory Size 16KB (8K x 16)  Program Memory Type OTP  EEPROM Size - RAM Size 454 x 8  Voltage - Supply (Vcc/Vdd) 4.5V ~ 6V  Data Converters - Oscillator Type External  Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                             | Core Size                  | 8-Bit                                                                    |

| Peripherals POR, PWM, WDT  Number of I/O 33  Program Memory Size 16KB (8K x 16)  Program Memory Type OTP  EEPROM Size - RAM Size 454 x 8  Voltage - Supply (Vcc/Vdd) 4.5V ~ 6V  Data Converters - Oscillator Type External  Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                      | Speed                      | 25MHz                                                                    |

| Number of I/O 33 Program Memory Size 16KB (8K x 16) Program Memory Type OTP  EEPROM Size - RAM Size 454 x 8 Voltage - Supply (Vcc/Vdd) 4.5V ~ 6V Data Converters - Coscillator Type External Operating Temperature -40°C ~ 85°C (TA) Mounting Type Through Hole Package / Case 40-DIP (0.600", 15.24mm) Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                        | Connectivity               | UART/USART                                                               |

| Program Memory Size 16KB (8K x 16)  Program Memory Type OTP  EEPROM Size -  RAM Size 454 x 8  Voltage - Supply (Vcc/Vdd) 4.5V ~ 6V  Data Converters -  Oscillator Type External  Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                 | Peripherals                | POR, PWM, WDT                                                            |

| Program Memory Type OTP  EEPROM Size -  RAM Size 454 x 8  Voltage - Supply (Vcc/Vdd) 4.5V ~ 6V  Data Converters -  Oscillator Type External  Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Number of I/O              | 33                                                                       |

| EEPROM Size                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Program Memory Size        | 16KB (8K x 16)                                                           |

| RAM Size 454 x 8  Voltage - Supply (Vcc/Vdd) 4.5V ~ 6V  Data Converters - Oscillator Type External  Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Program Memory Type        | OTP                                                                      |

| Voltage - Supply (Vcc/Vdd) 4.5V ~ 6V  Data Converters - Oscillator Type External Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EEPROM Size                | -                                                                        |

| Data Converters -  Oscillator Type External  Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RAM Size                   | 454 x 8                                                                  |

| Oscillator Type External  Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Operating Temperature -40°C ~ 85°C (TA)  Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Data Converters            | -                                                                        |

| Mounting Type Through Hole  Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Oscillator Type            | External                                                                 |

| Package / Case 40-DIP (0.600", 15.24mm)  Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Supplier Device Package 40-PDIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Mounting Type              | Through Hole                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic17c44-25i-p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Supplier Device Package    | 40-PDIP                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44-25i-p |

### 1.0 OVERVIEW

This data sheet covers the PIC17C4X group of the PIC17CXX family of microcontrollers. The following devices are discussed in this data sheet:

- PIC17C42

- PIC17CR42

- PIC17C42A

- PIC17C43

- PIC17CR43

- PIC17C44

The PIC17CR42, PIC17C42A, PIC17C43, PIC17CR43, and PIC17C44 devices include architectural enhancements over the PIC17C42. These enhancements will be discussed throughout this data sheet.

The PIC17C4X devices are 40/44-Pin, EPROM/ROM-based members of the versatile PIC17CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC17CXX has enhanced core features, 16-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 16-bit wide instruction word with a separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 55 instructions (reduced instruction set) are available in the PIC17C42 and 58 instructions in all the other devices. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance. For mathematical intensive applications all devices, except the PIC17C42, have a single cycle 8 x 8 Hardware Multiplier.

PIC17CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC17C4X devices have up to 454 bytes of RAM and 33 I/O pins. In addition, the PIC17C4X adds several peripheral features useful in many high performance applications including:

- · Four timer/counters

- · Two capture inputs

- Two PWM outputs

- A Universal Synchronous Asynchronous Receiver Transmitter (USART)

These special features reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LF oscillator is for low frequency crystals and minimizes power consumption, XT is a standard crystal, and the EC is for external clock input. The SLEEP (power-down) mode offers additional

power saving. The user can wake-up the chip from SLEEP through several external and internal interrupts and device resets.

There are four configuration options for the device operational modes:

- Microprocessor

- Microcontroller

- · Extended microcontroller

- Protected microcontroller

The microprocessor and extended microcontroller modes allow up to 64K-words of external program memory.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software malfunction.

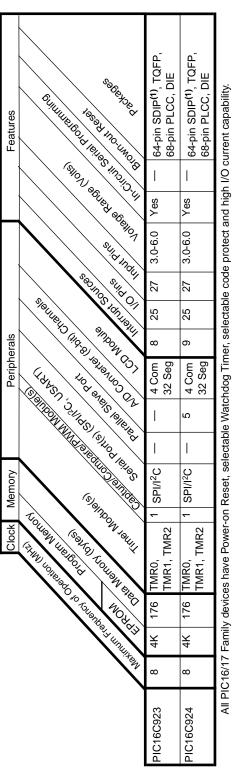

Table 1-1 lists the features of the PIC17C4X devices.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

The PIC17C4X fits perfectly in applications ranging from precise motor control and industrial process control to automotive, instrumentation, and telecom applications. Other applications that require extremely fast execution of complex software programs or the flexibility of programming the software code as one of the last steps of the manufacturing process would also be well suited. The EPROM technology makes customization of application programs (with unique security codes, combinations, model numbers, parameter storage, etc.) fast and convenient. Small footprint package options make the PIC17C4X ideal for applications with space limitations that require high performance. High speed execution, powerful peripheral features, flexible I/O, and low power consumption all at low cost make the PIC17C4X ideal for a wide range of embedded control applications.

### 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X and PIC16CXX families of microcontrollers will see the architectural enhancements that have been implemented. These enhancements allow the device to be more efficient in software and hardware requirements. Please refer to Appendix A for a detailed list of enhancements and modifications. Code written for PIC16C5X or PIC16CXX can be easily ported to PIC17CXX family of devices (Appendix B).

### 1.2 <u>Development Support</u>

The PIC17CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a universal programmer, a "C" compiler, and fuzzy logic support tools.

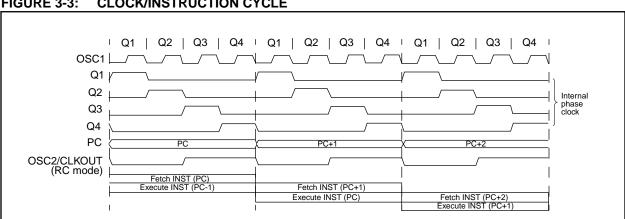

#### **Clocking Scheme/Instruction Cycle** 3.1

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-3.

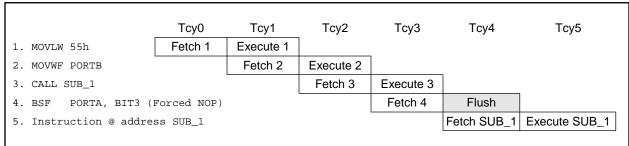

#### 3.2 **Instruction Flow/Pipelining**

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g. GOTO) then two cycles are required to complete the instruction (Example 3-2).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### **EXAMPLE 3-2: INSTRUCTION PIPELINE FLOW**

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

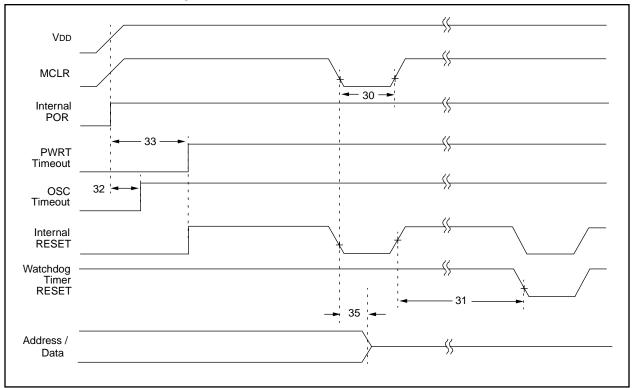

#### RESET 4.0

The PIC17CXX differentiates between various kinds of

- Power-on Reset (POR)

- MCLR reset during normal operation

- WDT Reset (normal operation)

Some registers are not affected in any reset condition: their status is unknown on POR and unchanged in any other reset. Most other registers are forced to a "reset state" on Power-on Reset (POR), on MCLR or WDT Reset and on MCLR reset during SLEEP. They are not affected by a WDT Reset during SLEEP, since this reset is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of reset. See Table 4-4 for a full description of reset states of all registers.

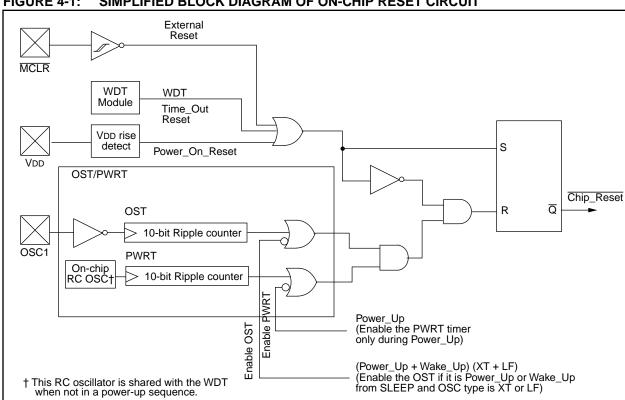

Note: While the device is in a reset state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

A simplified block diagram of the on-chip reset circuit is shown in Figure 4-1.

#### 4.1 Power-on Reset (POR), Power-up Timer (PWRT), and Oscillator Start-up Timer (OST)

#### 4.1.1 POWER-ON RESET (POR)

The Power-on Reset circuit holds the device in reset until VDD is above the trip point (in the range of 1.4V -2.3V). The PIC17C42 does not produce an internal reset when VDD declines. All other devices will produce an internal reset for both rising and falling VDD. To take advantage of the POR, just tie the MCLR/VPP pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD is required. See Electrical Specifications for details.

#### 4.1.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 96 ms time-out (nominal) on power-up. This occurs from rising edge of the POR signal and after the first rising edge of MCLR (detected high). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. In most cases the PWRT delay allows the VDD to rise to an acceptable level.

The power-up time delay will vary from chip to chip and to VDD and temperature. See DC parameters for details.

SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT FIGURE 4-1:

## 5.2 <u>Peripheral Interrupt Enable Register</u> (PIE)

This register contains the individual flag bits for the Peripheral interrupts.

## FIGURE 5-3: PIE REGISTER (ADDRESS: 17h, BANK 1)

| RBIE<br>bit7 | TMR3IE TMR2IE TMR1IE  CA2IE   CA1IE   TXIE   R                                                                                           | bit0 W | = Readable bit  = Writable bit = Value at POR reset |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------|

| bit 7:       | RBIE: PORTB Interrupt on Change Enable bit  1 = Enable PORTB interrupt on change  0 = Disable PORTB interrupt on change                  |        |                                                     |

| bit 6:       | TMR3IE: Timer3 Interrupt Enable bit 1 = Enable Timer3 interrupt 0 = Disable Timer3 interrupt                                             |        |                                                     |

| bit 5:       | TMR2IE: Timer2 Interrupt Enable bit 1 = Enable Timer2 interrupt 0 = Disable Timer2 interrupt                                             |        |                                                     |

| bit 4:       | TMR1IE: Timer1 Interrupt Enable bit 1 = Enable Timer1 interrupt 0 = Disable Timer1 interrupt                                             |        |                                                     |

| bit 3:       | CA2IE: Capture2 Interrupt Enable bit  1 = Enable Capture interrupt on RB1/CAP2 pin  0 = Disable Capture interrupt on RB1/CAP2 pin        |        |                                                     |

| bit 2:       | CA1IE: Capture1 Interrupt Enable bit 1 = Enable Capture interrupt on RB2/CAP1 pin 0 = Disable Capture interrupt on RB2/CAP1 pin          |        |                                                     |

| bit 1:       | <b>TXIE</b> : USART Transmit Interrupt Enable bit 1 = Enable Transmit buffer empty interrupt 0 = Disable Transmit buffer empty interrupt |        |                                                     |

| bit 0:       | RCIE: USART Receive Interrupt Enable bit  1 = Enable Receive buffer full interrupt  0 = Disable Receive buffer full interrupt            |        |                                                     |

**TABLE 6-3: SPECIAL FUNCTION REGISTERS**

| Address            | Name    | Bit 7        | Bit 6                                     | Bit 5        | Bit 4        | Bit 3         | Bit 2         | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------|--------------|-------------------------------------------|--------------|--------------|---------------|---------------|-------------|-------------|-------------------------------|-------------------------------------|

| Unbanke            | ed      | •            |                                           |              |              |               |               | •           |             |                               | •                                   |

| 00h                | INDF0   | Uses con     | tents of FSI                              | R0 to addres | ss data mem  | ory (not a p  | hysical regis | ster)       |             |                               |                                     |

| 01h                | FSR0    | Indirect da  | ata memory                                | address po   | ointer 0     |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 02h                | PCL     | Low order    | r 8-bits of P                             | С            |              |               |               |             |             | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH  | Holding re   | egister for u                             | pper 8-bits  | of PC        |               |               |             |             | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA  | FS3          | FS2                                       | FS1          | FS0          | OV            | Z             | DC          | С           | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA   | INTEDG       | T0SE                                      | T0CS         | PS3          | PS2           | PS1           | PS0         | _           | 0000 000-                     | 0000 000-                           |

| 06h <sup>(2)</sup> | CPUSTA  | _            | _                                         | STKAV        | GLINTD       | TO            | PD            | _           | _           | 11 11                         | 11 qq                               |

| 07h                | INTSTA  | PEIF         | T0CKIF                                    | T0IF         | INTF         | PEIE          | T0CKIE        | TOIE        | INTE        | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1   | Uses con     | tents of FSI                              | R1 to addres | ss data mem  | lory (not a p | hysical regis | ster)       |             |                               |                                     |

| 09h                | FSR1    | Indirect da  | ata memory                                | address po   | ointer 1     |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG    | Working r    | egister                                   |              |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L   | TMR0 reg     | gister; low b                             | yte          |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H   | TMR0 reg     | jister; high l                            | oyte         |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 0Dh                | TBLPTRL | Low byte     |                                           |              |              |               |               |             |             |                               | (4)                                 |

| 0Eh                | TBLPTRH | High byte    | High byte of program memory table pointer |              |              |               |               |             |             |                               | (4)                                 |

| 0Fh                | BSR     | Bank sele    | ct register                               |              |              |               |               |             |             | 0000 0000                     | 0000 0000                           |

| Bank 0             |         | •            |                                           |              |              |               |               |             |             |                               | •                                   |

| 10h                | PORTA   | RBPU         | _                                         | RA5          | RA4          | RA3           | RA2           | RA1/T0CKI   | RA0/INT     | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB    | Data dired   | ction registe                             | er for PORTE | 3            |               |               |             |             | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB   | PORTB d      | ata latch                                 |              |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA   | SPEN         | RX9                                       | SREN         | CREN         | _             | FERR          | OERR        | RX9D        | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG   | Serial por   | t receive re                              | gister       |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA   | CSRC         | TX9                                       | TXEN         | SYNC         | _             | _             | TRMT        | TX9D        | 00001x                        | 00001u                              |

| 16h                | TXREG   | Serial por   | t transmit re                             | egister      |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG   | Baud rate    | generator                                 | register     |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |         | •            |                                           |              |              |               |               |             |             |                               | •                                   |

| 10h                | DDRC    | Data direc   | ction registe                             | er for PORT  | C            |               |               |             |             | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC   | RC7/<br>AD7  | RC6/<br>AD6                               | RC5/<br>AD5  | RC4/<br>AD4  | RC3/<br>AD3   | RC2/<br>AD2   | RC1/<br>AD1 | RC0/<br>AD0 | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD    | Data dired   | Data direction register for PORTD         |              |              |               |               |             |             | 1111 1111                     | 1111 1111                           |

| 13h                | PORTD   | RD7/<br>AD15 | RD6/<br>AD14                              | RD5/<br>AD13 | RD4/<br>AD12 | RD3/<br>AD11  | RD2/<br>AD10  | RD1/<br>AD9 | RD0/<br>AD8 | xxxx xxxx                     | uuuu uuuu                           |

| 14h                | DDRE    | Data dired   | ction registe                             | er for PORTE | <u> </u>     | 1             | •             |             | •           | 111                           | 111                                 |

| 15h                | PORTE   | _            | _                                         | _            | _            | _             | RE2/WR        | RE1/OE      | RE0/ALE     | xxx                           | uuu                                 |

| 16h                | PIR     | RBIF         | TMR3IF                                    | TMR2IF       | TMR1IF       | CA2IF         | CA1IF         | TXIF        | RCIF        | 0000 0010                     | 0000 0010                           |

| 17h                | PIE     | RBIE         | TMR3IE                                    | TMR2IE       | TMR1IE       | CA2IE         | CA1IE         | TXIE        | RCIE        | 0000 0000                     | 0000 0000                           |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1: from or transferred to the upper byte of the program counter. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  status bits in CPUSTA are not affected by a MCLR reset.

Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. The following values are for both TBLPTRL and TBLPTRH:

All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000)

except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

The PRODL and PRODH registers are not implemented on the PIC17C42.

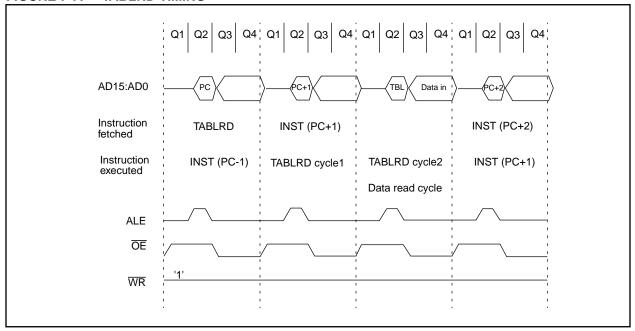

### 7.3 Table Reads

The table read allows the program memory to be read. This allows constant data to be stored in the program memory space, and retrieved into data memory when needed. Example 7-2 reads the 16-bit value at program memory address TBLPTR. After the dummy byte has been read from the TABLATH, the TABLATH is loaded with the 16-bit data from program memory address TBLPTR + 1. The first read loads the data into the latch, and can be considered a dummy read (unknown data loaded into 'f'). INDFO should be configured for either auto-increment or auto-decrement.

#### **EXAMPLE 7-2: TABLE READ**

HIGH (TBL\_ADDR) ; Load the Table MOVLW MOVWF TBLPTRH address LOW (TBL\_ADDR) MOVLW MOVWF TBLPTRL TABLRD 0,0,DUMMY ; Dummy read, ; Updates TABLATCH TLRD 1, INDF0 ; Read HI byte of TABLATCH TABLRD 0,1,INDF0 ; Read LO byte of TABLATCH and Update TABLATCH

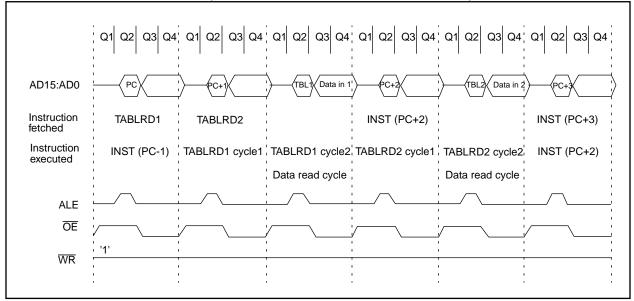

FIGURE 7-7: TABLRD TIMING

FIGURE 7-8: TABLRD TIMING (CONSECUTIVE TABLRD INSTRUCTIONS)

TABLE 13-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Address                                        | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1     | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|--------|--------|--------|-------|-------|-----------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF      | RCIF      | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   | _     | FERR  | OERR      | RX9D      | 0000 -00x                     | 0000 -00u                               |

| 16h, Bank 0                                    | TXREG | TX7   | TX6    | TX5    | TX4    | TX3   | TX2   | TX1       | TX0       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE      | RCIE      | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9    | TXEN   | SYNC   | _     | _     | TRMT      | TX9D      | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |        |        |        |       |       | xxxx xxxx | uuuu uuuu |                               |                                         |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous master transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

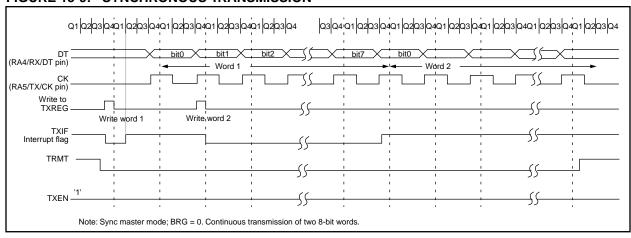

### FIGURE 13-9: SYNCHRONOUS TRANSMISSION

| BTF                 | SS             | Bit Test, s                                                     | Bit Test, skip if Set                                                                                                                                                                                                                                |        |      |  |  |  |  |

|---------------------|----------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|--|--|--|--|

| Synt                | ax:            | [label] B                                                       | TFSS f,b                                                                                                                                                                                                                                             | )      |      |  |  |  |  |

| Ope                 | rands:         | $0 \le f \le 12$                                                | 7                                                                                                                                                                                                                                                    |        |      |  |  |  |  |

|                     |                | $0 \le b < 7$                                                   |                                                                                                                                                                                                                                                      |        |      |  |  |  |  |

| Ope                 | ration:        | skip if (f <b< td=""><td>o&gt;) = 1</td><td></td><td></td></b<> | o>) = 1                                                                                                                                                                                                                                              |        |      |  |  |  |  |

| Stat                | us Affected:   | None                                                            |                                                                                                                                                                                                                                                      |        |      |  |  |  |  |

| Ence                | oding:         | 1001                                                            | 0bbb                                                                                                                                                                                                                                                 | ffff   | ffff |  |  |  |  |

| Des                 | cription:      | instruction If bit 'b' is 1 fetched dur cution, is d            | If bit 'b' in register 'f' is 1 then the next instruction is skipped.  If bit 'b' is 1, then the next instruction fetched during the current instruction execution, is discarded and an NOP is executed instead, making this a two-cycle instruction |        |      |  |  |  |  |

| Wor                 | ds:            | 1                                                               |                                                                                                                                                                                                                                                      |        |      |  |  |  |  |

| Cycl                | es:            | 1(2)                                                            |                                                                                                                                                                                                                                                      |        |      |  |  |  |  |

| Q C                 | ycle Activity: |                                                                 | · /                                                                                                                                                                                                                                                  |        |      |  |  |  |  |

|                     | Q1             | Q2                                                              | Q3                                                                                                                                                                                                                                                   | 1      | Q4   |  |  |  |  |

|                     | Decode         | Read register 'f'                                               | Execu                                                                                                                                                                                                                                                | ute    | NOP  |  |  |  |  |

| If sk               | ip:            |                                                                 | •                                                                                                                                                                                                                                                    | •      |      |  |  |  |  |

|                     | Q1             | Q2                                                              | Q3                                                                                                                                                                                                                                                   | 1      | Q4   |  |  |  |  |

|                     | Forced NOP     | NOP                                                             | Execu                                                                                                                                                                                                                                                | ıte    | NOP  |  |  |  |  |

| <u>Exa</u>          | mple:          | HERE I                                                          |                                                                                                                                                                                                                                                      | FLAG,1 |      |  |  |  |  |

| Before Instruction  |                |                                                                 |                                                                                                                                                                                                                                                      |        |      |  |  |  |  |

| PC = address (HERE) |                |                                                                 |                                                                                                                                                                                                                                                      |        |      |  |  |  |  |

0;

address (FALSE)

address (TRUE)

| BTG   |                         | Bit Toggl                          | e f                                              |       |                    |  |  |  |

|-------|-------------------------|------------------------------------|--------------------------------------------------|-------|--------------------|--|--|--|

| Synt  | ax:                     | [ label ] E                        | BTG f,b                                          |       |                    |  |  |  |

| Ope   | rands:                  | $0 \le f \le 25$ $0 \le b < 7$     | 5                                                |       |                    |  |  |  |

| Ope   | ration:                 | $(\overline{f{<}b{>}})\rightarrow$ | (f <b>)</b>                                      |       |                    |  |  |  |

| Statu | us Affected:            | None                               |                                                  |       |                    |  |  |  |

| Enco  | oding:                  | 0011                               | 1bbb                                             | ffff  | ffff               |  |  |  |

| Desc  | cription:               | Bit 'b' in da inverted.            | Bit 'b' in data memory location 'f' is inverted. |       |                    |  |  |  |

| Word  | ds:                     | 1                                  |                                                  |       |                    |  |  |  |

| Cycle | es:                     | 1                                  |                                                  |       |                    |  |  |  |

| Q Cy  | cle Activity:           |                                    |                                                  |       |                    |  |  |  |

|       | Q1                      | Q2                                 | Q3                                               |       | Q4                 |  |  |  |

|       | Decode                  | Read<br>register 'f'               | Execut                                           | ·   · | Vrite<br>ister 'f' |  |  |  |

| Exar  | nple:                   | BTG                                | PORTC,                                           | 4     |                    |  |  |  |

|       | Before Instru<br>PORTC  |                                    | 0101 <b>[0x7</b> 5                               | 5]    |                    |  |  |  |

|       | After Instruct<br>PORTC | tion:<br>= 0110                    | 0101 <b>[0x6</b> 5                               | 5]    |                    |  |  |  |

|       |                         |                                    |                                                  |       |                    |  |  |  |

After Instruction

If FLAG<1>

PC

If FLAG<1> PC

| RLNCF       |          | Rota                     | te L                                                                                                                                                           | eft f (no                  | carı  | y) |                     |  |  |

|-------------|----------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------|----|---------------------|--|--|

| Syntax:     |          | [ labe                   | e/]                                                                                                                                                            | RLNCF                      | f,d   |    |                     |  |  |

| Operands:   |          |                          | $0 \le f \le 255$<br>$d \in [0,1]$                                                                                                                             |                            |       |    |                     |  |  |

| Operation:  |          | f <n><br/>f&lt;7&gt;</n> |                                                                                                                                                                | <n+1>;<br/>&lt;0&gt;</n+1> |       |    |                     |  |  |

| Status Affe | ected:   | None                     | )                                                                                                                                                              |                            |       |    |                     |  |  |

| Encoding:   |          | 0.0                      | 10                                                                                                                                                             | 001d                       | ff    | ff | ffff                |  |  |

| Description | n:       | one b<br>place           | The contents of register 'f' are rotated one bit to the left. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is stored back in register 'f'. |                            |       |    |                     |  |  |

|             |          |                          | •                                                                                                                                                              | reg                        | ister | f  | ]◀┐                 |  |  |

| Words:      |          | 1                        |                                                                                                                                                                |                            |       |    |                     |  |  |

| Cycles:     |          | 1                        |                                                                                                                                                                |                            |       |    |                     |  |  |

| Q Cycle A   | ctivity: |                          |                                                                                                                                                                |                            |       |    |                     |  |  |

|             | 21       | Q2                       |                                                                                                                                                                | Q3                         |       |    | Q4                  |  |  |

| Dec         | code     | Read<br>registe          | -                                                                                                                                                              | Execu                      | te    |    | rite to<br>tination |  |  |

| Example:    |          | RLNC                     | F                                                                                                                                                              | REC                        | 3, 1  |    |                     |  |  |

| Before      | e Instru | iction                   |                                                                                                                                                                |                            |       |    |                     |  |  |

| C<br>R      | :<br>EG  | = 0<br>= 11              | 10 1                                                                                                                                                           | .011                       |       |    |                     |  |  |

|             | nstruct  | tion                     |                                                                                                                                                                |                            |       |    |                     |  |  |

| C<br>R      | :<br>EG  | =<br>= 11                | 01 (                                                                                                                                                           | )111                       |       |    |                     |  |  |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                                                                                                                                                                                                                                               | RRCF Rotate Right f through Carry |                                                                                                                                               |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| $d \in [0,1]$ Operation: $f < n > \rightarrow d < n - 1 > ;$ $f < 0 > \rightarrow C;$ $C \rightarrow d < 7 >$ Status Affected: $C$ Encoding: $0001  100d  ffff  ffff$ Description: $The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'.  C \qquad \qquad$ | Syntax:                           | [label] RRCF f,d                                                                                                                              |  |  |  |  |  |  |

| $f<0> \rightarrow C; \\ C \rightarrow d<7>$ Status Affected: C Encoding: $0001  100d  ffff  ffff$ Description: The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'.                                                                                                                                                                                                               | Operands:                         |                                                                                                                                               |  |  |  |  |  |  |

| Encoding:  Description:  The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'.  C register f  Words:  1  Cycles:  1  Q Cycle Activity:  Q1  Q2  Q3  Q4  Decode  Read  Read  register 'f'  REG1, 0  Before Instruction  REG1 = 1110 0110  C = 0  After Instruction                                                                                                                  | Operation:                        | $f$ <0> $\rightarrow$ C;                                                                                                                      |  |  |  |  |  |  |

| Description:  The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'.  Cregister f  Words:  1  Cycles:  1  Q Cycle Activity:  Q1  Q2  Q3  Q4  Decode Read Execute Write to destination  Example:  RRCF  REG1, 0  Before Instruction  REG1 = 1110 0110  C = 0  After Instruction                                                                                                      | Status Affected:                  | С                                                                                                                                             |  |  |  |  |  |  |

| one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'.  C register f  Words:  1  Cycles:  1  Q Cycle Activity:  Q1  Q2  Q3  Q4  Decode Read Execute Write to destination  Example:  RRCF  REG1, 0  Before Instruction  REG1 = 1110 0110  C = 0  After Instruction                                                                                                                                                            | Encoding:                         | 0001 100d ffff ffff                                                                                                                           |  |  |  |  |  |  |

| Cycles: 1  Q Cycle Activity:      Q1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description:                      | one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'. |  |  |  |  |  |  |

| Q Cycle Activity:  Q1 Q2 Q3 Q4  Decode Read Execute Write to destination  Example: RRCF REG1, 0  Before Instruction  REG1 = 1110 0110  C = 0  After Instruction                                                                                                                                                                                                                                                                                                                                                     | Words:                            | 1                                                                                                                                             |  |  |  |  |  |  |

| Q Cycle Activity:  Q1 Q2 Q3 Q4  Decode Read Execute Write to destination  Example: RRCF REG1, 0  Before Instruction  REG1 = 1110 0110  C = 0  After Instruction                                                                                                                                                                                                                                                                                                                                                     | Cycles:                           | 1                                                                                                                                             |  |  |  |  |  |  |

| Q1 Q2 Q3 Q4  Decode Read Execute Write to destination  Example: RRCF REG1, 0  Before Instruction REG1 = 1110 0110 C = 0  After Instruction                                                                                                                                                                                                                                                                                                                                                                          | •                                 |                                                                                                                                               |  |  |  |  |  |  |

| register 'f'         destination           Example:         RRCF         REG1,0           Before Instruction         REG1 = 1110 0110         0110           C = 0         After Instruction                                                                                                                                                                                                                                                                                                                        | -                                 | Q2 Q3 Q4                                                                                                                                      |  |  |  |  |  |  |

| Before Instruction  REG1 = 1110 0110  C = 0  After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Decode                            |                                                                                                                                               |  |  |  |  |  |  |

| REG1 = 1110 0110<br>C = 0<br>After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Example:                          | RRCF REG1,0                                                                                                                                   |  |  |  |  |  |  |

| C = 0  After Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Before Instru                     | iction                                                                                                                                        |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • .                               |                                                                                                                                               |  |  |  |  |  |  |

| REG1 = 1110 0110                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | After Instruc                     | ion                                                                                                                                           |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | REG1                              | 1110 0110                                                                                                                                     |  |  |  |  |  |  |

| WREG = 0111 0011<br>C = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |                                                                                                                                               |  |  |  |  |  |  |

| TABLRD            | Table Re    | ead      |           |

|-------------------|-------------|----------|-----------|

| Example1:         | TABLRD      | 1, 1,    | REG ;     |

| Before Instruc    | tion        |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | vrite co | mpletion) |

| REG               |             | =        | 0xAA      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             | =        | 0xA357    |

| MEMORY            | (TBLPTR)    | =        | 0x5678    |

| Example2:         | TABLRD      | 0, 0,    | REG ;     |

| Before Instruc    | tion        |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | vrite co | mpletion) |

| REG               |             | =        | 0x55      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY            | (TBLPTR)    | =        | 0x1234    |

|                   |             |          |           |

| TABLWT           | Table Wri                                                                                                                                                                                                                                                                                                                                                                                                                 | ite    |        |      |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|------|--|--|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                                                                                                                                                                                                 | TABLWT | Γt,i,f |      |  |  |  |

| Operands:        | $0 \le f \le 256$<br>$i \in [0,1]$<br>$t \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                       | 5      |        |      |  |  |  |

| Operation:       | If t = 0,<br>$f \rightarrow TBLATL$ ;<br>If t = 1,<br>$f \rightarrow TBLATH$ ;<br>$TBLAT \rightarrow Prog Mem (TBLPTR)$ ;<br>If i = 1,<br>$TBLPTR + 1 \rightarrow TBLPTR$                                                                                                                                                                                                                                                 |        |        |      |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                                                      |        |        |      |  |  |  |

| Encoding:        | 1010                                                                                                                                                                                                                                                                                                                                                                                                                      | 11ti   | ffff   | ffff |  |  |  |

| Description:     | 1. Load value in 'f' into 16-bit table latch (TBLAT)  If t = 0: load into low byte;  If t = 1: load into high byte  2. The contents of TBLAT is written to the program memory location pointed to by TBLPTR  If TBLPTR points to external program memory location, then the instruction takes two-cycle If TBLPTR points to an internal EPROM location, then the instruction is terminated when an interrupt is received. |        |        |      |  |  |  |

Note: The MCLR/VPP pin must be at the programming voltage for successful programming of internal memory.

If  $\overline{MCLR}/VPP = VDD$

the programming sequence of internal memory will be executed, but will not be successful (although the internal memory location may be disturbed)

The TBLPTR can be automatically incremented

If i = 0; TBLPTR is not incremented

If i = 1; TBLPTR is incremented

Words: 1

Cycles: 2 (many if write is to on-chip EPROM program memory)

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read         | Execute | Write     |

|        | register 'f' |         | register  |

|        |              |         | TBLATH or |

|        |              |         | TBLATL    |

NOTES:

Applicable Devices 42 R42 42A 43 R43 44

#### 17.1 DC CHARACTERISTICS: