Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 33MHz                                                                   |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | <u> </u>                                                                |

| RAM Size                   | 454 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-LCC (J-Lead)                                                         |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44-33-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

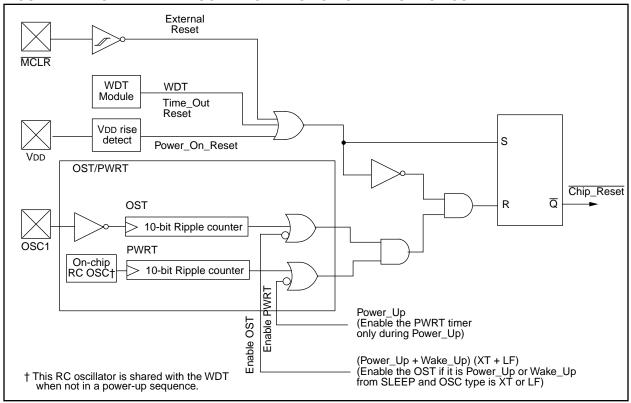

# 4.0 RESET

The PIC17CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- WDT Reset (normal operation)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are forced to a "reset state" on Power-on Reset (POR), on  $\overline{\text{MCLR}}$  or WDT Reset and on  $\overline{\text{MCLR}}$  reset during SLEEP. They are not affected by a WDT Reset during SLEEP, since this reset is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of reset. See Table 4-4 for a full description of reset states of all registers.

**Note:** While the device is in a reset state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

A simplified block diagram of the on-chip reset circuit is shown in Figure 4-1.

### 4.1 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT), and Oscillator Start-up</u> <u>Timer (OST)</u>

### 4.1.1 POWER-ON RESET (POR)

The Power-on Reset circuit holds the device in reset until VDD is above the trip point (in the range of 1.4V -2.3V). The PIC17C42 does not produce an internal reset when VDD declines. All other devices will produce an internal reset for both rising and falling VDD. To take advantage of the POR, just tie the MCLR/VPP pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD is required. See Electrical Specifications for details.

#### 4.1.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 96 ms time-out (nominal) on power-up. This occurs from rising edge of the POR signal and after the first rising edge of  $\overline{\text{MCLR}}$  (detected high). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. In most cases the PWRT delay allows the VDD to rise to an acceptable level.

The power-up time delay will vary from chip to chip and to VDD and temperature. See DC parameters for details.

# FIGURE 4-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 1996 Microchip Technology Inc.

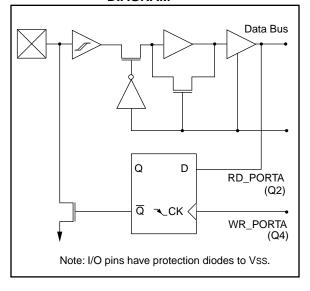

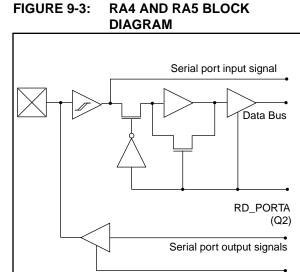

FIGURE 9-2: RA2 AND RA3 BLOCK DIAGRAM

$\overline{OE}$  = SPEN,SYNC,TXEN,  $\overline{CREN}$ ,  $\overline{SREN}$  for RA4  $\overline{OE}$  = SPEN ( $\overline{SYNC}$ +SYNC, $\overline{CSRC}$ ) for RA5

Note: I/O pins have protection diodes to VDD and VSS.

| TABLE 9-1: | PO | RTA FUNCTI | ONS |

|------------|----|------------|-----|

|            |    |            |     |

. . . . .

\_ \_ \_ \_ \_ . . . . . . . . . . . . . .

| Name      | Bit0 | Buffer Type | Function                                                                            |

|-----------|------|-------------|-------------------------------------------------------------------------------------|

| RA0/INT   | bit0 | ST          | Input or external interrupt input.                                                  |

| RA1/T0CKI | bit1 | ST          | Input or clock input to the TMR0 timer/counter, and/or an external interrupt input. |

| RA2       | bit2 | ST          | Input/Output. Output is open drain type.                                            |

| RA3       | bit3 | ST          | Input/Output. Output is open drain type.                                            |

| RA4/RX/DT | bit4 | ST          | Input or USART Asynchronous Receive or USART Synchronous Data.                      |

| RA5/TX/CK | bit5 | ST          | Input or USART Asynchronous Transmit or USART Synchronous Clock.                    |

| RBPU      | bit7 |             | Control bit for PORTB weak pull-ups.                                                |

Legend: ST = Schmitt Trigger input.

### TABLE 9-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address       | Name  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-------|--------|-------|-------|-------|-------|-------|-----------|---------|-------------------------------|-----------------------------------------|

| 10h, Bank 0   | PORTA | RBPU   | _     | RA5   | RA4   | RA3   | RA2   | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                               |

| 05h, Unbanked | TOSTA | INTEDG | T0SE  | TOCS  | PS3   | PS2   | PS1   | PS0       | _       | 0000 000-                     | 0000 000-                               |

| 13h, Bank 0   | RCSTA | SPEN   | RC9   | SREN  | CREN  | —     | FERR  | OERR      | RC9D    | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0   | TXSTA | CSRC   | TX9   | TXEN  | SYNC  | _     | —     | TRMT      | TX9D    | 00001x                        | 0000lu                                  |

Legend: x = unknown, u = unchanged, - = unimplemented reads as '0'. Shaded cells are not used by PORTA. Note 1: Other (non power-up) resets include: external reset through  $\overline{MCLR}$  and the Watchdog Timer Reset.

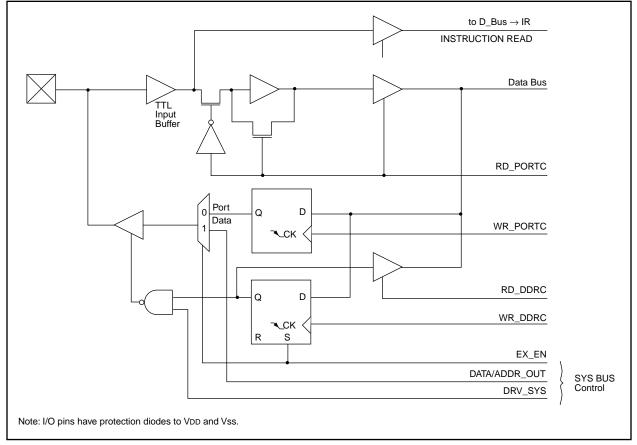

# 9.3 PORTC and DDRC Registers

PORTC is an 8-bit bi-directional port. The corresponding data direction register is DDRC. A '1' in DDRC configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTC reads the status of the pins, whereas writing to it will write to the port latch. PORTC is multiplexed with the system bus. When operating as the system bus, PORTC is the low order byte of the address/data bus (AD7:AD0). The timing for the system bus is shown in the Electrical Characteristics section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-2 shows the instruction sequence to initialize PORTC. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-2: INITIALIZING PORTC

| 1     | ;             | Select Bank 1                                        |

|-------|---------------|------------------------------------------------------|

| PORTC | ;             | Initialize PORTC data                                |

|       | ;             | latches before setting                               |

|       | ;             | the data direction                                   |

|       | ;             | register                                             |

| 0xCF  | ;             | Value used to initialize                             |

|       | ;             | data direction                                       |

| DDRC  | ;             | Set RC<3:0> as inputs                                |

|       | ;             | RC<5:4> as outputs                                   |

|       | ;             | RC<7:6> as inputs                                    |

|       | PORTC<br>0xCF | PORTC ;<br>;<br>;<br>;<br>;<br>0xCF ;<br>DDRC ;<br>; |

### FIGURE 9-6: BLOCK DIAGRAM OF RC<7:0> PORT PINS

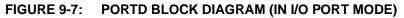

# 9.4 PORTD and DDRD Registers

PORTD is an 8-bit bi-directional port. The corresponding data direction register is DDRD. A '1' in DDRD configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTD reads the status of the pins, whereas writing to it will write to the port latch. PORTD is multiplexed with the system bus. When operating as the system bus, PORTD is the high order byte of the address/data bus (AD15:AD8). The timing for the system bus is shown in the Electrical Characteristics section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-3 shows the instruction sequence to initialize PORTD. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-3: INITIALIZING PORTD

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTD | ; | Initialize PORTD data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0xCF  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRD  | ; | Set RD<3:0> as inputs    |

|       |       | ; | RD<5:4> as outputs       |

|       |       | ; | RD<7:6> as inputs        |

|       |       |   |                          |

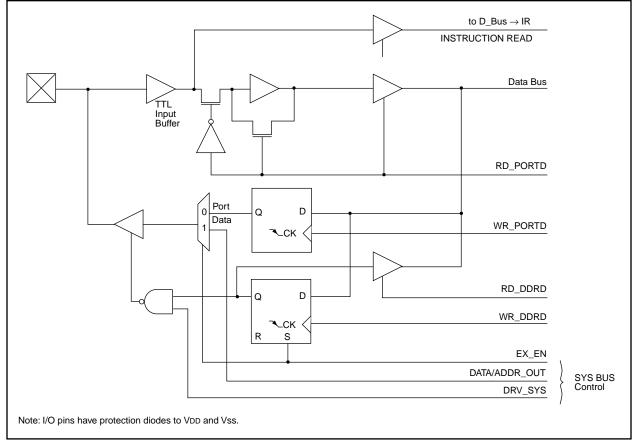

# 12.0 TIMER1, TIMER2, TIMER3, PWMS AND CAPTURES

The PIC17C4X has a wealth of timers and time-based functions to ease the implementation of control applications. These time-base functions include two PWM outputs and two Capture inputs.

Timer1 and Timer2 are two 8-bit incrementing timers, each with a period register (PR1 and PR2 respectively) and separate overflow interrupt flags. Timer1 and Timer2 can operate either as timers (increment on internal Fosc/4 clock) or as counters (increment on falling edge of external clock on pin RB4/TCLK12). They are also software configurable to operate as a single 16-bit timer. These timers are also used as the time-base for the PWM (pulse width modulation) module. Timer3 is a 16-bit timer/counter consisting of the TMR3H and TMR3L registers. This timer has four other associated registers. Two registers are used as a 16-bit period register or a 16-bit Capture1 register (PR3H/CA1H:PR3L/CA1L). The other two registers are strictly the Capture2 registers (CA2H:CA2L). Timer3 is the time-base for the two 16-bit captures.

TMR3 can be software configured to increment from the internal system clock or from an external signal on the RB5/TCLK3 pin.

Figure 12-1 and Figure 12-2 are the control registers for the operation of Timer1, Timer2, and Timer3, as well as PWM1, PWM2, Capture1, and Capture2.

# FIGURE 12-1: TCON1 REGISTER (ADDRESS: 16h, BANK 3)

| bit7     | I CA2ED0 CA1ED1 CA1ED0 T16 TMR3CS TMR2CS TMR1CS bit0                                                                                                                                                           | R = Readable bit<br>W = Writable bit<br>-n = Value at POR reset |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| bit 7-6: | <b>CA2ED1:CA2ED0</b> : Capture2 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 5-4: | <b>CA1ED1:CA1ED0</b> : Capture1 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 3:   | <b>T16</b> : Timer1:Timer2 Mode Select bit<br>1 = Timer1 and Timer2 form a 16-bit timer<br>0 = Timer1 and Timer2 are two 8-bit timers                                                                          |                                                                 |

| bit 2:   | <b>TMR3CS</b> : Timer3 Clock Source Select bit<br>1 = TMR3 increments off the falling edge of the RB5/TCLK3 pin<br>0 = TMR3 increments off the internal clock                                                  |                                                                 |

| bit 1:   | <b>TMR2CS</b> : Timer2 Clock Source Select bit<br>1 = TMR2 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR2 increments off the internal clock                                                 |                                                                 |

| bit 0:   | <b>TMR1CS</b> : Timer1 Clock Source Select bit<br>1 = TMR1 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR1 increments off the internal clock                                                 |                                                                 |

# FIGURE 12-2: TCON2 REGISTER (ADDRESS: 17h, BANK 3)

| R - 0  | R - 0 R/W - 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | F CA10VF PWM20N PWM10N CA1/PR3 TMR30N TMR20N TMR10N R = Readable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit7   | bit0 W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | -n = Value at POR reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 7: | <ul> <li>CA2OVF: Capture2 Overflow Status bit</li> <li>This bit indicates that the capture value had not been read from the capture register pair (CA2H:CA2L)</li> <li>before the next capture event occurred. The capture register retains the oldest unread capture value (last capture before overflow). Subsequent capture events will not update the capture register with the Timer3 value until the capture register has been read (both bytes).</li> <li>1 = Overflow occurred on Capture2 register</li> <li>0 = No overflow occurred on Capture2 register</li> </ul> |

| bit 6: | <b>CA1OVF</b> : Capture1 Overflow Status bit<br>This bit indicates that the capture value had not been read from the capture register pair<br>(PR3H/CA2H:PR3L/CA2L) before the next capture event occurred. The capture register retains the old-<br>est unread capture value (last capture before overflow). Subsequent capture events will not update the<br>capture register with the TMR3 value until the capture register has been read (both bytes).<br>1 = Overflow occurred on Capture1 register<br>0 = No overflow occurred on Capture1 register                     |

| bit 5: | <b>PWM2ON</b> : PWM2 On bit<br>1 = PWM2 is enabled (The RB3/PWM2 pin ignores the state of the DDRB<3> bit)<br>0 = PWM2 is disabled (The RB3/PWM2 pin uses the state of the DDRB<3> bit for data direction)                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4: | <b>PWM1ON</b> : PWM1 On bit<br>1 = PWM1 is enabled (The RB2/PWM1 pin ignores the state of the DDRB<2> bit)<br>0 = PWM1 is disabled (The RB2/PWM1 pin uses the state of the DDRB<2> bit for data direction)                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3: | <b>CA1/PR3</b> : CA1/PR3 Register Mode Select bit<br>1 = Enables Capture1 (PR3H/CA1H:PR3L/CA1L is the Capture1 register. Timer3 runs without<br>a period register)<br>0 = Enables the Period register (PR3H/CA1H:PR3L/CA1L is the Period register for Timer3)                                                                                                                                                                                                                                                                                                                 |

| bit 2: | TMR3ON: Timer3 On bit<br>1 = Starts Timer3<br>0 = Stops Timer3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 1: | <b>TMR2ON</b> : Timer2 On bit<br>This bit controls the incrementing of the Timer2 register. When Timer2:Timer1 form the 16-bit timer (T16<br>is set), TMR2ON must be set. This allows the MSB of the timer to increment.<br>1 = Starts Timer2 (Must be enabled if the T16 bit (TCON1<3>) is set)<br>0 = Stops Timer2                                                                                                                                                                                                                                                          |

| bit 0: | TMR1ON: Timer1 On bit<br><u>When T16 is set (in 16-bit Timer Mode)</u><br>1 = Starts 16-bit Timer2:Timer1<br>0 = Stops 16-bit Timer2:Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | <u>When T16 is clear (in 8-bit Timer Mode)</u><br>1 = Starts 8-bit Timer1<br>0 = Stops 8-bit Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

#### 12.1.2 TIMER1 & TIMER2 IN 16-BIT MODE

To select 16-bit mode, the T16 bit must be set. In this mode TMR1 and TMR2 are concatenated to form a 16-bit timer (TMR2:TMR1). The 16-bit timer increments until it matches the 16-bit period register (PR2:PR1). On the following timer clock, the timer value is reset to 0h, and the TMR1IF bit is set.

When selecting the clock source for the16-bit timer, the TMR1CS bit controls the entire 16-bit timer and TMR2CS is a "don't care." When TMR1CS is clear, the timer increments once every instruction cycle (Fosc/4). When TMR1CS is set, the timer increments on every falling edge of the RB4/TCLK12 pin. For the 16-bit timer to increment, both TMR1ON and TMR2ON bits must be set (Table 12-1).

#### 12.1.2.1 EXTERNAL CLOCK INPUT FOR TMR1:TMR2

When TMR1CS is set, the 16-bit TMR2:TMR1 increments on the falling edge of clock input TCLK12. The input on the RB4/TCLK12 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on RB4/TCLK12 to the time TMR2:TMR1 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

| TMR2ON | TMR10N | Result                         |

|--------|--------|--------------------------------|

| 1      | 1      | 16-bit timer<br>(TMR2:TMR1) ON |

| 0      | 1      | Only TMR1 increments           |

| x      | 0      | 16-bit timer OFF               |

#### FIGURE 12-4: TMR1 AND TMR2 IN 16-BIT TIMER/COUNTER MODE

#### TABLE 12-2: SUMMARY OF TIMER1 AND TIMER2 REGISTERS

| Address       | Name   | Bit 7      | Bit 6        | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|------------|--------------|--------|--------|---------|--------|--------|--------|-------------------------------|-----------------------------------------|

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0       | CA1ED1 | CA1ED0 | T16     | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF       | PWM2ON | PWM1ON | CA1/PR3 | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                               |

| 10h, Bank 2   | TMR1   | Timer1 reg | gister       |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 11h, Bank 2   | TMR2   | Timer2 reg | gister       |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF       | TMR2IF | TMR1IF | CA2IF   | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE       | TMR2IE | TMR1IE | CA2IE   | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked | INTSTA | PEIF       | T0CKIF       | T0IF   | INTF   | PEIE    | T0CKIE | TOIE   | INTE   | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked | CPUSTA | _          | -            | STKAV  | GLINTD | TO      | PD     | _      | _      | 11 11                         | 11 qq                                   |

| 14h, Bank 2   | PR1    | Timer1 pe  | riod registe | r      |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 2   | PR2    | Timer2 pe  | riod registe | r      |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 3   | PW1DCL | DC1        | DC0          | —      | _      | —       | —      | —      | —      | xx                            | uu                                      |

| 11h, Bank 3   | PW2DCL | DC1        | DC0          | TM2PW2 |        | —       | _      | _      | _      | xx0                           | uu0                                     |

| 12h, Bank 3   | PW1DCH | DC9        | DC8          | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 3   | PW2DCH | DC9        | DC8          | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', q - value depends on condition,

shaded cells are not used by Timer1 or Timer2.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

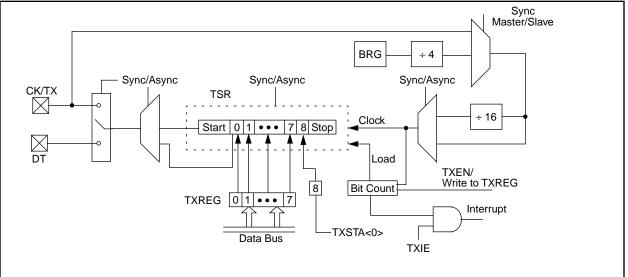

#### FIGURE 13-3: USART TRANSMIT

Table 15-2 lists the instructions recognized by the MPASM assembler.

| Note 1: | Any unused opcode is Reserved. Use of |  |  |  |  |  |

|---------|---------------------------------------|--|--|--|--|--|

|         | any reserved opcode may cause unex-   |  |  |  |  |  |

|         | pected operation.                     |  |  |  |  |  |

**Note 2:** The shaded instructions are not available in the PIC17C42

All instruction examples use the following format to represent a hexadecimal number:

0xhh

where h signifies a hexadecimal digit.

To represent a binary number:

0000 0100b

where b signifies a binary string.

#### FIGURE 15-1: GENERAL FORMAT FOR INSTRUCTIONS

#### 15.1 <u>Special Function Registers as</u> <u>Source/Destination</u>

The PIC17C4X's orthogonal instruction set allows read and write of all file registers, including special function registers. There are some special situations the user should be aware of:

#### 15.1.1 ALUSTA AS DESTINATION

If an instruction writes to ALUSTA, the Z, C, DC and OV bits may be set or cleared as a result of the instruction and overwrite the original data bits written. For example, executing CLRF ALUSTA will clear register ALUSTA, and then set the Z bit leaving 0000 0100b in the register.

#### 15.1.2 PCL AS SOURCE OR DESTINATION

Read, write or read-modify-write on PCL may have the following results:

| Read PC:           | $PCH \to PCLATH; PCL \to dest$                                                                |

|--------------------|-----------------------------------------------------------------------------------------------|

| Write PCL:         | PCLATH $\rightarrow$ PCH;<br>8-bit destination value $\rightarrow$ PCL                        |

| Read-Modify-Write: | $PCL \rightarrow ALU$ operand<br>$PCLATH \rightarrow PCH$ ;<br>8-bit result $\rightarrow PCL$ |

Where PCH = program counter high byte (not an addressable register), PCLATH = Program counter high holding latch, dest = destination, WREG or f.

#### 15.1.3 BIT MANIPULATION

All bit manipulation instructions are done by first reading the entire register, operating on the selected bit and writing the result back (read-modify-write). The user should keep this in mind when operating on special function registers, such as ports.

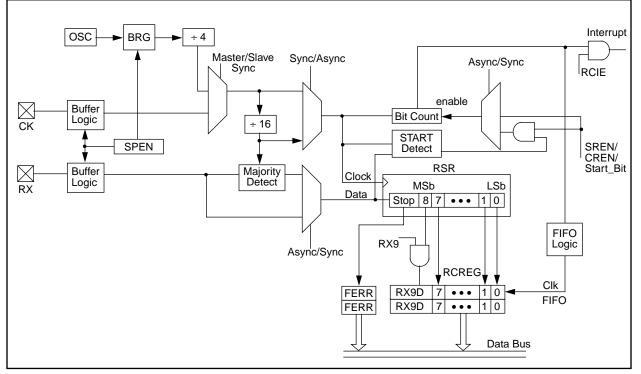

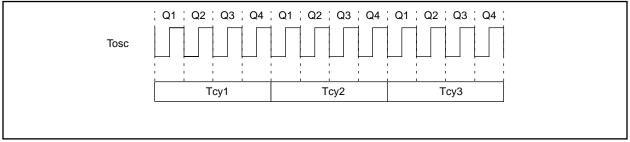

# 15.2 <u>Q Cycle Activity</u>

Each instruction cycle (Tcy) is comprised of four Q cycles (Q1-Q4). The Q cycles provide the timing/designation for the Decode, Read, Execute, Write etc., of each instruction cycle. The following diagram shows the relationship of the Q cycles to the instruction cycle.

The 4 Q cycles that make up an instruction cycle (Tcy) can be generalized as:

- Q1: Instruction Decode Cycle or forced NOP

- Q2: Instruction Read Cycle or NOP

- Q3: Instruction Execute

- Q4: Instruction Write Cycle or NOP

Each instruction will show the detailed Q cycle operation for the instruction.

# FIGURE 15-2: Q CYCLE ACTIVITY

# PIC17C4X

| BTFSS                                                                                                                                                                                                                  |           | Bit Test, skip if Set                                                                                                                                                                                            |                                                     |        |      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|--------|------|

| Syntax:                                                                                                                                                                                                                |           | [label]                                                                                                                                                                                                          | BTFSS f,b                                           | )      |      |

| Operands                                                                                                                                                                                                               | S:        | $0 \le f \le 127$                                                                                                                                                                                                |                                                     |        |      |

|                                                                                                                                                                                                                        |           | $0 \le b < 7$                                                                                                                                                                                                    |                                                     |        |      |

| Operation                                                                                                                                                                                                              | ו:        | skip if (f <b>) = 1</b>                                                                                                                                                                                          |                                                     |        |      |

| Status Af                                                                                                                                                                                                              | fected:   | None                                                                                                                                                                                                             |                                                     |        |      |

| Encoding                                                                                                                                                                                                               | :         | 1001                                                                                                                                                                                                             | 0bbb                                                | ffff   | ffff |

| Descriptio                                                                                                                                                                                                             | on:       | If bit 'b' in register 'f' is 1 then the next<br>instruction is skipped.<br>If bit 'b' is 1, then the next instruction<br>fetched during the current instruction exe-<br>cution, is discarded and an NOP is exe- |                                                     |        |      |

|                                                                                                                                                                                                                        |           |                                                                                                                                                                                                                  | cuted instead, making this a two-cycle instruction. |        |      |

| Words:                                                                                                                                                                                                                 |           | 1                                                                                                                                                                                                                |                                                     |        |      |

| Cycles:                                                                                                                                                                                                                |           | 1(2)                                                                                                                                                                                                             |                                                     |        |      |

| Q Cycle A                                                                                                                                                                                                              | Activity: |                                                                                                                                                                                                                  |                                                     |        |      |

|                                                                                                                                                                                                                        | Q1        | Q2                                                                                                                                                                                                               | Q3                                                  | 1      | Q4   |

| De                                                                                                                                                                                                                     | ecode     | Read<br>register 'f'                                                                                                                                                                                             | Execu                                               | ute    | NOP  |

| lf skip:                                                                                                                                                                                                               |           |                                                                                                                                                                                                                  |                                                     |        |      |

|                                                                                                                                                                                                                        | Q1        | Q2                                                                                                                                                                                                               | Q3                                                  |        | Q4   |

| Forc                                                                                                                                                                                                                   | ed NOP    | NOP                                                                                                                                                                                                              | Execu                                               | ute    | NOP  |

| <u>Example</u> :                                                                                                                                                                                                       |           | HERE<br>FALSE<br>TRUE                                                                                                                                                                                            | BTFSS<br>:<br>:                                     | FLAG,1 |      |

| Before Instruction<br>PC = address (HERE)                                                                                                                                                                              |           |                                                                                                                                                                                                                  |                                                     |        |      |

| $\begin{array}{rcl} \mbox{After Instruction} & & \\ \mbox{If FLAG<1>} &= & 0; \\ \mbox{PC} &= & \mbox{address} (\mbox{FALSE}) \\ \mbox{If FLAG<1>} &= & 1; \\ \mbox{PC} &= & \mbox{address} (\mbox{TRUE}) \end{array}$ |           |                                                                                                                                                                                                                  |                                                     |        |      |

| BTG               | Bit Toggle f                  |                                                  |                  |                         |

|-------------------|-------------------------------|--------------------------------------------------|------------------|-------------------------|

| Syntax:           | [label] E                     | [ <i>label</i> ] BTG f,b                         |                  |                         |

| Operands:         | 0 ≤ f ≤ 25<br>0 ≤ b < 7       | $0 \le f \le 255$<br>$0 \le b < 7$               |                  |                         |

| Operation:        | $(\overline{f}) \to$          | $\overline{(f < b >)} \rightarrow (f < b >)$     |                  |                         |

| Status Affected:  | None                          |                                                  |                  |                         |

| Encoding:         | 0011                          | 1bbb                                             | ffff             | ffff                    |

| Description:      | Bit 'b' in da inverted.       | Bit 'b' in data memory location 'f' is inverted. |                  |                         |

| Words:            | 1                             |                                                  |                  |                         |

| Cycles:           | 1                             |                                                  |                  |                         |

| Q Cycle Activity: |                               |                                                  |                  |                         |

| Q1                | Q2                            | Q3                                               | (                |                         |

| <u> </u>          | 92                            | 0,5                                              |                  | Q4                      |

| Decode            | Read<br>register 'f'          | Execute                                          | e W              | Q4<br>/rite<br>ster 'f' |

|                   | Read<br>register 'f'          |                                                  | e V<br>regi      | /rite                   |

| Decode            | Read<br>register 'f'<br>BTG 1 | Execute                                          | e W<br>regi<br>4 | /rite                   |

| XORLW             | Exclusive OR Literal with                                                                       | XORWF                          | Exclusive OR WREG with f                                                                                                                                           |  |  |

|-------------------|-------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                   | WREG                                                                                            | Syntax:                        | [label] XORWF f,d                                                                                                                                                  |  |  |

| Syntax:           | [ <i>label</i> ] XORLW k                                                                        | Operands:                      | $0 \le f \le 255$                                                                                                                                                  |  |  |

| Operands:         | $0 \le k \le 255$                                                                               |                                | d ∈ [0,1]                                                                                                                                                          |  |  |

| Operation:        | (WREG) .XOR. $k \rightarrow (WREG)$                                                             | Operation:                     | (WREG) .XOR. (f) $\rightarrow$ (dest)                                                                                                                              |  |  |

| Status Affected:  | Z                                                                                               | Status Affected:               | Z                                                                                                                                                                  |  |  |

| Encoding:         | 1011 0100 kkkk kkkk                                                                             | Encoding:                      | 0000 110d ffff ffff                                                                                                                                                |  |  |

| Description:      | The contents of WREG are XOR'ed<br>with the 8-bit literal 'k'. The result is<br>placed in WREG. | Description:                   | Exclusive OR the contents of WREG<br>with register 'f'. If 'd' is 0 the result is<br>stored in WREG. If 'd' is 1 the result is<br>stored back in the register 'f'. |  |  |

| Words:            | 1                                                                                               | Words:                         | 1                                                                                                                                                                  |  |  |

| Cycles:           | 1                                                                                               | Cycles:                        | 1                                                                                                                                                                  |  |  |

| Q Cycle Activity: |                                                                                                 | Q Cycle Activity:              |                                                                                                                                                                    |  |  |

| Q1                | Q2 Q3 Q4                                                                                        | Q Cycle Activity.<br>Q1        | Q2 Q3 Q4                                                                                                                                                           |  |  |

| Decode            | ReadExecuteWrite toliteral 'k'WREG                                                              | Decode                         | Read Execute Write to destination                                                                                                                                  |  |  |

| Example:          | XORLW 0xAF                                                                                      | L                              |                                                                                                                                                                    |  |  |

| Before Instruc    | ction                                                                                           | Example:                       | XORWF REG, 1                                                                                                                                                       |  |  |

| After Instructi   | = 0xB5<br>on<br>= 0x1A                                                                          | Before Instru<br>REG<br>WREG   | ction<br>= 0xAF<br>= 0xB5                                                                                                                                          |  |  |

|                   |                                                                                                 | After Instructi<br>REG<br>WREG | ion<br>= 0x1A<br>= 0xB5                                                                                                                                            |  |  |

MPASM allow full symbolic debugging from the Microchip Universal Emulator System (PICMASTER).

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

# 16.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

# 16.12 C Compiler (MPLAB-C)

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

### 16.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 16.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

#### 16.15 <u>SEEVAL® Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 16.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

### 16.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

# PIC17C4X

# Applicable Devices 42 R42 42A 43 R43 44

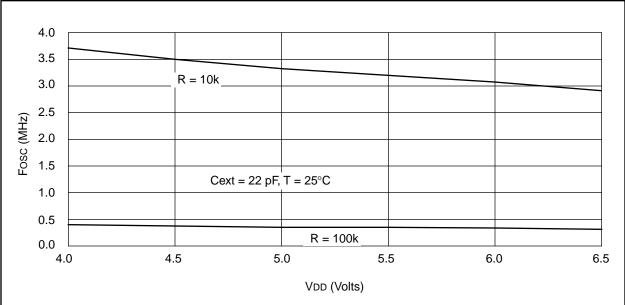

# FIGURE 18-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

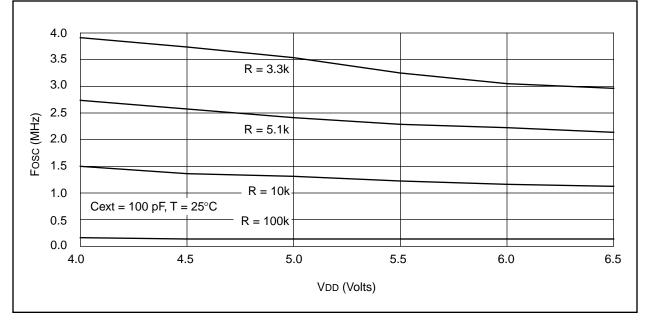

### FIGURE 18-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

# PIC17C4X

# Applicable Devices 42 R42 42A 43 R43 44

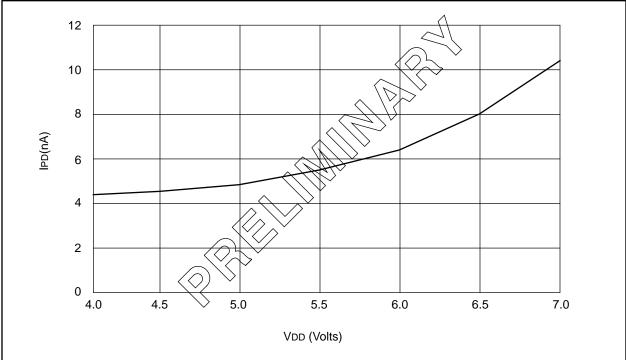

# FIGURE 20-9: TYPICAL IPD vs. VDD WATCHDOG DISABLED 25°C

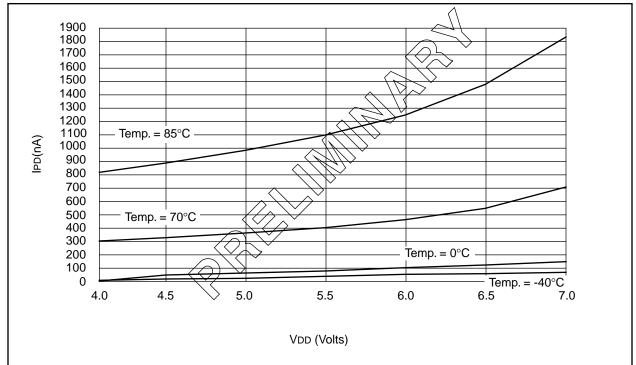

FIGURE 20-10: MAXIMUM IPD vs. VDD WATCHDOG DISABLED

# Applicable Devices 42 R42 42A 43 R43 44

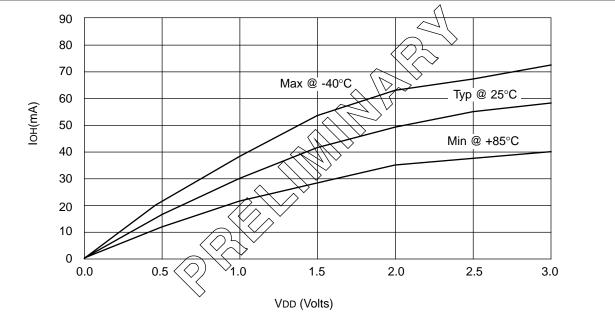

# FIGURE 20-17: IOL vs. VOL, VDD = 5V

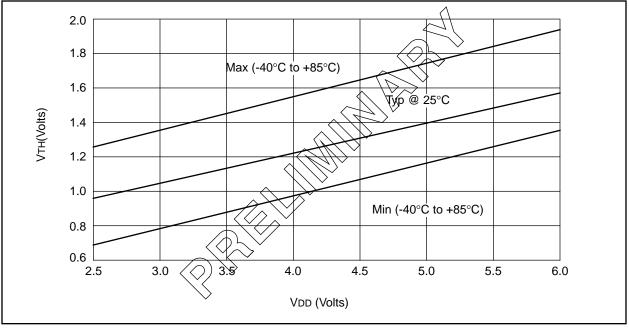

### FIGURE 20-18: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS (TTL) VS. VDD

NOTES:

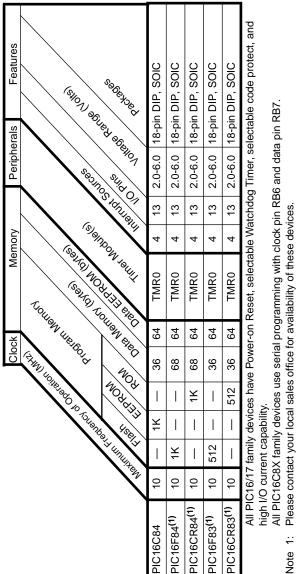

#### E.6 **PIC16C8X Family of Devices**

÷ Note NOTES:

#### Note the following details of the code protection feature on PICmicro<sup>®</sup> MCUs.

- The PICmicro family meets the specifications contained in the Microchip Data Sheet.

- Microchip believes that its family of PICmicro microcontrollers is one of the most secure products of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the PICmicro microcontroller in a manner outside the operating specifications contained in the data sheet. The person doing so may be engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable".

- Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our product.

If you have any further questions about this matter, please contact the local sales office nearest to you.

Information contained in this publication regarding device applications and the like is intended through suggestion only and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. No representation or warranty is given and no liability is assumed by Microchip Technology Incorporated with respect to the accuracy or use of such information, or infringement of patents or other intellectual property rights arising from such use or otherwise. Use of Microchip's products as critical components in life support systems is not authorized except with express written approval by Microchip. No licenses are conveyed, implicitly or otherwise, under any intellectual property rights.

#### Trademarks

The Microchip name and logo, the Microchip logo, FilterLab, KEELOQ, microID, MPLAB, PIC, PICmicro, PICMASTER, PICSTART, PRO MATE, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

dsPIC, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, microPort, Migratable Memory, MPASM, MPLIB, MPLINK, MPSIM, MXDEV, PICC, PICDEM, PICDEM.net, rfPIC, Select Mode and Total Endurance are trademarks of Microchip Technology Incorporated in the U.S.A.

Serialized Quick Turn Programming (SQTP) is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2002, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received QS-9000 quality system certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona in July 1999. The Company's quality system processes and procedures are QS-9000 compliant for its PICmicro® 8-bit MCUs, KEELoq® code hopping devices, Serial EEPROMs and microperipheral products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001 certified.