# E·XFL

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 33MHz                                                                   |

| Connectivity               | UART/USART                                                              |

| Peripherals                | POR, PWM, WDT                                                           |

| Number of I/O              | 33                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | OTP                                                                     |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 454 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                               |

| Data Converters            | -                                                                       |

| Oscillator Type            | External                                                                |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                         |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                |

| Supplier Device Package    | 40-PDIP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44-33-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| TABLE 3-1. |            |                      |                 |               |                |                                                                                                                                                                             |

|------------|------------|----------------------|-----------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name       | DIP<br>No. | PLCC<br>No.          | QFP<br>No.      | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                 |

|            |            |                      |                 |               |                | PORTD is a bi-directional I/O Port.                                                                                                                                         |

| RD0/AD8    | 40         | 43                   | 15              | I/O           | TTL            | This is also the upper byte of the 16-bit system bus in                                                                                                                     |

| RD1/AD9    | 39         | 42                   | 14              | I/O           | TTL            | microprocessor mode or extended microprocessor mode                                                                                                                         |

| RD2/AD10   | 38         | 41                   | 13              | I/O           | TTL            | or extended microcontroller mode. In multiplexed system                                                                                                                     |

| RD3/AD11   | 37         | 40                   | 12              | I/O           | TTL            | bus configuration these pins are address output as well as data input or output.                                                                                            |

| RD4/AD12   | 36         | 39                   | 11              | I/O           | TTL            |                                                                                                                                                                             |

| RD5/AD13   | 35         | 38                   | 10              | I/O           | TTL            |                                                                                                                                                                             |

| RD6/AD14   | 34         | 37                   | 9               | I/O           | TTL            |                                                                                                                                                                             |

| RD7/AD15   | 33         | 36                   | 8               | I/O           | TTL            |                                                                                                                                                                             |

|            |            |                      |                 |               |                | PORTE is a bi-directional I/O Port.                                                                                                                                         |

| RE0/ALE    | 30         | 32                   | 4               | I/O           | TTL            | In microprocessor mode or extended microcontroller<br>mode, it is the Address Latch Enable (ALE) output.<br>Address should be latched on the falling edge of ALE<br>output. |

| RE1/OE     | 29         | 31                   | 3               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Output Enable ( $\overline{OE}$ ) control output (active low).                                                |

| RE2/WR     | 28         | 30                   | 2               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Write Enable (WR) control output (active low).                                                                |

| TEST       | 27         | 29                   | 1               | I             | ST             | Test mode selection control input. Always tie to Vss for nor-<br>mal operation.                                                                                             |

| Vss        | 10,<br>31  | 11,<br>12,<br>33, 34 | 5, 6,<br>27, 28 | Р             |                | Ground reference for logic and I/O pins.                                                                                                                                    |

| Vdd        | 1          | 1, 44                | 16, 17          | Р             |                | Positive supply for logic and I/O pins.                                                                                                                                     |

| TABLE 3-1: | PINOUT DESCRIPTIONS |

|------------|---------------------|

|------------|---------------------|

Legend: I = Input only; O = Output only; I/O = Input/Output; P = Power; — = Not Used; TTL = TTL input; ST = Schmitt Trigger input.

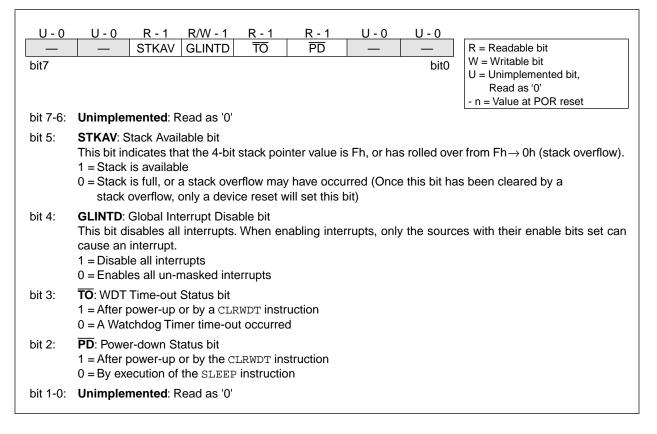

### 6.2.2.2 CPU STATUS REGISTER (CPUSTA)

The CPUSTA register contains the status and control bits for the CPU. This register is used to globally enable/disable interrupts. If only a specific interrupt is desired to be enabled/disabled, please refer to the INTerrupt STAtus (INTSTA) register and the Peripheral Interrupt Enable (PIE) register. This register also indicates if the stack is available and contains the Power-down (PD) and Time-out (TO) bits. The TO, PD, and STKAV bits are not writable. These bits are set and cleared according to device logic. Therefore, the result of an instruction with the CPUSTA register as destination may be different than intended.

### FIGURE 6-8: CPUSTA REGISTER (ADDRESS: 06h, UNBANKED)

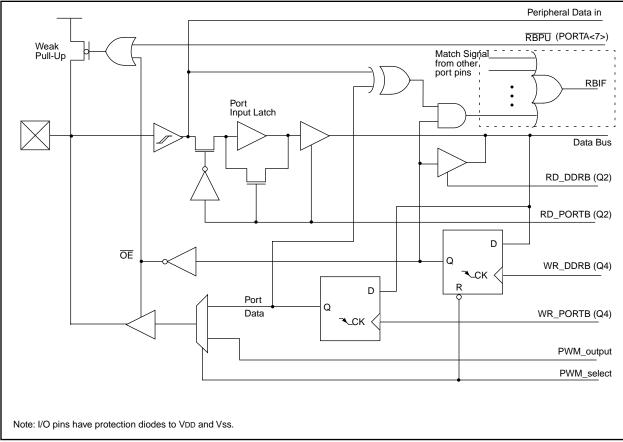

### FIGURE 9-5: BLOCK DIAGRAM OF RB3 AND RB2 PORT PINS

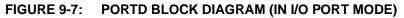

### 9.4 PORTD and DDRD Registers

PORTD is an 8-bit bi-directional port. The corresponding data direction register is DDRD. A '1' in DDRD configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTD reads the status of the pins, whereas writing to it will write to the port latch. PORTD is multiplexed with the system bus. When operating as the system bus, PORTD is the high order byte of the address/data bus (AD15:AD8). The timing for the system bus is shown in the Electrical Characteristics section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-3 shows the instruction sequence to initialize PORTD. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

### EXAMPLE 9-3: INITIALIZING PORTD

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTD | ; | Initialize PORTD data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0xCF  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRD  | ; | Set RD<3:0> as inputs    |

|       |       | ; | RD<5:4> as outputs       |

|       |       | ; | RD<7:6> as inputs        |

|       |       |   |                          |

### 11.1 <u>Timer0 Operation</u>

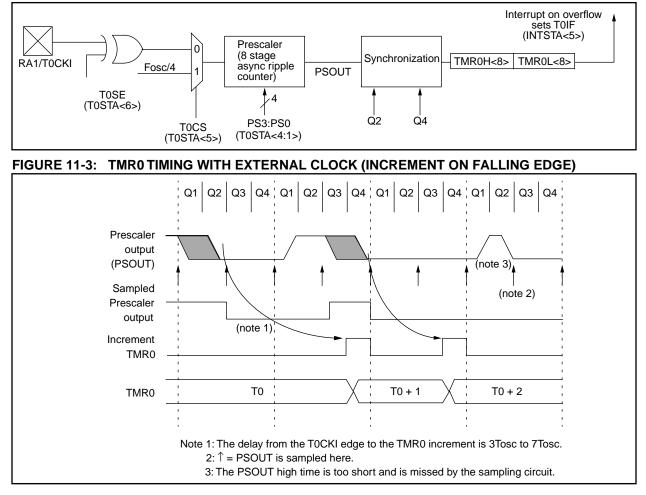

When the TOCS (TOSTA<5>) bit is set, TMR0 increments on the internal clock. When TOCS is clear, TMR0 increments on the external clock (RA1/T0CKI pin). The external clock edge can be configured in software. When the TOSE (TOSTA<6>) bit is set, the timer will increment on the rising edge of the RA1/T0CKI pin. When T0SE is clear, the timer will increment on the falling edge of the RA1/T0CKI pin. The prescaler can be programmed to introduce a prescale of 1:1 to 1:256. The timer increments from 0000h to FFFFh and rolls over to 0000h. On overflow, the TMR0 Interrupt Flag bit (T0IF) is set. The TMR0 interrupt can be masked by clearing the corresponding TMR0 Interrupt Enable bit (T0IE). The TMR0 Interrupt Flag bit (T0IF) is automatically cleared when vectoring to the TMR0 interrupt vector.

### 11.2 Using Timer0 with External Clock

When the external clock input is used for Timer0, it is synchronized with the internal phase clocks. Figure 11-3 shows the synchronization of the external clock. This synchronization is done after the prescaler. The output of the prescaler (PSOUT) is sampled twice in every instruction cycle to detect a rising or a falling edge. The timing requirements for the external clock are detailed in the electrical specification section for the desired device.

### 11.2.1 DELAY FROM EXTERNAL CLOCK EDGE

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time TMR0 is actually incremented. Figure 11-3 shows that this delay is between 3Tosc and 7Tosc. Thus, for example, measuring the interval between two edges (e.g. period) will be accurate within  $\pm$ 4Tosc ( $\pm$ 121 ns @ 33 MHz).

### FIGURE 11-2: TIMER0 MODULE BLOCK DIAGRAM

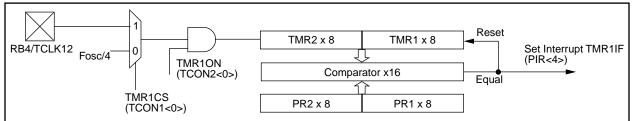

### 12.1.2 TIMER1 & TIMER2 IN 16-BIT MODE

To select 16-bit mode, the T16 bit must be set. In this mode TMR1 and TMR2 are concatenated to form a 16-bit timer (TMR2:TMR1). The 16-bit timer increments until it matches the 16-bit period register (PR2:PR1). On the following timer clock, the timer value is reset to 0h, and the TMR1IF bit is set.

When selecting the clock source for the16-bit timer, the TMR1CS bit controls the entire 16-bit timer and TMR2CS is a "don't care." When TMR1CS is clear, the timer increments once every instruction cycle (Fosc/4). When TMR1CS is set, the timer increments on every falling edge of the RB4/TCLK12 pin. For the 16-bit timer to increment, both TMR1ON and TMR2ON bits must be set (Table 12-1).

### 12.1.2.1 EXTERNAL CLOCK INPUT FOR TMR1:TMR2

When TMR1CS is set, the 16-bit TMR2:TMR1 increments on the falling edge of clock input TCLK12. The input on the RB4/TCLK12 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on RB4/TCLK12 to the time TMR2:TMR1 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

| TMR2ON | TMR10N | Result                         |

|--------|--------|--------------------------------|

| 1      | 1      | 16-bit timer<br>(TMR2:TMR1) ON |

| 0      | 1      | Only TMR1 increments           |

| x      | 0      | 16-bit timer OFF               |

### FIGURE 12-4: TMR1 AND TMR2 IN 16-BIT TIMER/COUNTER MODE

### TABLE 12-2: SUMMARY OF TIMER1 AND TIMER2 REGISTERS

| Address       | Name   | Bit 7      | Bit 6        | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|------------|--------------|--------|--------|---------|--------|--------|--------|-------------------------------|-----------------------------------------|

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0       | CA1ED1 | CA1ED0 | T16     | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF       | PWM2ON | PWM1ON | CA1/PR3 | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                               |

| 10h, Bank 2   | TMR1   | Timer1 reg | gister       |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 11h, Bank 2   | TMR2   | Timer2 reg | gister       |        |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF       | TMR2IF | TMR1IF | CA2IF   | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE       | TMR2IE | TMR1IE | CA2IE   | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked | INTSTA | PEIF       | T0CKIF       | T0IF   | INTF   | PEIE    | T0CKIE | TOIE   | INTE   | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked | CPUSTA | _          | -            | STKAV  | GLINTD | TO      | PD     | _      | _      | 11 11                         | 11 qq                                   |

| 14h, Bank 2   | PR1    | Timer1 pe  | riod registe | r      |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 2   | PR2    | Timer2 pe  | riod registe | r      |        |         |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 3   | PW1DCL | DC1        | DC0          | —      | _      | —       | —      | —      | —      | xx                            | uu                                      |

| 11h, Bank 3   | PW2DCL | DC1        | DC0          | TM2PW2 |        | —       | _      | _      | _      | xx0                           | uu0                                     |

| 12h, Bank 3   | PW1DCH | DC9        | DC8          | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 3   | PW2DCH | DC9        | DC8          | DC7    | DC6    | DC5     | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', q - value depends on condition,

shaded cells are not used by Timer1 or Timer2.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

| BAUD        | Fosc = 3 | 3 MHz  | SPBRG              | Fosc = 2 | 5 MHz  | SPBRG              | Fosc = 2 | 0 MHz  | SPBRG              | Fosc = 1 | 6 MHz  | SPBRG              |

|-------------|----------|--------|--------------------|----------|--------|--------------------|----------|--------|--------------------|----------|--------|--------------------|

| RATE<br>(K) | KBAUD    | %ERROR | value<br>(decimal) |

| 0.3         | NA       | _      | —                  | NA       | _      |                    | NA       | _      | _                  | NA       | _      | -                  |

| 1.2         | NA       | _      | _                  | NA       | _      | _                  | 1.221    | +1.73  | 255                | 1.202    | +0.16  | 207                |

| 2.4         | 2.398    | -0.07  | 214                | 2.396    | 0.14   | 162                | 2.404    | +0.16  | 129                | 2.404    | +0.16  | 103                |

| 9.6         | 9.548    | -0.54  | 53                 | 9.53     | -0.76  | 40                 | 9.469    | -1.36  | 32                 | 9.615    | +0.16  | 25                 |

| 19.2        | 19.09    | -0.54  | 26                 | 19.53    | +1.73  | 19                 | 19.53    | +1.73  | 15                 | 19.23    | +0.16  | 12                 |

| 76.8        | 73.66    | -4.09  | 6                  | 78.13    | +1.73  | 4                  | 78.13    | +1.73  | 3                  | 83.33    | +8.51  | 2                  |

| 96          | 103.12   | +7.42  | 4                  | 97.65    | +1.73  | 3                  | 104.2    | +8.51  | 2                  | NA       | _      | _                  |

| 300         | 257.81   | -14.06 | 1                  | 390.63   | +30.21 | 0                  | 312.5    | +4.17  | 0                  | NA       | _      | -                  |

| 500         | 515.62   | +3.13  | 0                  | NA       | _      | _                  | NA       | _      | _                  | NA       | _      | -                  |

| HIGH        | 515.62   | _      | 0                  | _        | _      | 0                  | 312.5    | _      | 0                  | 250      | _      | 0                  |

| LOW         | 2.014    | —      | 255                | 1.53     | —      | 255                | 1.221    | —      | 255                | 0.977    | _      | 255                |

### TABLE 13-4: BAUD RATES FOR ASYNCHRONOUS MODE

| BAUD<br>RATE | Fosc = 10 MH | Iz     | SPBRG<br>value     | Fosc = 7.159 | ) MHz  | SPBRG<br>value     | FOSC = 5.068 | 8 MHz  | SPBRG<br>value     |

|--------------|--------------|--------|--------------------|--------------|--------|--------------------|--------------|--------|--------------------|

| (K)          | KBAUD        | %ERROR | (decimal)          | KBAUD        | %ERROR | (decimal)          | KBAUD        | %ERROR | (decimal)          |

| 0.3          | NA           | _      | _                  | NA           | _      | _                  | 0.31         | +3.13  | 255                |

| 1.2          | 1.202        | +0.16  | 129                | 1.203        | _0.23  | 92                 | 1.2          | 0      | 65                 |

| 2.4          | 2.404        | +0.16  | 64                 | 2.380        | -0.83  | 46                 | 2.4          | 0      | 32                 |

| 9.6          | 9.766        | +1.73  | 15                 | 9.322        | -2.90  | 11                 | 9.9          | -3.13  | 7                  |

| 19.2         | 19.53        | +1.73  | 7                  | 18.64        | -2.90  | 5                  | 19.8         | +3.13  | 3                  |

| 76.8         | 78.13        | +1.73  | 1                  | NA           | _      | —                  | 79.2         | +3.13  | 0                  |

| 96           | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 300          | NA           | _      | —                  | NA           | _      | —                  | NA           | _      | _                  |

| 500          | NA           | _      | _                  | NA           | _      | _                  | NA           | _      | _                  |

| HIGH         | 156.3        | _      | 0                  | 111.9        | _      | 0                  | 79.2         | _      | 0                  |

| LOW          | 0.610        | —      | 255                | 0.437        | —      | 255                | 0.309        | _      | 2 <b>55</b>        |

| BAUD         | Fosc = 3.579 | MHz    | SPBRG              | Fosc = 1 MH  | z      | SPBRG              | FOSC = 32.76 | 8 kHz  | SPBRG              |

| RATE<br>(K)  | KBAUD        | %ERROR | value<br>(decimal) | KBAUD        | %ERROR | value<br>(decimal) | KBAUD        | %ERROR | value<br>(decimal) |

| 0.3          | 0.301        | +0.23  | 185                | 0.300        | +0.16  | 51                 | 0.256        | -14.67 | 1                  |

| 1.2          | 1.190        | -0.83  | 46                 | 1.202        | +0.16  | 12                 | NA           | —      | —                  |

| 2.4          | 2.432        | +1.32  | 22                 | 2.232        | -6.99  | 6                  | NA           | —      | —                  |

| 9.6          | 9.322        | -2.90  | 5                  | NA           | _      | _                  | NA           | _      | _                  |

| 19.2         | 18.64        | -2.90  | 2                  | NA           | —      | —                  | NA           | —      | —                  |

| 76.8         | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 96           | NA           | _      | _                  | NA           | _      | _                  | NA           | _      | _                  |

| 300          | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 500          | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| HIGH         | 55.93        | _      | 0                  | 15.63        | _      | 0                  | 0.512        | _      | 0                  |

| l mon        |              |        |                    |              |        |                    |              |        |                    |

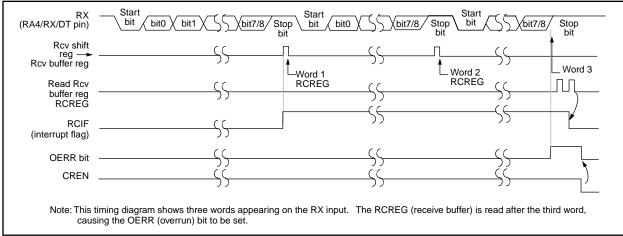

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

### FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6</b> : | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|---------------------|---------------------------------------------------------|

|                     |                                                         |

| Address     | Name  | Bit 7     | Bit 6     | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-----------|-----------|----------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR   | RBIF      | TMR3IF    | TMR2IF   | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA | SPEN      | RX9       | SREN     | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0 | RCREG | RX7       | RX6       | RX5      | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE   | RBIE      | TMR3IE    | TMR2IE   | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA | CSRC      | TX9       | TXEN     | SYNC   | _     | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | SPBRG | Baud rate | generator | register |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

### 13.3 USART Synchronous Master Mode

In Master Synchronous mode, the data is transmitted in a half-duplex manner; i.e. transmission and reception do not occur at the same time: when transmitting data, the reception is inhibited and vice versa. The synchronous mode is entered by setting the SYNC (TXSTA<4>) bit. In addition, the SPEN (RCSTA<7>) bit is set in order to configure the RA5 and RA4 I/O ports to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting the CSRC (TXSTA<7>) bit.

### 13.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer TXREG. TXREG is loaded with data in software. The TSR is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), TXREG is empty and the TXIF (PIR<1>) bit is set. This interrupt can be enabled/disabled by setting/clearing the TXIE bit (PIE<1>). TXIF will be set regardless of the state of bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of TXREG, TRMT (TXSTA<1>) shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the RA5/TX/CK pin. Data out is stable around the falling edge of the synchronous clock (Figure 13-10). The transmission can also be started by first loading TXREG and then setting TXEN. This is advantageous when slow baud rates are selected, since BRG is kept in RESET when the TXEN, CREN, and SREN bits are clear. Setting the TXEN bit will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to the TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The RA4/RX/DT and RA5/TX/CK pins will revert to hi-impedance. If either CREN or SREN are set during a transmission, the transmission is aborted and the

RA4/RX/DT pin reverts to a hi-impedance state (for a reception). The RA5/TX/CK pin will remain an output if the CSRC bit is set (internal clock). The transmitter logic is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear the TXEN bit. If the SREN bit is set (to interrupt an ongoing transmission and receive a single word), then after the single word is received, SREN will be cleared and the serial port will revert back to transmitting, since the TXEN bit is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty). If the TSR was empty and TXREG was written before writing the "new" TX9D, the "present" value of TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (see Baud Rate Generator Section for details).

- 2. Enable the synchronous master serial port by setting the SYNC, SPEN, and CSRC bits.

- 3. Ensure that the CREN and SREN bits are clear (these bits override transmission when set).

- 4. If interrupts are desired, then set the TXIE bit (the GLINTD bit must be clear and the PEIE bit must be set).

- 5. If 9-bit transmission is desired, then set the TX9 bit.

- 6. Start transmission by loading data to the TXREG register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 8. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the reverse order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

### 14.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC17CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- OSC selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- · Code protection

The PIC17CXX has a Watchdog Timer which can be shut off only through EPROM bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 96 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake from SLEEP through external reset, Watchdog Timer Reset or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LF crystal option saves power. Configuration bits are used to select various options. This configuration word has the format shown in Figure 14-1.

| <u>R/P - 1</u><br>PM2 <sup>(1)</sup> | U - x                                                       | U - x                                  | <u>U-x</u>                             | U - x       | U - x   | <u>U-x</u> | U - x         |                                                                                                                 |

|--------------------------------------|-------------------------------------------------------------|----------------------------------------|----------------------------------------|-------------|---------|------------|---------------|-----------------------------------------------------------------------------------------------------------------|

| bit15-7                              |                                                             |                                        | _                                      |             |         |            | bit0          |                                                                                                                 |

| U - x                                | R/P - 1                                                     | U - x                                  | <u>R/P - 1</u>                         | R/P - 1     | R/P - 1 | R/P - 1    | R/P - 1       | R = Readable bit                                                                                                |

| <br>bit15-7                          | PM1                                                         |                                        | PM0                                    | WDTPS1      | WDTPS0  | FOSC1      | FOSC0<br>bit0 | P = Programmable bit $P = Programmable bit$ $U = Unimplemented$ $- n = Value for Erased Device$ $(x = unknown)$ |

| bit 15-9:                            | Unimpler                                                    | nented: R                              | ead as a                               | '1'         |         |            |               |                                                                                                                 |

|                                      |                                                             | rocontrolle<br>ended mic<br>de protect | er mode<br>crocontrol<br>ed microc     | ontroller m | ode     |            |               |                                                                                                                 |

| bit 7, 5:                            | Unimpler                                                    | nented: R                              | ead as a                               | '0'         |         |            |               |                                                                                                                 |

| bit 3-2:                             | 11 = WD<br>10 = WD<br>01 = WD                               | Γ enabled<br>Γ enabled<br>Γ enabled    | , postscal<br>, postscal<br>, postscal | er = 256    |         |            |               |                                                                                                                 |

| bit 1-0:                             | FOSC1:F<br>11 = EC (<br>10 = XT (<br>01 = RC (<br>00 = LF ( | oscillator<br>oscillator<br>oscillator | scillator S                            | elect bits  |         |            |               |                                                                                                                 |

|                                      |                                                             |                                        |                                        |             |         |            |               |                                                                                                                 |

### FIGURE 14-1: CONFIGURATION WORD

<sup>© 1996</sup> Microchip Technology Inc.

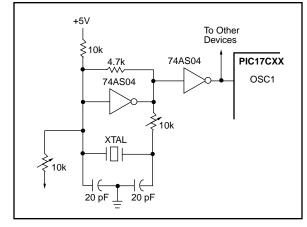

### 14.2.4 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

Figure 14-5 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

### FIGURE 14-5: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

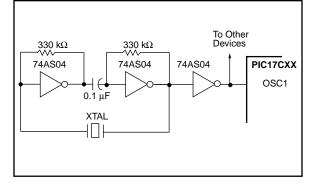

Figure 14-6 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

### FIGURE 14-6: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

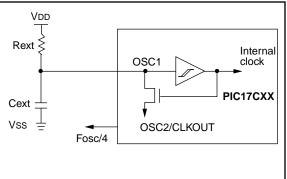

### 14.2.5 RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 14-6 shows how the R/C combination is connected to the PIC17CXX. For Rext values below 2.2 kQ, the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3  $k\Omega$  and 100  $k\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With little or no external capacitance, oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 18.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 18.0 for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-2 for waveform).

### FIGURE 14-7: RC OSCILLATOR MODE

### 14.4 Power-down Mode (SLEEP)

The Power-down mode is entered by executing a SLEEP instruction. This clears the Watchdog Timer and postscaler (if enabled). The  $\overrightarrow{PD}$  bit is cleared and the  $\overrightarrow{TO}$  bit is set (in the CPUSTA register). In SLEEP mode, the oscillator driver is turned off. The I/O ports maintain their status (driving high, low, or hi-impedance).

The  $\overline{\text{MCLR}}/\text{VPP}$  pin must be at a logic high level (VIHMC). A WDT time-out RESET does not drive the  $\overline{\text{MCLR}}/\text{VPP}$  pin low.

### 14.4.1 WAKE-UP FROM SLEEP

The device can wake up from SLEEP through one of the following events:

- A POR reset

- External reset input on MCLR/VPP pin

- WDT Reset (if WDT was enabled)

- Interrupt from RA0/INT pin, RB port change, T0CKI interrupt, or some Peripheral Interrupts

The following peripheral interrupts can wake-up from SLEEP:

- · Capture1 interrupt

- Capture2 interrupt

- USART synchronous slave transmit interrupt

- · USART synchronous slave receive interrupt

Other peripherals can not generate interrupts since during SLEEP, no on-chip Q clocks are present.

Any reset event will cause a device reset. Any interrupt event is considered a continuation of program execution. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits in the CPUSTA register can be used to determine the cause of device reset. The

$\overline{PD}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The  $\overline{TO}$  bit is cleared if WDT time-out occurred (and caused wake-up).

When the SLEEP instruction is being executed, the next instruction (PC + 1) is pre-fetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GLINTD bit. If the GLINTD bit is set (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GLINTD bit is clear (enabled), the device executes the instruction after the SLEEP instruction and then branches to the interrupt vector address. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GLINTD is set), but any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from sleep. The TO bit is set, and the PD bit is cleared.

The WDT is cleared when the device wake from SLEEP, regardless of the source of wake-up.

14.4.1.1 WAKE-UP DELAY

When the oscillator type is configured in XT or LF mode, the Oscillator Start-up Timer (OST) is activated on wake-up. The OST will keep the device in reset for 1024Tosc. This needs to be taken into account when considering the interrupt response time when coming out of SLEEP.

### FIGURE 14-9: WAKE-UP FROM SLEEP THROUGH INTERRUPT

|                              | Q1   Q2   Q3   Q4                                                                                     | Q1   Q2   Q3   Q4                                  | Q1   Q2      | Q3   Q4      | Q1   Q2       | Q3  Q4                 | Q1   Q2   Q3   Q4     |

|------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|--------------|---------------|------------------------|-----------------------|

| OSC1                         |                                                                                                       |                                                    |              |              |               | $\frown \frown \frown$ |                       |

| CLKOUT(4)                    |                                                                                                       | /                                                  |              | Tost(2)      | \/<br>\/      |                        |                       |

| INT                          |                                                                                                       |                                                    |              |              | I<br>I        |                        |                       |

| (RA0/INT pin)                | ı ı                                                                                                   |                                                    | : (          |              | 1             |                        | 1 1                   |

| INTF flag                    |                                                                                                       |                                                    | <u>`</u>     |              | I             |                        | Interrupt Latency (2) |

| GLINTD bit                   | 1<br>11                                                                                               |                                                    | · ·          |              | I             |                        |                       |

|                              | · · · ·                                                                                               |                                                    | Processor    |              | 1             |                        | 1 I                   |

| INSTRUCTION                  | FLOW                                                                                                  |                                                    | in SLEEP     |              | 1<br>1        |                        | I I                   |

| PC                           | C PC                                                                                                  | PC+1                                               |              | +2           | × 0004        | h                      | × <u>0005h</u>        |

| Instruction (<br>fetched     | Inst (PC) = SLEEP                                                                                     | Inst (PC+1)                                        |              |              | Inst (PC      | +2)                    |                       |

| Instruction {                | Inst (PC-1)                                                                                           | SLEEP                                              |              |              | Inst (PC      | +1)                    | Dummy Cycle           |

| 2: Tost = 102<br>3: When GLI | scillator mode assume<br>4Tosc (drawing not to s<br>NTD = 0 processor jum<br>s not available in these | scale). This delay will<br>ps to interrupt routing | e after wake | -up. If GLIN | ITD = 1, exec | ution will             | continue in line.     |

| MOVFP                        | Move f to                                                                                                                                                                          | р             |                       | MOVLB                    | Move Lite                                                                                                                                                                                      | eral to low r       | nibble in BSR                 |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|--|

| Syntax:                      | [ <i>label</i> ] N                                                                                                                                                                 | IOVFP f,p     |                       | Syntax:                  | [ label ]                                                                                                                                                                                      | MOVLB k             |                               |  |

| Operands:                    | 0 ≤ f ≤ 255                                                                                                                                                                        | 5             |                       | Operands:                | $0 \le k \le 15$                                                                                                                                                                               |                     |                               |  |

|                              | $0 \le p \le 31$                                                                                                                                                                   |               |                       | Operation:               | $k \rightarrow (BSR)$                                                                                                                                                                          | <3:0>)              |                               |  |

| Operation:                   | $(f) \to (p)$                                                                                                                                                                      |               |                       | Status Affected:         | None                                                                                                                                                                                           |                     |                               |  |

| Status Affected:             | None                                                                                                                                                                               |               |                       | Encoding:                | 1011                                                                                                                                                                                           | 1000 ui             | uuu kkkk                      |  |

| Encoding:                    | 011p                                                                                                                                                                               | pppp ff       | ff ffff               | Description:             | The four bi                                                                                                                                                                                    | t literal 'k' is lo | aded in the                   |  |

| Description:                 | Move data from data memory location 'f'<br>to data memory location 'p'. Location 'f'<br>can be anywhere in the 256 word data<br>space (00h to FFh) while 'p' can be 00h<br>to 1Fh. |               |                       |                          | Bank Select Register (BSR). Only the<br>low 4-bits of the Bank Select Register<br>are affected. The upper half of the BSR<br>is unchanged. The assembler will<br>encode the "u" fields as '0'. |                     |                               |  |

|                              |                                                                                                                                                                                    | 'f' can be WR | EG (a useful          | Words:                   | 1                                                                                                                                                                                              |                     |                               |  |

|                              | special situ                                                                                                                                                                       | ,             | ful for transfer-     | Cycles:                  | 1                                                                                                                                                                                              |                     |                               |  |

|                              |                                                                                                                                                                                    |               | on to a periph-       | Q Cycle Activity:        |                                                                                                                                                                                                |                     |                               |  |

|                              | eral register (such as the transmit buffer or an I/O port). Both 'f' and 'p' can be                                                                                                |               | Q1                    | Q2                       | Q3                                                                                                                                                                                             | Q4                  |                               |  |

|                              | indirectly a                                                                                                                                                                       |               | d p can be            | Decode                   | Read                                                                                                                                                                                           | Execute             | Write literal                 |  |

| Words:                       | 1                                                                                                                                                                                  |               |                       |                          | literal 'u:k'                                                                                                                                                                                  |                     | 'k' to<br>BSR<3:0>            |  |

| Cycles:                      | 1                                                                                                                                                                                  |               |                       | Example:                 | MOVLB                                                                                                                                                                                          | 0x5                 |                               |  |

| Q Cycle Activity             |                                                                                                                                                                                    |               |                       | Before Instru            | uction                                                                                                                                                                                         |                     |                               |  |

| Q1                           | Q2                                                                                                                                                                                 | Q3            | Q4                    | BSR reg                  | ister = 0x                                                                                                                                                                                     | 22                  |                               |  |

| Decode                       | Read<br>register 'f'                                                                                                                                                               | Execute       | Write<br>register 'p' | After Instruc<br>BSR reg |                                                                                                                                                                                                | 25                  |                               |  |

| Example:                     | MOVFP                                                                                                                                                                              | REG1, REG2    |                       | Note: For th             | ne PIC17C42                                                                                                                                                                                    | 2, only the lo      | ow four bits of               |  |

| Before Instr<br>REG1<br>REG2 |                                                                                                                                                                                    | 33,<br>11     |                       |                          | 3SR registe<br>ed. The uppe                                                                                                                                                                    |                     | sically imple-<br>ead as '0'. |  |

| After Instruc<br>REG1        |                                                                                                                                                                                    | 33,           |                       |                          |                                                                                                                                                                                                |                     |                               |  |

REG2

0x33

=

| TABLWT            | Table Wr    | ite      |         |                |

|-------------------|-------------|----------|---------|----------------|

| Example1:         | TABLWT      | 0, 1,    | REG     |                |

| Before Instruc    | ction       |          |         |                |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA356  |                |

| MEMORY            | (TBLPTR)    | =        | 0xFFFI  | F              |

| After Instruction | on (table v | vrite co | mpletio | n)             |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0x53    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA357  | 7              |

| MEMORY            | (TBLPTR -   | 1) =     | 0x5355  | 5              |

| Example 2:        | TABLWT      | 1, 0,    | REG     |                |

| Before Instruc    | ction       |          |         |                |

| REG               |             | =        | 0x53    |                |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x55    |                |

| TBLPTR            |             | =        | 0xA356  | 6              |

| MEMORY            | (TBLPTR)    | =        | 0xFFFI  | F              |

| After Instruction | on (table v | vrite co | mpletio | n)             |

| REG               | ,           | =        | 0x53    | ,              |

| TBLATH            |             | =        | 0xAA    |                |

| TBLATL            |             | =        | 0x53    |                |

| TBLPTR            |             | =        | 0xA356  | 6              |

| MEMORY            | (TBLPTR)    | =        | 0xAA5   | 3              |

|                   |             |          |         |                |

|                   | <br>ר       |          | г       |                |

| Program<br>Memory | 15          |          | 0       | Data<br>Memory |

|                   |             |          |         | wentory        |

|                   | 1 ( 🖳       | TBLPTR   |         |                |

|                                       | TBLPTR       |

|---------------------------------------|--------------|

| · · · · · · · · · · · · · · · · · · · |              |

| 16 bits                               | TBLAT 8 bits |

| TLR          | D                 | Table Late                                     | ch Read                                                                                                                                                               |                       |  |  |  |  |

|--------------|-------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|--|

| Syntax:      |                   | [label] T                                      | [label] TLRD t,f                                                                                                                                                      |                       |  |  |  |  |

| Operands:    |                   | 0 ≤ f ≤ 255<br>t ∈ [0,1]                       | $0 \le f \le 255$<br>t $\in [0,1]$                                                                                                                                    |                       |  |  |  |  |

| Operation:   |                   | lf t = 0,<br>TBLAT                             |                                                                                                                                                                       |                       |  |  |  |  |

|              |                   | lf t = 1,<br>TBLAT                             | $H \rightarrow f$                                                                                                                                                     |                       |  |  |  |  |

| State        | us Affected:      | None                                           |                                                                                                                                                                       |                       |  |  |  |  |

| Enco         | oding:            | 1010                                           | 1010 00tx ffff ffff                                                                                                                                                   |                       |  |  |  |  |

| Description: |                   | (TBLAT) into<br>is unaffecte<br>If t = 1; high | Read data from 16-bit table latch<br>(TBLAT) into file register 'f'. Table Latch<br>is unaffected.<br>If $t = 1$ ; high byte is read<br>If $t = 0$ ; low byte is read |                       |  |  |  |  |

|              |                   | with TABLR                                     | tion is used ir<br>□ to transfer c<br>ory to data me                                                                                                                  | lata from pro-        |  |  |  |  |

| Word         | ds:               | 1                                              |                                                                                                                                                                       |                       |  |  |  |  |

| Cycl         | es:               | 1                                              |                                                                                                                                                                       |                       |  |  |  |  |

| QC           | cle Activity:     |                                                |                                                                                                                                                                       |                       |  |  |  |  |

|              | Q1                | Q2                                             | Q3                                                                                                                                                                    | Q4                    |  |  |  |  |

|              | Decode            | Read<br>register<br>TBLATH or<br>TBLATL        | Execute                                                                                                                                                               | Write<br>register 'f' |  |  |  |  |

| <u>Exar</u>  | <u>mple</u> :     | TLRD t                                         | , RAM                                                                                                                                                                 |                       |  |  |  |  |

|              | Before Instru     | iction                                         |                                                                                                                                                                       |                       |  |  |  |  |

|              | t<br>RAM          | = 0<br>= ?                                     |                                                                                                                                                                       |                       |  |  |  |  |

|              | TBLAT             | = ?<br>= 0x00AF                                | (TBLATH =<br>(TBLATL =                                                                                                                                                |                       |  |  |  |  |

|              | After Instruct    | tion                                           |                                                                                                                                                                       |                       |  |  |  |  |

|              | RAM<br>TBLAT      | = 0xAF<br>= 0x00AF                             | (TBLATH =<br>(TBLATL =                                                                                                                                                | ,                     |  |  |  |  |

|              | Before Instru     | iction                                         |                                                                                                                                                                       |                       |  |  |  |  |

|              | t<br>RAM          | = 1<br>= ?                                     |                                                                                                                                                                       |                       |  |  |  |  |

|              | TBLAT             | = ?<br>= 0x00AF                                | (TBLATH =<br>(TBLATL =                                                                                                                                                | ,                     |  |  |  |  |

|              | After Instruct    | tion                                           |                                                                                                                                                                       |                       |  |  |  |  |

|              | RAM<br>TBLAT      | = 0x00<br>= 0x00AF                             | (TBLATH =<br>(TBLATL =                                                                                                                                                | ,                     |  |  |  |  |

|              | Program<br>Memory | 15                                             | 0                                                                                                                                                                     | Data<br>Memory        |  |  |  |  |

|              |                   |                                                |                                                                                                                                                                       |                       |  |  |  |  |

| • - •        |                   |                                                | . (                                                                                                                                                                   | ÷                     |  |  |  |  |

|              | 16 bits           |                                                | BLAT                                                                                                                                                                  | 8 bits                |  |  |  |  |

### Applicable Devices 42 R42 42A 43 R43 44

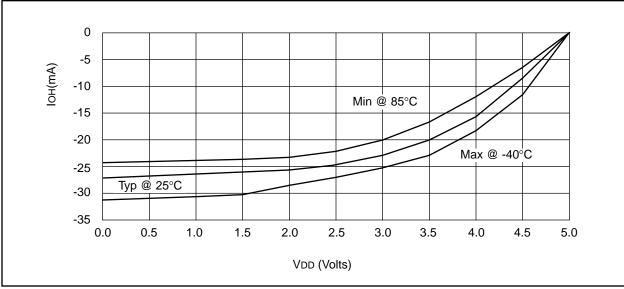

FIGURE 18-16: IOL vs. VOL, VDD = 3V

#### 21.6 Package Marking Information 40-Lead PDIP/CERDIP Example PIC17C43-25I/P L006 AABBCDE 9441CCA MICROCHIP MICROCHIP $\bigcirc$ 40 Lead CERDIP Windowed Example XXXXXXXXXXXX PIC17C44 XXXXXXXXXXXX /JW XXXXXXXXXXXX L184 AABBCDE 9444CCT 44-Lead PLCC Example $\mathcal{M}$ $\mathcal{M}$ MICROCHIP MICROCHIP PIC17C42 XXXXXXXXXX ○ <sub>XXXXXXXXX</sub> Ο -16I/L XXXXXXXXXX L013 AABBCDE 9445CCN 44-Lead MQFP Example $\mathcal{M}$ $\mathbf{w}$ XXXXXXXXXX PIC17C44 -25/PT XXXXXXXXXX XXXXXXXXXXX L247 AABBCDE 9450CAT $\cap$ $\cap$ 44-Lead TQFP Example \$ $\mathcal{Q}$ PIC17C44 XXXXXXXXXX -25/TQ XXXXXXXXXX XXXXXXXXXXX L247 AABBCDE 9450CAT $\cap$ $\cap$ Microchip part number information Legend: MM...M XX...X Customer specific information\* AA Year code (last 2 digits of calendar year) BΒ Week code (week of January 1 is week '01') С Facility code of the plant at which wafer is manufactured C = Chandler, Arizona, U.S.A., S = Tempe, Arizona, U.S.A. D Mask revision number Е Assembly code of the plant or country of origin in which part was assembled Note: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line thus limiting the number of available characters for customer specific information. Standard OTP marking consists of Microchip part number, year code, week code, facility code, mask rev#, and assembly code. For OTP marking beyond

code, facility code, mask rev#, and assembly code. For OTP marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

| Figure 6-12:                                                                                   | Program Counter using The CALL and                      |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Figure 6-13:                                                                                   | GOTO Instructions                                       |

| Figure 7-1:                                                                                    | TLWT Instruction Operation43                            |

| Figure 7-2:                                                                                    | TABLWT Instruction Operation                            |

| Figure 7-3:                                                                                    | TLRD Instruction Operation                              |

| Figure 7-4:                                                                                    | TABLRD Instruction Operation                            |

|                                                                                                |                                                         |

| Figure 7-5:                                                                                    | TABLWT Write Timing                                     |

| Figure 7-6:                                                                                    | (External Memory) 46<br>Consecutive TABLWT Write Timing |

|                                                                                                | (External Memory)47                                     |

| Figure 7-7:                                                                                    | TABLRD Timing48                                         |

| Figure 7-8:                                                                                    | TABLRD Timing (Consecutive TABLRD                       |

| 0                                                                                              | Instructions)                                           |

| Figure 9-1:                                                                                    | RA0 and RA1 Block Diagram53                             |

| Figure 9-2:                                                                                    | RA2 and RA3 Block Diagram                               |

|                                                                                                |                                                         |

| Figure 9-3:                                                                                    | RA4 and RA5 Block Diagram54                             |

| Figure 9-4:                                                                                    | Block Diagram of RB<7:4> and RB<1:0><br>Port Pins       |

| Figure 9-5:                                                                                    | Block Diagram of RB3 and RB2 Port Pins56                |

| 0                                                                                              |                                                         |

| Figure 9-6:                                                                                    | Block Diagram of RC<7:0> Port Pins                      |

| Figure 9-7:                                                                                    | PORTD Block Diagram                                     |

|                                                                                                | (in I/O Port Mode)60                                    |

| Figure 9-8:                                                                                    | PORTE Block Diagram                                     |

|                                                                                                | (in I/O Port Mode)                                      |

| Figure 9-9:                                                                                    | Successive I/O Operation                                |

| Figure 11-1:                                                                                   | T0STA Register (Address: 05h,                           |

| rigulo II I.                                                                                   | Unbanked)                                               |

| Figure 11-2:                                                                                   | Timer0 Module Block Diagram                             |

| 0                                                                                              |                                                         |

| Figure 11-3:                                                                                   | TMR0 Timing with External Clock                         |

|                                                                                                | (Increment on Falling Edge)68                           |