#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 33MHz                                                                    |

| Connectivity               | UART/USART                                                               |

| Peripherals                | POR, PWM, WDT                                                            |

| Number of I/O              | 33                                                                       |

| Program Memory Size        | 16KB (8K x 16)                                                           |

| Program Memory Type        | OTP                                                                      |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 454 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | External                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                 |

| Supplier Device Package    | 40-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44-33i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

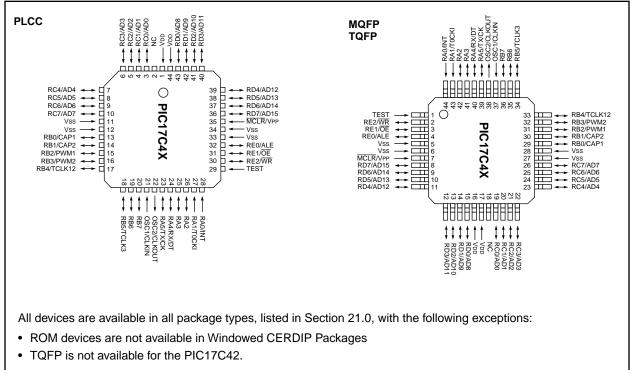

## Pin Diagrams Cont.'d

## 1.0 OVERVIEW

This data sheet covers the PIC17C4X group of the PIC17CXX family of microcontrollers. The following devices are discussed in this data sheet:

- PIC17C42

- PIC17CR42

- PIC17C42A

- PIC17C43

- PIC17CR43

- PIC17C44

The PIC17CR42, PIC17C42A, PIC17C43, PIC17CR43, and PIC17C44 devices include architectural enhancements over the PIC17C42. These enhancements will be discussed throughout this data sheet.

The PIC17C4X devices are 40/44-Pin, EPROM/ROM-based members of the versatile PIC17CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC17CXX has enhanced core features, 16-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 16-bit wide instruction word with a separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 55 instructions (reduced instruction set) are available in the PIC17C42 and 58 instructions in all the other devices. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance. For mathematical intensive applications all devices, except the PIC17C42, have a single cycle 8 x 8 Hardware Multiplier.

PIC17CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC17C4X devices have up to 454 bytes of RAM and 33 I/O pins. In addition, the PIC17C4X adds several peripheral features useful in many high performance applications including:

- · Four timer/counters

- Two capture inputs

- Two PWM outputs

- A Universal Synchronous Asynchronous Receiver Transmitter (USART)

These special features reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LF oscillator is for low frequency crystals and minimizes power consumption, XT is a standard crystal, and the EC is for external clock input. The SLEEP (power-down) mode offers additional power saving. The user can wake-up the chip from SLEEP through several external and internal interrupts and device resets.

There are four configuration options for the device operational modes:

- Microprocessor

- Microcontroller

- Extended microcontroller

- Protected microcontroller

The microprocessor and extended microcontroller modes allow up to 64K-words of external program memory.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software malfunction.

Table 1-1 lists the features of the PIC17C4X devices.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

The PIC17C4X fits perfectly in applications ranging from precise motor control and industrial process control to automotive, instrumentation, and telecom applications. Other applications that require extremely fast execution of complex software programs or the flexibility of programming the software code as one of the last steps of the manufacturing process would also be well suited. The EPROM technology makes customization of application programs (with unique security codes, combinations, model numbers, parameter storage, etc.) fast and convenient. Small footprint package options make the PIC17C4X ideal for applications with space limitations that require high performance. High speed execution, powerful peripheral features, flexible I/O, and low power consumption all at low cost make the PIC17C4X ideal for a wide range of embedded control applications.

## 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X and PIC16CXX families of microcontrollers will see the architectural enhancements that have been implemented. These enhancements allow the device to be more efficient in software and hardware requirements. Please refer to Appendix A for a detailed list of enhancements and modifications. Code written for PIC16C5X or PIC16CXX can be easily ported to PIC17CXX family of devices (Appendix B).

## 1.2 Development Support

The PIC17CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a universal programmer, a "C" compiler, and fuzzy logic support tools.

<sup>© 1996</sup> Microchip Technology Inc.

NOTES:

| TABLE 3-1. |            |                      |                 |               |                |                                                                                                                                                                             |

|------------|------------|----------------------|-----------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name       | DIP<br>No. | PLCC<br>No.          | QFP<br>No.      | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                 |

|            |            |                      |                 |               |                | PORTD is a bi-directional I/O Port.                                                                                                                                         |

| RD0/AD8    | 40         | 43                   | 15              | I/O           | TTL            | This is also the upper byte of the 16-bit system bus in                                                                                                                     |

| RD1/AD9    | 39         | 42                   | 14              | I/O           | TTL            | microprocessor mode or extended microprocessor mode                                                                                                                         |

| RD2/AD10   | 38         | 41                   | 13              | I/O           | TTL            | or extended microcontroller mode. In multiplexed system                                                                                                                     |

| RD3/AD11   | 37         | 40                   | 12              | I/O           | TTL            | bus configuration these pins are address output as well as data input or output.                                                                                            |

| RD4/AD12   | 36         | 39                   | 11              | I/O           | TTL            |                                                                                                                                                                             |

| RD5/AD13   | 35         | 38                   | 10              | I/O           | TTL            |                                                                                                                                                                             |

| RD6/AD14   | 34         | 37                   | 9               | I/O           | TTL            |                                                                                                                                                                             |

| RD7/AD15   | 33         | 36                   | 8               | I/O           | TTL            |                                                                                                                                                                             |

|            |            |                      |                 |               |                | PORTE is a bi-directional I/O Port.                                                                                                                                         |

| RE0/ALE    | 30         | 32                   | 4               | I/O           | TTL            | In microprocessor mode or extended microcontroller<br>mode, it is the Address Latch Enable (ALE) output.<br>Address should be latched on the falling edge of ALE<br>output. |

| RE1/OE     | 29         | 31                   | 3               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Output Enable ( $\overline{OE}$ ) control output (active low).                                                |

| RE2/WR     | 28         | 30                   | 2               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Write Enable (WR) control output (active low).                                                                |

| TEST       | 27         | 29                   | 1               | I             | ST             | Test mode selection control input. Always tie to Vss for nor-<br>mal operation.                                                                                             |

| Vss        | 10,<br>31  | 11,<br>12,<br>33, 34 | 5, 6,<br>27, 28 | Р             |                | Ground reference for logic and I/O pins.                                                                                                                                    |

| Vdd        | 1          | 1, 44                | 16, 17          | Р             |                | Positive supply for logic and I/O pins.                                                                                                                                     |

| TABLE 3-1: | PINOUT DESCRIPTIONS |

|------------|---------------------|

|------------|---------------------|

Legend: I = Input only; O = Output only; I/O = Input/Output; P = Power; — = Not Used; TTL = TTL input; ST = Schmitt Trigger input.

### 6.2.2.1 ALU STATUS REGISTER (ALUSTA)

The ALUSTA register contains the status bits of the Arithmetic and Logic Unit and the mode control bits for the indirect addressing register.

As with all the other registers, the ALUSTA register can be the destination for any instruction. If the ALUSTA register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the ALUSTA register as destination may be different than intended.

For example, CLRF ALUSTA will clear the upper four bits and set the Z bit. This leaves the ALUSTA register as 0000u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions be used to alter the ALUSTA register because these instructions do not affect any status bit. To see how other instructions affect the status bits, see the "Instruction Set Summary."

| Note | 1: The C and DC bits operate as a borrow<br>out bit in subtraction. See the SUBLW and<br>SUBWF instructions for examples. |

|------|---------------------------------------------------------------------------------------------------------------------------|

| Note | 2: The overflow bit will be set if the 2's com-<br>plement result exceeds +127 or is less<br>than -128.                   |

Arithmetic and Logic Unit (ALU) is capable of carrying out arithmetic or logical operations on two operands or a single operand. All single operand instructions operate either on the WREG register or a file register. For two operand instructions, one of the operands is the WREG register and the other one is either a file register or an 8-bit immediate constant.

| FS3      | FS2                                  | FS1                                                                | FS0                                                  | OV                                                      | Z                                   | DC                       | С          | R = Readable bit                                                  |

|----------|--------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|-------------------------------------|--------------------------|------------|-------------------------------------------------------------------|

| bit7     | 1                                    | 1                                                                  |                                                      |                                                         |                                     | I                        | bit0       | W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)      |

| bit 7-6: | 01 = Pos                             | FSR1 Mo<br>t auto-dect<br>t auto-incre<br>t value de               | rement FS<br>ement FSI                               | R1 value<br>R1 value                                    |                                     |                          |            |                                                                   |

| bit 5-4: | 01 = Pos                             | FSR0 Mo<br>t auto-deci<br>t auto-incre<br>0 value de               | rement FS<br>ement FSI                               | R0 value<br>R0 value                                    |                                     |                          |            |                                                                   |

| bit 3:   | which cau<br>1 = Overfl              | s used for<br>uses the si                                          | gn bit (bit7<br>ed for sign                          | ') to chang                                             |                                     |                          |            | overflow of the 7-bit magnitude,                                  |

| bit 2:   |                                      | esult of an                                                        |                                                      |                                                         | peration is operation is            |                          |            |                                                                   |

| bit 1:   | For ADDW<br>1 = A carr $0 = No ca$   | •                                                                  | LW instruc<br>the 4th lo<br>m the 4th                | w order bi<br>low order                                 | t of the res<br>bit of the re<br>I. |                          | d          |                                                                   |

| bit 0:   | 1 = A carr<br>Note that<br>(RRCF, RL | F and ADD<br>y-out from<br>a subtrac<br>CF) instru-<br>rry-out fro | the most<br>tion is exe<br>ctions, this<br>m the mos | significant<br>cuted by a<br>bit is load<br>t significa | ded with eit<br>nt bit of the       | two's com<br>her the hig | plement of | the second operand. For rotate<br>der bit of the source register. |

## FIGURE 6-7: ALUSTA REGISTER (ADDRESS: 04h, UNBANKED)

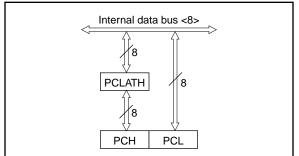

## 6.7 Program Counter Module

The Program Counter (PC) is a 16-bit register. PCL, the low byte of the PC, is mapped in the data memory. PCL is readable and writable just as is any other register. PCH is the high byte of the PC and is not directly addressable. Since PCH is not mapped in data or program memory, an 8-bit register PCLATH (PC high latch) is used as a holding latch for the high byte of the PC. PCLATH is mapped into data memory. The user can read or write PCH through PCLATH.

The 16-bit wide PC is incremented after each instruction fetch during Q1 unless:

- Modified by GOTO, CALL, LCALL, RETURN, RETLW, or RETFIE instruction

- · Modified by an interrupt response

- Due to destination write to PCL by an instruction

"Skips" are equivalent to a forced NOP cycle at the skipped address.

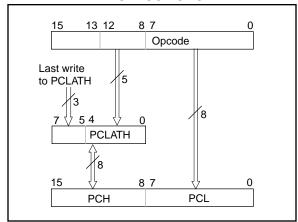

Figure 6-11 and Figure 6-12 show the operation of the program counter for various situations.

## FIGURE 6-11: PROGRAM COUNTER OPERATION

FIGURE 6-12: PROGRAM COUNTER USING THE CALL AND GOTO INSTRUCTIONS

Using Figure 6-11, the operations of the PC and PCLATH for different instructions are as follows:

- a) <u>LCALL instructions</u>: An 8-bit destination address is provided in the instruction (opcode). PCLATH is unchanged. PCLATH → PCH Opcode<7:0> → PCL

- b) Read instructions on PCL: Any instruction that reads PCL. PCL  $\rightarrow$  data bus  $\rightarrow$  ALU or destination PCH  $\rightarrow$  PCLATH

- c) <u>Write instructions on PCL</u>: Any instruction that writes to PCL. 8-bit data  $\rightarrow$  data bus  $\rightarrow$  PCL PCLATH  $\rightarrow$  PCH

- d) <u>Read-Modify-Write instructions on PCL:</u> Any instruction that does a read-write-modify operation on PCL, such as ADDWF PCL. Read: PCL → data bus → ALU Write: 8-bit result → data bus → PCL

- $\mathsf{PCLATH} \to \mathsf{PCH}$

- e) <u>RETURN instruction:</u> PCH  $\rightarrow$  PCLATH Stack<MRU>  $\rightarrow$  PC<15:0>

Using Figure 6-12, the operation of the PC and PCLATH for GOTO and CALL instructions is a follows:

CALL, GOTO instructions: A 13-bit destination address is provided in the instruction (opcode). Opcode<12:0>  $\rightarrow$  PC <12:0>

$PC<15:13> \rightarrow PCLATH<7:5>$

Opcode<12:8>  $\rightarrow$  PCLATH <4:0>

The read-modify-write only affects the PCL with the result. PCH is loaded with the value in the PCLATH. For example, ADDWF PCL will result in a jump within the current page. If PC = 03F0h, WREG = 30h and PCLATH = 03h before instruction, PC = 0320h after the instruction. To accomplish a true 16-bit computed jump, the user needs to compute the 16-bit destination address, write the high byte to PCLATH and then write the low value to PCL.

The following PC related operations do not change PCLATH:

- a) LCALL, RETLW, and RETFIE instructions.

- b) Interrupt vector is forced onto the PC.

- c) Read-modify-write instructions on PCL (e.g.BSF PCL).

Example 8-3 shows the sequence to do a 16 x 16 unsigned multiply. Equation 8-1 shows the algorithm that is used. The 32-bit result is stored in 4 registers RES3:RES0.

#### **EQUATION 8-1:** 16 x 16 UNSIGNED MULTIPLICATION ALGORITHM

=

- ARG1H:ARG1L \* ARG2H:ARG2L RES3:RES0 =

- (ARG1H \* ARG2H \* 2<sup>16</sup>) +

(ARG1H \* ARG2L \* 2<sup>8</sup>) +

(ARG1L \* ARG2H \* 2<sup>8</sup>) (ARG1L \* ARG2L)

+

## EXAMPLE 8-3: 16 x 16 MULTIPLY ROUTINE

|   |                                  |                            | ; ARG1L * ARG2L -<br>; PRODH:PRODL  | > |

|---|----------------------------------|----------------------------|-------------------------------------|---|

| ; |                                  | PRODH, RES1<br>PRODL, RES0 | ;                                   |   |

| , |                                  |                            | ; ARG1H * ARG2H -<br>; PRODH:PRODL  | > |

| ; |                                  | PRODH, RES3<br>PRODL, RES2 |                                     |   |

| - | MOVFP<br>MULWF                   |                            | ; ARG1L * ARG2H -<br>; PRODH:PRODL  | > |

|   | ADDWF<br>MOVFP<br>ADDWFC         |                            | ; Add cross<br>; products<br>;      |   |

| ; | ADDWFC                           | RES3, F<br>ARG1H, WREG     | ;                                   |   |

|   | MULWF                            | ARG2L                      | ; ARG1H * ARG2L -<br>; PRODH:PRODL  | > |

|   | ADDWF<br>MOVFP<br>ADDWFC<br>CLRF |                            | ; Add cross<br>; products<br>;<br>; |   |

## 9.0 I/O PORTS

The PIC17C4X devices have five I/O ports, PORTA through PORTE. PORTB through PORTE have a corresponding Data Direction Register (DDR), which is used to configure the port pins as inputs or outputs. These five ports are made up of 33 I/O pins. Some of these ports pins are multiplexed with alternate functions.

PORTC, PORTD, and PORTE are multiplexed with the system bus. These pins are configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, these pins are general purpose I/O.

PORTA and PORTB are multiplexed with the peripheral features of the device. These peripheral features are:

- Timer modules

- Capture module

- PWM module

- USART/SCI module

- External Interrupt pin

When some of these peripheral modules are turned on, the port pin will automatically configure to the alternate function. The modules that do this are:

- PWM module

- USART/SCI module

When a pin is automatically configured as an output by a peripheral module, the pins data direction (DDR) bit is unknown. After disabling the peripheral module, the user should re-initialize the DDR bit to the desired configuration.

The other peripheral modules (which require an input) must have their data direction bit configured appropriately.

**Note:** A pin that is a peripheral input, can be configured as an output (DDRx<y> is cleared). The peripheral events will be determined by the action output on the port pin.

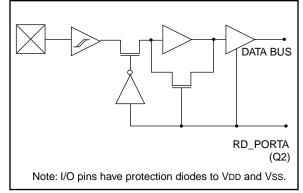

## 9.1 PORTA Register

PORTA is a 6-bit wide latch. PORTA does not have a corresponding Data Direction Register (DDR).

Reading PORTA reads the status of the pins.

The RA1 pin is multiplexed with TMR0 clock input, and RA4 and RA5 are multiplexed with the USART functions. The control of RA4 and RA5 as outputs is automatically configured by the USART module.

9.1.1 USING RA2, RA3 AS OUTPUTS

The RA2 and RA3 pins are open drain outputs. To use the RA2 or the RA3 pin(s) as output(s), simply write to the PORTA register the desired value. A '0' will cause the pin to drive low, while a '1' will cause the pin to float (hi-impedance). An external pull-up resistor should be used to pull the pin high. Writes to PORTA will not affect the other pins.

| Note: | When using the RA2 or RA3 pin(s) as out-<br>put(s), read-modify-write instructions (such<br>as BCF, BSF, BTG) on PORTA are not rec-<br>ommended.<br>Such operations read the port pins, do the<br>desired operation, and then write this value<br>to the data latch. This may inadvertently<br>cause the RA2 or RA3 pins to switch from<br>input to output (or vice-versa).<br>It is recommended to use a shadow regis-<br>ter for PORTA. Do the bit operations on this<br>shadow register and then move it to<br>PORTA. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

#### FIGURE 9-1: RA0 AND RA1 BLOCK DIAGRAM

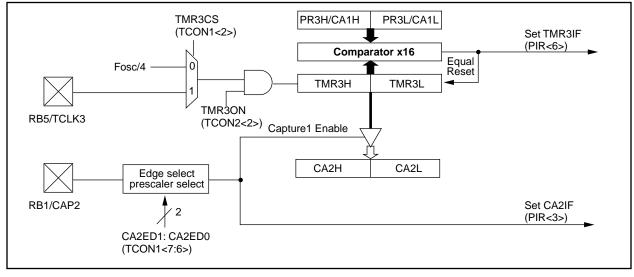

#### 12.2.1 ONE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 12-7. The timer increments until it equals the period register and then resets to 0000h. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

This mode is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode, and the corresponding Interrupt bit CA1IF is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h.

Capture2 is active in this mode. The CA2ED1 and CA2ED0 bits determine the event on which capture will occur. The possible events are:

- · Capture on every falling edge

- Capture on every rising edge

- · Capture every 4th rising edge

- · Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CA2IF bit. This interrupt can be enabled by setting the corresponding mask bit CA2IE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CA2IF interrupt flag bit must be cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip reset. Capture pin RB1/CAP2 is a multiplexed pin. When used as a port pin, Capture2 is not disabled. However, the user can simply disable the Capture2 interrupt by clearing CA2IE. If RB1/CAP2 is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt.

The input on capture pin RB1/CAP2 is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the Timer3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 12-1.

## EXAMPLE 12-1: SEQUENCE TO READ CAPTURE REGISTERS

| MOVLB 3              | ;Select Bank 3          |

|----------------------|-------------------------|

| MOVPF CA2L,LO_BYTE   | ;Read Capture2 low      |

|                      | ;byte, store in LO_BYTE |

| MOVPF CA2H, HI_BYTE  | ;Read Capture2 high     |

|                      | ;byte, store in HI_BYTE |

| MOVPF TCON2,STAT_VAL | ;Read TCON2 into file   |

|                      | ;STAT_VAL               |

#### FIGURE 12-7: TIMER3 WITH ONE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

| BAUD        | Fosc = 3 | 3 MHz  | SPBRG              | Fosc = 2 | 5 MHz  | SPBRG              | Fosc = 2 | 0 MHz  | SPBRG              | Fosc = 1 | 6 MHz  | SPBRG              |

|-------------|----------|--------|--------------------|----------|--------|--------------------|----------|--------|--------------------|----------|--------|--------------------|

| RATE<br>(K) | KBAUD    | %ERROR | value<br>(decimal) |

| 0.3         | NA       | _      | —                  | NA       | _      |                    | NA       | _      | _                  | NA       | _      | -                  |

| 1.2         | NA       | _      | _                  | NA       | _      | _                  | 1.221    | +1.73  | 255                | 1.202    | +0.16  | 207                |

| 2.4         | 2.398    | -0.07  | 214                | 2.396    | 0.14   | 162                | 2.404    | +0.16  | 129                | 2.404    | +0.16  | 103                |

| 9.6         | 9.548    | -0.54  | 53                 | 9.53     | -0.76  | 40                 | 9.469    | -1.36  | 32                 | 9.615    | +0.16  | 25                 |

| 19.2        | 19.09    | -0.54  | 26                 | 19.53    | +1.73  | 19                 | 19.53    | +1.73  | 15                 | 19.23    | +0.16  | 12                 |

| 76.8        | 73.66    | -4.09  | 6                  | 78.13    | +1.73  | 4                  | 78.13    | +1.73  | 3                  | 83.33    | +8.51  | 2                  |

| 96          | 103.12   | +7.42  | 4                  | 97.65    | +1.73  | 3                  | 104.2    | +8.51  | 2                  | NA       | _      | _                  |

| 300         | 257.81   | -14.06 | 1                  | 390.63   | +30.21 | 0                  | 312.5    | +4.17  | 0                  | NA       | _      | -                  |

| 500         | 515.62   | +3.13  | 0                  | NA       | _      | _                  | NA       | _      | _                  | NA       | _      | -                  |

| HIGH        | 515.62   | _      | 0                  | _        | _      | 0                  | 312.5    | _      | 0                  | 250      | _      | 0                  |

| LOW         | 2.014    | —      | 255                | 1.53     | —      | 255                | 1.221    | —      | 255                | 0.977    | _      | 255                |

## TABLE 13-4: BAUD RATES FOR ASYNCHRONOUS MODE

| BAUD<br>RATE | Fosc = 10 MH | Iz     | SPBRG<br>value     | Fosc = 7.159 | ) MHz  | SPBRG<br>value     | FOSC = 5.068 | 8 MHz  | SPBRG<br>value     |

|--------------|--------------|--------|--------------------|--------------|--------|--------------------|--------------|--------|--------------------|

| (K)          | KBAUD        | %ERROR | (decimal)          | KBAUD        | %ERROR | (decimal)          | KBAUD        | %ERROR | (decimal)          |

| 0.3          | NA           | _      | _                  | NA           | _      | _                  | 0.31         | +3.13  | 255                |

| 1.2          | 1.202        | +0.16  | 129                | 1.203        | _0.23  | 92                 | 1.2          | 0      | 65                 |

| 2.4          | 2.404        | +0.16  | 64                 | 2.380        | -0.83  | 46                 | 2.4          | 0      | 32                 |

| 9.6          | 9.766        | +1.73  | 15                 | 9.322        | -2.90  | 11                 | 9.9          | -3.13  | 7                  |

| 19.2         | 19.53        | +1.73  | 7                  | 18.64        | -2.90  | 5                  | 19.8         | +3.13  | 3                  |

| 76.8         | 78.13        | +1.73  | 1                  | NA           | _      | —                  | 79.2         | +3.13  | 0                  |

| 96           | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 300          | NA           | _      | —                  | NA           | _      | —                  | NA           | _      | _                  |

| 500          | NA           | _      | _                  | NA           | _      | _                  | NA           | _      | _                  |

| HIGH         | 156.3        | _      | 0                  | 111.9        | _      | 0                  | 79.2         | _      | 0                  |

| LOW          | 0.610        | —      | 255                | 0.437        | —      | 255                | 0.309        | _      | 2 <b>55</b>        |

| BAUD         | Fosc = 3.579 | MHz    | SPBRG              | Fosc = 1 MH  | z      | SPBRG              | FOSC = 32.76 | 8 kHz  | SPBRG              |

| RATE<br>(K)  | KBAUD        | %ERROR | value<br>(decimal) | KBAUD        | %ERROR | value<br>(decimal) | KBAUD        | %ERROR | value<br>(decimal) |

| 0.3          | 0.301        | +0.23  | 185                | 0.300        | +0.16  | 51                 | 0.256        | -14.67 | 1                  |

| 1.2          | 1.190        | -0.83  | 46                 | 1.202        | +0.16  | 12                 | NA           | —      | —                  |

| 2.4          | 2.432        | +1.32  | 22                 | 2.232        | -6.99  | 6                  | NA           | —      | —                  |

| 9.6          | 9.322        | -2.90  | 5                  | NA           | _      | _                  | NA           | _      | _                  |

| 19.2         | 18.64        | -2.90  | 2                  | NA           | —      | —                  | NA           | —      | —                  |

| 76.8         | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 96           | NA           | _      | _                  | NA           | _      | _                  | NA           | _      | _                  |

| 300          | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 500          | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| HIGH         | 55.93        | _      | 0                  | 15.63        | _      | 0                  | 0.512        | _      | 0                  |

| l mon        |              |        |                    |              |        |                    |              |        |                    |

# PIC17C4X

| DCF        | SNZ                                                          | Decreme                                                  | ent f, skij                                                                             | o if no                                            | ot O                                                                    |  |  |  |  |

|------------|--------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| Synt       | tax:                                                         | [ <i>label</i> ] D                                       | CFSNZ                                                                                   | f,d                                                |                                                                         |  |  |  |  |

|            |                                                              | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                  | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$                       |                                                    |                                                                         |  |  |  |  |

| •          |                                                              | .,                                                       | (f) $-1 \rightarrow$ (dest);<br>skip if not 0                                           |                                                    |                                                                         |  |  |  |  |

| Stat       | us Affected:                                                 | None                                                     |                                                                                         |                                                    |                                                                         |  |  |  |  |

| Encoding:  |                                                              | 0010                                                     | 011d                                                                                    | ffff                                               | ffff                                                                    |  |  |  |  |

| Des        | cription:                                                    | WREG. If '<br>back in reg<br>If the resul<br>which is al | 'd' is 0 the<br>d' is 1 the<br>gister 'f'.<br>t is not 0, t<br>ready fetc<br>DP is exec | e result<br>result<br>he nex<br>hed, is<br>uted in | is placed in<br>is placed<br>t instruction,<br>discarded,<br>stead mak- |  |  |  |  |

| Wor        | ds:                                                          | 1                                                        |                                                                                         |                                                    |                                                                         |  |  |  |  |

| Cycl       | es:                                                          | 1(2)                                                     |                                                                                         |                                                    |                                                                         |  |  |  |  |

| QC         | ycle Activity:                                               |                                                          |                                                                                         |                                                    |                                                                         |  |  |  |  |

|            | Q1                                                           | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |  |  |  |

|            | Decode                                                       | Read<br>register 'f'                                     | Execu                                                                                   | ıte                                                | Write to destination                                                    |  |  |  |  |

| lf sk      | ip:                                                          |                                                          |                                                                                         |                                                    |                                                                         |  |  |  |  |

|            | Q1                                                           | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |  |  |  |

|            | Forced NOP                                                   | NOP                                                      | Execu                                                                                   | ute                                                | NOP                                                                     |  |  |  |  |

| <u>Exa</u> | <u>mple</u> :                                                | HERE<br>ZERO<br>NZERO                                    | DCFSNZ<br>:<br>:                                                                        | TEMP                                               | P, 1                                                                    |  |  |  |  |

|            | Before Instru<br>TEMP_V                                      |                                                          | ?                                                                                       |                                                    |                                                                         |  |  |  |  |

|            | After Instruct<br>TEMP_V<br>If TEMP_<br>PC<br>If TEMP_<br>PC | ALUE =<br>VALUE =<br>=                                   | 0;<br>Addre:<br>0;                                                                      | _VALU<br>ss (ze<br>ss (nz                          | RO)                                                                     |  |  |  |  |

| Syntax:<br>Operand | de.         |                                                                                     | 0010                                                                                                   |                                     | Unconditional Branch             |  |  |  |  |  |  |

|--------------------|-------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------|--|--|--|--|--|--|

| Operand            | 18.         | $0 \le k \le 81$                                                                    | ~                                                                                                      | i.                                  |                                  |  |  |  |  |  |  |

|                    |             |                                                                                     | •                                                                                                      |                                     |                                  |  |  |  |  |  |  |

| Operatio           | on:         | k<12:8> -                                                                           | $k \rightarrow PC<12:0>;$<br>$k<12:8> \rightarrow PCLATH<4:0>,$<br>$PC<15:13> \rightarrow PCLATH<7:5>$ |                                     |                                  |  |  |  |  |  |  |

| Status A           | Affected:   | None                                                                                |                                                                                                        |                                     |                                  |  |  |  |  |  |  |

| Encodin            | ig:         | 110k                                                                                | kkkk                                                                                                   | kkkk                                | kkkl                             |  |  |  |  |  |  |

| Descript           |             | anywhere w<br>The thirtee<br>loaded into<br>upper eigh<br>PCLATH. o<br>instruction. | n bit imm<br>PC bits<br>t bits of P<br>30T0 is a                                                       | ediate va<br><12:0>. 1<br>C are loa | alue is<br>Then the<br>aded into |  |  |  |  |  |  |

| Words:             |             | 1                                                                                   |                                                                                                        |                                     |                                  |  |  |  |  |  |  |

| Cycles:            |             | 2                                                                                   |                                                                                                        |                                     |                                  |  |  |  |  |  |  |

| Q Cycle            | Activity:   |                                                                                     |                                                                                                        |                                     |                                  |  |  |  |  |  |  |

|                    | Q1          | Q2                                                                                  | Q3                                                                                                     | 5                                   | Q4                               |  |  |  |  |  |  |

| E                  | Decode      | Read literal<br>'k'<7:0>                                                            | Execu                                                                                                  | ute                                 | NOP                              |  |  |  |  |  |  |

| For                | ced NOP     | NOP                                                                                 | Execu                                                                                                  | ute                                 | NOP                              |  |  |  |  |  |  |

| Example            | <u>e</u> :  | GOTO THE                                                                            | RE                                                                                                     |                                     |                                  |  |  |  |  |  |  |

| Afte               | er Instruct | tion                                                                                |                                                                                                        |                                     |                                  |  |  |  |  |  |  |

|                    | PC =        | Address (TH                                                                         | HERE )                                                                                                 |                                     |                                  |  |  |  |  |  |  |

# PIC17C4X

| SUBWF                                   | Sub                              | otrac             | t WREG                                           | from             | f                |                       |          |

|-----------------------------------------|----------------------------------|-------------------|--------------------------------------------------|------------------|------------------|-----------------------|----------|

| Syntax:                                 | [ lab                            | oel]              | SUBWF                                            | f,d              |                  |                       | -        |

| Operands:                               | -                                | f ≤ 25<br>[0,1]   | 55                                               |                  |                  |                       | :        |

| Operation:                              | (f) –                            | · (W)             | $\rightarrow$ (dest                              | )                |                  |                       |          |

| Status Affected:                        | OV,                              | C, D              | C, Z                                             |                  |                  |                       | (        |

| Encoding:                               | 00                               | 00                | 010d                                             | fff              | f                | ffff                  | :        |

| Description:                            | com<br>resu                      | pleme<br>It is si | VREG fro<br>ent metho<br>tored in W<br>tored bac | d). If '<br>/REG | d' is<br>. If 'c | 0 the<br>I' is 1 the  | l        |

| Words:                                  | 1                                |                   |                                                  |                  |                  |                       |          |

| Cycles:                                 | 1                                |                   |                                                  |                  |                  |                       | ,        |

| Q Cycle Activity:                       |                                  |                   |                                                  |                  |                  |                       |          |

| Q1                                      | Qź                               |                   | Q3                                               | 3                |                  | Q4                    |          |

| Decode                                  | Rea<br>registe                   |                   | Execu                                            | ute              |                  | Vrite to<br>stination |          |

|                                         |                                  |                   | DECI                                             | 1                | ue               | Sunation              |          |

| Example 1:                              | SUB                              | M F.              | REG1,                                            | T                |                  |                       |          |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 3<br>= 2<br>= ?      |                   |                                                  |                  |                  |                       | <u> </u> |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= 1<br>= 2<br>= 1<br>= 0 | ;                 | result is p                                      | oositiv          | е                |                       |          |

| Example 2:                              |                                  |                   |                                                  |                  |                  |                       |          |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 2<br>= 2<br>= ?      |                   |                                                  |                  |                  |                       | <u> </u> |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= 0<br>= 2<br>= 1<br>= 1 | ;                 | result is z                                      | zero             |                  |                       |          |

| Example 3:                              |                                  |                   |                                                  |                  |                  |                       |          |

| Before Instru<br>REG1<br>WREG<br>C      | uction<br>= 1<br>= 2<br>= ?      |                   |                                                  |                  |                  |                       | ļ        |

| After Instruc<br>REG1<br>WREG<br>C<br>Z | tion<br>= F<br>= 2<br>= 0<br>= 0 |                   | result is r                                      | negatir          | ve               |                       |          |

| SUBWFB                            |                |                                  | t WREG                                                             | from                           | n f w                 | vith                  |

|-----------------------------------|----------------|----------------------------------|--------------------------------------------------------------------|--------------------------------|-----------------------|-----------------------|

| Syntax:                           |                | Borrow                           | SUBWF                                                              | Bfo                            | 1                     |                       |

| Operands:                         |                | $0 \le f \le 2$                  |                                                                    | , u                            |                       |                       |

| Operands.                         |                | d ∈ [0,1                         | ]                                                                  |                                |                       |                       |

| Operation:                        |                | (f) – (W)                        | $) - \overline{C} \rightarrow (0)$                                 | dest)                          |                       |                       |

| Status Affect                     | ed:            | OV, C, E                         | DC, Z                                                              |                                |                       |                       |

| Encoding:                         |                | 0000                             | 001d                                                               | fff                            | f                     | ffff                  |

| Description:                      |                | (borrow)<br>ment me<br>stored in | WREG an<br>from regis<br>thod). If 'd'<br>WREG. If<br>ack in regis | ter 'f'<br>is 0 tl<br>'d' is ´ | (2's<br>he r<br>1 the | comple-<br>esult is   |

| Words:                            |                | 1                                |                                                                    |                                |                       |                       |

| Cycles:                           |                | 1                                |                                                                    |                                |                       |                       |

| Q Cycle Activ                     | /ity:          |                                  |                                                                    |                                |                       |                       |

| Q1                                |                | Q2                               | Q3                                                                 |                                |                       | Q4                    |

| Decod                             | -              | Read<br>egister 'f'              | Execu                                                              | ıte                            |                       | Vrite to<br>stination |

| Example 1:                        |                | SUBWFB                           | REG1,                                                              | 1                              |                       |                       |

| Before Ir                         | nstructio      | on                               |                                                                    |                                |                       |                       |

| REG<br>WRE<br>C                   |                | 0x19<br>0x0D<br>1                | (0001<br>(0000                                                     |                                | '                     |                       |

| After Ins                         | truction       | 1                                |                                                                    |                                |                       |                       |

| REG<br>WRE<br>C                   | EG =<br>=      | 0x0C<br>0x0D<br>1                | (0000<br>(0000<br>; <b>resul</b> t                                 | 110                            | 1)                    | e                     |

| Z                                 | =              | 0                                |                                                                    |                                |                       |                       |

| Example2:                         |                | UBWFB                            | REG1,0                                                             |                                |                       |                       |

| Before Ir<br>REG<br>WRE<br>C      | 61 =           | 0x1B                             | (0001<br>(0001                                                     |                                | ,                     |                       |

| After Ins                         | truction       | 1                                |                                                                    |                                |                       |                       |

| REG                               |                | 0x1B                             | (0001                                                              | 101                            | 1)                    |                       |

| WRE<br>C<br>Z                     | EG =<br>=<br>= | 0x00<br>1<br>1                   | ; resul                                                            | t is ze                        | ro                    |                       |

| Example3:                         | S              | UBWFB                            | REG1,1                                                             |                                |                       |                       |

| Before Ir                         |                | on                               |                                                                    |                                |                       |                       |

| REG<br>WRE<br>C                   |                | 0x03<br>0x0E<br>1                | (0000<br>(0000                                                     |                                |                       |                       |

| After Ins<br>REG<br>WRE<br>C<br>Z | 61 =           | 0xF5<br>0x0E<br>0<br>0           | (1111<br>(0000<br>; <b>resul</b> t                                 | 110                            | 1)                    | ?'s comp]<br>ve       |

## Applicable Devices 42 R42 42A 43 R43 44

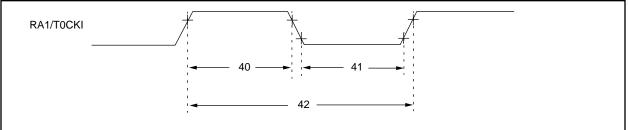

## FIGURE 17-5: TIMER0 CLOCK TIMINGS

## TABLE 17-5: TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sum  | Characteristic         |                | Min               | Tunt | Мах   | Unito | Conditions         |

|------------------|------|------------------------|----------------|-------------------|------|-------|-------|--------------------|

| NO.              | Sym  | Characteristic         |                | IVIIII            | Typ† | IVIAX | Units | Conditions         |

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5TCY + 20 §     | —    | _     | ns    |                    |

|                  |      |                        | With Prescaler | 10*               | —    | —     | ns    |                    |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20 §     | —    | —     | ns    |                    |

|                  |      |                        | With Prescaler | 10*               | —    | —     | ns    |                    |

| 42               | Tt0P | T0CKI Period           | •              | <u>Tcy + 40</u> § | —    | —     | ns    | N = prescale value |

|                  |      |                        |                | N                 |      |       |       | (1, 2, 4,, 256)    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

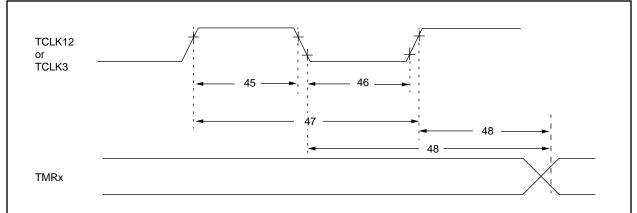

## FIGURE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK TIMINGS

## TABLE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK REQUIREMENTS

| Parameter |           |                                                               |                        | Тур |          |       |                                    |

|-----------|-----------|---------------------------------------------------------------|------------------------|-----|----------|-------|------------------------------------|

| No.       | Sym       | Characteristic                                                | Min                    | †   | Max      | Units | Conditions                         |

| 45        | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5 TCY + 20 §         |     | _        | ns    |                                    |

| 46        | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5 TCY + 20 §         |     |          | ns    |                                    |

| 47        | Tt123P    | TCLK12 and TCLK3 input period                                 | <u>Tcy + 40</u> §<br>N |     |          | ns    | N = prescale value<br>(1, 2, 4, 8) |

| 48        | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc §                |     | 6 Tosc § | _     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

## Applicable Devices 42 R42 42A 43 R43 44

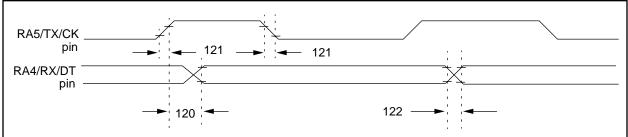

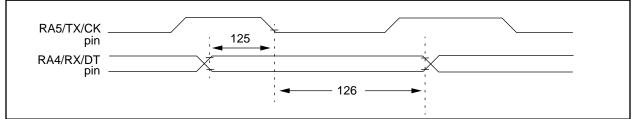

## FIGURE 19-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### **TABLE 19-9:** SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param | Course     | Characteristic                    |                                    | Min     | Truck  | Max    | Unite   | Conditions  |

|-------|------------|-----------------------------------|------------------------------------|---------|--------|--------|---------|-------------|

| No.   | Sym        | Characteristic                    |                                    | wiin    | Тур†   | Max    | Units   | Conditions  |

| 120   | TckH2dtV   | SYNC XMIT (MASTER &               |                                    |         |        |        |         |             |

|       |            | SLAVE)                            | PIC17CR42/42A/43/R43/44            | —       | -      | 50     | ns      |             |

|       |            | Clock high to data out valid      | PIC17LCR42/42A/43/R43/44           | 1 —     | -      | 75     | ns      |             |

| 121   | TckRF      | Clock out rise time and fall time | PIC17CR42/42A/43/R43/44            | —       | —      | 25     | ns      |             |

|       |            | (Master Mode)                     | PIC17LCR42/42A/43/R43/44           | —       | —      | 40     | ns      |             |

| 122   | TdtRF      | Data out rise time and fall time  | PIC17CR42/42A/43/R43/44            | —       | —      | 25     | ns      |             |

|       |            |                                   | PIC17LCR42/42A/43/R43/44           | —       | —      | 40     | ns      |             |

| +     | Data in "T | yp" column is at 5V, 25°C unless  | otherwise stated. These parameters | are for | design | guidan | ce only | and are not |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 19-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

## **TABLE 19-10: SYNCHRONOUS RECEIVE REQUIREMENTS**

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | _    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# Applicable Devices 42 R42 42A 43 R43 44

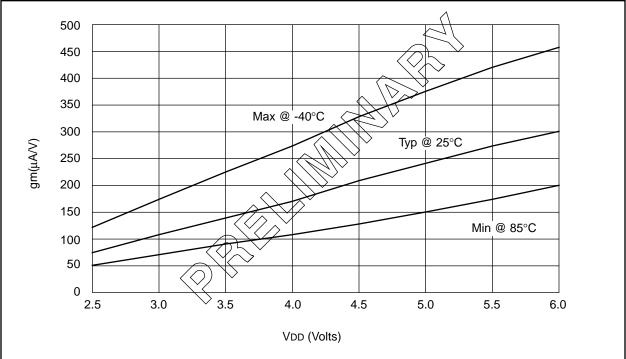

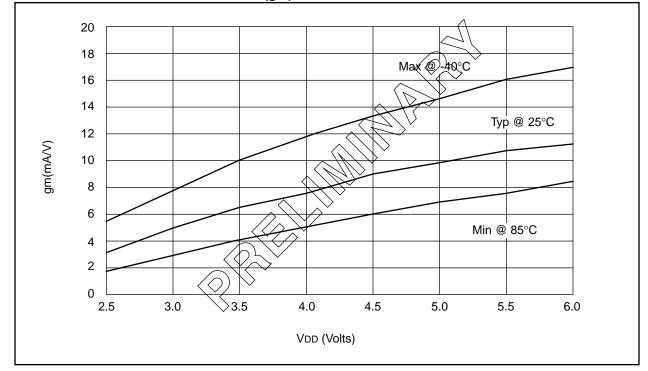

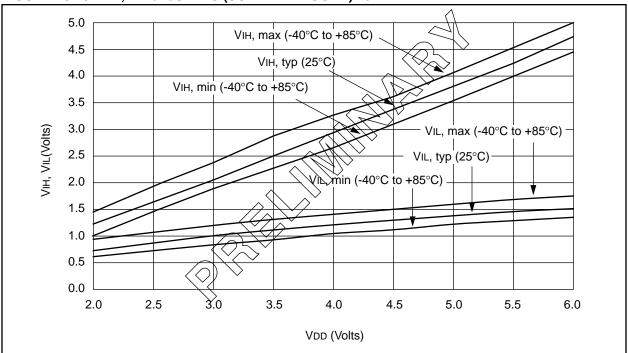

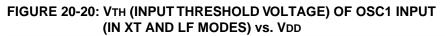

FIGURE 20-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

# PIC17C4X

## Applicable Devices 42 R42 42A 43 R43 44

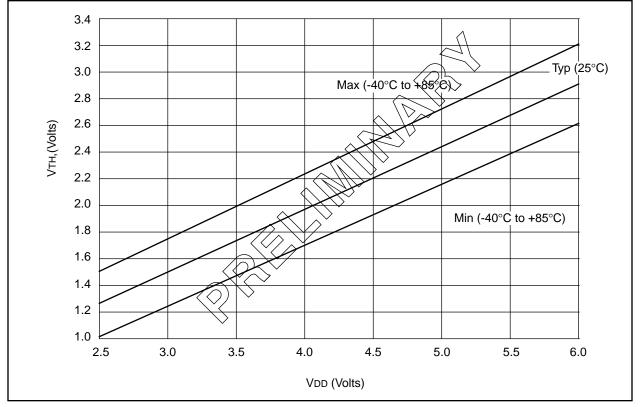

## 21.3 44-Lead Plastic Leaded Chip Carrier (Square)

|        | Ра     | ackage Group: F | Plastic Leaded C | hip Carrier (PL | CC)    |           |

|--------|--------|-----------------|------------------|-----------------|--------|-----------|

|        |        | Millimeters     |                  |                 | Inches |           |

| Symbol | Min    | Max             | Notes            | Min             | Max    | Notes     |

| А      | 4.191  | 4.572           |                  | 0.165           | 0.180  |           |

| A1     | 2.413  | 2.921           |                  | 0.095           | 0.115  |           |

| D      | 17.399 | 17.653          |                  | 0.685           | 0.695  |           |

| D1     | 16.510 | 16.663          |                  | 0.650           | 0.656  |           |

| D2     | 15.494 | 16.002          |                  | 0.610           | 0.630  |           |

| D3     | 12.700 | 12.700          | Reference        | 0.500           | 0.500  | Reference |

| E      | 17.399 | 17.653          |                  | 0.685           | 0.695  |           |

| E1     | 16.510 | 16.663          |                  | 0.650           | 0.656  |           |

| E2     | 15.494 | 16.002          |                  | 0.610           | 0.630  |           |

| E3     | 12.700 | 12.700          | Reference        | 0.500           | 0.500  | Reference |

| Ν      | 44     | 44              |                  | 44              | 44     |           |

| CP     | _      | 0.102           |                  | _               | 0.004  |           |

| LT     | 0.203  | 0.381           |                  | 0.008           | 0.015  |           |

## E.8 PIC17CXX Family of Devices

|           |         |              |          |                | Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Memory | ory    |                     | Peri   | Peripherals                           |          |                  |                                            |                                         | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------|--------------|----------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|---------------------|--------|---------------------------------------|----------|------------------|--------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|