Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 16MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 454 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44t-16e-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 4.1.3 OSCILLATOR START-UP TIMER (OST)

The Oscillator Start-up Timer (OST) provides a 1024 oscillator cycle (1024Tosc) delay after  $\overline{\text{MCLR}}$  is detected high or a wake-up from SLEEP event occurs.

The OST time-out is invoked only for XT and LF oscillator modes on a Power-on Reset or a Wake-up from SLEEP.

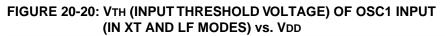

The OST counts the oscillator pulses on the OSC1/CLKIN pin. The counter only starts incrementing after the amplitude of the signal reaches the oscillator input thresholds. This delay allows the crystal oscillator or resonator to stabilize before the device exits reset. The length of time-out is a function of the crystal/resonator frequency.

#### 4.1.4 TIME-OUT SEQUENCE

On power-up the time-out sequence is as follows: First the internal POR signal goes high when the POR trip point is reached. If MCLR is high, then both the OST and PWRT timers start. In general the PWRT time-out is longer, except with low frequency crystals/resonators. The total time-out also varies based on oscillator configuration. Table 4-1 shows the times that are associated with the oscillator configuration. Figure 4-2 and Figure 4-3 display these time-out sequences.

If the device voltage is not within electrical specification at the end of a time-out, the  $\overline{\text{MCLR}}/\text{VPP}$  pin must be held low until the voltage is within the device specification. The use of an external RC delay is sufficient for many of these applications.

# TABLE 4-1:TIME-OUT IN VARIOUSSITUATIONS

| Oscillator<br>Configuration | Power-up                            | Wake up<br>from<br>SLEEP | MCLR<br>Reset |

|-----------------------------|-------------------------------------|--------------------------|---------------|

| XT, LF                      | Greater of:<br>96 ms or<br>1024Tosc | 1024Tosc                 | —             |

| EC, RC                      | Greater of:<br>96 ms or<br>1024Tosc |                          | —             |

The time-out sequence begins from the first rising edge of  $\overline{\text{MCLR}}$ .

Table 4-3 shows the reset conditions for some special registers, while Table 4-4 shows the initialization conditions for all the registers. The shaded registers (in Table 4-4) are for all devices except the PIC17C42. In the PIC17C42, the PRODH and PRODL registers are general purpose RAM.

# TABLE 4-2:STATUS BITS AND THEIR<br/>SIGNIFICANCE

| TO | PD | Event                                                                              |  |  |  |  |

|----|----|------------------------------------------------------------------------------------|--|--|--|--|

| 1  | 1  | Power-on Reset, MCLR Reset during normal operation, or CLRWDT instruction executed |  |  |  |  |

| 1  | 0  | MCLR Reset during SLEEP or interrupt wake-up from SLEEP                            |  |  |  |  |

| 0  | 1  | WDT Reset during normal operation                                                  |  |  |  |  |

| 0  | 0  | WDT Reset during SLEEP                                                             |  |  |  |  |

In Figure 4-2, Figure 4-3 and Figure 4-4, TPWRT > TOST, as would be the case in higher frequency crystals. For lower frequency crystals, (i.e., 32 kHz) TOST would be greater.

## TABLE 4-3: RESET CONDITION FOR THE PROGRAM COUNTER AND THE CPUSTA REGISTER

| Event                                 |                 | PCH:PCL               | CPUSTA | OST Active |

|---------------------------------------|-----------------|-----------------------|--------|------------|

| Power-on Reset                        |                 | 0000h                 | 11 11  | Yes        |

| MCLR Reset during normal ope          | ration          | 0000h                 | 11 11  | No         |

| MCLR Reset during SLEEP               |                 | 0000h                 | 11 10  | Yes (2)    |

| WDT Reset during normal operation     |                 | 0000h                 | 11 01  | No         |

| WDT Reset during SLEEP <sup>(3)</sup> |                 | 0000h                 | 11 00  | Yes (2)    |

| Interrupt wake-up from SLEEP          | GLINTD is set   | PC + 1                | 11 10  | Yes (2)    |

|                                       | GLINTD is clear | PC + 1 <sup>(1)</sup> | 10 10  | Yes (2)    |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0'.

Note 1: On wake-up, this instruction is executed. The instruction at the appropriate interrupt vector is fetched and then executed.

2: The OST is only active when the Oscillator is configured for XT or LF modes.

3: The Program Counter = 0, that is the device branches to the reset vector. This is different from the mid-range devices.

| Register  | Address | Power-on Reset | MCLR Reset<br>WDT Reset | Wake-up from SLEEF<br>through interrupt |

|-----------|---------|----------------|-------------------------|-----------------------------------------|

| Bank 2    |         | -              |                         | ·                                       |

| TMR1      | 10h     | XXXX XXXX      | սսսս սսսս               | uuuu uuuu                               |

| TMR2      | 11h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| TMR3L     | 12h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| TMR3H     | 13h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR1       | 14h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR2       | 15h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| PR3/CA1L  | 16h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| PR3/CA1H  | 17h     | XXXX XXXX      | uuuu uuuu               | սսսս սսսս                               |

| Bank 3    |         |                |                         |                                         |

| PW1DCL    | 10h     | xx             | uu                      | uu                                      |

| PW2DCL    | 11h     | xx             | uu                      | uu                                      |

| PW1DCH    | 12h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| PW2DCH    | 13h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| CA2L      | 14h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

| CA2H      | 15h     | XXXX XXXX      | นนนน นนนน               | uuuu uuuu                               |

| TCON1     | 16h     | 0000 0000      | 0000 0000               | uuuu uuuu                               |

| TCON2     | 17h     | 0000 0000      | 0000 0000               | uuuu uuuu                               |

| Unbanked  |         |                |                         |                                         |

| PRODL (5) | 18h     | XXXX XXXX      | นนนน นนนน               | นนนน นนนน                               |

| PRODH (5) | 19h     | xxxx xxxx      | uuuu uuuu               | uuuu uuuu                               |

#### TABLE 4-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS (Cont.'d)

Legend: u = unchanged, x = unknown, - = unimplemented read as '0', q = value depends on condition. Note 1: One or more bits in INTSTA, PIR will be affected (to cause wake-up).

2: When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

3: See Table 4-3 for reset value of specific condition.

4: Only applies to the PIC17C42.

5: Does not apply to the PIC17C42.

## 5.1 Interrupt Status Register (INTSTA)

The Interrupt Status/Control register (INTSTA) records the individual interrupt requests in flag bits, and contains the individual interrupt enable bits (not for the peripherals).

The PEIF bit is a read only, bit wise OR of all the peripheral flag bits in the PIR register (Figure 5-4).

Note: T0IF, INTF, T0CKIF, or PEIF will be set by the specified condition, even if the corresponding interrupt enable bit is clear (interrupt disabled) or the GLINTD bit is set (all interrupts disabled).

Care should be taken when clearing any of the INTSTA register enable bits when interrupts are enabled (GLINTD is clear). If any of the INTSTA flag bits (T0IF, INTF, T0CKIF, or PEIF) are set in the same instruction cycle as the corresponding interrupt enable bit is cleared, the device will vector to the reset address (0x00).

When disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled).

# FIGURE 5-2: INTSTA REGISTER (ADDRESS: 07h, UNBANKED)

| bit $W = V$                                                                                                                                                                                                                                                                                                                | eadable bit<br>/ritable bit<br>/alue at POR reset                                                                             |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| bit 7: <b>PEIF</b> : Peripheral Interrupt Flag bit<br>This bit is the OR of all peripheral interrupt flag bits AND'ed with their corres<br>1 = A peripheral interrupt is pending                                                                                                                                           | /alue at POR reset                                                                                                            |  |  |  |  |  |

| bit 7: <b>PEIF</b> : Peripheral Interrupt Flag bit<br>This bit is the OR of all peripheral interrupt flag bits AND'ed with their corres<br>1 = A peripheral interrupt is pending                                                                                                                                           |                                                                                                                               |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                            | ponding enable bits.                                                                                                          |  |  |  |  |  |

| <ul> <li>bit 6: TOCKIF: External Interrupt on TOCKI Pin Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program exercised</li> <li>1 = The software specified edge occurred on the RA1/T0CKI pin</li> <li>0 = The software specified edge did not occur on the RA1/T0CKI pin</li> </ul> | cution to vector (18h).                                                                                                       |  |  |  |  |  |

| bit 5: <b>T0IF</b> : TMR0 Overflow Interrupt Flag bit<br>This bit is cleared by hardware, when the interrupt logic forces program exer<br>1 = TMR0 overflowed<br>0 = TMR0 did not overflow                                                                                                                                 | cution to vector (10h).                                                                                                       |  |  |  |  |  |

| <ul> <li>bit 4: INTF: External Interrupt on INT Pin Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program exercise</li> <li>1 = The software specified edge occurred on the RA0/INT pin</li> <li>0 = The software specified edge did not occur on the RA0/INT pin</li> </ul>          | cution to vector (08h).                                                                                                       |  |  |  |  |  |

| <ul> <li>bit 3: PEIE: Peripheral Interrupt Enable bit</li> <li>This bit enables all peripheral interrupts that have their corresponding enabl</li> <li>1 = Enable peripheral interrupts</li> <li>0 = Disable peripheral interrupts</li> </ul>                                                                              | This bit enables all peripheral interrupts that have their corresponding enable bits set.<br>1 = Enable peripheral interrupts |  |  |  |  |  |

| bit 2: <b>TOCKIE</b> : External Interrupt on TOCKI Pin Enable bit<br>1 = Enable software specified edge interrupt on the RA1/TOCKI pin<br>0 = Disable interrupt on the RA1/TOCKI pin                                                                                                                                       |                                                                                                                               |  |  |  |  |  |

| bit 1: <b>T0IE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enable TMR0 overflow interrupt<br>0 = Disable TMR0 overflow interrupt                                                                                                                                                                                       | 1 = Enable TMR0 overflow interrupt                                                                                            |  |  |  |  |  |

| bit 0: <b>INTE</b> : External Interrupt on RA0/INT Pin Enable bit<br>1 = Enable software specified edge interrupt on the RA0/INT pin<br>0 = Disable software specified edge interrupt on the RA0/INT pin                                                                                                                   |                                                                                                                               |  |  |  |  |  |

| TABLE 6-3: | SPECIAL FUNCTION REGISTERS |

|------------|----------------------------|

|------------|----------------------------|

| Address            | Name          | Bit 7        | Bit 6                                         | Bit 5         | Bit 4        | Bit 3        | Bit 2           | Bit 1          | Bit 0           | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------------|--------------|-----------------------------------------------|---------------|--------------|--------------|-----------------|----------------|-----------------|-------------------------------|-------------------------------------|

| Unbank             | ed            | •            |                                               |               |              | •            |                 |                | •               |                               |                                     |

| 00h                | INDF0         | Uses con     | tents of FSI                                  | R0 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 01h                | FSR0          | Indirect d   | ata memory                                    | address po    | inter 0      |              |                 |                |                 | XXXX XXXX                     | uuuu uuuu                           |

| 02h                | PCL           | Low orde     | r 8-bits of P                                 | С             |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH        | Holding re   | egister for u                                 | pper 8-bits o | of PC        |              |                 |                |                 | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA        | FS3          | FS2                                           | FS1           | FS0          | OV           | Z               | DC             | С               | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA         | INTEDG       | TOSE                                          | TOCS          | PS3          | PS2          | PS1             | PS0            | —               | 0000 000-                     | 0000 000-                           |

| 06h <b>(2)</b>     | CPUSTA        | _            | _                                             | STKAV         | GLINTD       | TO           | PD              | _              | _               | 11 11                         | 11 qq                               |

| 07h                | INTSTA        | PEIF         | TOCKIF                                        | T0IF          | INTF         | PEIE         | TOCKIE          | TOIE           | INTE            | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1         | Uses con     | tents of FSI                                  | R1 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 09h                | FSR1          | Indirect d   | ata memory                                    | address po    | inter 1      |              | , ,             |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG          | Working r    | egister                                       |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L         | TMR0 reg     | gister; low b                                 | yte           |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H         | TMR0 reg     |                                               |               |              |              |                 |                | xxxx xxxx       | uuuu uuuu                     |                                     |

| 0Dh                | TBLPTRL       | Low byte     | Low byte of program memory table pointer (4)  |               |              |              |                 |                | (4)             | (4)                           |                                     |

| 0Eh                | TBLPTRH       | High byte    | High byte of program memory table pointer (4) |               |              |              |                 |                | (4)             | (4)                           |                                     |

| 0Fh                | BSR           | Bank sele    | Bank select register 0000 000                 |               |              |              |                 | 0000 0000      | 0000 0000       |                               |                                     |

| Bank 0             |               | 1            |                                               |               |              |              |                 |                |                 | I                             |                                     |

| 10h                | PORTA         | RBPU         | _                                             | RA5           | RA4          | RA3          | RA2             | RA1/T0CKI      | RA0/INT         | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB          | Data dire    | ction registe                                 | er for PORTE  | 3            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB         | PORTB d      | ata latch                                     |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA         | SPEN         | RX9                                           | SREN          | CREN         | —            | FERR            | OERR           | RX9D            | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG         | Serial por   | t receive re                                  | gister        |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA         | CSRC         | TX9                                           | TXEN          | SYNC         | —            | —               | TRMT           | TX9D            | 00001x                        | 00001u                              |

| 16h                | TXREG         | Serial por   | t transmit re                                 | egister       |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG         | Baud rate    | generator                                     | register      |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |               |              |                                               |               |              |              |                 |                |                 |                               |                                     |

| 10h                | DDRC          | Data dire    | ction registe                                 | er for PORT   | 2            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC         | RC7/<br>AD7  | RC6/<br>AD6                                   | RC5/<br>AD5   | RC4/<br>AD4  | RC3/<br>AD3  | RC2/<br>AD2     | RC1/<br>AD1    | RC0/<br>AD0     | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD          | Data dire    | ction registe                                 | er for PORTI  | )            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 4.01-              | PORTD         | RD7/<br>AD15 | RD6/<br>AD14                                  | RD5/<br>AD13  | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10    | RD1/<br>AD9    | RD0/<br>AD8     | xxxx xxxx                     | uuuu uuuu                           |

| 13h                |               | Data dira    | ction reaiste                                 | er for PORTE  | -            |              |                 | 1              |                 | 111                           | 111                                 |

| 13h<br>14h         | DDRE          | Data dire    |                                               |               |              |              |                 | -              |                 |                               |                                     |

|                    | DDRE<br>PORTE | Data dire    | _                                             | _             | _            | _            | RE2/WR          | RE1/OE         | RE0/ALE         | xxx                           | uuu                                 |

| 14h                |               | RBIF         | —<br>TMR3IF                                   | —<br>TMR2IF   | —<br>TMR1IF  | —<br>CA2IF   | RE2/WR<br>CA1IF | RE1/OE<br>TXIF | RE0/ALE<br>RCIF | xxx<br>0000 0010              | uuu<br>0000 0010                    |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1:

from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 2:

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

4:

The following values are for both TBLPTRL and TBLPTRH: All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

5: The PRODL and PRODH registers are not implemented on the PIC17C42.

# 8.0 HARDWARE MULTIPLIER

All PIC17C4X devices except the PIC17C42, have an 8 x 8 hardware multiplier included in the ALU of the device. By making the multiply a hardware operation, it completes in a single instruction cycle. This is an unsigned multiply that gives a 16-bit result. The result is stored into the 16-bit PRODuct register (PRODH:PRODL). The multiplier does not affect any flags in the ALUSTA register.

Making the 8 x 8 multiplier execute in a single cycle gives the following advantages:

- Higher computational throughput

- Reduces code size requirements for multiply algorithms

The performance increase allows the device to be used in applications previously reserved for Digital Signal Processors.

Table 8-1 shows a performance comparison between the PIC17C42 and all other PIC17CXX devices, which have the single cycle hardware multiply.

Example 8-1 shows the sequence to do an 8 x 8 unsigned multiply. Only one instruction is required when one argument of the multiply is already loaded in the WREG register.

Example 8-2 shows the sequence to do an  $8 \times 8$  signed multiply. To account for the sign bits of the arguments, each argument's most significant bit (MSb) is tested and the appropriate subtractions are done.

#### EXAMPLE 8-1: 8 x 8 MULTIPLY ROUTINE

| MOVFP | ARG1, | WREG |   |      |    |        |    |

|-------|-------|------|---|------|----|--------|----|

| MULWF | ARG2  |      | ; | ARG1 | *  | ARG2   | -> |

|       |       |      | ; | PRO  | DD | H:PROI | ЪГ |

#### EXAMPLE 8-2: 8 x 8 SIGNED MULTIPLY ROUTINE

| MOVFP | ARG1, WREG |                  |

|-------|------------|------------------|

| MULWF | ARG2       | ; ARG1 * ARG2 -> |

|       |            | ; PRODH:PRODL    |

| BTFSC | ARG2, SB   | ; Test Sign Bit  |

| SUBWF | PRODH, F   | ; PRODH = PRODH  |

|       |            | ; – ARG1         |

| MOVFP | ARG2, WREG |                  |

| BTFSC | ARG1, SB   | ; Test Sign Bit  |

| SUBWF | PRODH, F   | ; PRODH = PRODH  |

|       |            | ; – ARG2         |

| Routine          | Device                     | Program Memory |              | Time     |          |  |

|------------------|----------------------------|----------------|--------------|----------|----------|--|

| Routine          | Device                     | (Words)        | Cycles (Max) | @ 25 MHz | @ 33 MHz |  |

| 8 x 8 unsigned   | PIC17C42                   | 13             | 69           | 11.04 μs | N/A      |  |

|                  | All other PIC17CXX devices | 1              | 1            | 160 ns   | 121 ns   |  |

| 8 x 8 signed     | PIC17C42                   | _              |              | _        | N/A      |  |

|                  | All other PIC17CXX devices | 6              | 6            | 960 ns   | 727 ns   |  |

| 16 x 16 unsigned | PIC17C42                   | 21             | 242          | 38.72 μs | N/A      |  |

|                  | All other PIC17CXX devices | 24             | 24           | 3.84 μs  | 2.91 μs  |  |

| 16 x 16 signed   | PIC17C42                   | 52             | 254          | 40.64 μs | N/A      |  |

|                  | All other PIC17CXX devices | 36             | 36           | 5.76 μs  | 4.36 µs  |  |

#### TABLE 8-1: PERFORMANCE COMPARISON

# TABLE 9-7: PORTD FUNCTIONS

| Name     | Bit  | Buffer Type | Function                                       |  |

|----------|------|-------------|------------------------------------------------|--|

| RD0/AD8  | bit0 | TTL         | Input/Output or system bus address/data pin.   |  |

| RD1/AD9  | bit1 | TTL         | Input/Output or system bus address/data pin.   |  |

| RD2/AD10 | bit2 | TTL         | Input/Output or system bus address/data pin.   |  |

| RD3/AD11 | bit3 | TTL         | Input/Output or system bus address/data pin.   |  |

| RD4/AD12 | bit4 | TTL         | L Input/Output or system bus address/data pin. |  |

| RD5/AD13 | bit5 | TTL         | Input/Output or system bus address/data pin.   |  |

| RD6/AD14 | bit6 | TTL         | Input/Output or system bus address/data pin.   |  |

| RD7/AD15 | bit7 | TTL         | Input/Output or system bus address/data pin.   |  |

Legend: TTL = TTL input.

# TABLE 9-8: REGISTERS/BITS ASSOCIATED WITH PORTD

| Address     | Name  | Bit 7                             | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-----------------------------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------------------------|-----------------------------------------|

| 13h, Bank 1 | PORTD | RD7/<br>AD15                      | RD6/<br>AD14 | RD5/<br>AD13 | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10 | RD1/<br>AD9 | RD0/<br>AD8 | XXXX XXXX                     | uuuu uuuu                               |

| 12h, Bank 1 | DDRD  | Data direction register for PORTD |              |              |              |              |              | 1111 1111   | 1111 1111   |                               |                                         |

Legend: x = unknown, u = unchanged.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

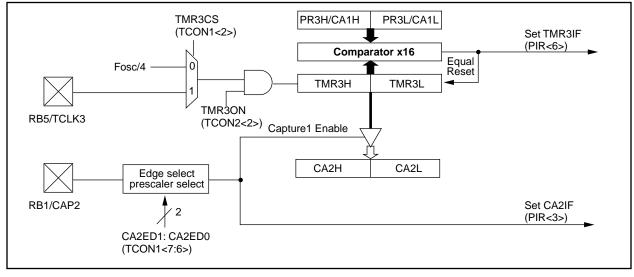

#### 12.2.1 ONE CAPTURE AND ONE PERIOD REGISTER MODE

In this mode registers PR3H/CA1H and PR3L/CA1L constitute a 16-bit period register. A block diagram is shown in Figure 12-7. The timer increments until it equals the period register and then resets to 0000h. TMR3 Interrupt Flag bit (TMR3IF) is set at this point. This interrupt can be disabled by clearing the TMR3 Interrupt Enable bit (TMR3IE). TMR3IF must be cleared in software.

This mode is selected if control bit CA1/PR3 is clear. In this mode, the Capture1 register, consisting of high byte (PR3H/CA1H) and low byte (PR3L/CA1L), is configured as the period control register for TMR3. Capture1 is disabled in this mode, and the corresponding Interrupt bit CA1IF is never set. TMR3 increments until it equals the value in the period register and then resets to 0000h.

Capture2 is active in this mode. The CA2ED1 and CA2ED0 bits determine the event on which capture will occur. The possible events are:

- · Capture on every falling edge

- Capture on every rising edge

- · Capture every 4th rising edge

- · Capture every 16th rising edge

When a capture takes place, an interrupt flag is latched into the CA2IF bit. This interrupt can be enabled by setting the corresponding mask bit CA2IE. The Peripheral Interrupt Enable bit (PEIE) must be set and the Global Interrupt Disable bit (GLINTD) must be cleared for the interrupt to be acknowledged. The CA2IF interrupt flag bit must be cleared in software.

When the capture prescale select is changed, the prescaler is not reset and an event may be generated. Therefore, the first capture after such a change will be ambiguous. However, it sets the time-base for the next capture. The prescaler is reset upon chip reset. Capture pin RB1/CAP2 is a multiplexed pin. When used as a port pin, Capture2 is not disabled. However, the user can simply disable the Capture2 interrupt by clearing CA2IE. If RB1/CAP2 is used as an output pin, the user can activate a capture by writing to the port pin. This may be useful during development phase to emulate a capture interrupt.

The input on capture pin RB1/CAP2 is synchronized internally to internal phase clocks. This imposes certain restrictions on the input waveform (see the Electrical Specification section for timing).

The Capture2 overflow status flag bit is double buffered. The master bit is set if one captured word is already residing in the Capture2 register and another "event" has occurred on the RB1/CA2 pin. The new event will not transfer the Timer3 value to the capture register, protecting the previous unread capture value. When the user reads both the high and the low bytes (in any order) of the Capture2 register, the master overflow bit is transferred to the slave overflow bit (CA2OVF) and then the master bit is reset. The user can then read TCON2 to determine the value of CA2OVF.

The recommended sequence to read capture registers and capture overflow flag bits is shown in Example 12-1.

#### EXAMPLE 12-1: SEQUENCE TO READ CAPTURE REGISTERS

| MOVLB 3              | ;Select Bank 3          |

|----------------------|-------------------------|

| MOVPF CA2L,LO_BYTE   | ;Read Capture2 low      |

|                      | ;byte, store in LO_BYTE |

| MOVPF CA2H, HI_BYTE  | ;Read Capture2 high     |

|                      | ;byte, store in HI_BYTE |

| MOVPF TCON2,STAT_VAL | ;Read TCON2 into file   |

|                      | ;STAT_VAL               |

#### FIGURE 12-7: TIMER3 WITH ONE CAPTURE AND ONE PERIOD REGISTER BLOCK DIAGRAM

#### 13.3 USART Synchronous Master Mode

In Master Synchronous mode, the data is transmitted in a half-duplex manner; i.e. transmission and reception do not occur at the same time: when transmitting data, the reception is inhibited and vice versa. The synchronous mode is entered by setting the SYNC (TXSTA<4>) bit. In addition, the SPEN (RCSTA<7>) bit is set in order to configure the RA5 and RA4 I/O ports to CK (clock) and DT (data) lines respectively. The Master mode indicates that the processor transmits the master clock on the CK line. The Master mode is entered by setting the CSRC (TXSTA<7>) bit.

#### 13.3.1 USART SYNCHRONOUS MASTER TRANSMISSION

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit (serial) shift register (TSR). The shift register obtains its data from the read/write transmit buffer TXREG. TXREG is loaded with data in software. The TSR is not loaded until the last bit has been transmitted from the previous load. As soon as the last bit is transmitted, the TSR is loaded with new data from TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), TXREG is empty and the TXIF (PIR<1>) bit is set. This interrupt can be enabled/disabled by setting/clearing the TXIE bit (PIE<1>). TXIF will be set regardless of the state of bit TXIE and cannot be cleared in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of TXREG, TRMT (TXSTA<1>) shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty. The TSR is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data. The first data bit will be shifted out on the next available rising edge of the clock on the RA5/TX/CK pin. Data out is stable around the falling edge of the synchronous clock (Figure 13-10). The transmission can also be started by first loading TXREG and then setting TXEN. This is advantageous when slow baud rates are selected, since BRG is kept in RESET when the TXEN, CREN, and SREN bits are clear. Setting the TXEN bit will start the BRG, creating a shift clock immediately. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to the TSR, resulting in an empty TXREG. Back-to-back transfers are possible.

Clearing TXEN during a transmission will cause the transmission to be aborted and will reset the transmitter. The RA4/RX/DT and RA5/TX/CK pins will revert to hi-impedance. If either CREN or SREN are set during a transmission, the transmission is aborted and the

RA4/RX/DT pin reverts to a hi-impedance state (for a reception). The RA5/TX/CK pin will remain an output if the CSRC bit is set (internal clock). The transmitter logic is not reset, although it is disconnected from the pins. In order to reset the transmitter, the user has to clear the TXEN bit. If the SREN bit is set (to interrupt an ongoing transmission and receive a single word), then after the single word is received, SREN will be cleared and the serial port will revert back to transmitting, since the TXEN bit is still set. The DT line will immediately switch from hi-impedance receive mode to transmit and start driving. To avoid this, TXEN should be cleared.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty). If the TSR was empty and TXREG was written before writing the "new" TX9D, the "present" value of TX9D is loaded.

Steps to follow when setting up a Synchronous Master Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate (see Baud Rate Generator Section for details).

- 2. Enable the synchronous master serial port by setting the SYNC, SPEN, and CSRC bits.

- 3. Ensure that the CREN and SREN bits are clear (these bits override transmission when set).

- 4. If interrupts are desired, then set the TXIE bit (the GLINTD bit must be clear and the PEIE bit must be set).

- 5. If 9-bit transmission is desired, then set the TX9 bit.

- 6. Start transmission by loading data to the TXREG register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 8. Enable the transmission by setting TXEN.

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the reverse order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

| ANDWF                                                         | AND WRE                                                  | AND WREG with f                                                   |                      |                       |  |  |  |  |

|---------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------|----------------------|-----------------------|--|--|--|--|

| Syntax:                                                       | [ <i>label</i> ] A                                       | [label] ANDWF f,d                                                 |                      |                       |  |  |  |  |

| Operands:                                                     | $0 \le f \le 255$ $d \in [0,1]$                          | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |                      |                       |  |  |  |  |

| Operation:                                                    | (WREG) .                                                 | AND. (f)                                                          | $\rightarrow$ (dest) | )                     |  |  |  |  |

| Status Affected:                                              | Z                                                        |                                                                   |                      |                       |  |  |  |  |

| Encoding:                                                     | 0000                                                     | 101d                                                              | ffff                 | ffff                  |  |  |  |  |

| Description:                                                  | The conten<br>register 'f'.<br>in WREG. I<br>back in reg | lf 'd' is 0<br>f 'd' is 1 t                                       | the result           | is stored             |  |  |  |  |

| Words:                                                        | 1                                                        |                                                                   |                      |                       |  |  |  |  |

| Cycles:                                                       | 1                                                        | 1                                                                 |                      |                       |  |  |  |  |

| Q Cycle Activity:                                             |                                                          |                                                                   |                      |                       |  |  |  |  |

| Q1                                                            | Q2                                                       | Q3                                                                | 8                    | Q4                    |  |  |  |  |

| Decode                                                        | Read<br>register 'f'                                     | Execu                                                             |                      | Vrite to<br>stination |  |  |  |  |

| Example:                                                      | ANDWF                                                    | REG, 1                                                            |                      |                       |  |  |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG<br>REG | = 0x17<br>= 0xC2                                         |                                                                   |                      |                       |  |  |  |  |

| BCF                                                                           |         | Bit Clear                        | Bit Clear f                                                         |     |                       |      |  |  |  |

|-------------------------------------------------------------------------------|---------|----------------------------------|---------------------------------------------------------------------|-----|-----------------------|------|--|--|--|

| Syntax:                                                                       |         | [ <i>label</i> ] E               | [label] BCF f,b                                                     |     |                       |      |  |  |  |

| Operands:                                                                     |         | $0 \le f \le 25$ $0 \le b \le 7$ | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \end{array}$ |     |                       |      |  |  |  |

| Operation:                                                                    |         | $0 \rightarrow (f < b >$         | -)                                                                  |     |                       |      |  |  |  |

| Status Affe                                                                   | cted:   | None                             |                                                                     |     |                       |      |  |  |  |

| Encoding:                                                                     |         | 1000                             | 1bbb                                                                | fff | f                     | ffff |  |  |  |

| Description                                                                   | :       | Bit 'b' in re                    | Bit 'b' in register 'f' is cleared.                                 |     |                       |      |  |  |  |

| Words:                                                                        |         | 1                                | 1                                                                   |     |                       |      |  |  |  |

| Cycles:                                                                       |         | 1                                | 1                                                                   |     |                       |      |  |  |  |

| Q Cycle Ac                                                                    | tivity: |                                  |                                                                     |     |                       |      |  |  |  |

| Q                                                                             | 1       | Q2                               | Q3                                                                  |     | Q4                    |      |  |  |  |

| Deco                                                                          | Decode  |                                  | Execute                                                             |     | Write<br>register 'f' |      |  |  |  |

| Example:                                                                      |         | BCF                              | FLAG_R                                                              | EG, | 7                     |      |  |  |  |

| Before Instruction<br>FLAG_REG = 0xC7<br>After Instruction<br>FLAG_REG = 0x47 |         |                                  |                                                                     |     |                       |      |  |  |  |

| FL.                                                                           |         | _0 = 0,47                        |                                                                     |     |                       |      |  |  |  |

| CALL                                                                                      | Subroutir                                                  | ne Call                                                                                                                                                                                   |              | CLF  | RF                                                                            | Clear f                                                                                                                                   |                                                                                           |       |                       |  |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|-----------------------|--|

| Syntax:                                                                                   | [label] C                                                  | CALL k                                                                                                                                                                                    |              | Syn  | tax:                                                                          | [ <i>label</i> ] CL                                                                                                                       | RF f,s                                                                                    |       |                       |  |

| Operands:                                                                                 | $0 \le k \le 40$                                           | $0 \le k \le 4095$                                                                                                                                                                        |              | Ope  | Operands: $0 \le f \le 255$                                                   |                                                                                                                                           |                                                                                           |       |                       |  |

| Operation:                                                                                | k<12:8> –                                                  | PC+ 1 $\rightarrow$ TOS, k $\rightarrow$ PC<12:0>,<br>k<12:8> $\rightarrow$ PCLATH<4:0>;<br>PC<15:13> $\rightarrow$ PCLATH<7:5>                                                           |              | ·    | ration:                                                                       | $00h \rightarrow de$                                                                                                                      | $\begin{array}{l} 00h \rightarrow f, \ s \in \ [0,1] \\ 00h \rightarrow dest \end{array}$ |       |                       |  |

| Status Affected:                                                                          | None                                                       |                                                                                                                                                                                           | 1<1.02       | Stat | us Affected:                                                                  | None                                                                                                                                      |                                                                                           |       |                       |  |

|                                                                                           |                                                            |                                                                                                                                                                                           |              | Enc  | oding:                                                                        | 0010                                                                                                                                      | 100s                                                                                      | ffff  | ffff                  |  |

| Encoding:<br>Description:                                                                 | return addr<br>the stack. T<br>PC bits<12<br>bits of the F | kkkk kkkk kkkk<br>tine call within 8K page. First,<br>ddress (PC+1) is pushed onto<br>k. The 13-bit value is loaded into<br><12:0>. Then the upper-eight<br>he PC are copied into PCLATH. |              |      | cription:                                                                     | Clears the contents of the sp<br>ister(s).<br>s = 0: Data memory location<br>WREG are cleared.<br>s = 1: Data memory location<br>cleared. |                                                                                           |       | 'f' and               |  |

|                                                                                           |                                                            | wo-cycle instru                                                                                                                                                                           |              |      | Words:                                                                        |                                                                                                                                           | 1                                                                                         |       |                       |  |

|                                                                                           | See LCALL<br>space.                                        | for calls outsic                                                                                                                                                                          | de 8K memory | Cyc  | les:                                                                          | 1                                                                                                                                         |                                                                                           |       |                       |  |

| Words:                                                                                    | 1                                                          |                                                                                                                                                                                           |              | QC   | ycle Activity:                                                                |                                                                                                                                           |                                                                                           |       |                       |  |

| Cycles:                                                                                   | 2                                                          |                                                                                                                                                                                           |              |      | Q1                                                                            | Q2                                                                                                                                        | Q                                                                                         |       | Q4                    |  |

| Q Cycle Activity:                                                                         |                                                            |                                                                                                                                                                                           |              |      | Decode                                                                        | Read<br>register 'f'                                                                                                                      | Exect                                                                                     |       | Write<br>egister 'f'  |  |

| Q1                                                                                        | Q2                                                         | Q3                                                                                                                                                                                        | Q4           |      |                                                                               | iegister i                                                                                                                                |                                                                                           |       | and other             |  |

| Decode                                                                                    | Read literal<br>'k'<7:0>                                   | Execute                                                                                                                                                                                   | NOP          |      |                                                                               |                                                                                                                                           |                                                                                           | :     | specified<br>register |  |

| Forced NOP                                                                                | NOP                                                        | Execute                                                                                                                                                                                   | NOP          | Exa  | <u>mple</u> :                                                                 | CLRF                                                                                                                                      | FLAG                                                                                      | G_REG |                       |  |

| Example: HERE CALL THERE<br>Before Instruction<br>PC = Address(HERE)<br>After Instruction |                                                            |                                                                                                                                                                                           |              |      | Before Instruction<br>FLAG_REG = 0x5A<br>After Instruction<br>FLAG_REG = 0x00 |                                                                                                                                           |                                                                                           |       |                       |  |

| PC =                                                                                      | Address (THI                                               | ERE)                                                                                                                                                                                      |              |      |                                                                               |                                                                                                                                           |                                                                                           |       |                       |  |

TOS = Address(HERE + 1)

| SLEEP                                                                                 | Enter SL                                             | Enter SLEEP mode                                                                                                                                                                                               |       |    |      |  |  |  |

|---------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|------|--|--|--|

| Syntax:                                                                               | [label] S                                            | [label] SLEEP                                                                                                                                                                                                  |       |    |      |  |  |  |

| Operands:                                                                             | None                                                 |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Operation:                                                                            |                                                      |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Status Affected:                                                                      | TO, PD                                               |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Encoding:                                                                             | 0000                                                 | 0000                                                                                                                                                                                                           | 000   | 0  | 0011 |  |  |  |

| Description:                                                                          | cleared. Th<br>set. Watch<br>are cleare<br>The proce | The power down status bit (PD) is<br>cleared. The time-out status bit (TO) is<br>set. Watchdog Timer and its prescaler<br>are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |       |    |      |  |  |  |

| Words:                                                                                | 1                                                    |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Cycles:                                                                               | 1                                                    | 1                                                                                                                                                                                                              |       |    |      |  |  |  |

| Q Cycle Activity:                                                                     |                                                      |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Q1                                                                                    | Q2                                                   | Q3                                                                                                                                                                                                             |       | (  | Q4   |  |  |  |

| Decode                                                                                | Read<br>register<br>PCLATH                           | Execu                                                                                                                                                                                                          | te    | N  | OP   |  |  |  |

| Example:                                                                              | SLEEP                                                |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Before Instruction<br>$\overline{TO} = ?$<br>$\overline{PD} = ?$<br>After Instruction |                                                      |                                                                                                                                                                                                                |       |    |      |  |  |  |

| TO =<br>PD =<br>† If WDT causes                                                       | 1†<br>0                                              | nie hit ie                                                                                                                                                                                                     | clear | be |      |  |  |  |

† If WDT causes wake-up, this bit is cleared

| SUE              | BLW                                                  | S                   | Subtract WREG from Literal |       |                          |         |    |                    |  |

|------------------|------------------------------------------------------|---------------------|----------------------------|-------|--------------------------|---------|----|--------------------|--|

| Syntax:          |                                                      |                     | [ <i>label</i> ] SUBLW k   |       |                          |         |    |                    |  |

| Operands:        |                                                      |                     | $\leq k$                   | ≤ 2   | 55                       |         |    |                    |  |

| Ope              | ration:                                              | k                   | — (V                       | VRE   | $\Xi G) \rightarrow (N)$ | VRE     | G) |                    |  |

| Status Affected: |                                                      |                     | DV, C                      | , D   | C, Z                     |         |    |                    |  |

| Enc              | oding:                                               | Γ                   | 101                        | 1     | 0010                     | kkł     | k  | kkkk               |  |

| Des              | cription:                                            | li                  |                            | k'. T | subtracte<br>he result   |         |    | e eight bit<br>⊢in |  |

| Wor              | ds:                                                  | 1                   |                            |       |                          |         |    |                    |  |

| Cycl             | les:                                                 | 1                   |                            |       |                          |         |    |                    |  |

| QC               | ycle Activity:                                       |                     |                            |       |                          |         |    |                    |  |

|                  | Q1                                                   |                     | Q2                         |       | Q3                       |         |    | Q4                 |  |

|                  | Decode                                               | -                   | Read<br>eral 'k            | ۲'    | Execu                    | ite     |    | Vrite to<br>WREG   |  |

| Exa              | <u>mple 1</u> :                                      | S                   | UBLW                       | 1 (   | Ox02                     |         |    |                    |  |

|                  | Before Instru<br>WREG<br>C<br>After Instruct<br>WREG | =<br>=              | ר<br>1<br>?<br>1           |       |                          |         |    |                    |  |

| <u>Exa</u>       | C<br>Z<br>mple <u>2</u> :                            | =                   | 1<br>0                     | ; re  | esult is po              | ositive |    |                    |  |

|                  | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>2<br>?                |       |                          |         |    |                    |  |

| <u>Exa</u>       | After Instruct<br>WREG<br>C<br>Z<br>mple <u>3</u> :  | tion<br>=<br>=<br>= | 0<br>1<br>1                | ; re  | esult is ze              | ero     |    |                    |  |

|                  | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>3<br>?                |       |                          |         |    |                    |  |

|                  | After Instruct<br>WREG<br>C<br>Z                     | tion<br>=<br>=<br>= | FF<br>0<br>1               |       | 's comple<br>esult is ne |         | ·  |                    |  |

MPASM allow full symbolic debugging from the Microchip Universal Emulator System (PICMASTER).

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

# 16.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

# 16.12 C Compiler (MPLAB-C)

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

## 16.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

#### 16.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

#### 16.15 <u>SEEVAL® Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

## 16.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

## 16.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

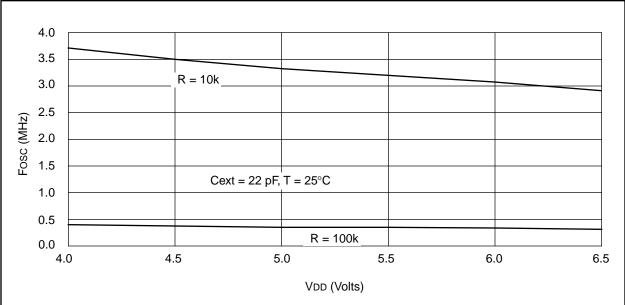

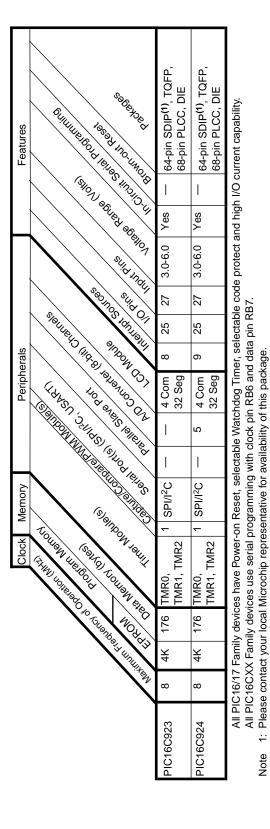

# Applicable Devices 42 R42 42A 43 R43 44

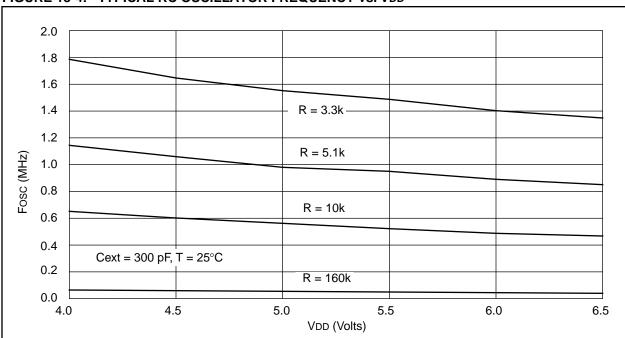

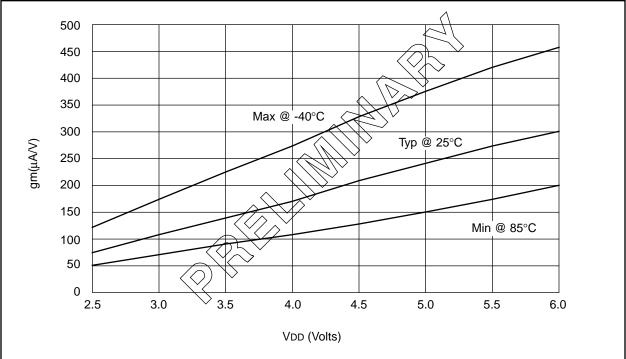

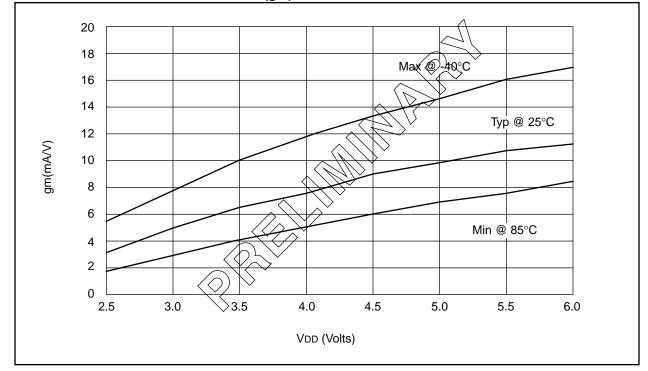

# FIGURE 18-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

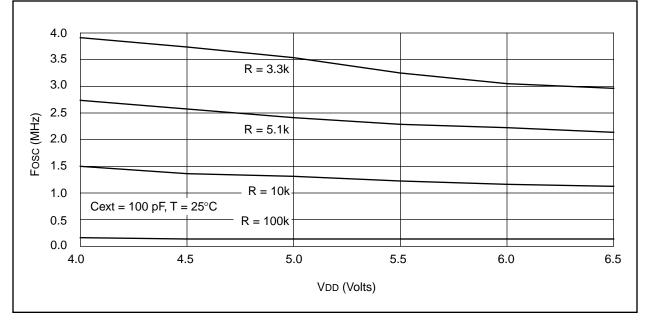

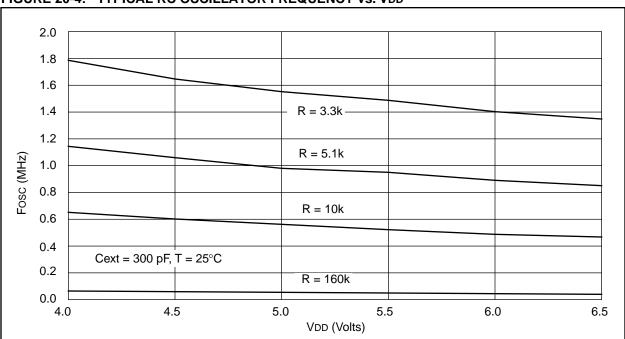

## FIGURE 18-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

Applicable Devices 42 R42 42A 43 R43 44

# FIGURE 18-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

## TABLE 18-2: RC OSCILLATOR FREQUENCIES

| Cext   | Rext |          | rage<br>5V, 25°C |

|--------|------|----------|------------------|

| 22 pF  | 10k  | 3.33 MHz | ± 12%            |

|        | 100k | 353 kHz  | ± 13%            |

| 100 pF | 3.3k | 3.54 MHz | ± 10%            |

|        | 5.1k | 2.43 MHz | ± 14%            |

|        | 10k  | 1.30 MHz | ± 17%            |