Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 454 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44t-33e-pt |

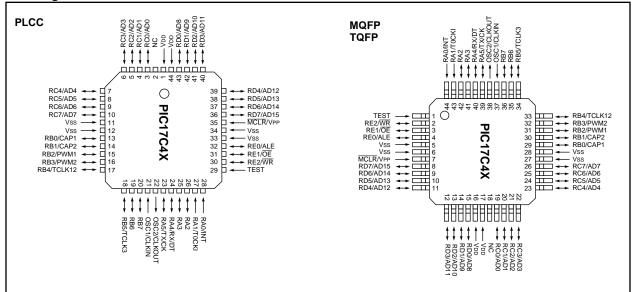

### Pin Diagrams Cont.'d

All devices are available in all package types, listed in Section 21.0, with the following exceptions:

- ROM devices are not available in Windowed CERDIP Packages

- TQFP is not available for the PIC17C42.

### 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC17C4X can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC17C4X uses a modified Harvard architecture. This architecture has the program and data accessed from separate memories. So the device has a program memory bus and a data memory bus. This improves bandwidth over traditional von Neumann architecture, where program and data are fetched from the same memory (accesses over the same bus). Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. PIC17C4X opcodes are 16-bits wide, enabling single word instructions. The full 16-bit wide program memory bus fetches a 16-bit instruction in a single cycle. A twostage pipeline overlaps fetch and execution of instructions. Consequently, all instructions execute in a single cycle (121 ns @ 33 MHz), except for program branches and two special instructions that transfer data between program and data memory.

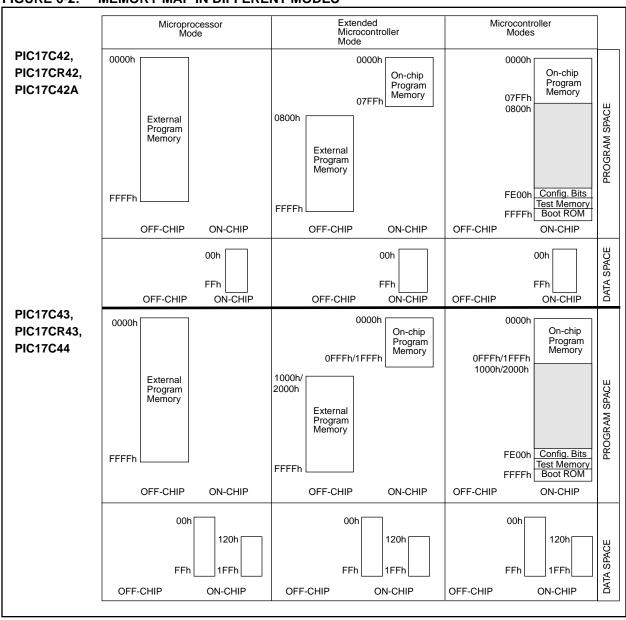

The PIC17C4X can address up to 64K x 16 of program memory space.

The **PIC17C42** and **PIC17C42A** integrate 2K x 16 of EPROM program memory on-chip, while the **PIC17CR42** has 2K x 16 of ROM program memory on-chip.

The **PIC17C43** integrates 4K x 16 of EPROM program memory, while the **PIC17CR43** has 4K x 16 of ROM program memory.

The **PIC17C44** integrates 8K x 16 EPROM program memory.

Program execution can be internal only (microcontroller or protected microcontroller mode), external only (microprocessor mode) or both (extended microcontroller mode). Extended microcontroller mode does not allow code protection.

The PIC17CXX can directly or indirectly address its register files or data memory. All special function registers, including the Program Counter (PC) and Working Register (WREG), are mapped in the data memory. The PIC17CXX has an orthogonal (symmetrical) instruction set that makes it possible to carry out any operation on any register using any addressing mode. This symmetrical nature and lack of 'special optimal situations' make programming with the PIC17CXX simple yet efficient. In addition, the learning curve is reduced significantly.

One of the PIC17CXX family architectural enhancements from the PIC16CXX family allows two file registers to be used in some two operand instructions. This allows data to be moved directly between two registers without going through the WREG register. This increases performance and decreases program memory usage.

The PIC17CXX devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift, and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature.

The WREG register is an 8-bit working register used for ALU operations.

All PIC17C4X devices (except the PIC17C42) have an 8 x 8 hardware multiplier. This multiplier generates a 16-bit result in a single cycle.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC), and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

Although the ALU does not perform signed arithmetic, the Overflow bit (OV) can be used to implement signed math. Signed arithmetic is comprised of a magnitude and a sign bit. The overflow bit indicates if the magnitude overflows and causes the sign bit to change state. Signed math can have greater than 7-bit values (magnitude), if more than one byte is used. The use of the overflow bit only operates on bit6 (MSb of magnitude) and bit7 (sign bit) of the value in the ALU. That is, the overflow bit is not useful if trying to implement signed math where the magnitude, for example, is 11-bits. If the signed math values are greater than 7-bits (15-, 24-or 31-bit), the algorithm must ensure that the low order bytes ignore the overflow status bit.

Care should be taken when adding and subtracting signed numbers to ensure that the correct operation is executed. Example 3-1 shows an item that must be taken into account when doing signed arithmetic on an ALU which operates as an unsigned machine.

#### **EXAMPLE 3-1: SIGNED MATH**

| Hex Value    | Signed Value<br>Math | Unsigned Value<br>Math |

|--------------|----------------------|------------------------|

| FFh          | -127                 | 255                    |

| <u>+ 01h</u> | <u>+ 1</u>           | <u>+ 1</u>             |

| = ?          | = -126  (FEh)        | = 0 (00h);             |

|              |                      | Carry bit = $1$        |

Signed math requires the result in REG to be FEh (-126). This would be accomplished by subtracting one as opposed to adding one.

Simplified block diagrams are shown in Figure 3-1 and Figure 3-2. The descriptions of the device pins are listed in Table 3-1.

TABLE 4-4: INITIALIZATION CONDITIONS FOR SPECIAL FUNCTION REGISTERS

| Register              | Address | Power-on R | Reset |      | LR Reset<br>DT Reset |      | from SLEEP<br>h interrupt |

|-----------------------|---------|------------|-------|------|----------------------|------|---------------------------|

| Unbanked              |         |            |       |      |                      |      |                           |

| INDF0                 | 00h     | 0000 000   | 00    | 0000 | 0000                 | 0000 | 0000                      |

| FSR0                  | 01h     | XXXX XXX   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| PCL                   | 02h     | 0000h      |       | 000  | )0h                  | PC + | 1(2)                      |

| PCLATH                | 03h     | 0000 000   | 00    | 0000 | 0000                 | uuuu | uuuu                      |

| ALUSTA                | 04h     | 1111 xx    | xx    | 1111 | uuuu                 | 1111 | uuuu                      |

| T0STA                 | 05h     | 0000 000   | 0 –   | 0000 | 000-                 | 0000 | 000-                      |

| CPUSTA <sup>(3)</sup> | 06h     | 11 11-     |       | 11   | dd                   | uu   | dd                        |

| INTSTA                | 07h     | 0000 000   | 00    | 0000 | 0000                 | uuuu | uuuu <mark>(1)</mark>     |

| INDF1                 | 08h     | 0000 000   | 00    | 0000 | 0000                 | uuuu | uuuu                      |

| FSR1                  | 09h     | xxxx xxx   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| WREG                  | 0Ah     | xxxx xxx   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| TMR0L                 | 0Bh     | xxxx xxx   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| TMR0H                 | 0Ch     | XXXX XXX   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| TBLPTRL (4)           | 0Dh     | xxxx xxx   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| TBLPTRH (4)           | 0Eh     | xxxx xxx   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| TBLPTRL (5)           | 0Dh     | 0000 000   | 00    | 0000 | 0000                 | uuuu | uuuu                      |

| TBLPTRH (5)           | 0Eh     | 0000 000   | 00    | 0000 | 0000                 | uuuu | uuuu                      |

| BSR                   | 0Fh     | 0000 000   | 00    | 0000 | 0000                 | uuuu | uuuu                      |

| Bank 0                |         |            |       |      |                      |      |                           |

| PORTA                 | 10h     | 0-xx xx    | xx    | 0-uu | uuuu                 | uuuu | uuuu                      |

| DDRB                  | 11h     | 1111 11:   | 11    | 1111 | 1111                 | uuuu | uuuu                      |

| PORTB                 | 12h     | xxxx xxx   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| RCSTA                 | 13h     | 0000 -00   | 0x    | 0000 | -00u                 | uuuu | -uuu                      |

| RCREG                 | 14h     | xxxx xxx   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| TXSTA                 | 15h     | 0000:      | 1x    | 0000 | 1u                   | uuuu | uu                        |

| TXREG                 | 16h     | XXXX XXX   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| SPBRG                 | 17h     | XXXX XXX   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| Bank 1                |         |            |       |      |                      |      |                           |

| DDRC                  | 10h     | 1111 11:   | 11    | 1111 | 1111                 | uuuu | uuuu                      |

| PORTC                 | 11h     | XXXX XXX   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| DDRD                  | 12h     | 1111 11:   | 11    | 1111 | 1111                 | uuuu | uuuu                      |

| PORTD                 | 13h     | xxxx xxx   | xx    | uuuu | uuuu                 | uuuu | uuuu                      |

| DDRE                  | 14h     | 1:         | 11    |      | -111                 |      | -uuu                      |

| PORTE                 | 15h     | x:         | xx    |      | -uuu                 |      | -uuu                      |

| PIR                   | 16h     | 0000 003   | 10    | 0000 | 0010                 | uuuu | uuuu(1)                   |

| PIE                   | 17h     | 0000 000   | 00    | 0000 | 0000                 | uuuu | uuuu                      |

Legend: u = unchanged, x = unknown, - = unimplemented read as '0', <math>q = value depends on condition.

Note 1: One or more bits in INTSTA, PIR will be affected (to cause wake-up).

- 3: See Table 4-3 for reset value of specific condition.

- 4: Only applies to the PIC17C42.

- 5: Does not apply to the PIC17C42.

<sup>2:</sup> When the wake-up is due to an interrupt and the GLINTD bit is cleared, the PC is loaded with the interrupt vector.

NOTES:

TABLE 6-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |

|------------------------------|-------------------------------|-------------------------------------------------|

| Microprocessor               | No Access                     | No Access                                       |

| Microcontroller              | Access                        | Access                                          |

| Extended<br>Microcontroller  | Access                        | No Access                                       |

| Protected<br>Microcontroller | Access                        | Access                                          |

The PIC17C4X can operate in modes where the program memory is off-chip. They are the microprocessor and extended microcontroller modes. The microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

FIGURE 6-2: MEMORY MAP IN DIFFERENT MODES

**TABLE 6-3: SPECIAL FUNCTION REGISTERS**

| Address            | Name    | Bit 7        | Bit 6          | Bit 5        | Bit 4        | Bit 3         | Bit 2         | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------|--------------|----------------|--------------|--------------|---------------|---------------|-------------|-------------|-------------------------------|-------------------------------------|

| Unbanke            | ed      | •            |                |              |              |               |               | •           |             |                               | •                                   |

| 00h                | INDF0   | Uses con     | tents of FSI   | R0 to addres | ss data mem  | ory (not a p  | hysical regis | ster)       |             |                               |                                     |

| 01h                | FSR0    | Indirect da  | ata memory     | address po   | ointer 0     |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 02h                | PCL     | Low order    | r 8-bits of P  | С            |              |               |               |             |             | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH  | Holding re   | egister for u  | pper 8-bits  | of PC        |               |               |             |             | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA  | FS3          | FS2            | FS1          | FS0          | OV            | Z             | DC          | С           | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA   | INTEDG       | T0SE           | T0CS         | PS3          | PS2           | PS1           | PS0         | _           | 0000 000-                     | 0000 000-                           |

| 06h <sup>(2)</sup> | CPUSTA  | _            | _              | STKAV        | GLINTD       | TO            | PD            | _           | _           | 11 11                         | 11 qq                               |

| 07h                | INTSTA  | PEIF         | T0CKIF         | T0IF         | INTF         | PEIE          | T0CKIE        | TOIE        | INTE        | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1   | Uses con     | tents of FSI   | R1 to addres | ss data mem  | lory (not a p | hysical regis | ster)       |             |                               |                                     |

| 09h                | FSR1    | Indirect da  | ata memory     | address po   | ointer 1     |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG    | Working r    | egister        |              |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L   | TMR0 reg     | gister; low b  | yte          |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H   | TMR0 reg     | jister; high l | oyte         |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 0Dh                | TBLPTRL | Low byte     | of program     | memory tab   | ole pointer  |               |               |             |             | (4)                           | (4)                                 |

| 0Eh                | TBLPTRH | High byte    | of program     | memory tal   | ble pointer  |               |               |             |             | (4)                           | (4)                                 |

| 0Fh                | BSR     | Bank sele    | ct register    |              |              |               |               |             |             | 0000 0000                     | 0000 0000                           |

| Bank 0             |         | •            |                |              |              |               |               |             |             |                               | •                                   |

| 10h                | PORTA   | RBPU         | _              | RA5          | RA4          | RA3           | RA2           | RA1/T0CKI   | RA0/INT     | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB    | Data dired   | ction registe  | er for PORTE | 3            |               |               |             |             | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB   | PORTB d      | ata latch      |              |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA   | SPEN         | RX9            | SREN         | CREN         | _             | FERR          | OERR        | RX9D        | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG   | Serial por   | t receive re   | gister       |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA   | CSRC         | TX9            | TXEN         | SYNC         | _             | _             | TRMT        | TX9D        | 00001x                        | 00001u                              |

| 16h                | TXREG   | Serial por   | t transmit re  | egister      |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG   | Baud rate    | generator      | register     |              |               |               |             |             | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |         | •            |                |              |              |               |               |             |             |                               | •                                   |

| 10h                | DDRC    | Data direc   | ction registe  | er for PORT  | C            |               |               |             |             | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC   | RC7/<br>AD7  | RC6/<br>AD6    | RC5/<br>AD5  | RC4/<br>AD4  | RC3/<br>AD3   | RC2/<br>AD2   | RC1/<br>AD1 | RC0/<br>AD0 | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD    | Data dired   | ction registe  | er for PORTI | 5            |               |               |             |             | 1111 1111                     | 1111 1111                           |

| 13h                | PORTD   | RD7/<br>AD15 | RD6/<br>AD14   | RD5/<br>AD13 | RD4/<br>AD12 | RD3/<br>AD11  | RD2/<br>AD10  | RD1/<br>AD9 | RD0/<br>AD8 | xxxx xxxx                     | uuuu uuuu                           |

| 14h                | DDRE    | Data dired   | ction registe  | er for PORTE | <u>.</u>     | 1             | •             |             | •           | 111                           | 111                                 |

| 15h                | PORTE   | _            | _              | _            | _            | _             | RE2/WR        | RE1/OE      | RE0/ALE     | xxx                           | uuu                                 |

| 16h                | PIR     | RBIF         | TMR3IF         | TMR2IF       | TMR1IF       | CA2IF         | CA1IF         | TXIF        | RCIF        | 0000 0010                     | 0000 0010                           |

| 17h                | PIE     | RBIE         | TMR3IE         | TMR2IE       | TMR1IE       | CA2IE         | CA1IE         | TXIE        | RCIE        | 0000 0000                     | 0000 0000                           |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1: from or transferred to the upper byte of the program counter. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  status bits in CPUSTA are not affected by a MCLR reset.

Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset. The following values are for both TBLPTRL and TBLPTRH:

All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000)

except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

The PRODL and PRODH registers are not implemented on the PIC17C42.

### 7.1 <u>Table Writes to Internal Memory</u>

A table write operation to internal memory causes a long write operation. The long write is necessary for programming the internal EPROM. Instruction execution is halted while in a long write cycle. The long write will be terminated by any enabled interrupt. To ensure that the EPROM location has been well programmed, a minimum programming time is required (see specification #D114). Having only one interrupt enabled to terminate the long write ensures that no unintentional interrupts will prematurely terminate the long write.

The sequence of events for programming an internal program memory location should be:

- Disable all interrupt sources, except the source to terminate EPROM program write.

- 2. Raise MCLR/VPP pin to the programming voltage.

- 3. Clear the WDT.

- 4. Do the table write. The interrupt will terminate the long write.

- 5. Verify the memory location (table read).

Note: Programming requirements must be met. See timing specification in electrical specifications for the desired device. Violating these specifications (including temperature) may result in EPROM locations that are not fully programmed and may lose their state over time.

#### 7.1.1 TERMINATING LONG WRITES

An interrupt source or reset are the only events that terminate a long write operation. Terminating the long write from an interrupt source requires that the interrupt enable and flag bits are set. The GLINTD bit only enables the vectoring to the interrupt address.

If the TOCKI, RAO/INT, or TMR0 interrupt source is used to terminate the long write; the interrupt flag, of the highest priority enabled interrupt, will terminate the long write and automatically be cleared.

- Note 1: If an interrupt is pending, the TABLWT is aborted (an NOP is executed). The highest priority pending interrupt, from the TOCKI, RAO/INT, or TMR0 sources that is enabled, has its flag cleared.

- Note 2: If the interrupt is not being used for the program write timing, the interrupt should be disabled. This will ensure that the interrupt is not lost, nor will it terminate the long write prematurely.

If a peripheral interrupt source is used to terminate the long write, the interrupt enable and flag bits must be set. The interrupt flag will not be automatically cleared upon the vectoring to the interrupt vector address.

If the GLINTD bit is cleared prior to the long write, when the long write is terminated, the program will branch to the interrupt vector.

If the GLINTD bit is set prior to the long write, when the long write is terminated, the program will not vector to the interrupt address.

TABLE 7-1: INTERRUPT - TABLE WRITE INTERACTION

| Interrupt<br>Source     | GLINTD | Enable<br>Bit | Flag<br>Bit | Action                                                                                                        |

|-------------------------|--------|---------------|-------------|---------------------------------------------------------------------------------------------------------------|

| RA0/INT, TMR0,<br>T0CKI | 0      | 1             | 1           | Terminate long table write (to internal program memory), branch to interrupt vector (branch clears flag bit). |

|                         | 0      | 1             | 0           | None                                                                                                          |

|                         | 1      | 0             | x           | None                                                                                                          |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is automatically cleared).                     |

| Peripheral              | 0      | 1             | 1           | Terminate table write, branch to interrupt vector.                                                            |

|                         | 0      | 1             | 0           | None                                                                                                          |

|                         | 1      | 0             | x           | None                                                                                                          |

|                         | 1      | 1             | 1           | Terminate table write, do not branch to interrupt vector (flag is set).                                       |

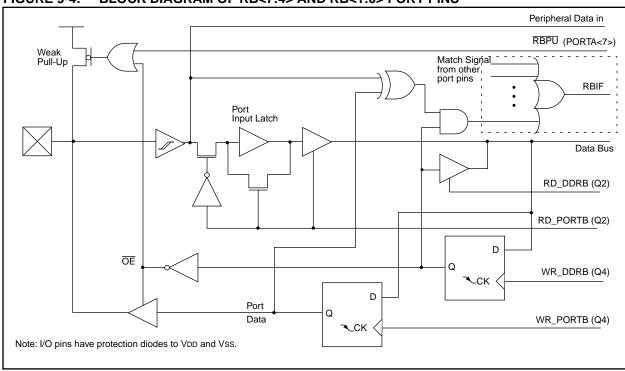

## 9.2 PORTB and DDRB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is DDRB. A '1' in DDRB configures the corresponding port pin as an input. A '0' in the DDRB register configures the corresponding port pin as an output. Reading PORTB reads the status of the pins, whereas writing to it will write to the port latch.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (PORTA<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are enabled on any reset.

PORTB also has an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB0 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB0) are compared with the value in the PORTB data latch. The "mismatch" outputs of RB7:RB0 are OR'ed together to generate the PORTB Interrupt Flag RBIF (PIR<7>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt by:

- Read-Write PORTB (such as; MOVPF PORTB, PORTB). This will end mismatch condition.

- b) Then, clear the RBIF bit.

A mismatch condition will continue to set the RBIF bit. Reading then writing PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on this port, allows easy interface to a key pad and make it possible for wake-up on key-depression. For an example, refer to AN552 in the *Embedded Control Handbook*.

The interrupt on change feature is recommended for wake-up on operations where PORTB is only used for the interrupt on change feature and key depression operation.

FIGURE 9-4: BLOCK DIAGRAM OF RB<7:4> AND RB<1:0> PORT PINS

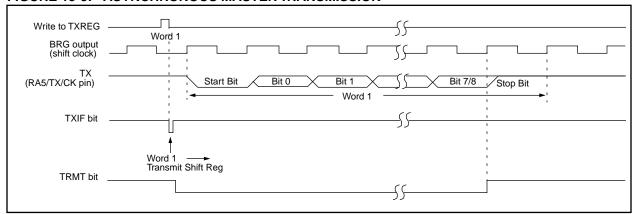

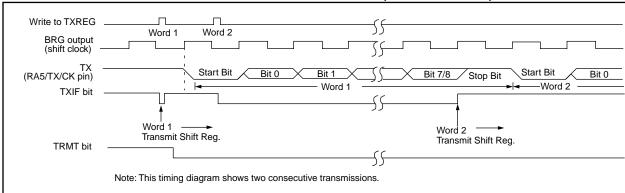

## FIGURE 13-5: ASYNCHRONOUS MASTER TRANSMISSION

## FIGURE 13-6: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

TABLE 13-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address     | Name                                           | Bit 7                              | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0     | Value on<br>Power-on<br>Reset | Value on all other resets (Note1) |

|-------------|------------------------------------------------|------------------------------------|--------|--------|--------|-------|-------|-------|-----------|-------------------------------|-----------------------------------|

| 16h, Bank 1 | PIR                                            | RBIF                               | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF      | 0000 0010                     | 0000 0010                         |

| 13h, Bank 0 | RCSTA                                          | SPEN                               | RX9    | SREN   | CREN   | _     | FERR  | OERR  | RX9D      | 0000 -00x                     | 0000 -00u                         |

| 16h, Bank 0 | TXREG                                          | KREG Serial port transmit register |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                   |

| 17h, Bank 1 | PIE                                            | RBIE                               | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE      | 0000 0000                     | 0000 0000                         |

| 15h, Bank 0 | TXSTA                                          | CSRC                               | TX9    | TXEN   | SYNC   | _     | _     | TRMT  | TX9D      | 00001x                        | 00001u                            |

| 17h, Bank 0 | 17h, Bank 0 SPBRG Baud rate generator register |                                    |        |        |        |       |       |       | xxxx xxxx | uuuu uuuu                     |                                   |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

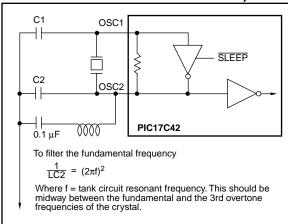

## FIGURE 14-3: CRYSTAL OPERATION, OVERTONE CRYSTALS (XT OSC CONFIGURATION)

TABLE 14-2: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Oscillator<br>Type | Resonator<br>Frequency         | Capacitor Range<br>C1 = C2               |

|--------------------|--------------------------------|------------------------------------------|

| LF                 | 455 kHz<br>2.0 MHz             | 15 - 68 pF<br>10 - 33 pF                 |

| XT                 | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 22 - 68 pF<br>33 - 100 pF<br>33 - 100 pF |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

| 455 kHz                                           | Panasonic EFO-A455K04B | ± 0.3% |  |  |  |

|---------------------------------------------------|------------------------|--------|--|--|--|

| 2.0 MHz                                           | Murata Erie CSA2.00MG  | ± 0.5% |  |  |  |

| 4.0 MHz                                           | Murata Erie CSA4.00MG  | ± 0.5% |  |  |  |

| 8.0 MHz                                           | Murata Erie CSA8.00MT  | ± 0.5% |  |  |  |

| 16.0 MHz   Murata Erie CSA16.00MX   ± 0.5%        |                        |        |  |  |  |

| Resonators used did not have built-in capacitors. |                        |        |  |  |  |

TABLE 14-3: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Freq                  | C1         | C2               |

|-------------|-----------------------|------------|------------------|

| LF          | 32 kHz <sup>(1)</sup> | 100-150 pF | 100-150 pF       |

|             | 1 MHz                 | 10-33 pF   | 10-33 pF         |

|             | 2 MHz                 | 10-33 pF   | 10-33 pF         |

| XT          | 2 MHz                 | 47-100 pF  | 47-100 pF        |

|             | 4 MHz                 | 15-68 pF   | 15-68 pF         |

|             | 8 MHz <sup>(2)</sup>  | 15-47 pF   | 15-47 pF         |

|             | 16 MHz                | TBD        | TBD              |

|             | 25 MHz                | 15-47 pF   | 15-47 pF         |

|             | 32 MHz <sup>(3)</sup> | 0 (3)      | <sub>0</sub> (3) |

Higher capacitance increases the stability of the oscillator but also increases the start-up time and the oscillator current. These values are for design guidance only. Rs may be required in XT mode to avoid overdriving the crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values for external components.

- Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

- 2: Rs of  $330\Omega$  is required for a capacitor combination of 15/15 pF.

- 3: Only the capacitance of the board was present.

#### **Crystals Used:**

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM |

|------------|-----------------------|----------|

| 1.0 MHz    | ECS-10-13-1           | ± 50 PPM |

| 2.0 MHz    | ECS-20-20-1           | ± 50 PPM |

| 4.0 MHz    | ECS-40-20-1           | ± 50 PPM |

| 8.0 MHz    | ECS ECS-80-S-4        | ± 50 PPM |

|            | ECS-80-18-1           |          |

| 16.0 MHz   | ECS-160-20-1          | TBD      |

| 25 MHz     | CTS CTS25M            | ± 50 PPM |

| 32 MHz     | CRYSTEK HF-2          | ± 50 PPM |

|            |                       |          |

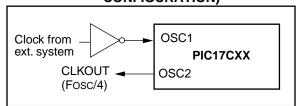

#### 14.2.3 EXTERNAL CLOCK OSCILLATOR

In the EC oscillator mode, the OSC1 input can be driven by CMOS drivers. In this mode, the OSC1/CLKIN pin is hi-impedance and the OSC2/CLK-OUT pin is the CLKOUT output (4 Tosc).

FIGURE 14-4: EXTERNAL CLOCK INPUT OPERATION (EC OSC CONFIGURATION)

**CLRWDT Clear Watchdog Timer** Syntax: [label] CLRWDT Operands: None Operation:  $00h \to WDT$  $0 \rightarrow WDT$  postscaler,  $1 \rightarrow \overline{TO}$  $1 \rightarrow \overline{PD}$ TO, PD Status Affected: Encoding: 0000 0000 0000 0100 Description: CLRWDT instruction resets the watchdog timer. It also resets the prescaler of the WDT. Status bits  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  are set. Words: 1

Cycles: 1

Q Cycle Activity:

| Q1     | Q2                         | Q3      | Q4  |

|--------|----------------------------|---------|-----|

| Decode | Read<br>register<br>ALUSTA | Execute | NOP |

Example: CLRWDT

Before Instruction

WDT counter ?

After Instruction

WDT counter 0x00 WDT Postscaler 0 TO 1  $\overline{\mathsf{PD}}$

| COMF              | Compler                        | ment f       |                                                 |           |

|-------------------|--------------------------------|--------------|-------------------------------------------------|-----------|

| Syntax:           | [ label ]                      | COMF         | f,d                                             |           |

| Operands:         | $0 \le f \le 25$ $d \in [0,1]$ | 55           |                                                 |           |

| Operation:        | $(\overline{f}) \rightarrow ($ | dest)        |                                                 |           |

| Status Affected:  | Z                              |              |                                                 |           |

| Encoding:         | 0001                           | 001d         | ffff                                            | ffff      |

| Description:      | mented. If                     | 'd' is 0 the | ister 'f' are<br>e result is s<br>e result is s | stored in |

| Words:            | 1                              |              |                                                 |           |

| Cycles:           | 1                              |              |                                                 |           |

| Q Cvcle Activity: |                                |              |                                                 |           |

Read register 'f' COMF

Q2

Q3

Execute

REG1,0

Q4

Write

register 'f'

Before Instruction

REG1 0x13

After Instruction

Q1

Decode

Example:

REG1 0x13 WREG 0xEC

| TABLRD            | Table Re    | ead      |           |

|-------------------|-------------|----------|-----------|

| Example1:         | TABLRD      | 1, 1,    | REG ;     |

| Before Instruc    | tion        |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY(           | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | vrite co | mpletion) |

| REG               |             | =        | 0xAA      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             | =        | 0xA357    |

| MEMORY(           | (TBLPTR)    | =        | 0x5678    |

| Example2:         | TABLRD      | 0, 0,    | REG ;     |

| Before Instruc    | tion        |          |           |

| REG               |             | =        | 0x53      |

| TBLATH            |             | =        | 0xAA      |

| TBLATL            |             | =        | 0x55      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY(           | (TBLPTR)    | =        | 0x1234    |

| After Instruction | on (table v | vrite co | mpletion) |

| REG               |             | =        | 0x55      |

| TBLATH            |             | =        | 0x12      |

| TBLATL            |             | =        | 0x34      |

| TBLPTR            |             | =        | 0xA356    |

| MEMORY(           | (TBLPTR)    | =        | 0x1234    |

|                   |             |          |           |

| TABLWT           | Table Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] TABLWT t,i,f                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Operands:        | $0 \le f \le 255$<br>$i \in [0,1]$<br>$t \in [0,1]$                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Operation:       | If t = 0,<br>f $\rightarrow$ TBLATL;<br>If t = 1,<br>f $\rightarrow$ TBLATH;<br>TBLAT $\rightarrow$ Prog Mem (TBLPTR)<br>If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Encoding:        | 1010 11ti ffff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| Description:     | <ol> <li>Load value in 'f' into 16-bit table latch (TBLAT)         If t = 0: load into low byte;         If t = 1: load into high byte         </li> <li>The contents of TBLAT is written to the program memory location pointed to by TBLPTR         If TBLPTR points to external program memory location, then the instruction takes two-cycle If TBLPTR points to an internal EPROM location, then the instruction is terminated when an interrupt is received.</li> </ol> |  |  |  |  |

**Note:** The MCLR/VPP pin must be at the programming voltage for successful programming of internal memory.

If  $\overline{MCLR}/VPP = VDD$

the programming sequence of internal memory will be executed, but will not be successful (although the internal memory location may be disturbed)

The TBLPTR can be automatically incremented

If i = 0; TBLPTR is not incremented

If i = 1; TBLPTR is incremented

Words: 1

Cycles: 2 (many if write is to on-chip EPROM program memory)

Q Cycle Activity:

| Q1     | Q2           | Q3      | Q4        |

|--------|--------------|---------|-----------|

| Decode | Read         | Execute | Write     |

|        | register 'f' |         | register  |

|        |              |         | TBLATH or |

|        |              |         | TBLATL    |

**Applicable Devices** 42 R42 42A 43 R43 44

## 17.3 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created using one of the following formats:

1. TppS2ppS

2. TppS

| 2. TppS |                                       |      |                                    |  |

|---------|---------------------------------------|------|------------------------------------|--|

| Т       |                                       |      |                                    |  |

| F       | Frequency                             | Т    | Time                               |  |

| Lowerd  | case symbols (pp) and their meanings: |      |                                    |  |

| рр      |                                       |      |                                    |  |

| ad      | Address/Data                          | ost  | Oscillator Start-up Timer          |  |

| al      | ALE                                   | pwrt | Power-up Timer                     |  |

| СС      | Capture1 and Capture2                 | rb   | PORTB                              |  |

| ck      | CLKOUT or clock                       | rd   | RD                                 |  |

| dt      | Data in                               | rw   | $\overline{RD}$ or $\overline{WR}$ |  |

| in      | INT pin                               | tO   | TOCKI                              |  |

| io      | I/O port                              | t123 | TCLK12 and TCLK3                   |  |

| mc      | MCLR                                  | wdt  | Watchdog Timer                     |  |

| oe      | ŌĒ                                    | wr   | WR                                 |  |

| os      | OSC1                                  |      |                                    |  |

| Upper   | case symbols and their meanings:      |      |                                    |  |

| S       |                                       |      |                                    |  |

| D       | Driven                                | L    | Low                                |  |

| E       | Edge                                  | P    | Period                             |  |

| F       | Fall                                  | R    | Rise                               |  |

| Н       | High                                  | V    | Valid                              |  |

| 1       | Invalid (Hi-impedance)                | Z    | Hi-impedance                       |  |

Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44

## PIC17CR42/42A/43/R43/44 ELECTRICAL CHARACTERISTICS

### **Absolute Maximum Ratings †**

| Ambient temperature under bias                                                                                           | 55 to +125°C                                    |

|--------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Storage temperature                                                                                                      | 65°C to +150°C                                  |

| /oltage on VDD with respect to Vss                                                                                       | 0 to +7.5\                                      |

| /oltage on MCLR with respect to Vss (Note 2)                                                                             | 0.6V to +14V                                    |

| /oltage on RA2 and RA3 with respect to Vss                                                                               | 0.6V to +14V                                    |

| /oltage on all other pins with respect to Vss                                                                            | 0.6V to VDD + 0.6V                              |

| Total power dissipation (Note 1)                                                                                         | 1.0W                                            |

| Maximum current out of Vss pin(s) - total                                                                                | 250 mA                                          |

| Maximum current into VDD pin(s) - total                                                                                  | 200 mA                                          |

| nput clamp current, liκ (Vi < 0 or Vi > VDD)                                                                             | ±20 mA                                          |

| Dutput clamp current, loκ (Vo < 0 or Vo > VDD)                                                                           | ±20 mA                                          |

| Maximum output current sunk by any I/O pin (except RA2 and RA3)                                                          | 35 mA                                           |

| Maximum output current sunk by RA2 or RA3 pins                                                                           | 60 mA                                           |

| Maximum output current sourced by any I/O pin                                                                            | 20 mA                                           |

| Maximum current sunk by PORTA and PORTB (combined)                                                                       | 150 mA                                          |

| Maximum current sourced by PORTA and PORTB (combined)                                                                    | 100 m/                                          |

| Maximum current sunk by PORTC, PORTD and PORTE (combined)                                                                | 150 m <i>A</i>                                  |

| Maximum current sourced by PORTC, PORTD and PORTE (combined)                                                             | 100 m/                                          |

| <b>Note 1:</b> Power dissipation is calculated as follows: Pdis = $VDD \times \{IDD - \sum IOH\} + \sum \{(VDD - VDD)\}$ | $\sqrt{OH} \times IOH + \Sigma(VOL \times IOL)$ |

Note 2: Voltage spikes below Vss at the MCLR pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of  $50-100\Omega$  should be used when applying a "low" level to the  $\overline{MCLR}$  pin rather than pulling this pin directly to Vss.

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

© 1996 Microchip Technology Inc.

## Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44

## 19.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|-------------|-----------|----------------------------------------|

| 2.TppS      | 4.Ts      | (I <sup>2</sup> C specifications only) |

| T |           |   |      |  |

|---|-----------|---|------|--|

| F | Frequency | T | Time |  |

Lowercase symbols (pp) and their meanings:

| рр |                       |      |                                    |

|----|-----------------------|------|------------------------------------|

| ad | Address/Data          | ost  | Oscillator Start-Up Timer          |

| al | ALE                   | pwrt | Power-Up Timer                     |

| СС | Capture1 and Capture2 | rb   | PORTB                              |

| ck | CLKOUT or clock       | rd   | RD                                 |

| dt | Data in               | rw   | $\overline{RD}$ or $\overline{WR}$ |

| in | INT pin               | t0   | T0CKI                              |

| io | I/O port              | t123 | TCLK12 and TCLK3                   |

| mc | MCLR                  | wdt  | Watchdog Timer                     |

| oe | ŌĒ                    | wr   | WR                                 |

| os | OSC1                  |      |                                    |

|    |                       |      |                                    |

Uppercase symbols and their meanings:

| S |                        |   |              |

|---|------------------------|---|--------------|

| D | Driven                 | L | Low          |

| E | Edge                   | P | Period       |

| F | Fall                   | R | Rise         |

| Н | High                   | V | Valid        |

| 1 | Invalid (Hi-impedance) | Z | Hi-impedance |

Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44

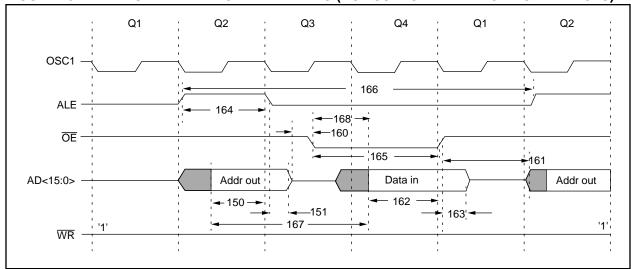

FIGURE 19-12: MEMORY INTERFACE READ TIMING (NOT SUPPORTED IN PIC17LC4X DEVICES)

TABLE 19-12: MEMORY INTERFACE READ REQUIREMENTS (NOT SUPPORTED IN PIC17LC4X DEVICES)

| Parameter<br>No. | Sym      | Characteristic                                         | Min           | Тур†      | Max          | Units | Conditions |

|------------------|----------|--------------------------------------------------------|---------------|-----------|--------------|-------|------------|

| 150              | TadV2alL | AD15:AD0 (address) valid to ALE↓ (address setup time)  | 0.25Tcy - 10  | _         | _            | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)        | 5*            | _         | _            | ns    |            |

| 160              | TadZ2oeL | AD15:AD0 hi-impedance to <del>OE</del> ↓               | 0*            | _         | _            | ns    |            |

| 161              | ToeH2adD | OE↑ to AD15:AD0 driven                                 | 0.25Tcy - 15  | _         | _            | ns    |            |

| 162              | TadV2oeH | Data in valid before <del>OE</del> ↑ (data setup time) | 35            | _         | _            | ns    |            |

| 163              | ToeH2adl | OE↑to data in invalid (data hold time)                 | 0             | _         | _            | ns    |            |

| 164              | TalH     | ALE pulse width                                        | _             | 0.25Tcy § | _            | ns    |            |

| 165              | ToeL     | OE pulse width                                         | 0.5Tcy - 35 § | _         | _            | ns    |            |

| 166              | TalH2alH | ALE↑ to ALE↑(cycle time)                               | _             | Tcy §     | _            | ns    |            |

| 167              | Tacc     | Address access time                                    | _             | _         | 0.75Tcy - 30 | ns    |            |

| 168              | Toe      | Output enable access time (OE low to Data Valid)       | _             | _         | 0.5Tcy - 45  | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>§</sup> This specification ensured by design.

Applicable Devices 42 R42 42A 43 R43 44

## 20.0 PIC17CR42/42A/43/R43/44 DC AND AC CHARACTERISTICS

The graphs and tables provided in this section are for design guidance and are not tested nor guaranteed. In some graphs or tables the data presented is outside specified operating range (e.g. outside specified VDD range). This is for information only and devices are ensured to operate properly only within the specified range.

The data presented in this section is a statistical summary of data collected on units from different lots over a period of time. "Typical" represents the mean of the distribution while "max" or "min" represents (mean +  $3\sigma$ ) and (mean -  $3\sigma$ ) respectively where  $\sigma$  is standard deviation.

TABLE 20-1: PIN CAPACITANCE PER PACKAGE TYPE

| Pin Name                            | Typical Capacitance (pF) |             |             |             |  |

|-------------------------------------|--------------------------|-------------|-------------|-------------|--|

| riii Naiile                         | 40-pin DIP               | 44-pin PLCC | 44-pin MQFP | 44-pin TQFP |  |

| All pins, except MCLR, VDD, and VSS | 10                       | 10          | 10          | 10          |  |

| MCLR pin                            | 20                       | 20          | 20          | 20          |  |

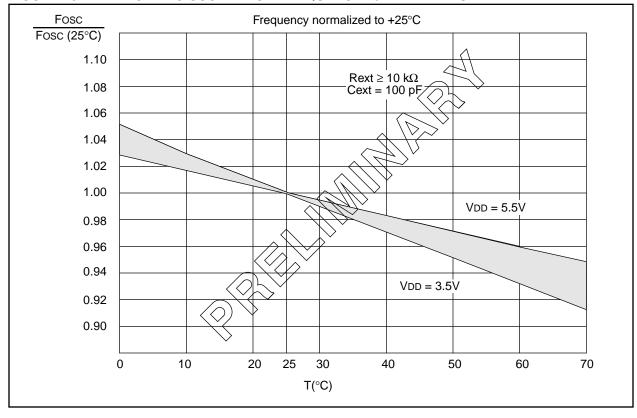

FIGURE 20-1: TYPICAL RC OSCILLATOR FREQUENCY vs. TEMPERATURE

© 1996 Microchip Technology Inc.

## 21.0 PACKAGING INFORMATION

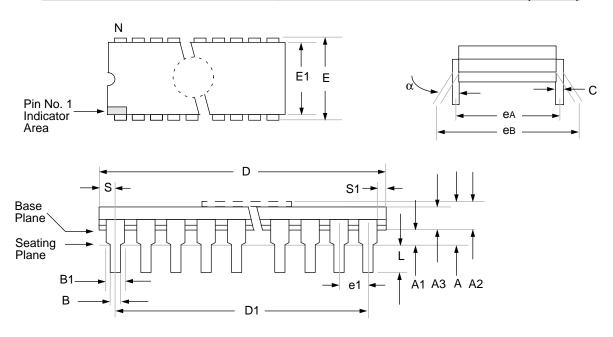

## 21.1 40-Lead Ceramic CERDIP Dual In-line, and CERDIP Dual In-line with Window (600 mil)

| Package Group: Ceramic CERDIP Dual In-Line (CDP) |        |             |           |        |       |           |

|--------------------------------------------------|--------|-------------|-----------|--------|-------|-----------|

|                                                  |        | Millimeters |           | Inches |       |           |

| Symbol                                           | Min    | Max         | Notes     | Min    | Max   | Notes     |

| α                                                | 0°     | 10°         |           | 0°     | 10°   |           |

| Α                                                | 4.318  | 5.715       |           | 0.170  | 0.225 |           |

| A1                                               | 0.381  | 1.778       |           | 0.015  | 0.070 |           |

| A2                                               | 3.810  | 4.699       |           | 0.150  | 0.185 |           |

| A3                                               | 3.810  | 4.445       |           | 0.150  | 0.175 |           |

| В                                                | 0.355  | 0.585       |           | 0.014  | 0.023 |           |

| B1                                               | 1.270  | 1.651       | Typical   | 0.050  | 0.065 | Typical   |

| С                                                | 0.203  | 0.381       | Typical   | 0.008  | 0.015 | Typical   |

| D                                                | 51.435 | 52.705      |           | 2.025  | 2.075 |           |

| D1                                               | 48.260 | 48.260      | Reference | 1.900  | 1.900 | Reference |

| E                                                | 15.240 | 15.875      |           | 0.600  | 0.625 |           |

| E1                                               | 12.954 | 15.240      |           | 0.510  | 0.600 |           |

| e1                                               | 2.540  | 2.540       | Reference | 0.100  | 0.100 | Reference |

| eA                                               | 14.986 | 16.002      | Typical   | 0.590  | 0.630 | Typical   |

| eB                                               | 15.240 | 18.034      |           | 0.600  | 0.710 |           |

| L                                                | 3.175  | 3.810       |           | 0.125  | 0.150 |           |

| N                                                | 40     | 40          |           | 40     | 40    |           |

| S                                                | 1.016  | 2.286       |           | 0.040  | 0.090 |           |

| S1                                               | 0.381  | 1.778       |           | 0.015  | 0.070 |           |

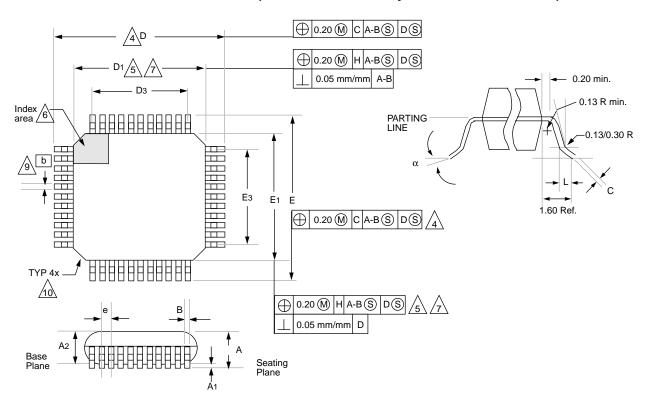

## 21.4 44-Lead Plastic Surface Mount (MQFP 10x10 mm Body 1.6/0.15 mm Lead Form)

| Package Group: Plastic MQFP |             |        |           |        |       |           |

|-----------------------------|-------------|--------|-----------|--------|-------|-----------|

|                             | Millimeters |        |           | Inches |       |           |

| Symbol                      | Min         | Max    | Notes     | Min    | Max   | Notes     |

| α                           | 0°          | 7°     |           | 0°     | 7°    |           |

| Α                           | 2.000       | 2.350  |           | 0.078  | 0.093 |           |

| A1                          | 0.050       | 0.250  |           | 0.002  | 0.010 |           |

| A2                          | 1.950       | 2.100  |           | 0.768  | 0.083 |           |

| b                           | 0.300       | 0.450  | Typical   | 0.011  | 0.018 | Typical   |

| С                           | 0.150       | 0.180  |           | 0.006  | 0.007 |           |

| D                           | 12.950      | 13.450 |           | 0.510  | 0.530 |           |

| D1                          | 9.900       | 10.100 |           | 0.390  | 0.398 |           |

| D3                          | 8.000       | 8.000  | Reference | 0.315  | 0.315 | Reference |

| E                           | 12.950      | 13.450 |           | 0.510  | 0.530 |           |

| E1                          | 9.900       | 10.100 |           | 0.390  | 0.398 |           |

| E3                          | 8.000       | 8.000  | Reference | 0.315  | 0.315 | Reference |

| е                           | 0.800       | 0.800  |           | 0.031  | 0.032 |           |

| L                           | 0.730       | 1.030  |           | 0.028  | 0.041 |           |

| N                           | 44          | 44     |           | 44     | 44    |           |

| СР                          | 0.102       | _      |           | 0.004  | _     |           |

| MP-C C Compiler145                             | PORTD                                 | 19, 34, 60 |

|------------------------------------------------|---------------------------------------|------------|

| MPSIM Software Simulator143, 145               | PORTE                                 | 19, 34, 62 |

| MULLW129                                       | Power-down Mode                       | 105        |

| Multiply Examples                              | Power-on Reset (POR)                  | 15, 99     |

| 16 x 16 Routine50                              | Power-up Timer (PWRT)                 | 15, 99     |

| 16 x 16 Signed Routine51                       | PR1                                   | 20, 35     |

| 8 x 8 Routine49                                | PR2                                   | 20, 35     |

| 8 x 8 Signed Routine49                         | PR3/CA1H                              | 20         |

| MULWF129                                       | PR3/CA1L                              | 20         |

|                                                | PR3H/CA1H                             | 35         |

| A.I.                                           | PR3L/CA1L                             | 35         |

| N                                              | Prescaler Assignments                 | 69         |

|                                                | PRO MATE® Universal Programmer        | 143        |

| NEGW130                                        | PRODH                                 |            |

| NOP130                                         | PRODL                                 |            |

|                                                | Program Counter (PC)                  | 41         |

| 0                                              | Program Memory                        |            |

| O .                                            | External Access Waveforms             | 31         |

| OERR84                                         | External Connection Diagram           |            |

| Opcode Field Descriptions                      | Map                                   |            |

| ·                                              | Modes                                 |            |

| OSC Selection                                  | Extended Microcontroller              | 20         |

| Oscillator                                     | Microcontroller                       |            |

| Configuration                                  | Microprocessor                        |            |

| Crystal100                                     | Protected Microcontroller             | 20         |

| External Clock101                              |                                       |            |

| External Crystal Circuit102                    | Operation                             |            |

| External Parallel Resonant Crystal Circuit 102 | Organization                          | 29         |

| External Series Resonant Crystal Circuit102    | Transfers from Data Memory            |            |

| RC102                                          | Protected Microcontroller             |            |

| RC Frequencies165, 195                         | PS0                                   | ,          |

| Oscillator Start-up Time (Figure)18            | PS1                                   | ,          |

| Oscillator Start-up Timer (OST)15, 99          | PS2                                   | ,          |

| OST15, 99                                      | PS3                                   | 38, 67     |

| OV9, 36                                        | PUSH                                  | 27, 39     |

| Overflow (OV)9                                 | PW1DCH                                | 20, 35     |

|                                                | PW1DCL                                | 20, 35     |

| <b>D</b>                                       | PW2DCH                                | 20, 35     |

| P                                              | PW2DCL                                | 20, 35     |

|                                                | PWM                                   | 71, 75     |

| Package Marking Information210                 | Duty Cycle                            | 76         |

| Packaging Information205                       | External Clock Source                 |            |

| Parameter Measurement Information154           | Frequency vs. Resolution              |            |

| PC (Program Counter)41                         | Interrupts                            |            |

| PCH41                                          | Max Resolution/Frequency for External |            |

| PCL34, 41, 108                                 | Clock Input                           | 77         |

| PCLATH34, 41                                   | Output                                |            |

| PD                                             | Periods                               |            |

| PEIE                                           | PWM1                                  |            |

| PEIF22                                         | PWM1ON                                |            |

| Peripheral Bank42                              | PWM2                                  |            |

| Peripheral Interrupt Enable                    |                                       |            |

| Peripheral Interrupt Request (PIR)24           | PWM2ON                                | •          |

| PICDEM-1 Low-Cost PIC16/17 Demo Board 143, 144 | PWRT                                  | 15, 99     |

| PICDEM-2 Low-Cost PIC16CXX Demo Board 143, 144 |                                       |            |

| PICDEM-3 Low-Cost PIC16C9XXX Demo Board 144    | R                                     |            |

| PICMASTER® RT In-Circuit Emulator143           |                                       |            |

|                                                | RA1/T0CKI pin                         | 67         |

| PICSTART® Low-Cost Development System143       | RBIE                                  |            |

| PIE                                            | RBIF                                  |            |

| Pin Compatible Devices                         | RBPU                                  |            |

| PIR                                            | RC Oscillator                         |            |

| PM0                                            |                                       |            |

| PM199, 106                                     | RC Oscillator Frequencies             | •          |

| POP27, 39                                      | RCIE                                  |            |

| POR15, 99                                      | RCIF                                  |            |

| PORTA19, 34, 53                                | RCREG 19, 34                          |            |

| PORTB                                          | RCSTA 19                              |            |

| PORTC                                          | Reading 16-bit Value                  | 69         |