Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 33MHz                                                                      |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 16KB (8K x 16)                                                             |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                |                                                                            |

| RAM Size                   | 454 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

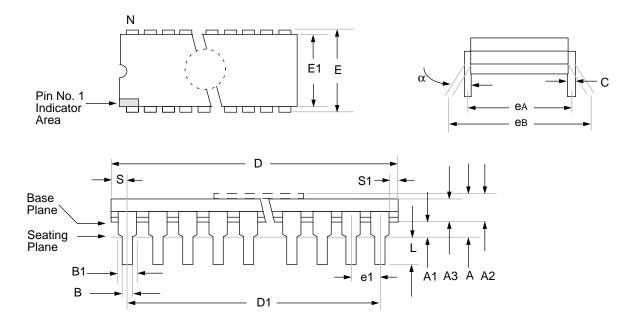

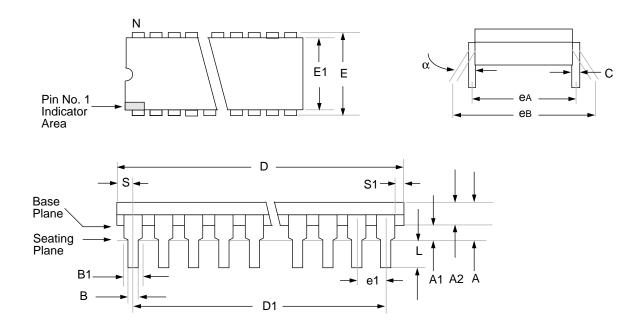

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-QFP                                                                     |

| Supplier Device Package    | 44-MQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17c44t-33i-pq |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

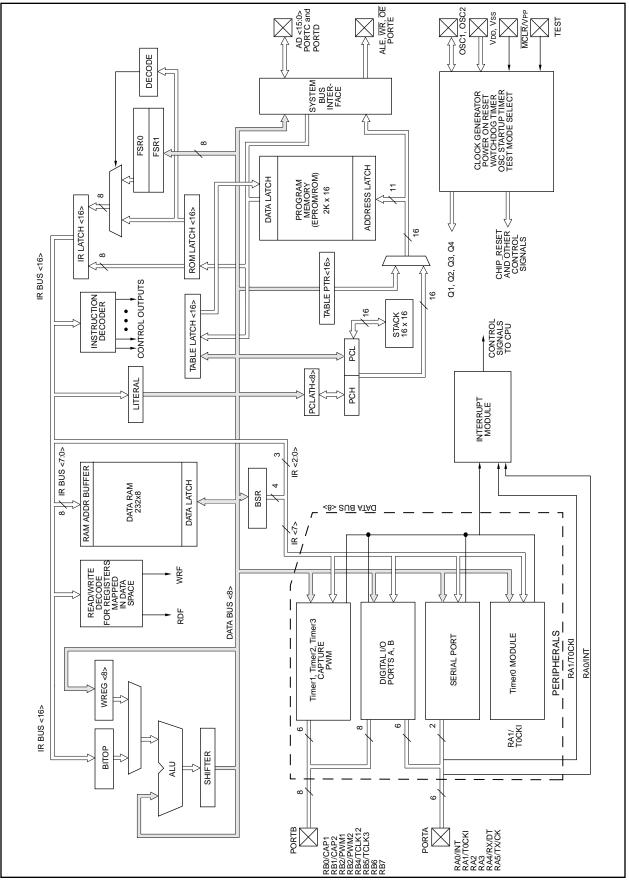

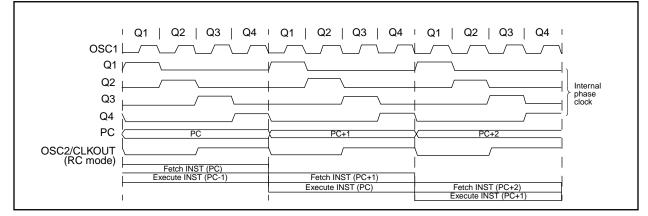

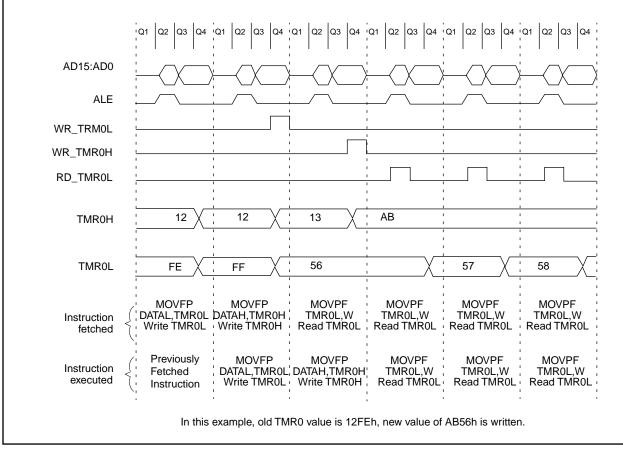

### 3.1 Clocking Scheme/Instruction Cycle

The clock input (from OSC1) is internally divided by four to generate four non-overlapping quadrature clocks, namely Q1, Q2, Q3, and Q4. Internally, the program counter (PC) is incremented every Q1, and the instruction is fetched from the program memory and latched into the instruction register in Q4. The instruction is decoded and executed during the following Q1 through Q4. The clocks and instruction execution flow are shown in Figure 3-3.

#### 3.2 Instruction Flow/Pipelining

An "Instruction Cycle" consists of four Q cycles (Q1, Q2, Q3, and Q4). The instruction fetch and execute are pipelined such that fetch takes one instruction cycle while decode and execute takes another instruction cycle. However, due to the pipelining, each instruction effectively executes in one cycle. If an instruction causes the program counter to change (e.g.GOTO) then two cycles are required to complete the instruction (Example 3-2).

A fetch cycle begins with the program counter incrementing in Q1.

In the execution cycle, the fetched instruction is latched into the "Instruction Register (IR)" in cycle Q1. This instruction is then decoded and executed during the Q2, Q3, and Q4 cycles. Data memory is read during Q2 (operand read) and written during Q4 (destination write).

### FIGURE 3-3: CLOCK/INSTRUCTION CYCLE

#### EXAMPLE 3-2: INSTRUCTION PIPELINE FLOW

All instructions are single cycle, except for any program branches. These take two cycles since the fetch instruction is "flushed" from the pipeline while the new instruction is being fetched and then executed.

## 5.1 Interrupt Status Register (INTSTA)

The Interrupt Status/Control register (INTSTA) records the individual interrupt requests in flag bits, and contains the individual interrupt enable bits (not for the peripherals).

The PEIF bit is a read only, bit wise OR of all the peripheral flag bits in the PIR register (Figure 5-4).

Note: T0IF, INTF, T0CKIF, or PEIF will be set by the specified condition, even if the corresponding interrupt enable bit is clear (interrupt disabled) or the GLINTD bit is set (all interrupts disabled).

Care should be taken when clearing any of the INTSTA register enable bits when interrupts are enabled (GLINTD is clear). If any of the INTSTA flag bits (T0IF, INTF, T0CKIF, or PEIF) are set in the same instruction cycle as the corresponding interrupt enable bit is cleared, the device will vector to the reset address (0x00).

When disabling any of the INTSTA enable bits, the GLINTD bit should be set (disabled).

## FIGURE 5-2: INTSTA REGISTER (ADDRESS: 07h, UNBANKED)

| bit $W = V$                                                                                                                                                                                                                                                                                                                | eadable bit<br>/ritable bit<br>/alue at POR reset |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| bit 7: <b>PEIF</b> : Peripheral Interrupt Flag bit<br>This bit is the OR of all peripheral interrupt flag bits AND'ed with their corres<br>1 = A peripheral interrupt is pending                                                                                                                                           | /alue at POR reset                                |

| bit 7: <b>PEIF</b> : Peripheral Interrupt Flag bit<br>This bit is the OR of all peripheral interrupt flag bits AND'ed with their corres<br>1 = A peripheral interrupt is pending                                                                                                                                           |                                                   |

|                                                                                                                                                                                                                                                                                                                            | ponding enable bits.                              |

| <ul> <li>bit 6: TOCKIF: External Interrupt on TOCKI Pin Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program exercised</li> <li>1 = The software specified edge occurred on the RA1/T0CKI pin</li> <li>0 = The software specified edge did not occur on the RA1/T0CKI pin</li> </ul> | cution to vector (18h).                           |

| bit 5: <b>T0IF</b> : TMR0 Overflow Interrupt Flag bit<br>This bit is cleared by hardware, when the interrupt logic forces program exer<br>1 = TMR0 overflowed<br>0 = TMR0 did not overflow                                                                                                                                 | cution to vector (10h).                           |

| <ul> <li>bit 4: INTF: External Interrupt on INT Pin Flag bit</li> <li>This bit is cleared by hardware, when the interrupt logic forces program exercise</li> <li>1 = The software specified edge occurred on the RA0/INT pin</li> <li>0 = The software specified edge did not occur on the RA0/INT pin</li> </ul>          | cution to vector (08h).                           |

| <ul> <li>bit 3: PEIE: Peripheral Interrupt Enable bit</li> <li>This bit enables all peripheral interrupts that have their corresponding enabl</li> <li>1 = Enable peripheral interrupts</li> <li>0 = Disable peripheral interrupts</li> </ul>                                                                              | e bits set.                                       |

| bit 2: <b>TOCKIE</b> : External Interrupt on TOCKI Pin Enable bit<br>1 = Enable software specified edge interrupt on the RA1/TOCKI pin<br>0 = Disable interrupt on the RA1/TOCKI pin                                                                                                                                       |                                                   |

| bit 1: <b>T0IE</b> : TMR0 Overflow Interrupt Enable bit<br>1 = Enable TMR0 overflow interrupt<br>0 = Disable TMR0 overflow interrupt                                                                                                                                                                                       |                                                   |

| bit 0: <b>INTE</b> : External Interrupt on RA0/INT Pin Enable bit<br>1 = Enable software specified edge interrupt on the RA0/INT pin<br>0 = Disable software specified edge interrupt on the RA0/INT pin                                                                                                                   |                                                   |

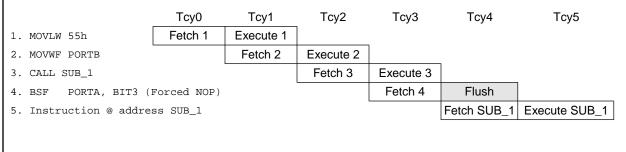

## 9.2 PORTB and DDRB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is DDRB. A '1' in DDRB configures the corresponding port pin as an input. A '0' in the DDRB register configures the corresponding port pin as an output. Reading PORTB reads the status of the pins, whereas writing to it will write to the port latch.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the  $\overline{\text{RBPU}}$  (PORTA<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are enabled on any reset.

PORTB also has an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB0 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB0) are compared with the value in the PORTB data latch. The "mismatch" outputs of RB7:RB0 are OR'ed together to generate the PORTB Interrupt Flag RBIF (PIR<7>). This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt by:

- a) Read-Write PORTB (such as; MOVPF PORTB, PORTB). This will end mismatch condition.

- b) Then, clear the RBIF bit.

A mismatch condition will continue to set the RBIF bit. Reading then writing PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on this port, allows easy interface to a key pad and make it possible for wake-up on key-depression. For an example, refer to AN552 in the *Embedded Control Handbook*.

The interrupt on change feature is recommended for wake-up on operations where PORTB is only used for the interrupt on change feature and key depression operation.

FIGURE 9-4: BLOCK DIAGRAM OF RB<7:4> AND RB<1:0> PORT PINS

Example 9-1 shows the instruction sequence to initialize PORTB. The Bank Select Register (BSR) must be selected to Bank 0 for the port to be initialized.

### EXAMPLE 9-1: INITIALIZING PORTB

| MOVLB | 0     | ; | Select Bank 0                |

|-------|-------|---|------------------------------|

| CLRF  | PORTB | ; | Initialize PORTB by clearing |

|       |       | ; | output data latches          |

| MOVLW | 0xCF  | ; | Value used to initialize     |

|       |       | ; | data direction               |

| MOVWF | DDRB  | ; | Set RB<3:0> as inputs        |

|       |       | ; | RB<5:4> as outputs           |

|       |       | ; | RB<7:6> as inputs            |

|       |       |   |                              |

| Name       | Bit  | Buffer Type | Function                                                                                                                                 |

|------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/CAP1   | bit0 | ST          | Input/Output or the RB0/CAP1 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB1/CAP2   | bit1 | ST          | Input/Output or the RB1/CAP2 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB2/PWM1   | bit2 | ST          | Input/Output or the RB2/PWM1 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB3/PWM2   | bit3 | ST          | Input/Output or the RB3/PWM2 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB4/TCLK12 | bit4 | ST          | Input/Output or the external clock input to Timer1 and Timer2. Software pro-<br>grammable weak pull-up and interrupt on change features. |

| RB5/TCLK3  | bit5 | ST          | Input/Output or the external clock input to Timer3. Software programmable weak pull-up and interrupt on change features.                 |

| RB6        | bit6 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

| RB7        | bit7 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

## TABLE 9-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger input.

## TABLE 9-4: REGISTERS/BITS ASSOCIATED WITH PORTB

| Address       | Name   | Bit 7      | Bit 6         | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|---------------|--------|-----------|-----------|--------|-----------|---------|-------------------------------|--------------------------------------------|

| 12h, Bank 0   | PORTB  | PORTB d    | ata latch     |        | xxxx xxxx | uuuu uuuu |        |           |         |                               |                                            |

| 11h, Bank 0   | DDRB   | Data dired | ction registe |        | 1111 1111 | 1111 1111 |        |           |         |                               |                                            |

| 10h, Bank 0   | PORTA  | RBPU       | _             | RA5    | RA4       | RA3       | RA2    | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                                  |

| 06h, Unbanked | CPUSTA | —          | _             | STKAV  | GLINTD    | TO        | PD     | _         | _       | 11 11                         | 11 qq                                      |

| 07h, Unbanked | INTSTA | PEIF       | <b>T0CKIF</b> | T0IF   | INTF      | PEIE      | T0CKIE | T0IE      | INTE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF        | TMR2IF | TMR1IF    | CA2IF     | CA1IF  | TXIF      | RCIF    | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE        | TMR2IE | TMR1IE    | CA2IE     | CA1IE  | TXIE      | RCIE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0        | CA1ED1 | CA1ED0    | T16       | TMR3CS | TMR2CS    | TMR1CS  | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF        | PWM2ON | PWM10N    | CA1/PR3   | TMR3ON | TMR2ON    | TMR10N  | 0000 0000                     | 0000 0000                                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = Value depends on condition.

Shaded cells are not used by PORTB.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

# 11.0 TIMER0

The Timer0 module consists of a 16-bit timer/counter, TMR0. The high byte is TMR0H and the low byte is TMR0L. A software programmable 8-bit prescaler makes an effective 24-bit overflow timer. The clock source is also software programmable as either the internal instruction clock or the RA1/T0CKI pin. The control bits for this module are in register T0STA (Figure 11-1).

| R/W - 0        | R/W - 0                                                              | R/W - 0                                          | R/W - 0                                                            | R/W - 0                    | R/W - 0                  | R/W - 0     | U - 0     |                                                                                                      |

|----------------|----------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------|----------------------------|--------------------------|-------------|-----------|------------------------------------------------------------------------------------------------------|

| INTEDG<br>bit7 | TOSE                                                                 | TOCS                                             | PS3                                                                | PS2                        | PS1                      | PS0         | —<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>Read as '0'<br>-n = Value at POR reset |

| bit 7:         | <b>INTEDG</b> : R<br>This bit sele<br>1 = Rising e<br>0 = Falling e  | ects the ed<br>edge of RA                        | ge upon w<br>0/INT pin g                                           | hich the in<br>generates i | terrupt is d<br>nterrupt | etected     |           | -n = value al POR lesel                                                                              |

| bit 6:         |                                                                      | ects the ed<br>S = 0<br>edge of RA<br>edge of RA | ge upon w<br>1/T0CKI pi                                            | hich TMR(                  | nts TMR0 a               | and/or gene |           | CKIF interrupt<br>CKIF interrupt                                                                     |

| bit 5:         | <b>TOCS</b> : Time<br>This bit sele<br>1 = Internal<br>0 = TOCKI     | ects the clo<br>instruction                      | ck source                                                          | for TMR0.                  |                          |             |           |                                                                                                      |

| bit 4-1:       | <b>PS3:PS0</b> : T<br>These bits                                     |                                                  |                                                                    |                            | R0.                      |             |           |                                                                                                      |

|                | PS3:PS0                                                              | Pre                                              | scale Valu                                                         | е                          |                          |             |           |                                                                                                      |

|                | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1xxx |                                                  | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |                            |                          |             |           |                                                                                                      |

| bit 0:         | Unimplem                                                             | <b>ented</b> : Rea                               | id as '0'                                                          |                            |                          |             |           |                                                                                                      |

### FIGURE 11-1: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

#### © 1996 Microchip Technology Inc.

| Address                                     | Name                             | Bit 7  | Bit 6  | Bit 5 | Bit 4  | Bit 3 | Bit 2         | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------------------------------------|----------------------------------|--------|--------|-------|--------|-------|---------------|-------|-------|-------------------------------|-----------------------------------------|

| 05h, Unbanked                               | TOSTA                            | INTEDG | T0SE   | TOCS  | PS3    | PS2   | PS1           | PS0   |       | 0000 000-                     | 0000 000-                               |

| 06h, Unbanked                               | CPUSTA                           | —      | _      | STKAV | GLINTD | TO    | PD            | _     | _     | 11 11                         | 11 qq                                   |

| 07h, Unbanked                               | INTSTA                           | PEIF   | TOCKIF | T0IF  | INTF   | PEIE  | <b>T0CKIE</b> | TOIE  | INTE  | 0000 0000                     | 0000 0000                               |

| 0Bh, Unbanked TMR0L TMR0 register; low byte |                                  |        |        |       |        |       |               |       |       | xxxx xxxx                     | uuuu uuuu                               |

| 0Ch, Unbanked                               | d TMR0H TMR0 register; high byte |        |        |       |        |       |               |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', g - value depends on condition, Shaded cells are not used by Timer0. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

# FIGURE 12-2: TCON2 REGISTER (ADDRESS: 17h, BANK 3)

| R - 0  | R - 0 R/W - 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | F CA10VF PWM20N PWM10N CA1/PR3 TMR30N TMR20N TMR10N R = Readable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| bit7   | bit0 W = Writable bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|        | -n = Value at POR reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| bit 7: | <ul> <li>CA2OVF: Capture2 Overflow Status bit</li> <li>This bit indicates that the capture value had not been read from the capture register pair (CA2H:CA2L)</li> <li>before the next capture event occurred. The capture register retains the oldest unread capture value (last capture before overflow). Subsequent capture events will not update the capture register with the Timer3 value until the capture register has been read (both bytes).</li> <li>1 = Overflow occurred on Capture2 register</li> <li>0 = No overflow occurred on Capture2 register</li> </ul> |

| bit 6: | <b>CA1OVF</b> : Capture1 Overflow Status bit<br>This bit indicates that the capture value had not been read from the capture register pair<br>(PR3H/CA2H:PR3L/CA2L) before the next capture event occurred. The capture register retains the old-<br>est unread capture value (last capture before overflow). Subsequent capture events will not update the<br>capture register with the TMR3 value until the capture register has been read (both bytes).<br>1 = Overflow occurred on Capture1 register<br>0 = No overflow occurred on Capture1 register                     |

| bit 5: | <b>PWM2ON</b> : PWM2 On bit<br>1 = PWM2 is enabled (The RB3/PWM2 pin ignores the state of the DDRB<3> bit)<br>0 = PWM2 is disabled (The RB3/PWM2 pin uses the state of the DDRB<3> bit for data direction)                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4: | <b>PWM1ON</b> : PWM1 On bit<br>1 = PWM1 is enabled (The RB2/PWM1 pin ignores the state of the DDRB<2> bit)<br>0 = PWM1 is disabled (The RB2/PWM1 pin uses the state of the DDRB<2> bit for data direction)                                                                                                                                                                                                                                                                                                                                                                    |

| bit 3: | <b>CA1/PR3</b> : CA1/PR3 Register Mode Select bit<br>1 = Enables Capture1 (PR3H/CA1H:PR3L/CA1L is the Capture1 register. Timer3 runs without<br>a period register)<br>0 = Enables the Period register (PR3H/CA1H:PR3L/CA1L is the Period register for Timer3)                                                                                                                                                                                                                                                                                                                 |

| bit 2: | TMR3ON: Timer3 On bit<br>1 = Starts Timer3<br>0 = Stops Timer3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| bit 1: | <b>TMR2ON</b> : Timer2 On bit<br>This bit controls the incrementing of the Timer2 register. When Timer2:Timer1 form the 16-bit timer (T16<br>is set), TMR2ON must be set. This allows the MSB of the timer to increment.<br>1 = Starts Timer2 (Must be enabled if the T16 bit (TCON1<3>) is set)<br>0 = Stops Timer2                                                                                                                                                                                                                                                          |

| bit 0: | TMR1ON: Timer1 On bit<br><u>When T16 is set (in 16-bit Timer Mode)</u><br>1 = Starts 16-bit Timer2:Timer1<br>0 = Stops 16-bit Timer2:Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|        | <u>When T16 is clear (in 8-bit Timer Mode)</u><br>1 = Starts 8-bit Timer1<br>0 = Stops 8-bit Timer1                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|        | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

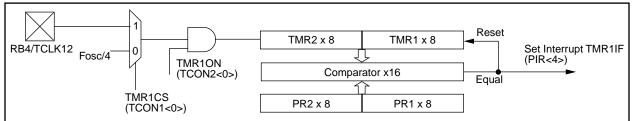

#### 12.1.2 TIMER1 & TIMER2 IN 16-BIT MODE

To select 16-bit mode, the T16 bit must be set. In this mode TMR1 and TMR2 are concatenated to form a 16-bit timer (TMR2:TMR1). The 16-bit timer increments until it matches the 16-bit period register (PR2:PR1). On the following timer clock, the timer value is reset to 0h, and the TMR1IF bit is set.

When selecting the clock source for the16-bit timer, the TMR1CS bit controls the entire 16-bit timer and TMR2CS is a "don't care." When TMR1CS is clear, the timer increments once every instruction cycle (Fosc/4). When TMR1CS is set, the timer increments on every falling edge of the RB4/TCLK12 pin. For the 16-bit timer to increment, both TMR1ON and TMR2ON bits must be set (Table 12-1).

#### 12.1.2.1 EXTERNAL CLOCK INPUT FOR TMR1:TMR2

When TMR1CS is set, the 16-bit TMR2:TMR1 increments on the falling edge of clock input TCLK12. The input on the RB4/TCLK12 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on RB4/TCLK12 to the time TMR2:TMR1 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

| TMR2ON | TMR10N | Result                         |

|--------|--------|--------------------------------|

| 1      | 1      | 16-bit timer<br>(TMR2:TMR1) ON |

| 0      | 1      | Only TMR1 increments           |

| x      | 0      | 16-bit timer OFF               |

#### FIGURE 12-4: TMR1 AND TMR2 IN 16-BIT TIMER/COUNTER MODE

#### TABLE 12-2: SUMMARY OF TIMER1 AND TIMER2 REGISTERS

| Address       | Name   | Bit 7      | Bit 6        | Bit 5  | Bit 4     | Bit 3     | Bit 2  | Bit 1  | Bit 0  | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|------------|--------------|--------|-----------|-----------|--------|--------|--------|-------------------------------|-----------------------------------------|

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0       | CA1ED1 | CA1ED0    | T16       | TMR3CS | TMR2CS | TMR1CS | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF       | PWM2ON | PWM1ON    | CA1/PR3   | TMR3ON | TMR2ON | TMR10N | 0000 0000                     | 0000 0000                               |

| 10h, Bank 2   | TMR1   | Timer1 reg | gister       |        |           |           |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 11h, Bank 2   | TMR2   | Timer2 reg | gister       |        | xxxx xxxx | uuuu uuuu |        |        |        |                               |                                         |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF       | TMR2IF | TMR1IF    | CA2IF     | CA1IF  | TXIF   | RCIF   | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE       | TMR2IE | TMR1IE    | CA2IE     | CA1IE  | TXIE   | RCIE   | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked | INTSTA | PEIF       | T0CKIF       | T0IF   | INTF      | PEIE      | T0CKIE | TOIE   | INTE   | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked | CPUSTA | _          | -            | STKAV  | GLINTD    | TO        | PD     | _      | _      | 11 11                         | 11 qq                                   |

| 14h, Bank 2   | PR1    | Timer1 pe  | riod registe | r      |           |           |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 2   | PR2    | Timer2 pe  | riod registe | r      |           |           |        |        |        | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 3   | PW1DCL | DC1        | DC0          | —      | _         | —         | —      | —      | —      | xx                            | uu                                      |

| 11h, Bank 3   | PW2DCL | DC1        | DC0          | TM2PW2 |           | —         | _      | _      | _      | xx0                           | uu0                                     |

| 12h, Bank 3   | PW1DCH | DC9        | DC8          | DC7    | DC6       | DC5       | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 3   | PW2DCH | DC9        | DC8          | DC7    | DC6       | DC5       | DC4    | DC3    | DC2    | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', q - value depends on condition,

shaded cells are not used by Timer1 or Timer2.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

| BAUD        | Fosc = 3 | 3 MHz  | SPBRG              | Fosc = 2 | 5 MHz  | SPBRG              | Fosc = 2 | 0 MHz  | SPBRG              | Fosc = 1 | 6 MHz  | SPBRG              |

|-------------|----------|--------|--------------------|----------|--------|--------------------|----------|--------|--------------------|----------|--------|--------------------|

| RATE<br>(K) | KBAUD    | %ERROR | value<br>(decimal) |

| 0.3         | NA       | _      | —                  | NA       | _      |                    | NA       | _      | _                  | NA       | _      | -                  |

| 1.2         | NA       | _      | _                  | NA       | _      | _                  | 1.221    | +1.73  | 255                | 1.202    | +0.16  | 207                |

| 2.4         | 2.398    | -0.07  | 214                | 2.396    | 0.14   | 162                | 2.404    | +0.16  | 129                | 2.404    | +0.16  | 103                |

| 9.6         | 9.548    | -0.54  | 53                 | 9.53     | -0.76  | 40                 | 9.469    | -1.36  | 32                 | 9.615    | +0.16  | 25                 |

| 19.2        | 19.09    | -0.54  | 26                 | 19.53    | +1.73  | 19                 | 19.53    | +1.73  | 15                 | 19.23    | +0.16  | 12                 |

| 76.8        | 73.66    | -4.09  | 6                  | 78.13    | +1.73  | 4                  | 78.13    | +1.73  | 3                  | 83.33    | +8.51  | 2                  |

| 96          | 103.12   | +7.42  | 4                  | 97.65    | +1.73  | 3                  | 104.2    | +8.51  | 2                  | NA       | _      | _                  |

| 300         | 257.81   | -14.06 | 1                  | 390.63   | +30.21 | 0                  | 312.5    | +4.17  | 0                  | NA       | _      | -                  |

| 500         | 515.62   | +3.13  | 0                  | NA       | _      | _                  | NA       | _      | _                  | NA       | _      | -                  |

| HIGH        | 515.62   | _      | 0                  | _        | _      | 0                  | 312.5    | _      | 0                  | 250      | _      | 0                  |

| LOW         | 2.014    | —      | 255                | 1.53     | —      | 255                | 1.221    | —      | 255                | 0.977    | _      | 255                |

# TABLE 13-4: BAUD RATES FOR ASYNCHRONOUS MODE

| BAUD<br>RATE | Fosc = 10 MH | Iz     | SPBRG<br>value     | Fosc = 7.159 | ) MHz  | SPBRG<br>value     | FOSC = 5.068 | 8 MHz  | SPBRG<br>value     |

|--------------|--------------|--------|--------------------|--------------|--------|--------------------|--------------|--------|--------------------|

| (K)          | KBAUD        | %ERROR | (decimal)          | KBAUD        | %ERROR | (decimal)          | KBAUD        | %ERROR | (decimal)          |

| 0.3          | NA           | _      | _                  | NA           | _      | _                  | 0.31         | +3.13  | 255                |

| 1.2          | 1.202        | +0.16  | 129                | 1.203        | _0.23  | 92                 | 1.2          | 0      | 65                 |

| 2.4          | 2.404        | +0.16  | 64                 | 2.380        | -0.83  | 46                 | 2.4          | 0      | 32                 |

| 9.6          | 9.766        | +1.73  | 15                 | 9.322        | -2.90  | 11                 | 9.9          | -3.13  | 7                  |

| 19.2         | 19.53        | +1.73  | 7                  | 18.64        | -2.90  | 5                  | 19.8         | +3.13  | 3                  |

| 76.8         | 78.13        | +1.73  | 1                  | NA           | _      | —                  | 79.2         | +3.13  | 0                  |

| 96           | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 300          | NA           | _      | —                  | NA           | _      | —                  | NA           | _      | _                  |

| 500          | NA           | _      | _                  | NA           | _      | _                  | NA           | _      | _                  |

| HIGH         | 156.3        | _      | 0                  | 111.9        | _      | 0                  | 79.2         | _      | 0                  |

| LOW          | 0.610        | —      | 255                | 0.437        | —      | 255                | 0.309        | _      | 2 <b>55</b>        |

| BAUD         | Fosc = 3.579 | MHz    | SPBRG              | Fosc = 1 MH  | z      | SPBRG              | FOSC = 32.76 | 8 kHz  | SPBRG              |

| RATE<br>(K)  | KBAUD        | %ERROR | value<br>(decimal) | KBAUD        | %ERROR | value<br>(decimal) | KBAUD        | %ERROR | value<br>(decimal) |

| 0.3          | 0.301        | +0.23  | 185                | 0.300        | +0.16  | 51                 | 0.256        | -14.67 | 1                  |

| 1.2          | 1.190        | -0.83  | 46                 | 1.202        | +0.16  | 12                 | NA           | —      | —                  |

| 2.4          | 2.432        | +1.32  | 22                 | 2.232        | -6.99  | 6                  | NA           | —      | —                  |

| 9.6          | 9.322        | -2.90  | 5                  | NA           | _      | _                  | NA           | _      | _                  |

| 19.2         | 18.64        | -2.90  | 2                  | NA           | —      | —                  | NA           | —      | —                  |

| 76.8         | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 96           | NA           | _      | _                  | NA           | _      | _                  | NA           | _      | _                  |

| 300          | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| 500          | NA           | —      | —                  | NA           | —      | —                  | NA           | —      | —                  |

| HIGH         | 55.93        | _      | 0                  | 15.63        | _      | 0                  | 0.512        | _      | 0                  |

| l mon        |              |        |                    |              |        |                    |              |        |                    |

### 13.2 USART Asynchronous Mode

In this mode, the USART uses standard nonreturn-to-zero (NRZ) format (one start bit, eight or nine data bits, and one stop bit). The most common data format is 8-bits. An on-chip dedicated 8-bit baud rate generator can be used to derive standard baud rate frequencies from the oscillator. The USART's transmitter and receiver are functionally independent but use the same data format and baud rate. The baud rate generator produces a clock x64 of the bit shift rate. Parity is not supported by the hardware, but can be implemented in software (and stored as the ninth data bit). Asynchronous mode is stopped during SLEEP.

The asynchronous mode is selected by clearing the SYNC bit (TXSTA<4>).

The USART Asynchronous module consists of the following important elements:

- Baud Rate Generator

- Sampling Circuit

- Asynchronous Transmitter

- Asynchronous Receiver

#### 13.2.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown in Figure 13-3. The heart of the transmitter is the transmit shift register (TSR). The shift register obtains its data from the read/write transmit buffer (TXREG). TXREG is loaded with data in software. The TSR is not loaded until the stop bit has been transmitted from the previous load. As soon as the stop bit is transmitted, the TSR is loaded with new data from the TXREG (if available). Once TXREG transfers the data to the TSR (occurs in one TCY at the end of the current BRG cycle), the TXREG is empty and an interrupt bit, TXIF (PIR<1>) is set. This interrupt can be enabled or disabled by the TXIE bit (PIE<1>). TXIF will be set regardless of TXIE and cannot be reset in software. It will reset only when new data is loaded into TXREG. While TXIF indicates the status of the TXREG, the TRMT (TXSTA<1>) bit shows the status of the TSR. TRMT is a read only bit which is set when the TSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the TSR is empty.

| Note: | The TSR is not mapped in data memory, |

|-------|---------------------------------------|

|       | so it is not available to the user.   |

Transmission enabled setting is by the TXEN (TXSTA<5>) bit. The actual transmission will not occur until TXREG has been loaded with data and the baud rate generator (BRG) has produced a shift clock (Figure 13-5). The transmission can also be started by first loading TXREG and then setting TXEN. Normally when transmission is first started, the TSR is empty, so a transfer to TXREG will result in an immediate transfer to TSR resulting in an empty TXREG. A back-to-back transfer is thus possible (Figure 13-6). Clearing TXEN during a transmission will cause the transmission to be aborted. This will reset the transmitter and the RA5/TX/CK pin will revert to hi-impedance.

In order to select 9-bit transmission, the TX9 (TXSTA<6>) bit should be set and the ninth bit should be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit data to the TXREG. This is because a data write to TXREG can result in an immediate transfer of the data to the TSR (if the TSR is empty).

Steps to follow when setting up an Asynchronous Transmission:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the TXIE bit.

- 4. If 9-bit transmission is desired, then set the TX9 bit.

- 5. Load data to the TXREG register.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in TX9D.

- 7. Enable the transmission by setting TXEN (starts transmission).

Writing the transmit data to the TXREG, then enabling the transmit (setting TXEN) allows transmission to start sooner then doing these two events in the opposite order.

Note: To terminate a transmission, either clear the SPEN bit, or the TXEN bit. This will reset the transmit logic, so that it will be in the proper state when transmit is re-enabled.

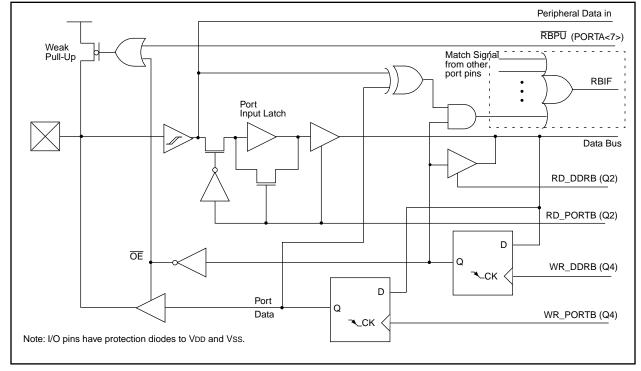

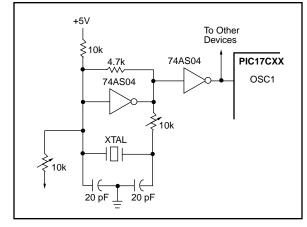

#### 14.2.4 EXTERNAL CRYSTAL OSCILLATOR CIRCUIT

Either a prepackaged oscillator can be used or a simple oscillator circuit with TTL gates can be built. Prepackaged oscillators provide a wide operating range and better stability. A well-designed crystal oscillator will provide good performance with TTL gates. Two types of crystal oscillator circuits can be used: one with series resonance, or one with parallel resonance.

Figure 14-5 shows implementation of a parallel resonant oscillator circuit. The circuit is designed to use the fundamental frequency of the crystal. The 74AS04 inverter performs the 180-degree phase shift that a parallel oscillator requires. The 4.7 k $\Omega$  resistor provides the negative feedback for stability. The 10 k $\Omega$  potentiometer biases the 74AS04 in the linear region. This could be used for external oscillator designs.

#### FIGURE 14-5: EXTERNAL PARALLEL RESONANT CRYSTAL OSCILLATOR CIRCUIT

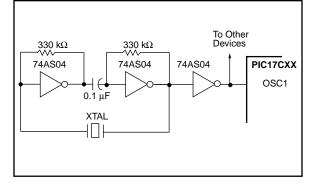

Figure 14-6 shows a series resonant oscillator circuit. This circuit is also designed to use the fundamental frequency of the crystal. The inverter performs a 180-degree phase shift in a series resonant oscillator circuit. The 330 k $\Omega$  resistors provide the negative feedback to bias the inverters in their linear region.

#### FIGURE 14-6: EXTERNAL SERIES RESONANT CRYSTAL OSCILLATOR CIRCUIT

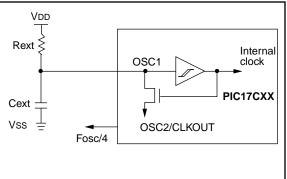

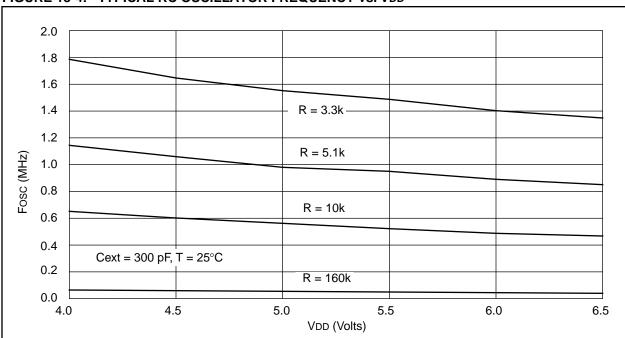

#### 14.2.5 RC OSCILLATOR

For timing insensitive applications, the RC device option offers additional cost savings. RC oscillator frequency is a function of the supply voltage, the resistor (Rext) and capacitor (Cext) values, and the operating temperature. In addition to this, oscillator frequency will vary from unit to unit due to normal process parameter variation. Furthermore, the difference in lead frame capacitance between package types will also affect oscillation frequency, especially for low Cext values. The user also needs to take into account variation due to tolerance of external R and C components used. Figure 14-6 shows how the R/C combination is connected to the PIC17CXX. For Rext values below 2.2 kQ, the oscillator operation may become unstable, or stop completely. For very high Rext values (e.g. 1 M $\Omega$ ), the oscillator becomes sensitive to noise, humidity and leakage. Thus, we recommend to keep Rext between 3  $k\Omega$  and 100  $k\Omega$ .

Although the oscillator will operate with no external capacitor (Cext = 0 pF), we recommend using values above 20 pF for noise and stability reasons. With little or no external capacitance, oscillation frequency can vary dramatically due to changes in external capacitances, such as PCB trace capacitance or package lead frame capacitance.

See Section 18.0 for RC frequency variation from part to part due to normal process variation. The variation is larger for larger R (since leakage current variation will affect RC frequency more for large R) and for smaller C (since variation of input capacitance will affect RC frequency more).

See Section 18.0 for variation of oscillator frequency due to VDD for given Rext/Cext values as well as frequency variation due to operating temperature for given R, C, and VDD values.

The oscillator frequency, divided by 4, is available on the OSC2/CLKOUT pin, and can be used for test purposes or to synchronize other logic (see Figure 3-2 for waveform).

#### FIGURE 14-7: RC OSCILLATOR MODE

| CALL                                | Subroutir                                                  | ne Call                                                                                            |                                                                              | CLF                                | RF                                       | Clear f                                                                       |                                                      |          |                       |

|-------------------------------------|------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------|------------------------------------------|-------------------------------------------------------------------------------|------------------------------------------------------|----------|-----------------------|

| Syntax:                             | [label] (                                                  | CALL k                                                                                             |                                                                              | Syn                                | tax:                                     | [ <i>label</i> ] CL                                                           | RF f,s                                               |          |                       |

| Operands:                           | $0 \le k \le 40$                                           | 95                                                                                                 |                                                                              | Ope                                | erands:                                  | $0 \le f \le 25$                                                              | 5                                                    |          |                       |

| Operation:                          | k<12:8> –                                                  |                                                                                                    |                                                                              | $k<12:8> \rightarrow PCLATH<4:0>;$ |                                          |                                                                               | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |          |                       |

| Status Affecte                      |                                                            |                                                                                                    |                                                                              | Stat                               | None                                     |                                                                               |                                                      |          |                       |

|                                     |                                                            |                                                                                                    |                                                                              | ר Enc                              | oding:                                   | 0010                                                                          | 100s                                                 | ffff     | ffff                  |

| Encoding:<br>Description:           | return addr<br>the stack. T<br>PC bits<12<br>bits of the F | kkkk kkl<br>call within 8K<br>ess (PC+1) is<br>he 13-bit value<br>:0>. Then the p<br>PC are copied | page. First,<br>pushed onto<br>is loaded into<br>upper-eight<br>into PCLATH. |                                    | scription:                               | Clears the<br>ister(s).<br>s = 0: Data<br>WREG are<br>s = 1: Data<br>cleared. | memory<br>cleared.                                   | location |                       |

|                                     |                                                            | wo-cycle instru                                                                                    |                                                                              | Woi                                | rds:                                     | 1                                                                             |                                                      |          |                       |

|                                     | See LCALL<br>space.                                        | for calls outsid                                                                                   | le 8K memory                                                                 | Сус                                | les:                                     | 1                                                                             |                                                      |          |                       |

| Words:                              | 1                                                          |                                                                                                    |                                                                              | QC                                 | cycle Activity:                          |                                                                               |                                                      |          |                       |

| Cycles:                             | 2                                                          |                                                                                                    |                                                                              |                                    | Q1                                       | Q2                                                                            | Q                                                    |          | Q4                    |

| Q Cycle Activ                       | ity:                                                       |                                                                                                    |                                                                              |                                    | Decode                                   | Read<br>register 'f'                                                          | Exec                                                 |          | Write<br>register 'f' |

| Q1                                  | Q2                                                         | Q3                                                                                                 | Q4                                                                           |                                    |                                          |                                                                               |                                                      |          | and other             |

| Decode                              | e Read literal<br>'k'<7:0>                                 | Execute                                                                                            | NOP                                                                          |                                    |                                          |                                                                               |                                                      |          | specified<br>register |

| Forced N                            | OP NOP                                                     | Execute                                                                                            | NOP                                                                          | <u>Exa</u>                         | mple:                                    | CLRF                                                                          | FLAC                                                 | G_REG    |                       |

| <u>Example</u> :<br>Before In<br>PC |                                                            | CALL THE                                                                                           | RE                                                                           |                                    | Before Instru<br>FLAG_R<br>After Instruc | EG = 0                                                                        | κ5Α                                                  |          |                       |

| After Inst<br>PC                    |                                                            | ERE)                                                                                               |                                                                              |                                    | FLAG_R                                   | EG = 0>                                                                       | (00                                                  |          |                       |

PC = Address(THERE) TOS = Address(HERE + 1)

| CPFS                                                                                                                                                                                                                                                                                                     | -SLT Compare f with WREG,<br>skip if f < WREG  |                              |                                                |         |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------|------------------------------------------------|---------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                                                                    | ax:                                            | [ <i>label</i> ] CPFSLT f    |                                                |         |  |  |  |  |

| Opera                                                                                                                                                                                                                                                                                                    |                                                |                              |                                                |         |  |  |  |  |

| Opera                                                                                                                                                                                                                                                                                                    | ation:                                         | G),<br>(WREG)<br>comparison) |                                                |         |  |  |  |  |

| Statu                                                                                                                                                                                                                                                                                                    | s Affected:                                    | None                         |                                                |         |  |  |  |  |

| Enco                                                                                                                                                                                                                                                                                                     | ding:                                          | 0011                         | 0000 ffi                                       | ff ffff |  |  |  |  |

| Description:<br>Compares the contents of data mem<br>location 'f' to the contents of WREG<br>performing an unsigned subtraction.<br>If the contents of 'f' < the contents of<br>WREG, then the fetched instruction<br>discarded and an NOP is executed<br>instead making this a two-cycle instr<br>tion. |                                                |                              |                                                |         |  |  |  |  |

| Word                                                                                                                                                                                                                                                                                                     | s:                                             | 1                            |                                                |         |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                                                                    | es:                                            | 1 (2)                        | 1 (2)                                          |         |  |  |  |  |

| Q Cy                                                                                                                                                                                                                                                                                                     | cle Activity:                                  |                              |                                                |         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                          | Q1                                             | Q2                           | Q3                                             | Q4      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                          | Decode                                         | Read<br>register 'f'         | Execute                                        | NOP     |  |  |  |  |

| lf skip                                                                                                                                                                                                                                                                                                  | o:                                             |                              |                                                |         |  |  |  |  |

| -                                                                                                                                                                                                                                                                                                        | Q1                                             | Q2                           | Q3                                             | Q4      |  |  |  |  |

|                                                                                                                                                                                                                                                                                                          | Forced NOP                                     | NOP                          | Execute                                        | NOP     |  |  |  |  |

| <u>Exarr</u>                                                                                                                                                                                                                                                                                             | nple:                                          | HERE<br>NLESS<br>LESS        | CPFSLT REG<br>:<br>:                           |         |  |  |  |  |

| E                                                                                                                                                                                                                                                                                                        | Before Instru<br>PC<br>W                       |                              | ddress (HERE)                                  |         |  |  |  |  |

| ŀ                                                                                                                                                                                                                                                                                                        | After Instruct<br>If REG<br>PC<br>If REG<br>PC | < W<br>= Ac<br>≥ W           | REG;<br>ddress (LESS)<br>REG;<br>ddress (NLESS |         |  |  |  |  |

| DAW                 |                                                | Decimal                                                      | Adjust WRE                                                                                                                                                                                                        | G Register                                         |  |  |  |

|---------------------|------------------------------------------------|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| Syntax              | K:                                             | [ <i>label</i> ] D                                           | AW f,s                                                                                                                                                                                                            |                                                    |  |  |  |

| Opera               | nds:                                           | $0 \le f \le 25$<br>s $\in [0,1]$                            | 5                                                                                                                                                                                                                 |                                                    |  |  |  |

| Opera               | tion:                                          | <sup>-</sup> WREG<br>else                                    | If [WREG<3:0> >9] .OR. [DC = 1] then<br>WREG<3:0> + 6 $\rightarrow$ f<3:0>, s<3:0>;<br>else<br>WREG<3:0> $\rightarrow$ f<3:0>, s<3:0>;                                                                            |                                                    |  |  |  |

|                     |                                                | WREG                                                         |                                                                                                                                                                                                                   | f<7:4>, s<7:4>                                     |  |  |  |

| Status              | Affected:                                      | C                                                            | $<7:4> \rightarrow f<7:$                                                                                                                                                                                          | 4>, S<7:4>                                         |  |  |  |

| Encod               |                                                | 0010                                                         | 111s ff                                                                                                                                                                                                           | ff ffff                                            |  |  |  |

| Descri              | U                                              |                                                              | ts the eight bi                                                                                                                                                                                                   |                                                    |  |  |  |

|                     |                                                | tion of two<br>BCD forma<br>packed BC<br>s = 0: Ro<br>m<br>W | WREG resulting from the earlier addi-<br>tion of two variables (each in packed<br>BCD format) and produces a correct<br>packed BCD result.<br>s = 0: Result is placed in Data<br>memory location 'f' and<br>WREG. |                                                    |  |  |  |

|                     |                                                |                                                              | esult is placed<br>emory locatio                                                                                                                                                                                  |                                                    |  |  |  |

| Words               | :                                              | 1                                                            |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Cycles              | 8:                                             | 1                                                            |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Q Cyc               | le Activity:                                   |                                                              |                                                                                                                                                                                                                   | •                                                  |  |  |  |

|                     | Q1<br>Decode                                   | Q2<br>Read                                                   | Q3<br>Execute                                                                                                                                                                                                     | Q4<br>Write                                        |  |  |  |

|                     | Decode                                         | register 'f'                                                 | Execute                                                                                                                                                                                                           | register 'f'<br>and other<br>specified<br>register |  |  |  |

| Exam                | ole1:                                          | DAW RE                                                       | G1, 0                                                                                                                                                                                                             |                                                    |  |  |  |

| B                   | <br>efore Instru                               | iction                                                       |                                                                                                                                                                                                                   |                                                    |  |  |  |

|                     | WREG<br>REG1<br>C<br>DC                        | = 0xA5<br>= ??<br>= 0<br>= 0                                 |                                                                                                                                                                                                                   |                                                    |  |  |  |

| Ai<br><u>Exam</u> t | fter Instruct<br>WREG<br>REG1<br>C<br>DC<br>DC | ion<br>= 0x05<br>= 0x05<br>= 1<br>= 0                        |                                                                                                                                                                                                                   |                                                    |  |  |  |

| В                   | efore Instru                                   |                                                              |                                                                                                                                                                                                                   |                                                    |  |  |  |

|                     | WREG<br>REG1<br>C                              | = 0xCE<br>= ??<br>= 0                                        |                                                                                                                                                                                                                   |                                                    |  |  |  |

| U             | -    | 0    |

|---------------|------|------|

| DC            | =    | 0    |

| After Instruc | tion |      |

| WREG          | =    | 0x24 |

| REG1          | =    | 0x24 |

| С             | =    | 1    |