Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 8MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 4KB (2K × 16)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 232 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc42a-08-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Overview                                                               | 5   |

|-------|------------------------------------------------------------------------|-----|

| 2.0   | PIC17C4X Device Varieties                                              | 7   |

| 3.0   | Architectural Overview                                                 | 9   |

| 4.0   | Reset                                                                  | 15  |

| 5.0   | Interrupts                                                             | 21  |

| 6.0   | Memory Organization                                                    | 29  |

| 7.0   | Table Reads and Table Writes                                           | 43  |

| 8.0   | Hardware Multiplier                                                    | 49  |

| 9.0   | I/O Ports                                                              | 53  |

| 10.0  | Overview of Timer Resources                                            |     |

| 11.0  | Timer0                                                                 |     |

| 12.0  | Timer1, Timer2, Timer3, PWMs and Captures                              |     |

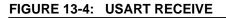

| 13.0  | Universal Synchronous Asynchronous Receiver Transmitter (USART) Module | 83  |

| 14.0  | Special Features of the CPU                                            | 99  |

| 15.0  | Instruction Set Summary                                                | 107 |

| 16.0  | Development Support                                                    | 143 |

| 17.0  | PIC17C42 Electrical Characteristics                                    |     |

| 18.0  | PIC17C42 DC and AC Characteristics                                     |     |

| 19.0  | PIC17CR42/42A/43/R43/44 Electrical Characteristics                     | 175 |

| 20.0  | PIC17CR42/42A/43/R43/44 DC and AC Characteristics                      |     |

| 21.0  | Packaging Information                                                  | 205 |

|       | dix A: Modifications                                                   |     |

|       | dix B: Compatibility                                                   |     |

| Appen | dix C: What's New                                                      | 212 |

| Appen | dix D: What's Changed                                                  | 212 |

|       | dix E: PIC16/17 Microcontrollers                                       |     |

|       | dix F: Errata for PIC17C42 Silicon                                     |     |

|       |                                                                        |     |

| PIC17 | C4X Product Identification System                                      | 237 |

For register and module descriptions in this data sheet, device legends show which devices apply to those sections. For example, the legend below shows that some features of only the PIC17C43, PIC17C43, PIC17C44 are described in this section.

#### Applicable Devices 42 R42 42A 43 R43 44

# To Our Valued Customers

We constantly strive to improve the quality of all our products and documentation. We have spent an exceptional amount of time to ensure that these documents are correct. However, we realize that we may have missed a few things. If you find any information that is missing or appears in error from the previous version of the PIC17C4X Data Sheet (Literature Number DS30412B), please use the reader response form in the back of this data sheet to inform us. We appreciate your assistance in making this a better document.

To assist you in the use of this document, Appendix C contains a list of new information in this data sheet, while Appendix D contains information that has changed

# 2.0 PIC17C4X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC17C4X Product Selection System section at the end of this data sheet. When placing orders, please use the "PIC17C4X Product Identification System" at the back of this data sheet to specify the correct part number.

For the PIC17C4X family of devices, there are four device "types" as indicated in the device number:

- C, as in PIC17C42. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC17LC42. These devices have EPROM type memory, operate over an extended voltage range, and reduced frequency range.

- 3. **CR**, as in PIC17**CR**42. These devices have ROM type memory and operate over the standard voltage range.

- 4. LCR, as in PIC17LCR42. These devices have ROM type memory, operate over an extended voltage range, and reduced frequency range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Microchip's PRO MATE<sup>TM</sup> programmer supports programming of the PIC17C4X. Third party programmers also are available; refer to the *Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers expecting frequent code changes and updates.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

ROM devices do not allow serialization information in the program memory space.

For information on submitting ROM code, please contact your regional sales office.

#### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

For information on submitting ROM code, please contact your regional sales office.

| TABLE 3-1. |            |                      |                 |               |                |                                                                                                                                                                             |

|------------|------------|----------------------|-----------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name       | DIP<br>No. | PLCC<br>No.          | QFP<br>No.      | I/O/P<br>Type | Buffer<br>Type | Description                                                                                                                                                                 |

|            |            |                      |                 |               |                | PORTD is a bi-directional I/O Port.                                                                                                                                         |

| RD0/AD8    | 40         | 43                   | 15              | I/O           | TTL            | This is also the upper byte of the 16-bit system bus in                                                                                                                     |

| RD1/AD9    | 39         | 42                   | 14              | I/O           | TTL            | microprocessor mode or extended microprocessor mode                                                                                                                         |

| RD2/AD10   | 38         | 41                   | 13              | I/O           | TTL            | or extended microcontroller mode. In multiplexed system                                                                                                                     |

| RD3/AD11   | 37         | 40                   | 12              | I/O           | TTL            | bus configuration these pins are address output as well as data input or output.                                                                                            |

| RD4/AD12   | 36         | 39                   | 11              | I/O           | TTL            |                                                                                                                                                                             |

| RD5/AD13   | 35         | 38                   | 10              | I/O           | TTL            |                                                                                                                                                                             |

| RD6/AD14   | 34         | 37                   | 9               | I/O           | TTL            |                                                                                                                                                                             |

| RD7/AD15   | 33         | 36                   | 8               | I/O           | TTL            |                                                                                                                                                                             |

|            |            |                      |                 |               |                | PORTE is a bi-directional I/O Port.                                                                                                                                         |

| RE0/ALE    | 30         | 32                   | 4               | I/O           | TTL            | In microprocessor mode or extended microcontroller<br>mode, it is the Address Latch Enable (ALE) output.<br>Address should be latched on the falling edge of ALE<br>output. |

| RE1/OE     | 29         | 31                   | 3               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Output Enable ( $\overline{OE}$ ) control output (active low).                                                |

| RE2/WR     | 28         | 30                   | 2               | I/O           | TTL            | In microprocessor or extended microcontroller mode, it is the Write Enable (WR) control output (active low).                                                                |

| TEST       | 27         | 29                   | 1               | I             | ST             | Test mode selection control input. Always tie to Vss for nor-<br>mal operation.                                                                                             |

| Vss        | 10,<br>31  | 11,<br>12,<br>33, 34 | 5, 6,<br>27, 28 | Р             |                | Ground reference for logic and I/O pins.                                                                                                                                    |

| Vdd        | 1          | 1, 44                | 16, 17          | Р             |                | Positive supply for logic and I/O pins.                                                                                                                                     |

| TABLE 3-1: | PINOUT DESCRIPTIONS |

|------------|---------------------|

|------------|---------------------|

Legend: I = Input only; O = Output only; I/O = Input/Output; P = Power; — = Not Used; TTL = TTL input; ST = Schmitt Trigger input.

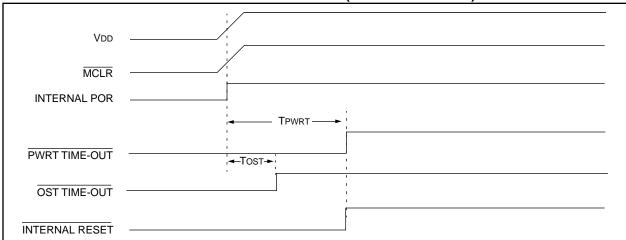

FIGURE 4-2: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

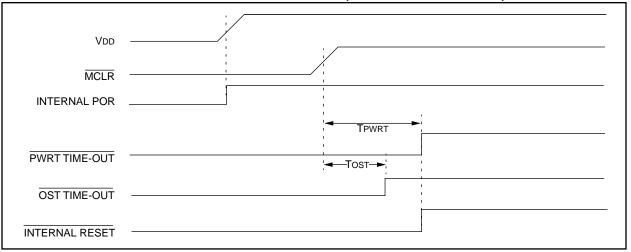

#### FIGURE 4-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD)

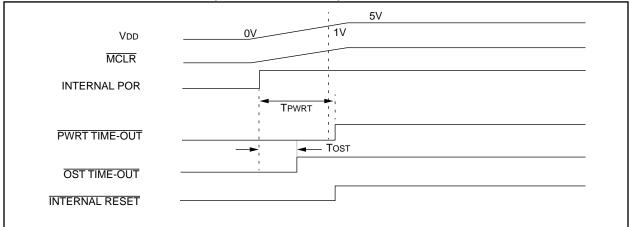

### FIGURE 4-4: SLOW RISE TIME (MCLR TIED TO VDD)

Example 9-1 shows the instruction sequence to initialize PORTB. The Bank Select Register (BSR) must be selected to Bank 0 for the port to be initialized.

#### EXAMPLE 9-1: INITIALIZING PORTB

| MOVLB | 0     | ; | Select Bank 0                |

|-------|-------|---|------------------------------|

| CLRF  | PORTB | ; | Initialize PORTB by clearing |

|       |       | ; | output data latches          |

| MOVLW | 0xCF  | ; | Value used to initialize     |

|       |       | ; | data direction               |

| MOVWF | DDRB  | ; | Set RB<3:0> as inputs        |

|       |       | ; | RB<5:4> as outputs           |

|       |       | ; | RB<7:6> as inputs            |

|       |       |   |                              |

| Name       | Bit  | Buffer Type | Function                                                                                                                                 |

|------------|------|-------------|------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/CAP1   | bit0 | ST          | Input/Output or the RB0/CAP1 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB1/CAP2   | bit1 | ST          | Input/Output or the RB1/CAP2 input pin. Software programmable weak pull-<br>up and interrupt on change features.                         |

| RB2/PWM1   | bit2 | ST          | Input/Output or the RB2/PWM1 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB3/PWM2   | bit3 | ST          | Input/Output or the RB3/PWM2 output pin. Software programmable weak pull-up and interrupt on change features.                            |

| RB4/TCLK12 | bit4 | ST          | Input/Output or the external clock input to Timer1 and Timer2. Software pro-<br>grammable weak pull-up and interrupt on change features. |

| RB5/TCLK3  | bit5 | ST          | Input/Output or the external clock input to Timer3. Software programmable weak pull-up and interrupt on change features.                 |

| RB6        | bit6 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

| RB7        | bit7 | ST          | Input/Output pin. Software programmable weak pull-up and interrupt on change features.                                                   |

# TABLE 9-3: PORTB FUNCTIONS

Legend: ST = Schmitt Trigger input.

#### TABLE 9-4: REGISTERS/BITS ASSOCIATED WITH PORTB

| Address       | Name   | Bit 7      | Bit 6         | Bit 5        | Bit 4  | Bit 3   | Bit 2  | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets<br>(Note1) |

|---------------|--------|------------|---------------|--------------|--------|---------|--------|-----------|---------|-------------------------------|--------------------------------------------|

| 12h, Bank 0   | PORTB  | PORTB d    | ata latch     |              |        |         |        |           |         | xxxx xxxx                     | uuuu uuuu                                  |

| 11h, Bank 0   | DDRB   | Data dired | ction registe | er for PORTE | 5      |         |        |           |         | 1111 1111                     | 1111 1111                                  |

| 10h, Bank 0   | PORTA  | RBPU       | _             | RA5          | RA4    | RA3     | RA2    | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                                  |

| 06h, Unbanked | CPUSTA | —          | _             | STKAV        | GLINTD | TO      | PD     | _         | _       | 11 11                         | 11 qq                                      |

| 07h, Unbanked | INTSTA | PEIF       | <b>T0CKIF</b> | T0IF         | INTF   | PEIE    | T0CKIE | T0IE      | INTE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 1   | PIR    | RBIF       | TMR3IF        | TMR2IF       | TMR1IF | CA2IF   | CA1IF  | TXIF      | RCIF    | 0000 0010                     | 0000 0010                                  |

| 17h, Bank 1   | PIE    | RBIE       | TMR3IE        | TMR2IE       | TMR1IE | CA2IE   | CA1IE  | TXIE      | RCIE    | 0000 0000                     | 0000 0000                                  |

| 16h, Bank 3   | TCON1  | CA2ED1     | CA2ED0        | CA1ED1       | CA1ED0 | T16     | TMR3CS | TMR2CS    | TMR1CS  | 0000 0000                     | 0000 0000                                  |

| 17h, Bank 3   | TCON2  | CA2OVF     | CA10VF        | PWM2ON       | PWM10N | CA1/PR3 | TMR3ON | TMR2ON    | TMR10N  | 0000 0000                     | 0000 0000                                  |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = Value depends on condition.

Shaded cells are not used by PORTB.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

# TABLE 9-5: PORTC FUNCTIONS

| Name    | Bit  | Buffer Type | Function                                     |

|---------|------|-------------|----------------------------------------------|

| RC0/AD0 | bit0 | TTL         | Input/Output or system bus address/data pin. |

| RC1/AD1 | bit1 | TTL         | Input/Output or system bus address/data pin. |

| RC2/AD2 | bit2 | TTL         | Input/Output or system bus address/data pin. |

| RC3/AD3 | bit3 | TTL         | Input/Output or system bus address/data pin. |

| RC4/AD4 | bit4 | TTL         | Input/Output or system bus address/data pin. |

| RC5/AD5 | bit5 | TTL         | Input/Output or system bus address/data pin. |

| RC6/AD6 | bit6 | TTL         | Input/Output or system bus address/data pin. |

| RC7/AD7 | bit7 | TTL         | Input/Output or system bus address/data pin. |

Legend: TTL = TTL input.

# TABLE 9-6: REGISTERS/BITS ASSOCIATED WITH PORTC

| Address     | Name                                               | Bit 7       | Bit 6       | Bit 5       | Bit 4       | Bit 3       | Bit 2       | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|----------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------------------------|-----------------------------------------|

| 11h, Bank 1 | PORTC                                              | RC7/<br>AD7 | RC6/<br>AD6 | RC5/<br>AD5 | RC4/<br>AD4 | RC3/<br>AD3 | RC2/<br>AD2 | RC1/<br>AD1 | RC0/<br>AD0 | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 1 | 10h, Bank 1 DDRC Data direction register for PORTC |             |             |             |             |             |             |             | 1111 1111   | 1111 1111                     |                                         |

Legend: x = unknown, u = unchanged.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

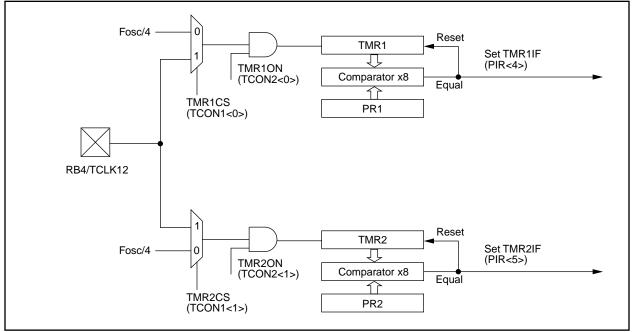

#### 12.1 <u>Timer1 and Timer2</u>

#### 12.1.1 TIMER1, TIMER2 IN 8-BIT MODE

Both Timer1 and Timer2 will operate in 8-bit mode when the T16 bit is clear. These two timers can be independently configured to increment from the internal instruction cycle clock or from an external clock source on the RB4/TCLK12 pin. The timer clock source is configured by the TMRxCS bit (x = 1 for Timer1 or = 2 for Timer2). When TMRxCS is clear, the clock source is internal and increments once every instruction cycle (Fosc/4). When TMRxCS is set, the clock source is the RB4/TCLK12 pin, and the timer will increment on every falling edge of the RB4/TCLK12 pin.

The timer increments from 00h until it equals the Period register (PRx). It then resets to 00h at the next increment cycle. The timer interrupt flag is set when the timer is reset. TMR1 and TMR2 have individual interrupt flag bits. The TMR1 interrupt flag bit is latched into TMR1IF, and the TMR2 interrupt flag bit is latched into TMR2IF.

Each timer also has a corresponding interrupt enable bit (TMRxIE). The timer interrupt can be enabled by setting this bit and disabled by clearing this bit. For peripheral interrupts to be enabled, the Peripheral Interrupt Enable bit must be enabled (PEIE is set) and global interrupts must be enabled (GLINTD is cleared).

The timers can be turned on and off under software control. When the Timerx On control bit (TMRxON) is set, the timer increments from the clock source. When TMRxON is cleared, the timer is turned off and cannot cause the timer interrupt flag to be set.

#### 12.1.1.1 EXTERNAL CLOCK INPUT FOR TIMER1 OR TIMER2

When TMRxCS is set, the clock source is the RB4/TCLK12 pin, and the timer will increment on every falling edge on the RB4/TCLK12 pin. The TCLK12 input is synchronized with internal phase clocks. This causes a delay from the time a falling edge appears on TCLK12 to the time TMR1 or TMR2 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

#### FIGURE 12-3: TIMER1 AND TIMER2 IN TWO 8-BIT TIMER/COUNTER MODE

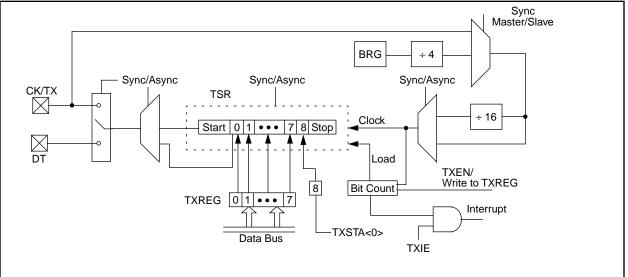

#### FIGURE 13-3: USART TRANSMIT

| CPFSEQ                                         | Compare f with WREG, skip if f = WREG                                                                                                                                                                                                                              |                                                |        | CPF        | SGT                                           | Compare<br>skip if f >                                                                                                                                                                                                                                                         | f with WRE<br>WREG                                             | G,      |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--------|------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------|--|--|

| Syntax:                                        | [label]                                                                                                                                                                                                                                                            | CPFSEQ f                                       |        | Syn        | tax:                                          | [label]                                                                                                                                                                                                                                                                        | [label] CPFSGT f                                               |         |  |  |

| Operands:                                      | $0 \le f \le 255$                                                                                                                                                                                                                                                  | 5                                              |        | Ope        | rands:                                        | $0 \le f \le 255$                                                                                                                                                                                                                                                              | $0 \le f \le 255$                                              |         |  |  |

| Operation:                                     | (f) – (WRE)<br>skip if (f) =<br>(unsigned o                                                                                                                                                                                                                        |                                                |        | Ope        | ration:                                       | skip if (f) >                                                                                                                                                                                                                                                                  | (f) – (WREG),<br>skip if (f) > (WREG)<br>(unsigned comparison) |         |  |  |

| Status Affected:                               | None                                                                                                                                                                                                                                                               |                                                |        | Stat       | us Affected:                                  | None                                                                                                                                                                                                                                                                           |                                                                |         |  |  |

| Encoding:                                      | 0011                                                                                                                                                                                                                                                               | 0001 fff                                       | f ffff | Enc        | oding:                                        | 0011                                                                                                                                                                                                                                                                           | 0010 ff:                                                       | ff ffff |  |  |

| Description:                                   | Compares the contents of data memory<br>location 'f' to the contents of WREG by<br>performing an unsigned subtraction.<br>If 'f' = WREG then the fetched instruc-<br>tion is discarded and an NOP is exe-<br>cuted instead making this a two-cycle<br>instruction. |                                                |        | Des        | cription:                                     | Compares the contents of data men<br>location 'f' to the contents of the WF<br>by performing an unsigned subtract<br>If the contents of 'f' > the contents of<br>WREG then the fetched instruction<br>discarded and an NOP is executed<br>instead making this a two-cycle inst |                                                                |         |  |  |

| Words:                                         | 1                                                                                                                                                                                                                                                                  |                                                |        | 14/0 -     | de .                                          | tion.<br>1                                                                                                                                                                                                                                                                     |                                                                |         |  |  |

| Cycles:                                        | 1 (2)                                                                                                                                                                                                                                                              |                                                |        | Wor        |                                               | -                                                                                                                                                                                                                                                                              |                                                                |         |  |  |

| Q Cycle Activity:                              |                                                                                                                                                                                                                                                                    |                                                |        | Cyc        |                                               | 1 (2)                                                                                                                                                                                                                                                                          |                                                                |         |  |  |

| Q1                                             | Q2                                                                                                                                                                                                                                                                 | Q3                                             | Q4     | QC         | ycle Activity:<br>Q1                          | Q2                                                                                                                                                                                                                                                                             | Q3                                                             | Q4      |  |  |

| Decode                                         | Read<br>register 'f'                                                                                                                                                                                                                                               | Execute                                        | NOP    |            | Decode                                        | Read                                                                                                                                                                                                                                                                           | Execute                                                        | NOP     |  |  |

| If skip:                                       |                                                                                                                                                                                                                                                                    |                                                |        | lf sk      | in:                                           | register 'f'                                                                                                                                                                                                                                                                   |                                                                |         |  |  |

| Q1                                             | Q2                                                                                                                                                                                                                                                                 | Q3                                             | Q4     |            | Q1                                            | Q2                                                                                                                                                                                                                                                                             | Q3                                                             | Q4      |  |  |

| Forced NOP                                     | NOP                                                                                                                                                                                                                                                                | Execute                                        | NOP    |            | Forced NOP                                    | NOP                                                                                                                                                                                                                                                                            | Execute                                                        | NOP     |  |  |

| <u>Example</u> :                               | NEQUAL                                                                                                                                                                                                                                                             | CPFSEQ REG<br>:<br>:                           |        | <u>Exa</u> | mple:                                         | HERE<br>NGREATER<br>GREATER                                                                                                                                                                                                                                                    | CPFSGT RE<br>:<br>:                                            | G       |  |  |

| Before Instru<br>PC Addre                      |                                                                                                                                                                                                                                                                    |                                                |        |            | Before Instru                                 | -                                                                                                                                                                                                                                                                              | ·                                                              |         |  |  |

| WREG<br>REG                                    | ess = HE<br>= ?<br>= ?                                                                                                                                                                                                                                             | RE                                             |        |            | PC<br>WREG                                    |                                                                                                                                                                                                                                                                                | dress (HERE)                                                   |         |  |  |

| After Instruct<br>If REG<br>PC<br>If REG<br>PC | = W<br>= Ac<br>≠ W                                                                                                                                                                                                                                                 | REG;<br>Idress (EQUAL<br>REG;<br>Idress (NEQUA |        |            | After Instruc<br>If REG<br>PC<br>If REG<br>PC | > Wi<br>= Ad<br>≤ Wi                                                                                                                                                                                                                                                           | REG;<br>Idress (GREAT<br>REG;<br>Idress (NGREZ                 |         |  |  |

# PIC17C4X

| SWAPF                                                                                                                                                                        | Swap f                                                            |                          |      |                       |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|------|-----------------------|--|--|--|--|

| Syntax:                                                                                                                                                                      | [label]                                                           | SWAPF                    | f,d  |                       |  |  |  |  |

| Operands:                                                                                                                                                                    | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ | 0 ≤ f ≤ 255<br>d ∈ [0,1] |      |                       |  |  |  |  |

| Operation:                                                                                                                                                                   | $f < 3:0 > \rightarrow f < 7:4 > \rightarrow$                     |                          | ,    |                       |  |  |  |  |

| Status Affected:                                                                                                                                                             | None                                                              |                          |      |                       |  |  |  |  |

| Encoding:                                                                                                                                                                    | 0001                                                              | 110d                     | ffff | ffff                  |  |  |  |  |

| Description: The upper and lower nibbles of register<br>'f' are exchanged. If 'd' is 0 the result is<br>placed in WREG. If 'd' is 1 the result is<br>placed in register 'f'. |                                                                   |                          |      |                       |  |  |  |  |

| Words:                                                                                                                                                                       | 1                                                                 | 1                        |      |                       |  |  |  |  |

| Cycles:                                                                                                                                                                      | 1                                                                 |                          |      |                       |  |  |  |  |

| Q Cycle Activity:                                                                                                                                                            |                                                                   |                          |      |                       |  |  |  |  |

| Q1                                                                                                                                                                           | Q2                                                                | Q                        | 3    | Q4                    |  |  |  |  |

| Decode                                                                                                                                                                       | Read<br>register 'f'                                              | Exect                    |      | Vrite to<br>stination |  |  |  |  |

| Example:                                                                                                                                                                     | SWAPF I                                                           | REG,                     | 0    |                       |  |  |  |  |

| Before Instruction<br>REG = 0x53                                                                                                                                             |                                                                   |                          |      |                       |  |  |  |  |

| REG = 0x53<br>After Instruction<br>REG = 0x35                                                                                                                                |                                                                   |                          |      |                       |  |  |  |  |

| TABLRD            | Table Rea                                                                                                                                                                                                                                                 | d            |                       |  |  |  |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------|--|--|--|--|--|

| Syntax:           | [label]                                                                                                                                                                                                                                                   | rablrd t,i,f |                       |  |  |  |  |  |

| Operands:         | $0 \le f \le 255$<br>$i \in [0,1]$<br>$t \in [0,1]$                                                                                                                                                                                                       | 5            |                       |  |  |  |  |  |

| Operation:        | If t = 1,<br>TBLATH $\rightarrow$ f;<br>If t = 0,<br>TBLATL $\rightarrow$ f;<br>Prog Mem (TBLPTR) $\rightarrow$ TBLAT;<br>If i = 1,<br>TBLPTR + 1 $\rightarrow$ TBLPTR                                                                                    |              |                       |  |  |  |  |  |

| Status Affected:  | None                                                                                                                                                                                                                                                      |              |                       |  |  |  |  |  |

| Encoding:         | 1010                                                                                                                                                                                                                                                      | 10ti ff      | ff ffff               |  |  |  |  |  |

| Description:      | <ol> <li>A byte of the table latch (TBLAT)<br/>is moved to register file 'f'.<br/>If t = 0: the high byte is moved;<br/>If t = 1: the low byte is moved</li> </ol>                                                                                        |              |                       |  |  |  |  |  |

|                   | <ol> <li>Then the contents of the program<br/>memory location pointed to by<br/>the 16-bit Table Pointer<br/>(TBLPTR) is loaded into the<br/>16-bit Table Latch (TBLAT).</li> <li>If i = 1: TBLPTR is incremented;<br/>If i = 0: TBLPTR is not</li> </ol> |              |                       |  |  |  |  |  |

| Words:            | 1                                                                                                                                                                                                                                                         | incremented  |                       |  |  |  |  |  |

| Cycles:           | 2 (3 cycle                                                                                                                                                                                                                                                | if f = PCL)  |                       |  |  |  |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                           |              |                       |  |  |  |  |  |

| Q1                | Q2 Q3 Q4                                                                                                                                                                                                                                                  |              |                       |  |  |  |  |  |

| Decode            | Read<br>register<br>TBLATH or<br>TBLATL                                                                                                                                                                                                                   | Execute      | Write<br>register 'f' |  |  |  |  |  |

Applicable Devices 42 R42 42A 43 R43 44

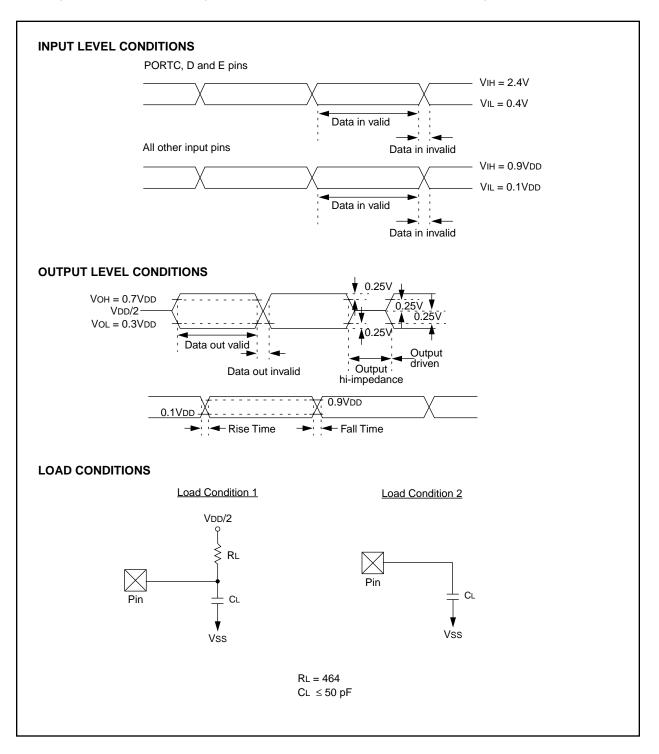

# FIGURE 17-1: PARAMETER MEASUREMENT INFORMATION

All timings are measure between high and low measurement points as indicated in the figures below.

# PIC17C4X

# Applicable Devices 42 R42 42A 43 R43 44

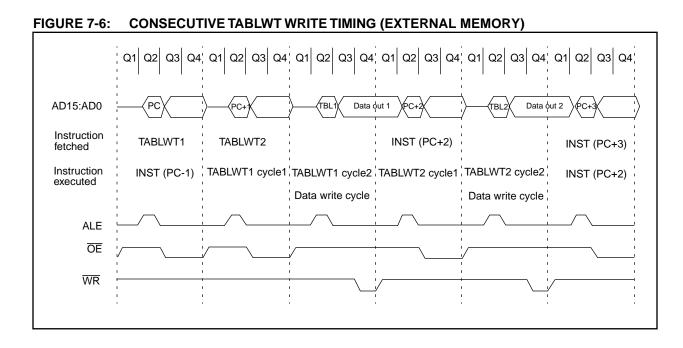

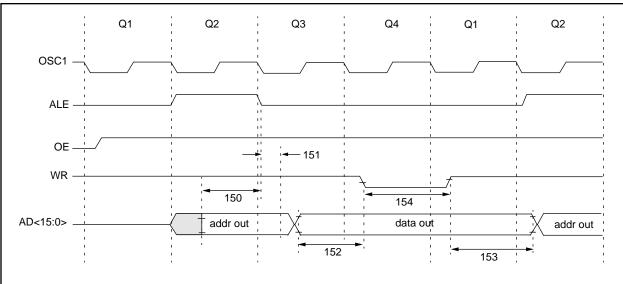

#### FIGURE 17-11: MEMORY INTERFACE WRITE TIMING

#### TABLE 17-11: MEMORY INTERFACE WRITE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                | Min          | Тур†      | Max | Units | Conditions |

|------------------|----------|---------------------------------------------------------------|--------------|-----------|-----|-------|------------|

| 150              | TadV2alL | AD<15:0> (address) valid to ALE↓<br>(address setup time)      | 0.25Tcy - 30 |           |     | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)               | 0            | _         | _   | ns    |            |

| 152              | TadV2wrL | Data out valid to $\overline{WR}\downarrow$ (data setup time) | 0.25Tcy - 40 | —         | —   | ns    |            |

| 153              | TwrH2adI | WR↑ to data out invalid<br>(data hold time)                   | _            | 0.25Tcy § | —   | ns    |            |

| 154              | TwrL     | WR pulse width                                                | —            | 0.25Tcy § | _   | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification is guaranteed by design.

# Applicable Devices 42 R42 42A 43 R43 44

#### 19.2 **DC CHARACTERISTICS:**

### PIC17LC42A/43/LC44 (Commercial, Industrial) PIC17LCR42/43 (Commercial, Industrial)

| DC CHARA         | Standard<br>Operating |                                                                  | •       |      | s (unless otherwise stated)<br>$\leq TA \leq +85^{\circ}C$ for industrial and<br>$\leq TA \leq +70^{\circ}C$ for commercial |       |                                           |

|------------------|-----------------------|------------------------------------------------------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------|

| Parameter<br>No. | Sym                   | Characteristic                                                   | Min     | Тур† | Мах                                                                                                                         | Units | Conditions                                |

| D001             | Vdd                   | Supply Voltage                                                   | 2.5     | _    | 6.0                                                                                                                         | V     |                                           |

| D002             | Vdr                   | RAM Data Retention<br>Voltage (Note 1)                           | 1.5 *   | -    | Ι                                                                                                                           | V     | Device in SLEEP mode                      |

| D003             | VPOR                  | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | _       | Vss  | _                                                                                                                           | V     | See section on Power-on Reset for details |

| D004             | SVDD                  | VDD rise rate to<br>ensure internal<br>Power-on Reset signal     | 0.060 * | _    | Ι                                                                                                                           | mV/ms | See section on Power-on Reset for details |

| D010             | IDD                   | Supply Current                                                   | -       | 3    | 6                                                                                                                           | mA    | Fosc = 4 MHz (Note 4)                     |

| D011             |                       | (Note 2)                                                         | -       | 6    | 12 *                                                                                                                        | mA    | Fosc = 8 MHz                              |

| D014             |                       |                                                                  | -       | 95   | 150                                                                                                                         | μA    | Fosc = 32 kHz,                            |

|                  |                       |                                                                  |         |      |                                                                                                                             |       | WDT disabled (EC osc configuration)       |

| D020             | IPD                   | Power-down                                                       | -       | 10   | 40                                                                                                                          | μA    | VDD = 5.5V, WDT enabled                   |

| D021             |                       | Current (Note 3)                                                 | -       | < 1  | 5                                                                                                                           | μA    | VDD = 5.5V, WDT disabled                  |

These parameters are characterized but not tested.

+ Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1=external square wave, from rail to rail; all I/O pins tristated, pulled to VDD or VSS, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

Current consumed from the oscillator and I/O's driving external capacitive or resistive loads needs to be considered.

For the RC oscillator, the current through the external pull-up resistor (R) can be estimated as: VbD / (2 • R). For capacitive loads, the current can be estimated (for an individual I/O pin) as (CL • VDD) • f

CL = Total capacitive load on the I/O pin; f = average frequency the I/O pin switches.

The capacitive currents are most significant when the device is configured for external execution (includes extended microcontroller mode).

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD or VSS.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IR = VDD/2Rext (mA) with Rext in kOhm.

Standard Operating Conditions (unloss otherwise stated)

## Applicable Devices 42 R42 42A 43 R43 44

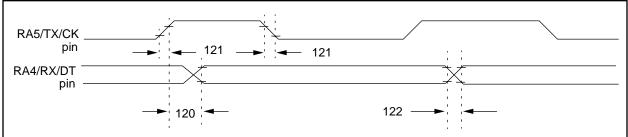

### FIGURE 19-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

#### TABLE 19-9: SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Param | C. m                                                                                                                     | Characteristic                    |                          | Min  | Trent | Max | Unito | Conditions |

|-------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------|------|-------|-----|-------|------------|

| No.   | Sym                                                                                                                      | Characteristic                    |                          | wiin | Тур†  | Max | Units | Conditions |

| 120   | TckH2dtV                                                                                                                 | SYNC XMIT (MASTER &               |                          |      |       |     |       |            |

|       |                                                                                                                          | SLAVE)                            | PIC17CR42/42A/43/R43/44  | _    | —     | 50  | ns    |            |

|       |                                                                                                                          | Clock high to data out valid      | PIC17LCR42/42A/43/R43/44 | 1 —  | —     | 75  | ns    |            |

| 121   | TckRF                                                                                                                    | Clock out rise time and fall time | PIC17CR42/42A/43/R43/44  | —    | —     | 25  | ns    |            |

|       |                                                                                                                          | (Master Mode)                     | PIC17LCR42/42A/43/R43/44 | —    | —     | 40  | ns    |            |

| 122   | TdtRF                                                                                                                    | Data out rise time and fall time  | PIC17CR42/42A/43/R43/44  | —    | —     | 25  | ns    |            |

|       |                                                                                                                          |                                   | PIC17LCR42/42A/43/R43/44 | —    | —     | 40  | ns    |            |

| †     | † Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not |                                   |                          |      |       |     |       |            |

Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

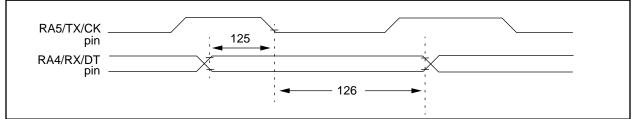

#### FIGURE 19-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

#### **TABLE 19-10: SYNCHRONOUS RECEIVE REQUIREMENTS**

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  |      | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | _    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC17C4X

# Applicable Devices 42 R42 42A 43 R43 44

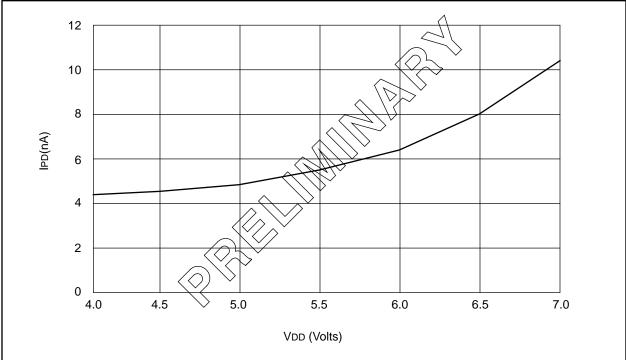

# FIGURE 20-9: TYPICAL IPD vs. VDD WATCHDOG DISABLED 25°C

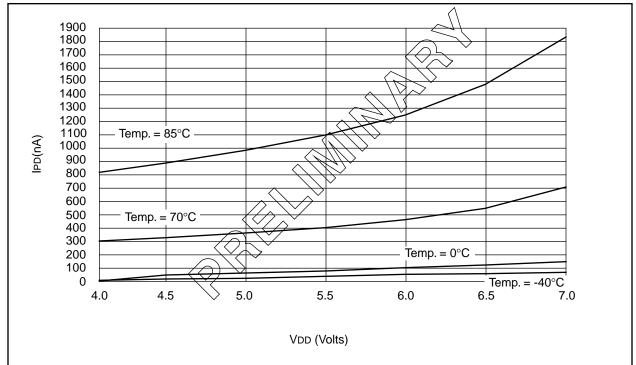

FIGURE 20-10: MAXIMUM IPD vs. VDD WATCHDOG DISABLED

NOTES:

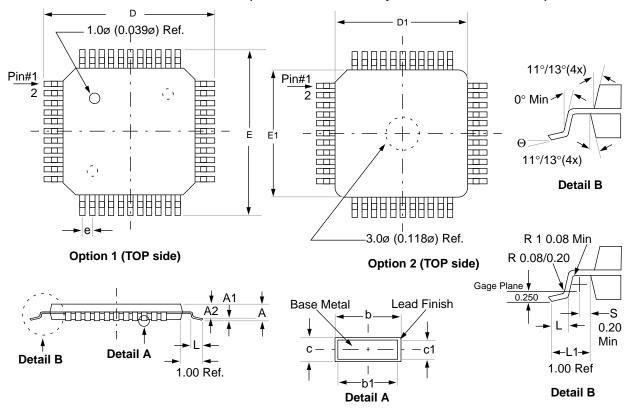

| 21.5 | 44-Lead Plastic Surface Mount ( | TOFP 10x10 mm Body | (1.0/0.10 mm Lead Form) |

|------|---------------------------------|--------------------|-------------------------|

| 21.0 |                                 |                    |                         |

|        | Package Group: Plastic TQFP |            |       |       |            |       |

|--------|-----------------------------|------------|-------|-------|------------|-------|

|        | Millimeters                 |            |       |       |            |       |

| Symbol | Min                         | Max        | Notes | Min   | Max        | Notes |

| Α      | 1.00                        | 1.20       |       | 0.039 | 0.047      |       |

| A1     | 0.05                        | 0.15       |       | 0.002 | 0.006      |       |

| A2     | 0.95                        | 1.05       |       | 0.037 | 0.041      |       |

| D      | 11.75                       | 12.25      |       | 0.463 | 0.482      |       |

| D1     | 9.90                        | 10.10      |       | 0.390 | 0.398      |       |

| E      | 11.75                       | 12.25      |       | 0.463 | 0.482      |       |

| E1     | 9.90                        | 10.10      |       | 0.390 | 0.398      |       |

| L      | 0.45                        | 0.75       |       | 0.018 | 0.030      |       |

| е      | 0.80                        | BSC        |       | 0.031 | BSC        |       |

| b      | 0.30                        | 0.45       |       | 0.012 | 0.018      |       |

| b1     | 0.30                        | 0.40       |       | 0.012 | 0.016      |       |

| С      | 0.09                        | 0.20       |       | 0.004 | 0.008      |       |

| c1     | 0.09                        | 0.16       |       | 0.004 | 0.006      |       |

| Ν      | 44                          | 44         |       | 44    | 44         |       |

| Θ      | 0°                          | <b>7</b> ° |       | 0°    | <b>7</b> ° |       |

Note 1: Dimensions D1 and E1 do not include mold protrusion. Allowable mold protrusion is 0.25m/m (0.010") per side. D1 and E1 dimensions including mold mismatch.

2: Dimension "b" does not include Dambar protrusion, allowable Dambar protrusion shall be 0.08m/m (0.003")max.

3: This outline conforms to JEDEC MS-026.

NOTES:

# **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:     |         | Technical Publications Manager Total Pages Sent                                           |

|---------|---------|-------------------------------------------------------------------------------------------|

| RE<br>_ |         | Reader Response                                                                           |

| Fro     | om:     | Name                                                                                      |

|         |         | Company                                                                                   |

|         |         | Address<br>City / State / ZIP / Country                                                   |

|         |         | Telephone: () FAX: ()                                                                     |

| Ар      | plica   | ation (optional):                                                                         |

| Wo      | buld    | you like a reply?YN                                                                       |

| De      | vice    | E: PIC17C4X Literature Number: DS30412C                                                   |

|         |         | ions:                                                                                     |

|         |         |                                                                                           |

| 1.      | W       | hat are the best features of this document?                                               |

|         |         |                                                                                           |

| 2       | —<br>Ho | ow does this document meet your hardware and software development needs?                  |

| ۷.      |         | Sw does this document meet your hardware and software development needs:                  |

|         |         |                                                                                           |

| 3.      | Do      | o you find the organization of this data sheet easy to follow? If not, why?               |

|         |         |                                                                                           |

|         |         |                                                                                           |

| 4.      | W       | hat additions to the data sheet do you think would enhance the structure and subject?     |

|         |         |                                                                                           |

| ~       |         |                                                                                           |

| 5.      | vvi     | hat deletions from the data sheet could be made without affecting the overall usefulness? |

|         |         |                                                                                           |

| 6.      | ls      | there any incorrect or misleading information (what and where)?                           |

|         |         |                                                                                           |

|         |         |                                                                                           |

| 7.      | Ho      | ow would you improve this document?                                                       |

|         |         |                                                                                           |

|         |         |                                                                                           |

| 8.      | Ho      | ow would you improve our software, systems, and silicon products?                         |