Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 8MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 4KB (2K x 16)                                                              |

| Program Memory Type        | ОТР                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 232 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-LCC (J-Lead)                                                            |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc42a-08i-l |

|                            |                                                                            |

#### RESET 4.0

The PIC17CXX differentiates between various kinds of

- Power-on Reset (POR)

- MCLR reset during normal operation

- WDT Reset (normal operation)

Some registers are not affected in any reset condition: their status is unknown on POR and unchanged in any other reset. Most other registers are forced to a "reset state" on Power-on Reset (POR), on MCLR or WDT Reset and on MCLR reset during SLEEP. They are not affected by a WDT Reset during SLEEP, since this reset is viewed as the resumption of normal operation. The TO and PD bits are set or cleared differently in different reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of reset. See Table 4-4 for a full description of reset states of all registers.

Note: While the device is in a reset state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

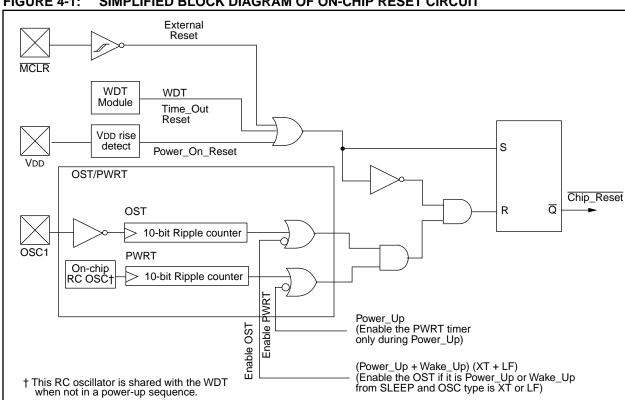

A simplified block diagram of the on-chip reset circuit is shown in Figure 4-1.

#### 4.1 Power-on Reset (POR), Power-up Timer (PWRT), and Oscillator Start-up Timer (OST)

#### 4.1.1 POWER-ON RESET (POR)

The Power-on Reset circuit holds the device in reset until VDD is above the trip point (in the range of 1.4V -2.3V). The PIC17C42 does not produce an internal reset when VDD declines. All other devices will produce an internal reset for both rising and falling VDD. To take advantage of the POR, just tie the MCLR/VPP pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD is required. See Electrical Specifications for details.

#### 4.1.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 96 ms time-out (nominal) on power-up. This occurs from rising edge of the POR signal and after the first rising edge of MCLR (detected high). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. In most cases the PWRT delay allows the VDD to rise to an acceptable level.

The power-up time delay will vary from chip to chip and to VDD and temperature. See DC parameters for details.

SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT FIGURE 4-1:

#### 6.0 MEMORY ORGANIZATION

There are two memory blocks in the PIC17C4X; program memory and data memory. Each block has its own bus, so that access to each block can occur during the same oscillator cycle.

The data memory can further be broken down into General Purpose RAM and the Special Function Registers (SFRs). The operation of the SFRs that control the "core" are described here. The SFRs used to control the peripheral modules are described in the section discussing each individual peripheral module.

#### 6.1 **Program Memory Organization**

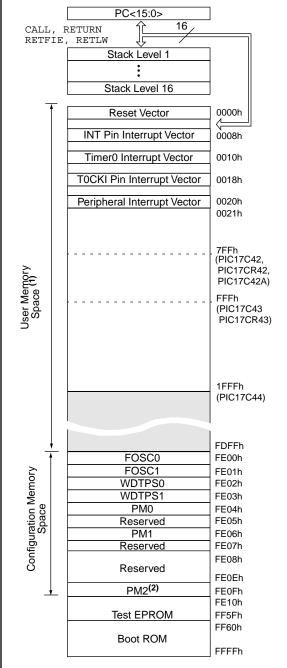

PIC17C4X devices have a 16-bit program counter capable of addressing a 64K x 16 program memory space. The reset vector is at 0000h and the interrupt vectors are at 0008h, 0010h, 0018h, and 0020h (Figure 6-1).

#### 6.1.1 PROGRAM MEMORY OPERATION

The PIC17C4X can operate in one of four possible program memory configurations. The configuration is selected by two configuration bits. The possible modes are:

- Microprocessor

- Microcontroller

- Extended Microcontroller

- Protected Microcontroller

The microcontroller and protected microcontroller modes only allow internal execution. Any access beyond the program memory reads unknown data. The protected microcontroller mode also enables the code protection feature.

The extended microcontroller mode accesses both the internal program memory as well as external program memory. Execution automatically switches between internal and external memory. The 16-bits of address allow a program memory range of 64K-words.

The microprocessor mode only accesses the external program memory. The on-chip program memory is ignored. The 16-bits of address allow a program memory range of 64K-words. Microprocessor mode is the default mode of an unprogrammed device.

The different modes allow different access to the configuration bits, test memory, and boot ROM. Table 6-1 lists which modes can access which areas in memory. Test Memory and Boot Memory are not required for normal operation of the device. Care should be taken to ensure that no unintended branches occur to these areas.

FIGURE 6-1: PROGRAM MEMORY MAP AND STACK

- Note 1: User memory space may be internal, external, or both. The memory configuration depends on the processor mode.

- 2: This location is reserved on the PIC17C42.

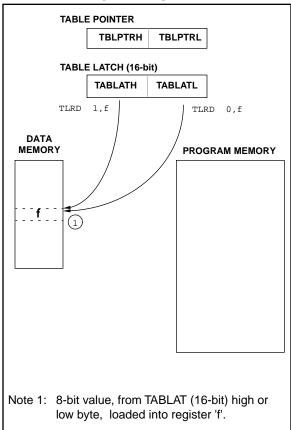

## FIGURE 7-3: TLRD INSTRUCTION OPERATION

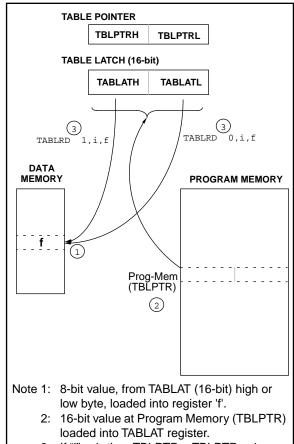

FIGURE 7-4: TABLRD INSTRUCTION OPERATION

3: If "i" = 1, then TBLPTR = TBLPTR + 1, If "i" = 0, then TBLPTR is unchanged.

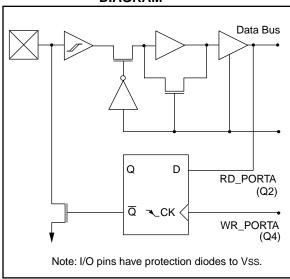

FIGURE 9-2: RA2 AND RA3 BLOCK DIAGRAM

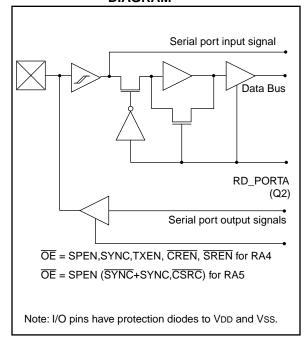

FIGURE 9-3: RA4 AND RA5 BLOCK DIAGRAM

TABLE 9-1: PORTA FUNCTIONS

| Name      | Bit0 | Buffer Type | Function                                                                            |

|-----------|------|-------------|-------------------------------------------------------------------------------------|

| RA0/INT   | bit0 | ST          | Input or external interrupt input.                                                  |

| RA1/T0CKI | bit1 | ST          | Input or clock input to the TMR0 timer/counter, and/or an external interrupt input. |

| RA2       | bit2 | ST          | Input/Output. Output is open drain type.                                            |

| RA3       | bit3 | ST          | Input/Output. Output is open drain type.                                            |

| RA4/RX/DT | bit4 | ST          | Input or USART Asynchronous Receive or USART Synchronous Data.                      |

| RA5/TX/CK | bit5 | ST          | Input or USART Asynchronous Transmit or USART Synchronous Clock.                    |

| RBPU      | bit7 | _           | Control bit for PORTB weak pull-ups.                                                |

Legend: ST = Schmitt Trigger input.

TABLE 9-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address       | Name  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-------|--------|-------|-------|-------|-------|-------|-----------|---------|-------------------------------|-----------------------------------------|

| 10h, Bank 0   | PORTA | RBPU   | -     | RA5   | RA4   | RA3   | RA2   | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                               |

| 05h, Unbanked | T0STA | INTEDG | T0SE  | T0CS  | PS3   | PS2   | PS1   | PS0       | _       | 0000 000-                     | 0000 000-                               |

| 13h, Bank 0   | RCSTA | SPEN   | RC9   | SREN  | CREN  | _     | FERR  | OERR      | RC9D    | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0   | TXSTA | CSRC   | TX9   | TXEN  | SYNC  | _     | _     | TRMT      | TX9D    | 00001x                        | 00001u                                  |

Legend: x = unknown, u = unchanged,  $- = unimplemented reads as '0'. Shaded cells are not used by PORTA. Note 1: Other (non power-up) resets include: external reset through <math>\overline{MCLR}$  and the Watchdog Timer Reset.

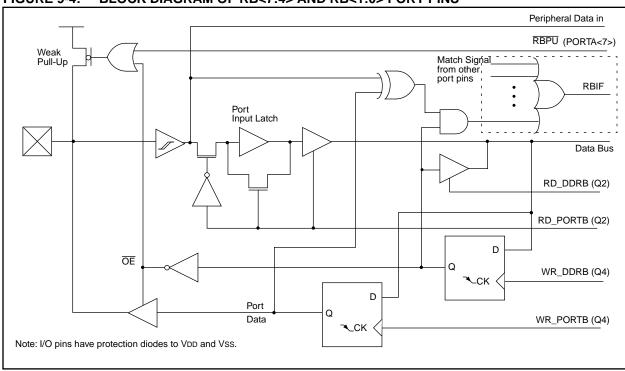

#### 9.2 PORTB and DDRB Registers

PORTB is an 8-bit wide bi-directional port. The corresponding data direction register is DDRB. A '1' in DDRB configures the corresponding port pin as an input. A '0' in the DDRB register configures the corresponding port pin as an output. Reading PORTB reads the status of the pins, whereas writing to it will write to the port latch.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all the pull-ups. This is done by clearing the RBPU (PORTA<7>) bit. The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are enabled on any reset.

PORTB also has an interrupt on change feature. Only pins configured as inputs can cause this interrupt to occur (i.e. any RB7:RB0 pin configured as an output is excluded from the interrupt on change comparison). The input pins (of RB7:RB0) are compared with the value in the PORTB data latch. The "mismatch" outputs of RB7:RB0 are OR'ed together to generate the PORTB Interrupt Flag RBIF (PIR<7>).

This interrupt can wake the device from SLEEP. The user, in the interrupt service routine, can clear the interrupt by:

- Read-Write PORTB (such as; MOVPF PORTB, PORTB). This will end mismatch condition.

- b) Then, clear the RBIF bit.

A mismatch condition will continue to set the RBIF bit. Reading then writing PORTB will end the mismatch condition, and allow the RBIF bit to be cleared.

This interrupt on mismatch feature, together with software configurable pull-ups on this port, allows easy interface to a key pad and make it possible for wake-up on key-depression. For an example, refer to AN552 in the *Embedded Control Handbook*.

The interrupt on change feature is recommended for wake-up on operations where PORTB is only used for the interrupt on change feature and key depression operation.

FIGURE 9-4: BLOCK DIAGRAM OF RB<7:4> AND RB<1:0> PORT PINS

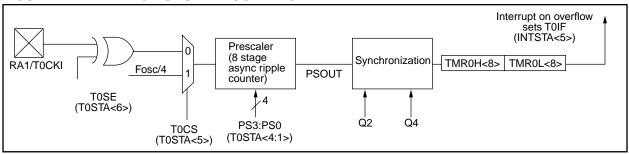

#### 11.1 <u>Timer0 Operation</u>

When the TOCS (TOSTA<5>) bit is set, TMR0 increments on the internal clock. When TOCS is clear, TMR0 increments on the external clock (RA1/TOCKI pin). The external clock edge can be configured in software. When the TOSE (TOSTA<6>) bit is set, the timer will increment on the rising edge of the RA1/TOCKI pin. When TOSE is clear, the timer will increment on the falling edge of the RA1/TOCKI pin. The prescaler can be programmed to introduce a prescale of 1:1 to 1:256. The timer increments from 0000h to FFFFh and rolls over to 0000h. On overflow, the TMR0 Interrupt Flag bit (TOIF) is set. The TMR0 interrupt can be masked by clearing the corresponding TMR0 Interrupt Enable bit (TOIE). The TMR0 Interrupt Flag bit (TOIF) is automatically cleared when vectoring to the TMR0 interrupt vector.

#### 11.2 <u>Using Timer0 with External Clock</u>

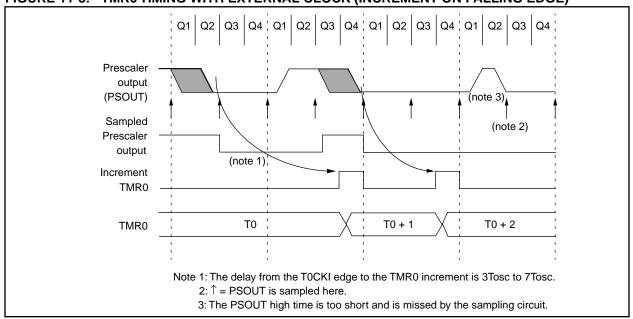

When the external clock input is used for Timer0, it is synchronized with the internal phase clocks. Figure 11-3 shows the synchronization of the external clock. This synchronization is done after the prescaler. The output of the prescaler (PSOUT) is sampled twice in every instruction cycle to detect a rising or a falling edge. The timing requirements for the external clock are detailed in the electrical specification section for the desired device.

#### 11.2.1 DELAY FROM EXTERNAL CLOCK EDGE

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time TMR0 is actually incremented. Figure 11-3 shows that this delay is between 3Tosc and 7Tosc. Thus, for example, measuring the interval between two edges (e.g. period) will be accurate within  $\pm 4Tosc$  ( $\pm 121$  ns @ 33 MHz).

FIGURE 11-2: TIMERO MODULE BLOCK DIAGRAM

FIGURE 11-3: TMR0 TIMING WITH EXTERNAL CLOCK (INCREMENT ON FALLING EDGE)

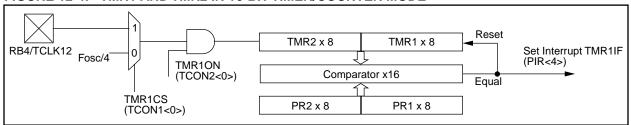

#### 12.1.2 TIMER1 & TIMER2 IN 16-BIT MODE

To select 16-bit mode, the T16 bit must be set. In this mode TMR1 and TMR2 are concatenated to form a 16-bit timer (TMR2:TMR1). The 16-bit timer increments until it matches the 16-bit period register (PR2:PR1). On the following timer clock, the timer value is reset to 0h, and the TMR1IF bit is set.

When selecting the clock source for the 16-bit timer, the TMR1CS bit controls the entire 16-bit timer and TMR2CS is a "don't care." When TMR1CS is clear, the timer increments once every instruction cycle (Fosc/4). When TMR1CS is set, the timer increments on every falling edge of the RB4/TCLK12 pin. For the 16-bit timer to increment, both TMR1ON and TMR2ON bits must be set (Table 12-1).

## 12.1.2.1 EXTERNAL CLOCK INPUT FOR TMR1:TMR2

When TMR1CS is set, the 16-bit TMR2:TMR1 increments on the falling edge of clock input TCLK12. The input on the RB4/TCLK12 pin is sampled and synchronized by the internal phase clocks twice every instruction cycle. This causes a delay from the time a falling edge appears on RB4/TCLK12 to the time TMR2:TMR1 is actually incremented. For the external clock input timing requirements, see the Electrical Specification section.

TABLE 12-1: TURNING ON 16-BIT TIMER

| TMR2ON | TMR10N | Result                         |

|--------|--------|--------------------------------|

| 1      | 1      | 16-bit timer<br>(TMR2:TMR1) ON |

| 0      | 1      | Only TMR1 increments           |

| х      | 0      | 16-bit timer OFF               |

FIGURE 12-4: TMR1 AND TMR2 IN 16-BIT TIMER/COUNTER MODE

TABLE 12-2: SUMMARY OF TIMER1 AND TIMER2 REGISTERS

| Address                          | Name                           | Bit 7     | Bit 6        | Bit 5  | Bit 4  | Bit 3   | Bit 2  | Bit 1     | Bit 0     | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|----------------------------------|--------------------------------|-----------|--------------|--------|--------|---------|--------|-----------|-----------|-------------------------------|-----------------------------------------|

| 16h, Bank 3                      | TCON1                          | CA2ED1    | CA2ED0       | CA1ED1 | CA1ED0 | T16     | TMR3CS | TMR2CS    | TMR1CS    | 0000 0000                     | 0000 0000                               |

| 17h, Bank 3                      | TCON2                          | CA2OVF    | CA10VF       | PWM2ON | PWM10N | CA1/PR3 | TMR3ON | TMR2ON    | TMR10N    | 0000 0000                     | 0000 0000                               |

| 10h, Bank 2 TMR1 Timer1 register |                                |           |              |        |        |         |        |           | xxxx xxxx | uuuu uuuu                     |                                         |

| 11h, Bank 2                      | n, Bank 2 TMR2 Timer2 register |           |              |        |        |         |        | xxxx xxxx | uuuu uuuu |                               |                                         |

| 16h, Bank 1                      | PIR                            | RBIF      | TMR3IF       | TMR2IF | TMR1IF | CA2IF   | CA1IF  | TXIF      | RCIF      | 0000 0010                     | 0000 0010                               |

| 17h, Bank 1                      | PIE                            | RBIE      | TMR3IE       | TMR2IE | TMR1IE | CA2IE   | CA1IE  | TXIE      | RCIE      | 0000 0000                     | 0000 0000                               |

| 07h, Unbanked                    | INTSTA                         | PEIF      | T0CKIF       | TOIF   | INTF   | PEIE    | T0CKIE | TOIE      | INTE      | 0000 0000                     | 0000 0000                               |

| 06h, Unbanked                    | CPUSTA                         | _         | _            | STKAV  | GLINTD | TO      | PD     | _         | _         | 11 11                         | 11 qq                                   |

| 14h, Bank 2                      | PR1                            | Timer1 pe | riod registe | r      |        |         |        |           |           | xxxx xxxx                     | uuuu uuuu                               |

| 15h, Bank 2                      | PR2                            | Timer2 pe | riod registe | r      |        |         |        |           |           | xxxx xxxx                     | uuuu uuuu                               |

| 10h, Bank 3                      | PW1DCL                         | DC1       | DC0          | _      | _      | _       | _      | _         | _         | xx                            | uu                                      |

| 11h, Bank 3                      | PW2DCL                         | DC1       | DC0          | TM2PW2 | _      | _       | _      | _         | _         | xx0                           | uu0                                     |

| 12h, Bank 3                      | PW1DCH                         | DC9       | DC8          | DC7    | DC6    | DC5     | DC4    | DC3       | DC2       | xxxx xxxx                     | uuuu uuuu                               |

| 13h, Bank 3                      | PW2DCH                         | DC9       | DC8          | DC7    | DC6    | DC5     | DC4    | DC3       | DC2       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', q - value depends on condition, shaded cells are not used by Timer1 or Timer2.

Note 1: Other (non power-up) resets include: external reset through MCLR and WDT Timer Reset.

# 13.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART) MODULE

The USART module is a serial I/O module. The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

The SPEN (RCSTA<7>) bit has to be set in order to configure RA4 and RA5 as the Serial Communication Interface.

The USART module will control the direction of the RA4/RX/DT and RA5/TX/CK pins, depending on the states of the USART configuration bits in the RCSTA and TXSTA registers. The bits that control I/O direction are:

- SPEN

- TXEN

- SREN

- CREN

- CSRC

The Transmit Status And Control Register is shown in Figure 13-1, while the Receive Status And Control Register is shown in Figure 13-2.

#### FIGURE 13-1: TXSTA REGISTER (ADDRESS: 15h, BANK 0)

| <u>R/W - 0</u><br>CSRC | R/W - 0<br>TX9                                                           | R/W - 0<br>TXEN                                | R/W - 0<br>SYNC  | <u>U - 0</u> | U - 0<br>—    | R - 1<br>TRMT | R/W - x<br>TX9D | R = Readable bit                                             |

|------------------------|--------------------------------------------------------------------------|------------------------------------------------|------------------|--------------|---------------|---------------|-----------------|--------------------------------------------------------------|

| oit7                   | 11.15                                                                    |                                                |                  |              |               |               | bit0            | W = Writable bit<br>-n = Value at POR reset<br>(x = unknown) |

| oit 7:                 | CSRC: C<br>Synchron<br>1 = Maste<br>0 = Slave<br>Asynchron<br>Don't care | ous mode<br>r Mode (C<br>mode (Clo<br>nous mod | lock gene        | rated inte   | rnally from I | BRG)          |                 |                                                              |

| oit 6:                 | <b>TX9</b> : 9-bit<br>1 = Select<br>0 = Select                           | s 9-bit tra                                    | nsmission        |              |               |               |                 |                                                              |

| oit 5:                 | TXEN: Tra<br>1 = Transr<br>0 = Transr<br>SREN/CR                         | nit enable<br>nit disable                      | d<br>d           | in SYNC      | mode          |               |                 |                                                              |

| oit 4:                 | SYNC: US<br>(Synchror<br>1 = Synch<br>0 = Async                          | nous/Asyn<br>ronous m                          | chronous)<br>ode |              |               |               |                 |                                                              |

| oit 3-2:               | Unimplen                                                                 | nented: R                                      | ead as '0'       |              |               |               |                 |                                                              |

| oit 1:                 | <b>TRMT</b> : Tra<br>1 = TSR e<br>0 = TSR fi                             | mpty                                           | ft Register      | (TSR) E      | mpty bit      |               |                 |                                                              |

| oit 0:                 | TYQD: Oth                                                                | hit of tran                                    | emit data        | (can he i    | sed to calci  | ulated the    | parity in so    | ftware)                                                      |

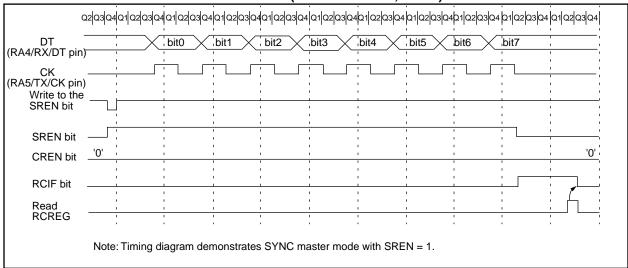

## 13.3.2 USART SYNCHRONOUS MASTER RECEPTION

Once synchronous mode is selected, reception is enabled by setting either the SREN (RCSTA<5>) bit or the CREN (RCSTA<4>) bit. Data is sampled on the RA4/RX/DT pin on the falling edge of the clock. If SREN is set, then only a single word is received. If CREN is set, the reception is continuous until CREN is reset. If both bits are set, then CREN takes precedence. After clocking the last bit, the received data in the Receive Shift Register (RSR) is transferred to RCREG (if it is empty). If the transfer is complete, the interrupt bit RCIF (PIR<0>) is set. The actual interrupt can be enabled/disabled by setting/clearing the RCIE (PIE<0>) bit. RCIF is a read only bit which is RESET by the hardware. In this case it is reset when RCREG has been read and is empty. RCREG is a double buffered register; i.e., it is a two deep FIFO. It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte to begin shifting into the RSR. On the clocking of the last bit of the third byte, if RCREG is still full, then the overrun error bit OERR (RCSTA<1>) is set. The word in the RSR will be lost. RCREG can be read twice to retrieve the two bytes in the FIFO. The OERR bit has to be cleared in software. This is done by clearing the CREN bit. If OERR bit is set, transfers from RSR to RCREG are inhibited, so it is essential to clear OERR bit if it is set. The 9th receive bit is buffered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with values for the next received data: therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old FERR and RX9D information.

Steps to follow when setting up a Synchronous Master Reception:

- Initialize the SPBRG register for the appropriate baud rate. See Section 13.1 for details.

- Enable the synchronous master serial port by setting bits SYNC, SPEN, and CSRC.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. If a single reception is required, set bit SREN. For continuous reception set bit CREN.

- The RCIF bit will be set when reception is complete and an interrupt will be generated if the RCIE bit was set.

- 7. Read RCSTA to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 8. Read the 8-bit received data by reading RCREG.

- If any error occurred, clear the error by clearing CREN.

Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

FIGURE 13-11: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

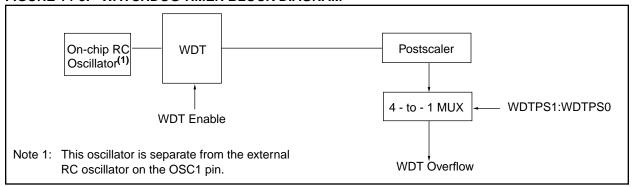

#### FIGURE 14-8: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 14-4: REGISTERS/BITS ASSOCIATED WITH THE WATCHDOG TIMER

| Address       | Name   | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all other resets (Note1) |

|---------------|--------|-------|-------|-------|--------|--------|--------|-------|-------|-------------------------------|-----------------------------------|

| _             | Config | _     | PM1   | _     | PM0    | WDTPS1 | WDTPS0 | FOSC1 | FOSC0 | (Note 2)                      | (Note 2)                          |

| 06h, Unbanked | CPUSTA | _     | -     | STKAV | GLINTD | TO     | PD     | _     |       | 11 11                         | 11 qq                             |

Legend: -= unimplemented read as '0', q - value depends on condition, shaded cells are not used by the WDT.

Note 1: Other (non power-up) resets include: external reset through  $\overline{\text{MCLR}}$  and Watchdog Timer Reset.

2: This value will be as the device was programmed, or if unprogrammed, will read as all '1's.

TABLE 15-2: PIC17CXX INSTRUCTION SET (Cont.'d)

| Mnemonic,  |        | Description                                   | Cycles |      | 16-bit | Opcod | е    | Status    | Notes |

|------------|--------|-----------------------------------------------|--------|------|--------|-------|------|-----------|-------|

| Operands   |        |                                               |        | MSb  |        |       | LSb  | Affected  |       |

| TABLWT     | t,i,f  | Table Write                                   | 2      | 1010 | 11ti   | ffff  | ffff | None      | 5     |

| TLRD       | t,f    | Table Latch Read                              | 1      | 1010 | 00tx   | ffff  | ffff | None      |       |

| TLWT       | t,f    | Table Latch Write                             | 1      | 1010 | 01tx   | ffff  | ffff | None      |       |

| TSTFSZ     | f      | Test f, skip if 0                             | 1 (2)  | 0011 | 0011   | ffff  | ffff | None      | 6,8   |

| XORWF      | f,d    | Exclusive OR WREG with f                      | 1      | 0000 | 110d   | ffff  | ffff | Z         |       |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS                         |        |      |        |       |      |           |       |

| BCF        | f,b    | Bit Clear f                                   | 1      | 1000 | 1bbb   | ffff  | ffff | None      |       |

| BSF        | f,b    | Bit Set f                                     | 1      | 1000 | 0bbb   | ffff  | ffff | None      |       |

| BTFSC      | f,b    | Bit test, skip if clear                       | 1 (2)  | 1001 | 1bbb   | ffff  | ffff | None      | 6,8   |

| BTFSS      | f,b    | Bit test, skip if set                         | 1 (2)  | 1001 | 0bbb   | ffff  | ffff | None      | 6,8   |

| BTG        | f,b    | Bit Toggle f                                  | 1      | 0011 | 1bbb   | ffff  | ffff | None      |       |

| LITERAL A  | ND CO  | NTROL OPERATIONS                              |        | •    |        |       |      |           |       |

| ADDLW      | k      | ADD literal to WREG                           | 1      | 1011 | 0001   | kkkk  | kkkk | OV,C,DC,Z |       |

| ANDLW      | k      | AND literal with WREG                         | 1      | 1011 | 0101   | kkkk  | kkkk | Z         |       |

| CALL       | k      | Subroutine Call                               | 2      | 111k | kkkk   | kkkk  | kkkk | None      | 7     |

| CLRWDT     | _      | Clear Watchdog Timer                          | 1      | 0000 | 0000   | 0000  | 0100 | TO,PD     |       |

| GOTO       | k      | Unconditional Branch                          | 2      | 110k | kkkk   | kkkk  | kkkk | None      | 7     |

| IORLW      | k      | Inclusive OR literal with WREG                | 1      | 1011 | 0011   | kkkk  | kkkk | Z         |       |

| LCALL      | k      | Long Call                                     | 2      | 1011 | 0111   | kkkk  | kkkk | None      | 4,7   |

| MOVLB      | k      | Move literal to low nibble in BSR             | 1      | 1011 | 1000   | uuuu  | kkkk | None      |       |

| MOVLR      | k      | Move literal to high nibble in BSR            | 1      | 1011 | 101x   | kkkk  | uuuu | None      | 9     |

| MOVLW      | k      | Move literal to WREG                          | 1      | 1011 | 0000   | kkkk  | kkkk | None      |       |

| MULLW      | k      | Multiply literal with WREG                    | 1      | 1011 | 1100   | kkkk  | kkkk | None      | 9     |

| RETFIE     | _      | Return from interrupt (and enable interrupts) | 2      | 0000 | 0000   | 0000  | 0101 | GLINTD    | 7     |

| RETLW      | k      | Return literal to WREG                        | 2      | 1011 | 0110   | kkkk  | kkkk | None      | 7     |

| RETURN     | _      | Return from subroutine                        | 2      | 0000 | 0000   | 0000  | 0010 | None      | 7     |

| SLEEP      | _      | Enter SLEEP Mode                              | 1      | 0000 | 0000   | 0000  | 0011 | TO, PD    |       |

| SUBLW      | k      | Subtract WREG from literal                    | 1      | 1011 | 0010   | kkkk  | kkkk | OV,C,DC,Z |       |

| XORLW      | k      | Exclusive OR literal with WREG                | 1      | 1011 | 0100   | kkkk  | kkkk | Z         |       |

|            |        |                                               |        | _    |        |       |      |           |       |

Legend: Refer to Table 15-1 for opcode field descriptions.

- Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

- 3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- 5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

CALLSubroutine CallSyntax:[label] CALL kOperands: $0 \le k \le 4095$ Operation: $PC+1 \rightarrow TOS, k \rightarrow PC<12:0>, k<12:8> \rightarrow PCLATH<4:0>; PC<15:13> \rightarrow PCLATH<7:5>$

Status Affected: None

Encoding: 111k kkkk kkkk kkkk

Description: Subroutine call within 8K page. First, return address (PC+1) is pushed onto the stack. The 13-bit value is loaded into PC bits<12:0>. Then the upper-eight bits of the PC are copied into PCLATH.

Call is a two-cycle instruction.

See LCALL for calls outside 8K memory appears

space.

Words: 1 Cycles: 2

Q Cycle Activity:

| Q1         | Q2                    | Q3      | Q4  |

|------------|-----------------------|---------|-----|

| Decode     | Read literal 'k'<7:0> | Execute | NOP |

| Forced NOP | NOP                   | Execute | NOP |

Example: HERE CALL THERE

Before Instruction

PC = Address(HERE)

After Instruction

PC = Address(THERE)

TOS = Address(HERE + 1)

| Syntax:    | [label] CLRF f,s                 |

|------------|----------------------------------|

| Operands:  | $0 \le f \le 255$                |

| Operation: | $00h \rightarrow f, s \in [0,1]$ |

Clear f

00h → dest

Status Affected: None

Encoding: 0010 100s fffff ffff

Description: Clears the contents of the specified register(s).

s = 0: Data memory location 'f' and

WREG are cleared.

s = 1: Data memory location 'f' is

cleared.

Words: 1

Cycles: 1

Q Cycle Activity:

**CLRF**

| Q1     | Q2                   | Q3      | Q4                                                          |

|--------|----------------------|---------|-------------------------------------------------------------|

| Decode | Read<br>register 'f' | Execute | Write<br>register 'f'<br>and other<br>specified<br>register |

Example: CLRF FLAG\_REG

Before Instruction

$FLAG_REG = 0x5A$

After Instruction

$FLAG_REG = 0x00$

| RLNCF       |          | Rota                     | te L            | eft f (no                                             | carı             | y)             |                     |

|-------------|----------|--------------------------|-----------------|-------------------------------------------------------|------------------|----------------|---------------------|

| Syntax:     |          | [ labe                   | e/]             | RLNCF                                                 | f,d              |                |                     |

| Operands:   |          | 0 ≤ f<br>d ∈ [           |                 | 55                                                    |                  |                |                     |

| Operation:  |          | f <n><br/>f&lt;7&gt;</n> |                 | <n+1>;<br/>&lt;0&gt;</n+1>                            |                  |                |                     |

| Status Affe | ected:   | None                     | )               |                                                       |                  |                |                     |

| Encoding:   |          | 0.0                      | 10              | 001d                                                  | ff               | ff             | ffff                |

| Description | n:       | one b<br>place           | it to<br>d in \ | nts of reg<br>the left. If<br>WREG. If<br>kk in regis | 'd' is<br>'d' is | 0 the<br>1 the | result is           |

|             |          |                          | •               | reg                                                   | ister            | f              | ]◀┐                 |

| Words:      |          | 1                        |                 |                                                       |                  |                |                     |

| Cycles:     |          | 1                        |                 |                                                       |                  |                |                     |

| Q Cycle A   | ctivity: |                          |                 |                                                       |                  |                |                     |

|             | 21       | Q2                       |                 | Q3                                                    |                  |                | Q4                  |

| Dec         | code     | Read<br>registe          | -               | Execu                                                 | te               |                | rite to<br>tination |

| Example:    |          | RLNC                     | F               | REC                                                   | 3, 1             |                |                     |

| Before      | e Instru | iction                   |                 |                                                       |                  |                |                     |

| C<br>R      | :<br>EG  | = 0<br>= 11              | 10 1            | .011                                                  |                  |                |                     |

|             | nstruct  | tion                     |                 |                                                       |                  |                |                     |

| C<br>R      | :<br>EG  | =<br>= 11                | 01 (            | )111                                                  |                  |                |                     |

| RRCF              | Rotate Right f through Carry                                                                                                                                                           |            |       |                      |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------|----------------------|--|

| Syntax:           | [ label ]                                                                                                                                                                              | RRCF       | f,d   |                      |  |

| Operands:         | $0 \le f \le 25$ $d \in [0,1]$                                                                                                                                                         | 55         |       |                      |  |

| Operation:        | $f$ < $n$ > $\rightarrow 0$ $f$ < $0$ > $\rightarrow 0$ $C$ $\rightarrow d$ < $7$                                                                                                      | <b>)</b> ; |       |                      |  |

| Status Affected:  | С                                                                                                                                                                                      |            |       |                      |  |

| Encoding:         | 0001                                                                                                                                                                                   | 100d       | fff   | f ffff               |  |

| Description:      | The contents of register 'f' are rotated one bit to the right through the Carry Flag. If 'd' is 0 the result is placed in WREG. If 'd' is 1 the result is placed back in register 'f'. |            |       |                      |  |

| Words:            | 1                                                                                                                                                                                      |            |       |                      |  |

| Cycles:           | 1                                                                                                                                                                                      |            |       |                      |  |

| Q Cycle Activity: |                                                                                                                                                                                        |            |       |                      |  |

| Q1                | Q2                                                                                                                                                                                     | Q3         |       | Q4                   |  |

| Decode            | Read<br>register 'f'                                                                                                                                                                   | Execu      | ıte   | Write to destination |  |

| Example:          | RRCF                                                                                                                                                                                   | 1          | REG1, | 0                    |  |

| Before Instru     | iction                                                                                                                                                                                 |            |       |                      |  |

| REG1<br>C         | = 1110<br>= 0                                                                                                                                                                          | 0110       |       |                      |  |

| After Instruction |                                                                                                                                                                                        |            |       |                      |  |

| REG1              | = 1110                                                                                                                                                                                 | 0110       |       |                      |  |

| WREG<br>C         |                                                                                                                                                                                        | 0011       |       |                      |  |

## PIC17C4X

Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44

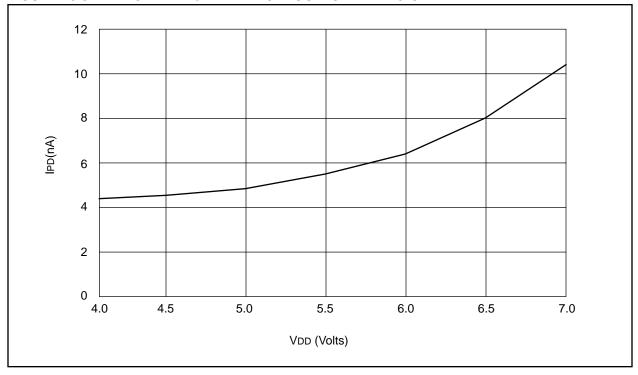

FIGURE 18-9: TYPICAL IPD vs. VDD WATCHDOG DISABLED 25°C

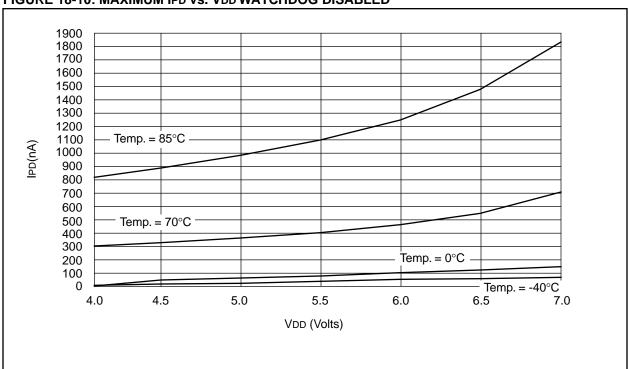

FIGURE 18-10: MAXIMUM IPD vs. VDD WATCHDOG DISABLED

Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44

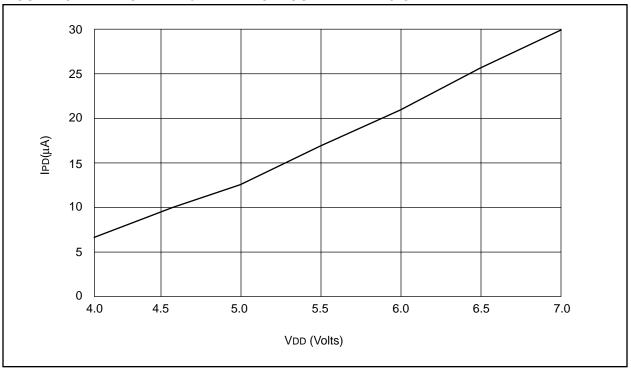

FIGURE 18-11: TYPICAL IPD vs. VDD WATCHDOG ENABLED 25°C

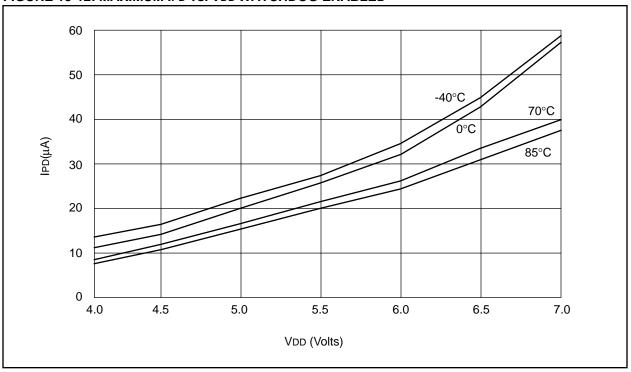

FIGURE 18-12: MAXIMUM IPD vs. VDD WATCHDOG ENABLED

Applicable Devices 42 R42 42A 43 R43 44

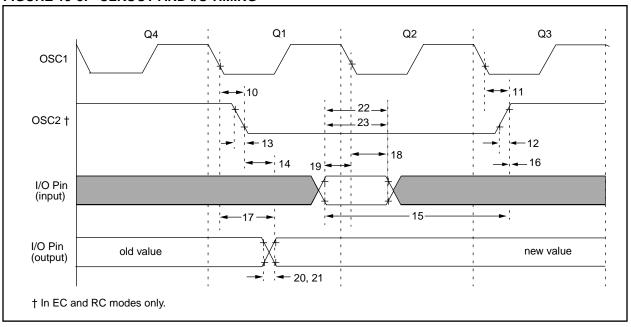

FIGURE 19-3: CLKOUT AND I/O TIMING

TABLE 19-3: CLKOUT AND I/O TIMING REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                            |                              | Min            | Тур† | Max           | Units | Conditions |

|------------------|----------|-----------------------------------------------------------|------------------------------|----------------|------|---------------|-------|------------|

| 10               | TosH2ckL | OSC1↓ to CLKOUT↓                                          |                              | _              | 15 ‡ | 30 ‡          | ns    | Note 1     |

| 11               | TosH2ckH | OSC1↓ to CLKOUT↑                                          |                              | _              | 15 ‡ | 30 ‡          | ns    | Note 1     |

| 12               | TckR     | CLKOUT rise time                                          |                              | _              | 5‡   | 15 ‡          | ns    | Note 1     |

| 13               | TckF     | CLKOUT fall time                                          |                              | _              | 5‡   | 15 ‡          | ns    | Note 1     |

| 14               | TckH2ioV | CLKOUT ↑ to Port out valid                                | PIC17CR42/42A/43/<br>R43/44  | _              | _    | 0.5Tcy + 20 ‡ | ns    | Note 1     |

|                  |          |                                                           | PIC17LCR42/42A/43/<br>R43/44 | _              | _    | 0.5Tcy + 50 ‡ | ns    | Note 1     |

| 15               | TioV2ckH | Port in valid before CLKOUT↑                              | PIC17CR42/42A/43/<br>R43/44  | 0.25Tcy + 25 ‡ | _    | _             | ns    | Note 1     |

|                  |          |                                                           | PIC17LCR42/42A/43/<br>R43/44 | 0.25Tcy + 50 ‡ | _    | _             | ns    | Note 1     |

| 16               | TckH2iol | Port in hold after CL                                     | KOUT <sup>↑</sup>            | 0 ‡            | _    | _             | ns    | Note 1     |

| 17               | TosH2ioV | OSC1↓ (Q1 cycle) t                                        | o Port out valid             | _              | _    | 100 ‡         | ns    |            |

| 18               | TosH2iol | OSC1↓ (Q2 cycle) to Port input invalid (I/O in hold time) |                              | 0 ‡            | _    | _             | ns    |            |

| 19               | TioV2osH | Port input valid to OSC1↓ (I/O in setup time)             |                              | 30 ‡           | _    | _             | ns    |            |

| 20               | TioR     | Port output rise time                                     |                              | _              | 10 ‡ | 35 ‡          | ns    |            |

| 21               | TioF     | Port output fall time                                     |                              | _              | 10 ‡ | 35 ‡          | ns    |            |

| 22               | TinHL    | INT pin high or low time                                  |                              | 25 *           | _    | _             | ns    |            |

| 23               | TrbHL    | RB7:RB0 change IN                                         | NT high or low time          | 25 *           | _    | _             | ns    |            |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Measurements are taken in EC Mode where CLKOUT output is 4 x Tosc.

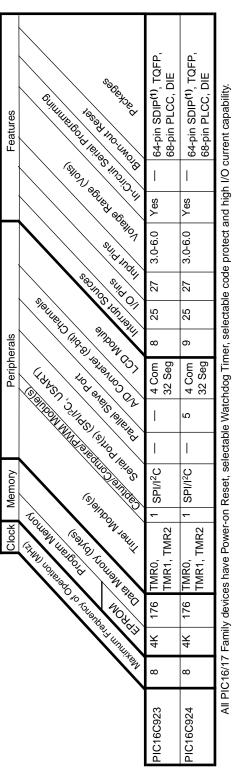

#### E.7 PIC16C9XX Family Of Devices

All PIC16CXX Family devices use serial programming with clock pin RB6 and data pin RB7. Please contact your local Microchip representative for availability of this package. Note

## PIC17C4X

| Delay From External Clock Edge68           | FOSC199                                                             |

|--------------------------------------------|---------------------------------------------------------------------|

| Development Support143                     | FS0                                                                 |

| Development Tools143                       | FS1                                                                 |

| Device Drawings                            | FS2                                                                 |

| 44-Lead Plastic Surface Mount (MQFP        | FS3                                                                 |

| 10x10 mm Body 1.6/0.15 mm Lead Form)209    | FSR0                                                                |

| DIGIT BORROW9                              | FSR1 34, 40                                                         |

| Digit Carry (DC)9                          | Fuzzy Logic Dev. System (fuzzyTECH®-MP) 143, 145                    |

| Duty Cycle75                               |                                                                     |

|                                            | G                                                                   |

| E                                          |                                                                     |

| Floatrical Characteristics                 | General Format for Instructions                                     |

| Electrical Characteristics                 | General Purpose RAM                                                 |

| PIC17C42                                   | General Purpose RAM Bank                                            |

| Absolute Maximum Ratings147                | General Purpose Register (GPR)                                      |

| Capture Timing                             | GLINTD                                                              |

| CLKOUT and I/O Timing156                   | GOTO                                                                |

| DC Characteristics                         | GPR (General Purpose Register)                                      |

| External Clock Timing                      | Graphs 170, 200                                                     |

| Memory Interface Read Timing               | IOH vs. VOH, VDD = 3V                                               |

| Memory Interface Write Timing              | IOH vs. VOH, VDD = 5V                                               |

| PWM Timing                                 | IOL vs. VOL, VDD = 3V                                               |

| RESET, Watchdog Timer, Oscillator Start-up | ,                                                                   |

| Timer and Power-up Timer                   | Maximum IDD vs. Frequency (External Cleak 135°C to 10°C)  167, 10°C |

| Timer0 Clock Timings                       | (External Clock 125°C to -40°C)                                     |

| Timer1, Timer2 and Timer3 Clock Timing 158 | Maximum IPD vs. VDD Watchdog Disabled 168, 198                      |

| USART Module, Synchronous Receive          | Maximum IPD vs. VDD Watchdog Enabled 169, 199                       |

| PIC17C43/44                                | RC Oscillator Frequency vs.  VDD (Cext = 100 pF)164, 194            |

|                                            |                                                                     |

| Absolute Maximum Ratings                   | RC Oscillator Frequency vs.  VDD (Cext = 22 pF)164, 194             |

| Capture Timing188 CLKOUT and I/O Timing185 | RC Oscillator Frequency vs.                                         |

| DC Characteristics177                      | VDD (Cext = 300 pF)                                                 |

| External Clock Timing                      | Transconductance of LF Oscillator vs.VDD 166, 196                   |

| Memory Interface Read Timing191            | Transconductance of XT Oscillator vs. VDD 166, 196                  |

| Memory Interface Write Timing190           | Typical IDD vs. Frequency                                           |

| Parameter Measurement Information183       | (External Clock 25°C)                                               |

| RESET, Watchdog Timer, Oscillator Start-up | Typical IPD vs. VDD Watchdog Disabled 25°C . 168, 198               |

| Timer and Power-up Timer Timing186         | Typical IPD vs. VDD Watchdog Enabled 25°C 169, 199                  |

| Timer Clock Timing187                      | Typical RC Oscillator vs. Temperature 163, 193                      |

| Timer1, Timer2 and Timer3 Clock Timing 187 | VTH (Input Threshold Voltage) of I/O Pins vs.                       |

| Timing Parameter Symbology182              | VDD                                                                 |

| USART Module Synchronous Receive           | VTH (Input Threshold Voltage) of OSC1 Input                         |

| Timing189                                  | (In XT, HS, and LP Modes) vs. VDD173, 203                           |

| USART Module Synchronous Transmission      | VTH, VIL of MCLR, TOCKI and OSC1                                    |

| Timing189                                  | (In RC Mode) vs. VDD                                                |

| EPROM Memory Access Time Order Suffix31    | WDT Timer Time-Out Period vs. VDD 170, 200                          |

| Extended Microcontroller                   | ., .,                                                               |

| Extended Microcontroller Mode31            |                                                                     |

| External Memory Interface31                | Н                                                                   |

| External Program Memory Waveforms31        | Hardware Multiplier49                                               |

| _                                          | Hardware Multiplier48                                               |

| F                                          | 1                                                                   |

| Family of Devices6                         |                                                                     |

| PIC14000                                   | I/O Ports                                                           |

| PIC16C5X                                   | Bi-directional64                                                    |

| PIC16CXXX                                  | I/O Ports53                                                         |

| PIC16C6X                                   | Programming Considerations64                                        |

| PIC16C7X217                                | Read-Modify-Write Instructions64                                    |

| PIC16C8X                                   | Successive Operations64                                             |

| PIC16C9XX                                  | INCF                                                                |

| PIC17CXX                                   | INCFSNZ                                                             |

| FERR84, 91                                 | INCFSZ                                                              |

| FOSC099                                    | INDF0                                                               |

|                                            | INDF1 34, 40                                                        |

| Receive Status and Control Register83     | SWAPF                           | 137    |

|-------------------------------------------|---------------------------------|--------|

| Register File Map33                       | SYNC                            | 83     |

| Registers                                 | Synchronous Master Mode         | 93     |

| ALUSTA27, 36                              | Synchronous Master Reception    | 95     |

| BRG86                                     | Synchronous Master Transmission | 93     |

| BSR27                                     | Synchronous Slave Mode          | 97     |

| CPUSTA37                                  | •                               |        |

| File Map                                  | <b>-</b>                        |        |

| FSR040                                    | Т                               |        |

| FSR140                                    |                                 |        |

| INDF040                                   | T0CKI Pin                       |        |

| INDF140                                   | TOCKIE                          |        |

| INTSTA                                    | T0CKIF                          |        |

| PIE                                       | T0CS                            | 38, 67 |

| PIR                                       | T0IE                            | 22     |

| RCSTA84                                   | T0IF                            | 22     |

| Special Function Table34                  | T0SE                            | 38, 67 |

| TOSTA                                     | T0STA                           | 34, 38 |

| TCON1                                     | T16                             | 71     |

| TCON2                                     | Table Latch                     | 40     |

|                                           | Table Pointer                   | 40     |

| TMR181                                    | Table Read                      |        |

| TMR281                                    | Example                         | 48     |

| TMR381                                    | Section                         |        |

| TXSTA83                                   | Table Reads Section             |        |

| WREG27                                    |                                 |        |

| Reset                                     | TABLRD Operation                |        |

| Section15                                 | Timing                          |        |

| Status Bits and Their Significance        | TLRD                            |        |

| Time-Out in Various Situations            | TLRD Operation                  | 44     |

| Time-Out Sequence                         | Table Write                     |        |

| RETFIE                                    | Code                            | 46     |

|                                           | Interaction                     | 45     |

| RETLW                                     | Section                         |        |

| RETURN                                    | TABLWT Operation                |        |

| RLCF                                      | Terminating Long Writes         |        |

| RLNCF                                     | Timing                          |        |

| RRCF                                      | TLWT Operation                  |        |

| RRNCF                                     | To External Memory              |        |

| RX Pin Sampling Scheme91                  |                                 |        |

| RX984                                     | To Internal Memory              |        |

| RX9D84                                    | TABLRD                          |        |

|                                           | TABLWT                          |        |

|                                           | TBLATH                          | 40     |

| S                                         | TBLATL                          | 40     |

|                                           | TBLPTRH                         | 34, 40 |

| Sampling91                                | TBLPTRL                         | 34, 40 |

| Saving STATUS and WREG in RAM27           | TCLK12                          | 71     |

| SETF                                      | TCLK3                           | 71     |

| SFR                                       | TCON1                           |        |

| SFR (Special Function Registers)          | TCON2                           | ,      |

| SFR As Source/Destination                 | Terminating Long Writes         | •      |

| Signed Math 9                             | Time-Out Sequence               |        |

| <u> </u>                                  | Timer Resources                 |        |

| SLEEP                                     |                                 |        |

| Software Simulator (MPSIM)145             | Timer0                          | b/     |

| SPBRG                                     | Timer1                          | _      |

| Special Features of the CPU99             | 16-bit Mode                     |        |

| Special Function Registers29, 32, 34, 108 | Clock Source Select             |        |

| SPEN                                      | On bit                          | 72     |

| SREN84                                    | Section                         | 71, 73 |

| Stack                                     | Timer2                          |        |

| Operation                                 | 16-bit Mode                     | 74     |

| Pointer                                   | Clock Source Select             |        |

| Stack                                     | On bit                          |        |

| STKAL 39                                  | Section                         |        |

| STKAV                                     | Timer3                          | 1, 1   |

| SUBLW                                     | Clock Source Select             | 7/     |

|                                           |                                 |        |

| SUBWF                                     | On bit                          |        |

| SUBWFB 136                                | Section                         | 71. 77 |

### WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

#### **Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: 480-792-7627 Web Address: http://www.microchip.com

#### **Rocky Mountain**

2355 West Chandler Blvd. Chandler, AZ 85224-6199

Tel: 480-792-7966 Fax: 480-792-7456

#### Atlanta

500 Sugar Mill Road, Suite 200B Atlanta, GA 30350

Tel: 770-640-0034 Fax: 770-640-0307

#### **Boston**

2 Lan Drive, Suite 120 Westford, MA 01886 Tel: 978-692-3848 Fax: 978-692-3821

#### Chicago

333 Pierce Road, Suite 180 Itasca, IL 60143

Tel: 630-285-0071 Fax: 630-285-0075

#### **Dallas**

4570 Westgrove Drive, Suite 160 Addison, TX 75001 Tel: 972-818-7423 Fax: 972-818-2924

#### Detroit

Tri-Atria Office Building 32255 Northwestern Highway, Suite 190 Farmington Hills, MI 48334 Tel: 248-538-2250 Fax: 248-538-2260

#### Kokomo

2767 S. Albright Road Kokomo, Indiana 46902 Tel: 765-864-8360 Fax: 765-864-8387

#### Los Angeles

18201 Von Karman, Suite 1090 Irvine, CA 92612

Tel: 949-263-1888 Fax: 949-263-1338

#### **New York**

150 Motor Parkway, Suite 202 Hauppauge, NY 11788 Tel: 631-273-5305 Fax: 631-273-5335

#### San Jose

Microchip Technology Inc. 2107 North First Street, Suite 590 San Jose, CA 95131 Tel: 408-436-7950 Fax: 408-436-7955

#### Toronto

6285 Northam Drive, Suite 108 Mississauga, Ontario L4V 1X5, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

#### Australia

Microchip Technology Australia Pty Ltd Suite 22, 41 Rawson Street Epping 2121, NSW Australia

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

#### China - Beijing Microchip Technology Consulting (Shanghai)

Co., Ltd., Beijing Liaison Office Unit 915 Bei Hai Wan Tai Bldg.

No. 6 Chaoyangmen Beidajie Beijing, 100027, No. China Tel: 86-10-85282100 Fax: 86-10-85282104

#### China - Chengdu

Microchip Technology Consulting (Shanghai)

Co., Ltd., Chengdu Liaison Office

Rm. 2401, 24th Floor, Ming Xing Financial Tower No. 88 TIDU Street Chengdu 610016, China Tel: 86-28-6766200 Fax: 86-28-6766599

#### China - Fuzhou

Microchip Technology Consulting (Shanghai) Co., Ltd., Fuzhou Liaison Office Unit 28F, World Trade Plaza No. 71 Wusi Road Fuzhou 350001, China Tel: 86-591-7503506 Fax: 86-591-7503521

#### China - Shanghai

Microchip Technology Consulting (Shanghai) Co., Ltd.

Room 701, Bldg. B Far East International Plaza No. 317 Xian Xia Road Shanghai, 200051

Tel: 86-21-6275-5700 Fax: 86-21-6275-5060

#### China - Shenzhen

Microchip Technology Consulting (Shanghai) Co., Ltd., Shenzhen Liaison Office Rm. 1315, 13/F, Shenzhen Kerry Centre, Renminnan Lu Shenzhen 518001, China Tel: 86-755-2350361 Fax: 86-755-2366086

#### **Hong Kong**

Microchip Technology Hongkong Ltd. Unit 901-6, Tower 2, Metroplaza 223 Hing Fong Road Kwai Fong, N.T., Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

#### India

Microchip Technology Inc. India Liaison Office Divvasree Chambers 1 Floor, Wing A (A3/A4) No. 11, O'Shaugnessey Road Bangalore, 560 025, India Tel: 91-80-2290061 Fax: 91-80-2290062

#### Japan

Microchip Technology Japan K.K. Benex S-1 6F 3-18-20, Shinyokohama Kohoku-Ku, Yokohama-shi Kanagawa, 222-0033, Japan

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

#### Korea

Microchip Technology Korea 168-1, Youngbo Bldg. 3 Floor Samsung-Dong, Kangnam-Ku Seoul, Korea 135-882

Tel: 82-2-554-7200 Fax: 82-2-558-5934

#### Singapore

Microchip Technology Singapore Pte Ltd. 200 Middle Road #07-02 Prime Centre Singapore, 188980

Tel: 65-334-8870 Fax: 65-334-8850

#### Taiwan

Microchip Technology Taiwan 11F-3, No. 207 Tung Hua North Road Taipei, 105, Taiwan Tel: 886-2-2717-7175 Fax: 886-2-2545-0139

#### **EUROPE**

#### Denmark

Microchip Technology Nordic ApS Regus Business Centre Lautrup hoj 1-3 Ballerup DK-2750 Denmark Tel: 45 4420 9895 Fax: 45 4420 9910

#### France

Microchip Technology SARL Parc d'Activite du Moulin de Massy 43 Rue du Saule Trapu Batiment A - Ier Etage 91300 Massy, France Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany** Microchip Technology GmbH Gustav-Heinemann Ring 125 D-81739 Munich, Germany Tel: 49-89-627-144 0 Fax: 49-89-627-144-44

#### Italy

Microchip Technology SRL Centro Direzionale Colleoni Palazzo Taurus 1 V. Le Colleoni 1 20041 Agrate Brianza Milan, Italy Tel: 39-039-65791-1 Fax: 39-039-6899883

#### **United Kingdom**

Arizona Microchip Technology Ltd. 505 Eskdale Road Winnersh Triangle Wokingham Berkshire, England RG41 5TU Tel: 44 118 921 5869 Fax: 44-118 921-5820

01/18/02