Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Detailo                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                    |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 8MHz                                                                        |

| Connectivity               | UART/USART                                                                  |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 33                                                                          |

| Program Memory Size        | 4KB (2K x 16)                                                               |

| Program Memory Type        | OTP                                                                         |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 232 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                   |

| Data Converters            | -                                                                           |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 44-LCC (J-Lead)                                                             |

| Supplier Device Package    | 44-PLCC (16.59x16.59)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc42at-08i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

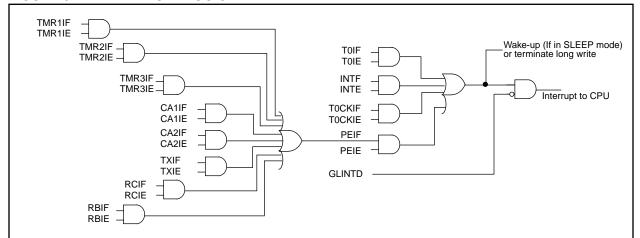

## 5.0 INTERRUPTS

The PIC17C4X devices have 11 sources of interrupt:

- External interrupt from the RA0/INT pin

- Change on RB7:RB0 pins

- TMR0 Overflow

- TMR1 Overflow

- TMR2 Overflow

- TMR3 Overflow

- USART Transmit buffer empty

- USART Receive buffer full

- Capture1

- Capture2

- T0CKI edge occurred

There are four registers used in the control and status of interrupts. These are:

- CPUSTA

- INTSTA

- PIE

- PIR

The CPUSTA register contains the GLINTD bit. This is the Global Interrupt Disable bit. When this bit is set, all interrupts are disabled. This bit is part of the controller core functionality and is described in the Memory Organization section. When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts which have the same vector address). These sources are:

- External interrupt from the RA0/INT pin

- TMR0 Overflow

- T0CKI edge occurred

- Any peripheral interrupt

When program execution vectors to one of these interrupt vector addresses (except for the peripheral interrupt address), the interrupt flag bit is automatically cleared. Vectoring to the peripheral interrupt vector address does not automatically clear the source of the interrupt. In the peripheral interrupt service routine, the source(s) of the interrupt can be determined by testing the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

All of the individual interrupt flag bits will be set regardless of the status of their corresponding mask bit or the GLINTD bit.

For external interrupt events, there will be an interrupt latency. For two cycle instructions, the latency could be one instruction cycle longer.

The "return from interrupt" instruction, RETFIE, can be used to mark the end of the interrupt service routine. When this instruction is executed, the stack is "POPed", and the GLINTD bit is cleared (to re-enable interrupts).

## FIGURE 5-1: INTERRUPT LOGIC

© 1996 Microchip Technology Inc.

#### 5.3 <u>Peripheral Interrupt Request Register</u> (PIR)

This register contains the individual flag bits for the peripheral interrupts.

**Note:** These bits will be set by the specified condition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the interrupt flag to ensure that the program does not immediately branch to the peripheral interrupt service routine.

## FIGURE 5-4: PIR REGISTER (ADDRESS: 16h, BANK 1)

|        | 0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 R-0                                                                                                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBIF   |                                                                                                                                                                                                                                                                              |

| bit7   | bit0 W = Writable bit<br>-n = Value at POR reset                                                                                                                                                                                                                             |

| bit 7: | <b>RBIF</b> : PORTB Interrupt on Change Flag bit<br>1 = One of the PORTB inputs changed (Software must end the mismatch condition)<br>0 = None of the PORTB inputs have changed                                                                                              |

| bit 6: | TMR3IF: Timer3 Interrupt Flag bit<br>If Capture1 is enabled (CA1/PR3 = 1)<br>1 = Timer3 overflowed<br>0 = Timer3 did not overflow                                                                                                                                            |

|        | If Capture1 is disabled (CA1/ $\overline{PR3}$ = 0)<br>1 = Timer3 value has rolled over to 0000h from equalling the period register (PR3H:PR3L) value<br>0 = Timer3 value has not rolled over to 0000h from equalling the period register (PR3H:PR3L) value                  |

| bit 5: | <b>TMR2IF</b> : Timer2 Interrupt Flag bit<br>1 = Timer2 value has rolled over to 0000h from equalling the period register (PR2) value<br>0 = Timer2 value has not rolled over to 0000h from equalling the period register (PR2) value                                        |

| bit 4: | <b>TMR1IF</b> : Timer1 Interrupt Flag bit<br>If Timer1 is in 8-bit mode (T16 = 0)<br>1 = Timer1 value has rolled over to 0000h from equalling the period register (PR) value<br>0 = Timer1 value has not rolled over to 0000h from equalling the period register (PR2) value |

|        | If Timer1 is in 16-bit mode (T16 = 1)<br>1 = TMR1:TMR2 value has rolled over to 0000h from equalling the period register (PR1:PR2) value<br>0 = TMR1:TMR2 value has not rolled over to 0000h from equalling the period register (PR1:PR2) value                              |

| bit 3: | <b>CA2IF</b> : Capture2 Interrupt Flag bit<br>1 = Capture event occurred on RB1/CAP2 pin<br>0 = Capture event did not occur on RB1/CAP2 pin                                                                                                                                  |

| bit 2: | <b>CA1IF</b> : Capture1 Interrupt Flag bit<br>1 = Capture event occurred on RB0/CAP1 pin<br>0 = Capture event did not occur on RB0/CAP1 pin                                                                                                                                  |

| bit 1: | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = Transmit buffer is empty<br>0 = Transmit buffer is full                                                                                                                                                               |

| bit 0: | RCIF: USART Receive Interrupt Flag bit<br>1 = Receive buffer is full<br>0 = Receive buffer is empty                                                                                                                                                                          |

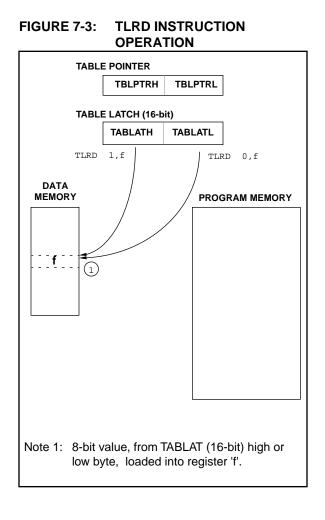

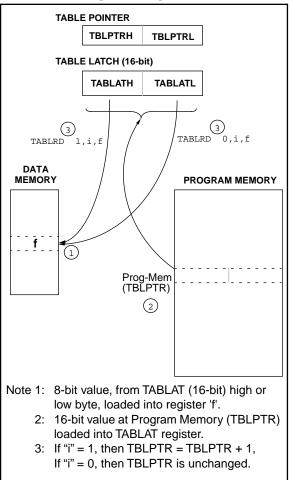

#### FIGURE 7-4: TABLRD INSTRUCTION OPERATION

## 9.0 I/O PORTS

The PIC17C4X devices have five I/O ports, PORTA through PORTE. PORTB through PORTE have a corresponding Data Direction Register (DDR), which is used to configure the port pins as inputs or outputs. These five ports are made up of 33 I/O pins. Some of these ports pins are multiplexed with alternate functions.

PORTC, PORTD, and PORTE are multiplexed with the system bus. These pins are configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, these pins are general purpose I/O.

PORTA and PORTB are multiplexed with the peripheral features of the device. These peripheral features are:

- Timer modules

- Capture module

- PWM module

- USART/SCI module

- External Interrupt pin

When some of these peripheral modules are turned on, the port pin will automatically configure to the alternate function. The modules that do this are:

- PWM module

- USART/SCI module

When a pin is automatically configured as an output by a peripheral module, the pins data direction (DDR) bit is unknown. After disabling the peripheral module, the user should re-initialize the DDR bit to the desired configuration.

The other peripheral modules (which require an input) must have their data direction bit configured appropriately.

**Note:** A pin that is a peripheral input, can be configured as an output (DDRx<y> is cleared). The peripheral events will be determined by the action output on the port pin.

## 9.1 PORTA Register

PORTA is a 6-bit wide latch. PORTA does not have a corresponding Data Direction Register (DDR).

Reading PORTA reads the status of the pins.

The RA1 pin is multiplexed with TMR0 clock input, and RA4 and RA5 are multiplexed with the USART functions. The control of RA4 and RA5 as outputs is automatically configured by the USART module.

9.1.1 USING RA2, RA3 AS OUTPUTS

The RA2 and RA3 pins are open drain outputs. To use the RA2 or the RA3 pin(s) as output(s), simply write to the PORTA register the desired value. A '0' will cause the pin to drive low, while a '1' will cause the pin to float (hi-impedance). An external pull-up resistor should be used to pull the pin high. Writes to PORTA will not affect the other pins.

| Note: | When using the RA2 or RA3 pin(s) as out-<br>put(s), read-modify-write instructions (such<br>as BCF, BSF, BTG) on PORTA are not rec-<br>ommended.<br>Such operations read the port pins, do the<br>desired operation, and then write this value<br>to the data latch. This may inadvertently<br>cause the RA2 or RA3 pins to switch from<br>input to output (or vice-versa).<br>It is recommended to use a shadow regis-<br>ter for PORTA. Do the bit operations on this<br>shadow register and then move it to<br>PORTA. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

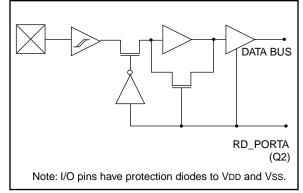

#### FIGURE 9-1: RA0 AND RA1 BLOCK DIAGRAM

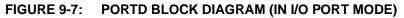

## 9.4 PORTD and DDRD Registers

PORTD is an 8-bit bi-directional port. The corresponding data direction register is DDRD. A '1' in DDRD configures the corresponding port pin as an input. A '0' in the DDRC register configures the corresponding port pin as an output. Reading PORTD reads the status of the pins, whereas writing to it will write to the port latch. PORTD is multiplexed with the system bus. When operating as the system bus, PORTD is the high order byte of the address/data bus (AD15:AD8). The timing for the system bus is shown in the Electrical Characteristics section.

**Note:** This port is configured as the system bus when the device's configuration bits are selected to Microprocessor or Extended Microcontroller modes. In the two other microcontroller modes, this port is a general purpose I/O. Example 9-3 shows the instruction sequence to initialize PORTD. The Bank Select Register (BSR) must be selected to Bank 1 for the port to be initialized.

#### EXAMPLE 9-3: INITIALIZING PORTD

| MOVLB | 1     | ; | Select Bank 1            |

|-------|-------|---|--------------------------|

| CLRF  | PORTD | ; | Initialize PORTD data    |

|       |       | ; | latches before setting   |

|       |       | ; | the data direction       |

|       |       | ; | register                 |

| MOVLW | 0xCF  | ; | Value used to initialize |

|       |       | ; | data direction           |

| MOVWF | DDRD  | ; | Set RD<3:0> as inputs    |

|       |       | ; | RD<5:4> as outputs       |

|       |       | ; | RD<7:6> as inputs        |

|       |       |   |                          |

## 12.0 TIMER1, TIMER2, TIMER3, PWMS AND CAPTURES

The PIC17C4X has a wealth of timers and time-based functions to ease the implementation of control applications. These time-base functions include two PWM outputs and two Capture inputs.

Timer1 and Timer2 are two 8-bit incrementing timers, each with a period register (PR1 and PR2 respectively) and separate overflow interrupt flags. Timer1 and Timer2 can operate either as timers (increment on internal Fosc/4 clock) or as counters (increment on falling edge of external clock on pin RB4/TCLK12). They are also software configurable to operate as a single 16-bit timer. These timers are also used as the time-base for the PWM (pulse width modulation) module. Timer3 is a 16-bit timer/counter consisting of the TMR3H and TMR3L registers. This timer has four other associated registers. Two registers are used as a 16-bit period register or a 16-bit Capture1 register (PR3H/CA1H:PR3L/CA1L). The other two registers are strictly the Capture2 registers (CA2H:CA2L). Timer3 is the time-base for the two 16-bit captures.

TMR3 can be software configured to increment from the internal system clock or from an external signal on the RB5/TCLK3 pin.

Figure 12-1 and Figure 12-2 are the control registers for the operation of Timer1, Timer2, and Timer3, as well as PWM1, PWM2, Capture1, and Capture2.

## FIGURE 12-1: TCON1 REGISTER (ADDRESS: 16h, BANK 3)

| bit7     | I CA2ED0 CA1ED1 CA1ED0 T16 TMR3CS TMR2CS TMR1CS bit0                                                                                                                                                           | R = Readable bit<br>W = Writable bit<br>-n = Value at POR reset |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| bit 7-6: | <b>CA2ED1:CA2ED0</b> : Capture2 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 5-4: | <b>CA1ED1:CA1ED0</b> : Capture1 Mode Select bits<br>00 = Capture on every falling edge<br>01 = Capture on every rising edge<br>10 = Capture on every 4th rising edge<br>11 = Capture on every 16th rising edge |                                                                 |

| bit 3:   | <b>T16</b> : Timer1:Timer2 Mode Select bit<br>1 = Timer1 and Timer2 form a 16-bit timer<br>0 = Timer1 and Timer2 are two 8-bit timers                                                                          |                                                                 |

| bit 2:   | <b>TMR3CS</b> : Timer3 Clock Source Select bit<br>1 = TMR3 increments off the falling edge of the RB5/TCLK3 pin<br>0 = TMR3 increments off the internal clock                                                  |                                                                 |

| bit 1:   | <b>TMR2CS</b> : Timer2 Clock Source Select bit<br>1 = TMR2 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR2 increments off the internal clock                                                 |                                                                 |

| bit 0:   | <b>TMR1CS</b> : Timer1 Clock Source Select bit<br>1 = TMR1 increments off the falling edge of the RB4/TCLK12 pin<br>0 = TMR1 increments off the internal clock                                                 |                                                                 |

## 13.0 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER TRANSMITTER (USART) MODULE

The USART module is a serial I/O module. The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

The SPEN (RCSTA<7>) bit has to be set in order to configure RA4 and RA5 as the Serial Communication Interface.

The USART module will control the direction of the RA4/RX/DT and RA5/TX/CK pins, depending on the states of the USART configuration bits in the RCSTA and TXSTA registers. The bits that control I/O direction are:

- SPEN

- TXEN

- SREN

- CREN

- CSRC

The Transmit Status And Control Register is shown in Figure 13-1, while the Receive Status And Control Register is shown in Figure 13-2.

| <b>D</b> 4 4 4  |                                                                                  |                                                 |                  |             |                       | <b>D</b> (           | <b>D</b> 4 4 4  |                                                      |

|-----------------|----------------------------------------------------------------------------------|-------------------------------------------------|------------------|-------------|-----------------------|----------------------|-----------------|------------------------------------------------------|

| R/W - 0<br>CSRC | R/W - 0<br>TX9                                                                   | R/W - 0<br>TXEN                                 | R/W - 0<br>SYNC  | <u>U-0</u>  | <u>U-0</u>            | <u>R - 1</u><br>TRMT | R/W - x<br>TX9D | R = Readable bit                                     |

| bit7            | 17.9                                                                             | TALM                                            | 51110            |             |                       |                      | bit0            | W = Writable bit-n = Value at POR reset(x = unknown) |

| bit 7:          | <b>CSRC</b> : C<br>Synchron<br>1 = Maste<br>0 = Slave<br>Asynchron<br>Don't care | ous mode<br>r Mode (C<br>mode (Clo<br>nous mode | lock gene        | rated inter | mally from I<br>urce) | BRG)                 |                 |                                                      |

| bit 6:          | <b>TX9</b> : 9-bit<br>1 = Select<br>0 = Select                                   | s 9-bit tra                                     | nsmission        |             |                       |                      |                 |                                                      |

| bit 5:          | <b>TXEN</b> : Tra<br>1 = Transr<br>0 = Transr<br>SREN/CR                         | nit enable<br>nit disable                       | d<br>ed          | in SYNC     | mode                  |                      |                 |                                                      |

| bit 4:          | SYNC: US<br>(Synchror<br>1 = Synch<br>0 = Async                                  | nous/Asyn<br>Ironous m                          | chronous)<br>ode |             |                       |                      |                 |                                                      |

| bit 3-2:        | Unimpler                                                                         | nented: R                                       | ead as '0'       |             |                       |                      |                 |                                                      |

| bit 1:          | <b>TRMT</b> : Tra<br>1 = TSR e<br>0 = TSR fr                                     | empty                                           | ft Registe       | r (TSR) Er  | npty bit              |                      |                 |                                                      |

| bit 0:          | <b>TX9D</b> : 9th                                                                | bit of trar                                     | emit data        | (can be u   | and to only           | مطلا امملمان         | nority in on    | ft                                                   |

## FIGURE 13-1: TXSTA REGISTER (ADDRESS: 15h, BANK 0)

© 1996 Microchip Technology Inc.

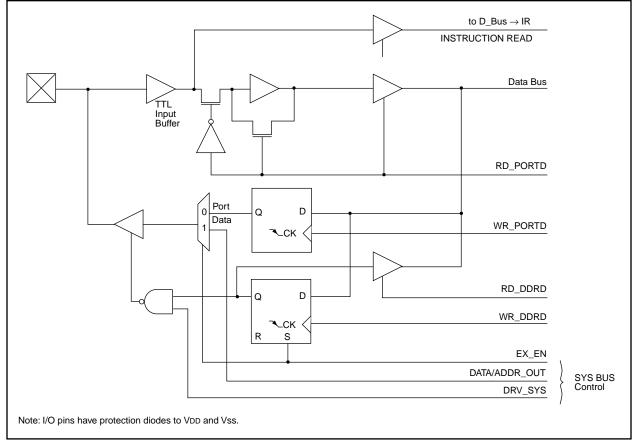

Steps to follow when setting up an Asynchronous Reception:

- 1. Initialize the SPBRG register for the appropriate baud rate.

- 2. Enable the asynchronous serial port by clearing the SYNC bit and setting the SPEN bit.

- 3. If interrupts are desired, then set the RCIE bit.

- 4. If 9-bit reception is desired, then set the RX9 bit.

- 5. Enable the reception by setting the CREN bit.

- 6. The RCIF bit will be set when reception completes and an interrupt will be generated if the RCIE bit was set.

- Read RCSTA to get the ninth bit (if enabled) and FERR bit to determine if any error occurred during reception.

- 8. Read RCREG for the 8-bit received data.

- 9. If an overrun error occurred, clear the error by clearing the OERR bit.

- Note: To terminate a reception, either clear the SREN and CREN bits, or the SPEN bit. This will reset the receive logic, so that it will be in the proper state when receive is re-enabled.

## FIGURE 13-8: ASYNCHRONOUS RECEPTION

| <b>TABLE 13-6</b> : | <b>REGISTERS ASSOCIATED WITH ASYNCHRONOUS RECEPTION</b> |

|---------------------|---------------------------------------------------------|

|                     |                                                         |

| Address                                        | Name  | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|------------------------------------------------|-------|-------|--------|--------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1                                    | PIR   | RBIF  | TMR3IF | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0                                    | RCSTA | SPEN  | RX9    | SREN   | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0                                    | RCREG | RX7   | RX6    | RX5    | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1                                    | PIE   | RBIE  | TMR3IE | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0                                    | TXSTA | CSRC  | TX9    | TXEN   | SYNC   | _     | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 SPBRG Baud rate generator register |       |       |        |        |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous reception. Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

# PIC17C4X

| DCF        | SNZ                                                          | Decreme                                                  | Decrement f, skip if not 0                                                              |                                                    |                                                                         |  |  |  |  |

|------------|--------------------------------------------------------------|----------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| Synt       | tax:                                                         | [ <i>label</i> ] D                                       | CFSNZ                                                                                   | f,d                                                |                                                                         |  |  |  |  |

| Ope        | rands:                                                       | 0 ≤ f ≤ 25<br>d ∈ [0,1]                                  | 5                                                                                       |                                                    |                                                                         |  |  |  |  |

| Ope        | ration:                                                      | .,                                                       | (f) $-1 \rightarrow$ (dest);<br>skip if not 0                                           |                                                    |                                                                         |  |  |  |  |

| Stat       | us Affected:                                                 | None                                                     |                                                                                         |                                                    |                                                                         |  |  |  |  |

| Enc        | oding:                                                       | 0010                                                     | 011d                                                                                    | ffff                                               | ffff                                                                    |  |  |  |  |

| Des        | cription:                                                    | WREG. If '<br>back in reg<br>If the resul<br>which is al | 'd' is 0 the<br>d' is 1 the<br>gister 'f'.<br>t is not 0, t<br>ready fetc<br>DP is exec | e result<br>result<br>he nex<br>hed, is<br>uted in | is placed in<br>is placed<br>t instruction,<br>discarded,<br>stead mak- |  |  |  |  |

| Wor        | ds:                                                          | 1                                                        |                                                                                         |                                                    |                                                                         |  |  |  |  |

| Cycl       | es:                                                          | 1(2)                                                     |                                                                                         |                                                    |                                                                         |  |  |  |  |

| QC         | ycle Activity:                                               |                                                          |                                                                                         |                                                    |                                                                         |  |  |  |  |

|            | Q1                                                           | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |  |  |  |

|            | Decode                                                       | Read<br>register 'f'                                     | Execu                                                                                   | ıte                                                | Write to destination                                                    |  |  |  |  |

| lf sk      | ip:                                                          |                                                          |                                                                                         |                                                    |                                                                         |  |  |  |  |

|            | Q1                                                           | Q2                                                       | Q3                                                                                      |                                                    | Q4                                                                      |  |  |  |  |

|            | Forced NOP                                                   | NOP                                                      | Execu                                                                                   | ute                                                | NOP                                                                     |  |  |  |  |

| <u>Exa</u> | <u>mple</u> :                                                | HERE<br>ZERO<br>NZERO                                    | DCFSNZ<br>:<br>:                                                                        | TEMP                                               | P, 1                                                                    |  |  |  |  |

|            | Before Instru<br>TEMP_V                                      |                                                          | ?                                                                                       |                                                    |                                                                         |  |  |  |  |

|            | After Instruct<br>TEMP_V<br>If TEMP_<br>PC<br>If TEMP_<br>PC | ALUE =<br>VALUE =<br>=                                   | 0;<br>Addre:<br>0;                                                                      | _VALU<br>ss (ze<br>ss (nz                          | RO)                                                                     |  |  |  |  |

| Syntax:<br>Operand | de.        |                                                     | 0010                                                                                                                                                                                                                                                       |      |      |  |  |  |  |

|--------------------|------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|--|--|--|

| Operand            | 18.        | $0 \le k \le 81$                                    | [ <i>label</i> ] GOTO k                                                                                                                                                                                                                                    |      |      |  |  |  |  |

|                    | ·          |                                                     | •                                                                                                                                                                                                                                                          |      |      |  |  |  |  |

| Operatio           | on:        | k → PC<1<br>k<12:8> -<br>PC<15:13                   | → PCLA                                                                                                                                                                                                                                                     |      | ,    |  |  |  |  |

| Status A           | Affected:  | None                                                |                                                                                                                                                                                                                                                            |      |      |  |  |  |  |

| Encoding:          |            | 110k                                                | kkkk                                                                                                                                                                                                                                                       | kkkk | kkkl |  |  |  |  |

| Description:       |            | The thirtee<br>loaded into<br>upper eigh<br>PCLATH. | GOTO allows an unconditional branch<br>anywhere within an 8K page boundary.<br>The thirteen bit immediate value is<br>loaded into PC bits <12:0>. Then the<br>upper eight bits of PC are loaded into<br>PCLATH. GOTO is always a two-cycle<br>instruction. |      |      |  |  |  |  |

| Words:             |            | 1                                                   |                                                                                                                                                                                                                                                            |      |      |  |  |  |  |

| Cycles:            |            | 2                                                   |                                                                                                                                                                                                                                                            |      |      |  |  |  |  |

| Q Cycle            | Activity:  |                                                     |                                                                                                                                                                                                                                                            |      |      |  |  |  |  |

|                    | Q1         | Q2                                                  | Q3                                                                                                                                                                                                                                                         | 5    | Q4   |  |  |  |  |

| E                  | Decode     | Read literal<br>'k'<7:0>                            | Execu                                                                                                                                                                                                                                                      | ute  | NOP  |  |  |  |  |

| For                | ced NOP    | NOP                                                 | Execu                                                                                                                                                                                                                                                      | ute  | NOP  |  |  |  |  |

| Example            | <u>e</u> : | GOTO THE                                            | RE                                                                                                                                                                                                                                                         |      |      |  |  |  |  |

| Afte               |            |                                                     |                                                                                                                                                                                                                                                            |      |      |  |  |  |  |

|                    | PC =       | Address (TH                                         | HERE )                                                                                                                                                                                                                                                     |      |      |  |  |  |  |

# PIC17C4X

| MOVFP                        | Move f to                 | р                                 |                                                                         | MOVLB                    | Move Lite                                                                                                                                                                         | eral to low i       | nibble in BSR                 |  |

|------------------------------|---------------------------|-----------------------------------|-------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|--|

| Syntax:                      | [ <i>label</i> ] N        | IOVFP f,p                         |                                                                         | Syntax:                  | [ label ]                                                                                                                                                                         | MOVLB k             |                               |  |

| Operands:                    | 0 ≤ f ≤ 255               | 5                                 |                                                                         | Operands:                | $0 \le k \le 15$                                                                                                                                                                  | 5                   |                               |  |

|                              | $0 \le p \le 31$          |                                   |                                                                         | Operation:               | k  ightarrow (BSR                                                                                                                                                                 | (<3:0>)             |                               |  |

| Operation:                   | $(f) \to (p)$             |                                   |                                                                         | Status Affected:         | None                                                                                                                                                                              |                     |                               |  |

| Status Affected:             | None                      |                                   |                                                                         | Encoding:                | 1011                                                                                                                                                                              | 1000 ui             | uuu kkkk                      |  |

| Encoding:                    | 011p                      | pppp ff                           | ff ffff                                                                 | Description:             | The four bi                                                                                                                                                                       | t literal 'k' is lo | baded in the                  |  |

| Description:                 | to data mer<br>can be any | mory location '<br>where in the 2 | nory location 'f'<br>p'. Location 'f'<br>56 word data<br>'p' can be 00h |                          | Bank Select Register (BSR). Only the low 4-bits of the Bank Select Registing are affected. The upper half of the E is unchanged. The assembler will encode the "u" fields as '0'. |                     |                               |  |

|                              |                           | 'f' can be WR                     | EG (a useful                                                            | Words:                   | 1                                                                                                                                                                                 |                     |                               |  |

|                              | special situ              | ,                                 | ful for transfer-                                                       | Cycles:                  | 1                                                                                                                                                                                 |                     |                               |  |

|                              |                           |                                   | on to a periph-                                                         | Q Cycle Activity:        |                                                                                                                                                                                   |                     |                               |  |

|                              |                           |                                   | transmit buffer                                                         | Q1                       | Q2                                                                                                                                                                                | Q3                  | Q4                            |  |

|                              | indirectly a              | ort). Both 'f' an<br>ddressed.    | d p can be                                                              | Decode                   | Read                                                                                                                                                                              | Execute             | Write literal                 |  |

| Words:                       | 1                         |                                   |                                                                         |                          | literal 'u:k'                                                                                                                                                                     |                     | 'k' to<br>BSR<3:0>            |  |

| Cycles:                      | 1                         |                                   |                                                                         | Example:                 | MOVLB                                                                                                                                                                             | 0x5                 |                               |  |

| Q Cycle Activity             | :                         |                                   |                                                                         | Before Instru            | uction                                                                                                                                                                            |                     |                               |  |

| Q1                           | Q2                        | Q3                                | Q4                                                                      | BSR reg                  | ister = 0x                                                                                                                                                                        | :22                 |                               |  |

| Decode                       | Read<br>register 'f'      | Execute                           | Write<br>register 'p'                                                   | After Instruc<br>BSR reg |                                                                                                                                                                                   | :25                 |                               |  |

| Example:                     | MOVFP I                   | REG1, REG2                        |                                                                         | Note: For th             | ne PIC17C42                                                                                                                                                                       | 2, only the lo      | ow four bits of               |  |

| Before Insti<br>REG1<br>REG2 |                           | 33,<br>11                         |                                                                         |                          | BSR registe<br>ed. The uppe                                                                                                                                                       |                     | sically imple-<br>ead as '0'. |  |

| After Instru<br>REG1         |                           | 33,                               |                                                                         |                          |                                                                                                                                                                                   |                     |                               |  |

REG2

0x33

=

| SLEEP                                                                                 | Enter SL                                             | Enter SLEEP mode                                                                                                                                                                                               |       |    |      |  |  |  |

|---------------------------------------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----|------|--|--|--|

| Syntax:                                                                               | [label] S                                            | [label] SLEEP                                                                                                                                                                                                  |       |    |      |  |  |  |

| Operands:                                                                             | None                                                 | None                                                                                                                                                                                                           |       |    |      |  |  |  |

| Operation:                                                                            |                                                      |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Status Affected:                                                                      | TO, PD                                               |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Encoding:                                                                             | 0000                                                 | 0000                                                                                                                                                                                                           | 000   | 0  | 0011 |  |  |  |

| Description:                                                                          | cleared. Th<br>set. Watch<br>are cleare<br>The proce | The power down status bit (PD) is<br>cleared. The time-out status bit (TO) is<br>set. Watchdog Timer and its prescaler<br>are cleared.<br>The processor is put into SLEEP<br>mode with the oscillator stopped. |       |    |      |  |  |  |

| Words:                                                                                | 1                                                    |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Cycles:                                                                               | 1                                                    |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Q Cycle Activity:                                                                     |                                                      |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Q1                                                                                    | Q2                                                   | Q3                                                                                                                                                                                                             |       | (  | Q4   |  |  |  |

| Decode                                                                                | Read<br>register<br>PCLATH                           | Execu                                                                                                                                                                                                          | te    | N  | OP   |  |  |  |

| Example:                                                                              | SLEEP                                                |                                                                                                                                                                                                                |       |    |      |  |  |  |

| Before Instruction<br>$\overline{TO} = ?$<br>$\overline{PD} = ?$<br>After Instruction |                                                      |                                                                                                                                                                                                                |       |    |      |  |  |  |

| TO =<br>PD =<br>† If WDT causes                                                       | 1†<br>0                                              | nie hit ie                                                                                                                                                                                                     | clear | be |      |  |  |  |

† If WDT causes wake-up, this bit is cleared

| SUE        | BLW                                                  | S                   | Subtr                                                                                  | act  | WREG                     | from    | ı Lit | teral            |  |

|------------|------------------------------------------------------|---------------------|----------------------------------------------------------------------------------------|------|--------------------------|---------|-------|------------------|--|

| Synt       | tax:                                                 | [                   | labe                                                                                   | /] : | SUBLW                    | k       |       |                  |  |

| Ope        | rands:                                               | 0                   | $\leq k$                                                                               | ≤ 2  | 55                       |         |       |                  |  |

| Ope        | ration:                                              | k                   | $k - (WREG) \rightarrow (WREG)$                                                        |      |                          |         |       |                  |  |

| Stat       | us Affected:                                         | C                   | DV, C                                                                                  | , D  | C, Z                     |         |       |                  |  |

| Enc        | oding:                                               | Γ                   | 101                                                                                    | 1    | 0010                     | kkł     | k     | kkkk             |  |

| Des        | cription:                                            | li                  | WREG is subtracted from the eight bit<br>literal 'k'. The result is placed in<br>WREG. |      |                          |         |       |                  |  |

| Wor        | ds:                                                  | 1                   |                                                                                        |      |                          |         |       |                  |  |

| Cycl       | les:                                                 | 1                   |                                                                                        |      |                          |         |       |                  |  |

| QC         | ycle Activity:                                       |                     |                                                                                        |      |                          |         |       |                  |  |

|            | Q1                                                   |                     | Q2                                                                                     |      | Q3                       |         |       | Q4               |  |

|            | Decode                                               | -                   | Read<br>eral 'k                                                                        | ۲'   | Execu                    | ite     |       | Vrite to<br>WREG |  |

| Exa        | <u>mple 1</u> :                                      | S                   | UBLW                                                                                   | 1 (  | Ox02                     |         |       |                  |  |

|            | Before Instru<br>WREG<br>C<br>After Instruct<br>WREG | =<br>=              | ר<br>1<br>?<br>1                                                                       |      |                          |         |       |                  |  |

| <u>Exa</u> | C<br>Z<br>mple <u>2</u> :                            | =                   | 1<br>0                                                                                 | ; re | esult is po              | ositive |       |                  |  |

|            | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>2<br>?                                                                            |      |                          |         |       |                  |  |

| <u>Exa</u> | After Instruct<br>WREG<br>C<br>Z<br>mple <u>3</u> :  | tion<br>=<br>=<br>= | 0<br>1<br>1                                                                            | ; re | esult is ze              | ero     |       |                  |  |

|            | Before Instru<br>WREG<br>C                           | ictior<br>=<br>=    | ר<br>3<br>?                                                                            |      |                          |         |       |                  |  |

|            | After Instruct<br>WREG<br>C<br>Z                     | tion<br>=<br>=<br>= | FF<br>0<br>1                                                                           |      | 's comple<br>esult is ne |         | ·     |                  |  |

# Applicable Devices 42 R42 42A 43 R43 44

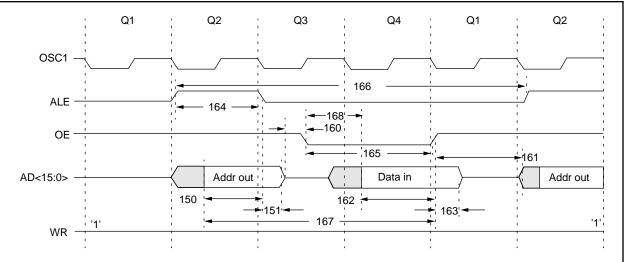

### FIGURE 17-12: MEMORY INTERFACE READ TIMING

| Parameter<br>No. | Sym      | Characteristic                                           | Min           | Тур†      | Max          | Units | Conditions |

|------------------|----------|----------------------------------------------------------|---------------|-----------|--------------|-------|------------|

| 150              | TadV2alL | AD<15:0> (address) valid to ALE↓<br>(address setup time) | 0.25Tcy - 30  |           | _            | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)          | 5*            |           | _            | ns    |            |

| 160              | TadZ2oeL | AD<15:0> high impedance to $\overline{OE}\downarrow$     | 0*            | _         | —            | ns    |            |

| 161              | ToeH2adD | OE↑ to AD<15:0> driven                                   | 0.25Tcy - 15  | _         | _            | ns    |            |

| 162              | TadV2oeH | Data in valid before OE↑<br>(data setup time)            | 35            | _         | _            | ns    |            |

| 163              | ToeH2adl | OE to data in invalid (data hold time)                   | 0             | _         | _            | ns    |            |

| 164              | TalH     | ALE pulse width                                          | —             | 0.25Tcy § | —            | ns    |            |

| 165              | ToeL     | OE pulse width                                           | 0.5Tcy - 35 § | _         | _            | ns    |            |

| 166              | TalH2alH | ALE <sup>↑</sup> to ALE <sup>↑</sup> (cycle time)        | —             | TCY §     | —            | ns    |            |

| 167              | Tacc     | Address access time                                      | —             | _         | 0.75 Tcy-40  | ns    |            |

| 168              | Тое      | Output enable access time<br>(OE low to Data Valid)      | -             | _         | 0.5 TCY - 60 | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification guaranteed by design.

# PIC17C4X

## Applicable Devices 42 R42 42A 43 R43 44

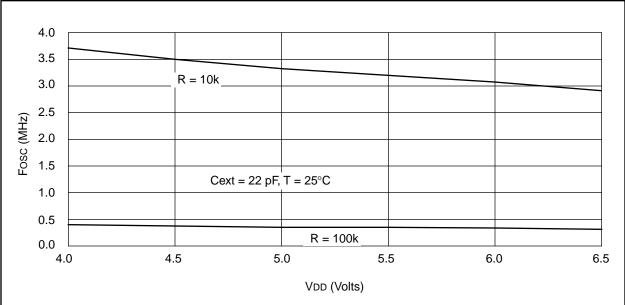

## FIGURE 18-2: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

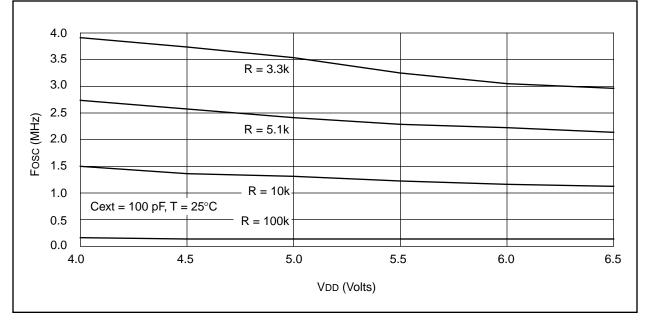

## FIGURE 18-3: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

## Applicable Devices 42 R42 42A 43 R43 44

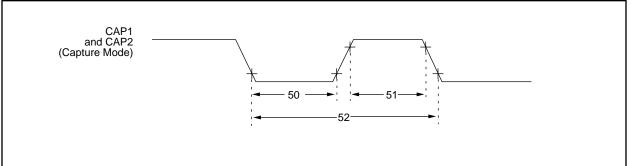

## FIGURE 19-7: CAPTURE TIMINGS

## TABLE 19-7: CAPTURE REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                        | Min                | Тур† | Max | Units | Conditions                      |

|------------------|------|---------------------------------------|--------------------|------|-----|-------|---------------------------------|

| 50               | TccL | Capture1 and Capture2 input low time  | 10 *               | —    | —   | ns    |                                 |

| 51               | TccH | Capture1 and Capture2 input high time | 10 *               | —    |     | ns    |                                 |

| 52               | TccP | Capture1 and Capture2 input period    | <u>2Tcy</u> §<br>N | _    | _   | ns    | N = prescale value<br>(4 or 16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

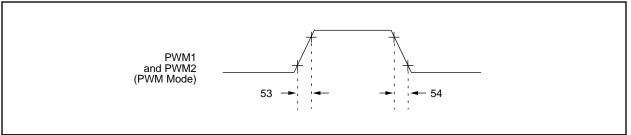

#### FIGURE 19-8: PWM TIMINGS

#### TABLE 19-8: PWM REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                           | Min | Тур† | Max   | Units | Conditions |

|------------------|------|------------------------------------------|-----|------|-------|-------|------------|

| 53               | TccR | PWM1 and PWM2 output rise time           |     | 10 * | 35 *§ | ns    |            |

| 54               | TccF | PWM1 and PWM2 output fall time           |     | 10 * | 35 *§ | ns    |            |

| * The            |      | motors are observatorized but not tested |     |      |       |       |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

# Applicable Devices 42 R42 42A 43 R43 44

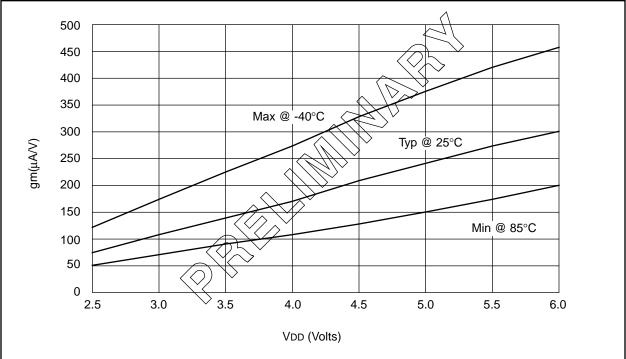

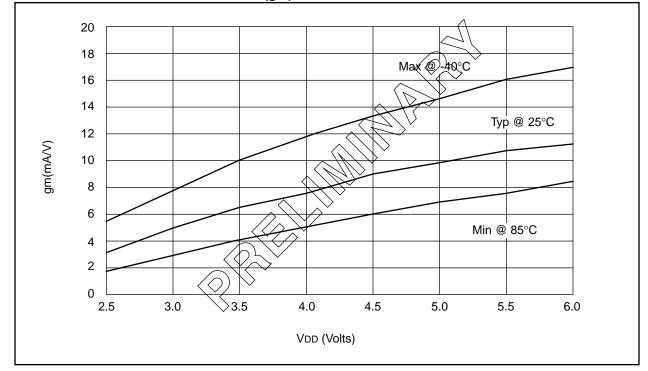

FIGURE 20-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

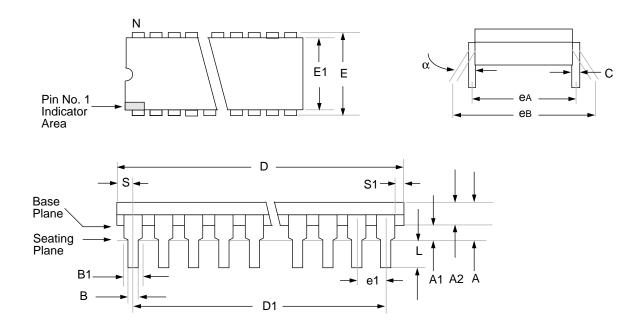

## 21.2 <u>40-Lead Plastic Dual In-line (600 mil)</u>

|        |        | Package Gro | up: Plastic Dual | In-Line (PLA) |        |           |

|--------|--------|-------------|------------------|---------------|--------|-----------|

|        |        | Millimeters |                  |               | Inches |           |

| Symbol | Min    | Мах         | Notes            | Min           | Max    | Notes     |

| α      | 0°     | 10°         |                  | 0°            | 10°    |           |

| Α      | _      | 5.080       |                  | _             | 0.200  |           |

| A1     | 0.381  | _           |                  | 0.015         | _      |           |

| A2     | 3.175  | 4.064       |                  | 0.125         | 0.160  |           |

| В      | 0.355  | 0.559       |                  | 0.014         | 0.022  |           |

| B1     | 1.270  | 1.778       | Typical          | 0.050         | 0.070  | Typical   |

| С      | 0.203  | 0.381       | Typical          | 0.008         | 0.015  | Typical   |

| D      | 51.181 | 52.197      |                  | 2.015         | 2.055  |           |

| D1     | 48.260 | 48.260      | Reference        | 1.900         | 1.900  | Reference |

| E      | 15.240 | 15.875      |                  | 0.600         | 0.625  |           |

| E1     | 13.462 | 13.970      |                  | 0.530         | 0.550  |           |

| e1     | 2.489  | 2.591       | Typical          | 0.098         | 0.102  | Typical   |

| eA     | 15.240 | 15.240      | Reference        | 0.600         | 0.600  | Reference |

| eB     | 15.240 | 17.272      |                  | 0.600         | 0.680  |           |

| L      | 2.921  | 3.683       |                  | 0.115         | 0.145  |           |

| N      | 40     | 40          |                  | 40            | 40     |           |

| S      | 1.270  | _           |                  | 0.050         | _      |           |

| S1     | 0.508  | -           |                  | 0.020         | _      |           |

## E.4 PIC16C6X Family of Devices

|                          |                 |                    |                    |                                               | L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Memory         | ory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | ſ               | Peripherals      | rals                     |                         |            | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |