Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                  |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | OTP                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc43-08-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

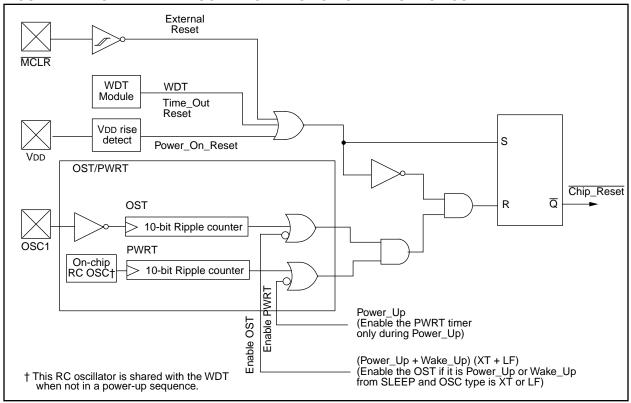

# 4.0 RESET

The PIC17CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- WDT Reset (normal operation)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are forced to a "reset state" on Power-on Reset (POR), on  $\overline{\text{MCLR}}$  or WDT Reset and on  $\overline{\text{MCLR}}$  reset during SLEEP. They are not affected by a WDT Reset during SLEEP, since this reset is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of reset. See Table 4-4 for a full description of reset states of all registers.

**Note:** While the device is in a reset state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

A simplified block diagram of the on-chip reset circuit is shown in Figure 4-1.

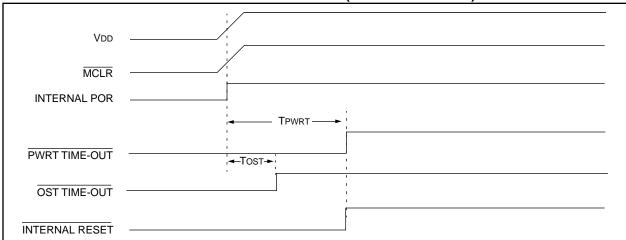

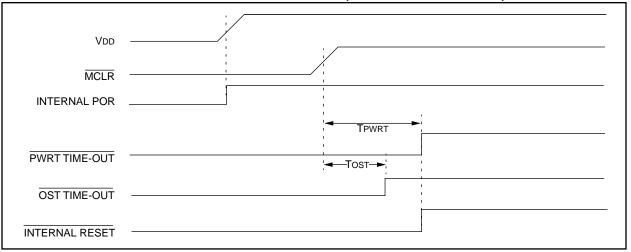

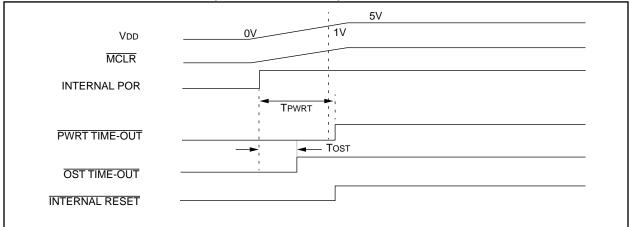

## 4.1 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT), and Oscillator Start-up</u> <u>Timer (OST)</u>

## 4.1.1 POWER-ON RESET (POR)

The Power-on Reset circuit holds the device in reset until VDD is above the trip point (in the range of 1.4V -2.3V). The PIC17C42 does not produce an internal reset when VDD declines. All other devices will produce an internal reset for both rising and falling VDD. To take advantage of the POR, just tie the MCLR/VPP pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD is required. See Electrical Specifications for details.

#### 4.1.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 96 ms time-out (nominal) on power-up. This occurs from rising edge of the POR signal and after the first rising edge of  $\overline{\text{MCLR}}$  (detected high). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. In most cases the PWRT delay allows the VDD to rise to an acceptable level.

The power-up time delay will vary from chip to chip and to VDD and temperature. See DC parameters for details.

## FIGURE 4-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 1996 Microchip Technology Inc.

FIGURE 4-2: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD)

#### FIGURE 4-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD)

## FIGURE 4-4: SLOW RISE TIME (MCLR TIED TO VDD)

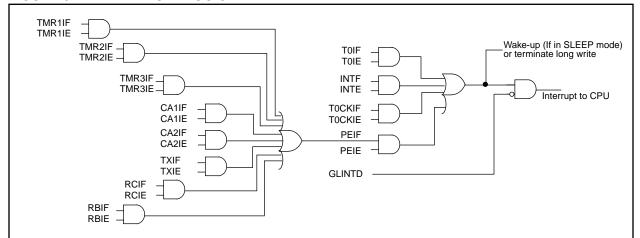

# 5.0 INTERRUPTS

The PIC17C4X devices have 11 sources of interrupt:

- External interrupt from the RA0/INT pin

- Change on RB7:RB0 pins

- TMR0 Overflow

- TMR1 Overflow

- TMR2 Overflow

- TMR3 Overflow

- USART Transmit buffer empty

- USART Receive buffer full

- Capture1

- Capture2

- T0CKI edge occurred

There are four registers used in the control and status of interrupts. These are:

- CPUSTA

- INTSTA

- PIE

- PIR

The CPUSTA register contains the GLINTD bit. This is the Global Interrupt Disable bit. When this bit is set, all interrupts are disabled. This bit is part of the controller core functionality and is described in the Memory Organization section. When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts which have the same vector address). These sources are:

- External interrupt from the RA0/INT pin

- TMR0 Overflow

- T0CKI edge occurred

- Any peripheral interrupt

When program execution vectors to one of these interrupt vector addresses (except for the peripheral interrupt address), the interrupt flag bit is automatically cleared. Vectoring to the peripheral interrupt vector address does not automatically clear the source of the interrupt. In the peripheral interrupt service routine, the source(s) of the interrupt can be determined by testing the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

All of the individual interrupt flag bits will be set regardless of the status of their corresponding mask bit or the GLINTD bit.

For external interrupt events, there will be an interrupt latency. For two cycle instructions, the latency could be one instruction cycle longer.

The "return from interrupt" instruction, RETFIE, can be used to mark the end of the interrupt service routine. When this instruction is executed, the stack is "POPed", and the GLINTD bit is cleared (to re-enable interrupts).

## FIGURE 5-1: INTERRUPT LOGIC

© 1996 Microchip Technology Inc.

#### 5.2 <u>Peripheral Interrupt Enable Register</u> (PIE)

This register contains the individual flag bits for the Peripheral interrupts.

# FIGURE 5-3: PIE REGISTER (ADDRESS: 17h, BANK 1)

| RBIE   | 0 R/W - 0 R/W<br>TMR3IE TMR2IE TMR1IE CA2IE CA1IE TXIE R0                                              | CIE R = Readable bit                             |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| bit7   |                                                                                                                                                | bit0 W = Writable bit<br>-n = Value at POR reset |

| bit 7: | <b>RBIE</b> : PORTB Interrupt on Change Enable bit<br>1 = Enable PORTB interrupt on change<br>0 = Disable PORTB interrupt on change            |                                                  |

| bit 6: | <b>TMR3IE</b> : Timer3 Interrupt Enable bit<br>1 = Enable Timer3 interrupt<br>0 = Disable Timer3 interrupt                                     |                                                  |

| bit 5: | <b>TMR2IE</b> : Timer2 Interrupt Enable bit<br>1 = Enable Timer2 interrupt<br>0 = Disable Timer2 interrupt                                     |                                                  |

| bit 4: | <b>TMR1IE</b> : Timer1 Interrupt Enable bit<br>1 = Enable Timer1 interrupt<br>0 = Disable Timer1 interrupt                                     |                                                  |

| bit 3: | <b>CA2IE</b> : Capture2 Interrupt Enable bit<br>1 = Enable Capture interrupt on RB1/CAP2 pin<br>0 = Disable Capture interrupt on RB1/CAP2 pin  |                                                  |

| bit 2: | <b>CA1IE</b> : Capture1 Interrupt Enable bit<br>1 = Enable Capture interrupt on RB2/CAP1 pin<br>0 = Disable Capture interrupt on RB2/CAP1 pin  |                                                  |

| bit 1: | <b>TXIE</b> : USART Transmit Interrupt Enable bit<br>1 = Enable Transmit buffer empty interrupt<br>0 = Disable Transmit buffer empty interrupt |                                                  |

| bit 0: | <b>RCIE</b> : USART Receive Interrupt Enable bit<br>1 = Enable Receive buffer full interrupt<br>0 = Disable Receive buffer full interrupt      |                                                  |

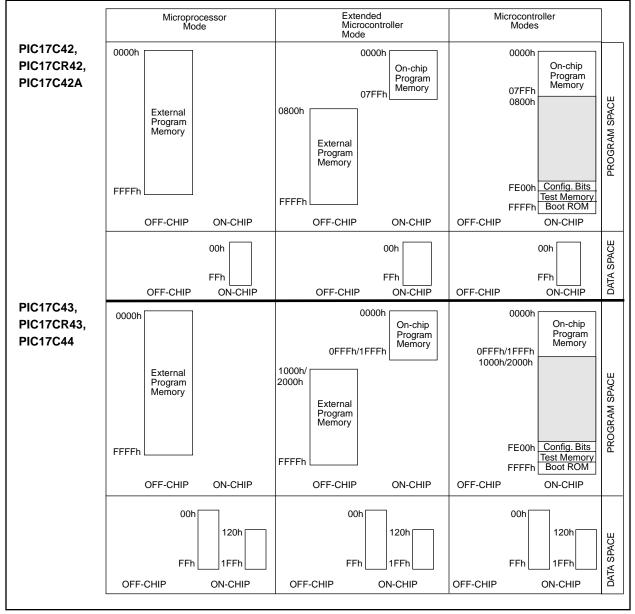

## TABLE 6-1: MODE MEMORY ACCESS

| Operating<br>Mode            | Internal<br>Program<br>Memory | Configuration Bits,<br>Test Memory,<br>Boot ROM |  |

|------------------------------|-------------------------------|-------------------------------------------------|--|

| Microprocessor               | No Access                     | No Access                                       |  |

| Microcontroller              | Access                        | Access                                          |  |

| Extended<br>Microcontroller  | Access                        | No Access                                       |  |

| Protected<br>Microcontroller | Access                        | Access                                          |  |

The PIC17C4X can operate in modes where the program memory is off-chip. They are the microprocessor and extended microcontroller modes. The microprocessor mode is the default for an unprogrammed device.

Regardless of the processor mode, data memory is always on-chip.

## FIGURE 6-2: MEMORY MAP IN DIFFERENT MODES

| TABLE 6-3: | SPECIAL FUNCTION REGISTERS |

|------------|----------------------------|

|------------|----------------------------|

| Address            | Name          | Bit 7        | Bit 6          | Bit 5         | Bit 4        | Bit 3        | Bit 2           | Bit 1          | Bit 0           | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------------|--------------|----------------|---------------|--------------|--------------|-----------------|----------------|-----------------|-------------------------------|-------------------------------------|

| Unbank             | ed            | •            |                |               |              | •            |                 |                | •               |                               |                                     |

| 00h                | INDF0         | Uses con     | tents of FSI   | R0 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 01h                | FSR0          | Indirect d   | ata memory     | address po    | inter 0      |              |                 |                |                 | XXXX XXXX                     | uuuu uuuu                           |

| 02h                | PCL           | Low orde     | r 8-bits of P  | С             |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| 03h <sup>(1)</sup> | PCLATH        | Holding re   | egister for u  | pper 8-bits o | of PC        |              |                 |                |                 | 0000 0000                     | uuuu uuuu                           |

| 04h                | ALUSTA        | FS3          | FS2            | FS1           | FS0          | OV           | Z               | DC             | С               | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA         | INTEDG       | TOSE           | TOCS          | PS3          | PS2          | PS1             | PS0            | —               | 0000 000-                     | 0000 000-                           |

| 06h <b>(2)</b>     | CPUSTA        | _            | —              | STKAV         | GLINTD       | TO           | PD              | _              | _               | 11 11                         | 11 qq                               |

| 07h                | INTSTA        | PEIF         | TOCKIF         | T0IF          | INTF         | PEIE         | TOCKIE          | TOIE           | INTE            | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1         | Uses con     | tents of FSI   | R1 to addres  | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 09h                | FSR1          | Indirect d   | ata memory     | address po    | inter 1      |              | , ,             |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ah                | WREG          | Working r    | egister        |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Bh                | TMR0L         | TMR0 reg     | gister; low b  | yte           |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Ch                | TMR0H         | TMR0 reg     | gister; high I | oyte          |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 0Dh                | TBLPTRL       | Low byte     | of program     | memory tab    | le pointer   |              |                 |                |                 | (4)                           | (4)                                 |

| 0Eh                | TBLPTRH       | High byte    | of program     | memory tal    | ole pointer  |              |                 |                |                 | (4)                           | (4)                                 |

| 0Fh                | BSR           | Bank sele    | ect register   |               |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| Bank 0             |               | 1            |                |               |              |              |                 |                |                 | I                             |                                     |

| 10h                | PORTA         | RBPU         | _              | RA5           | RA4          | RA3          | RA2             | RA1/T0CKI      | RA0/INT         | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB          | Data dire    | ction registe  | er for PORTE  | 3            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB         | PORTB d      | ata latch      |               |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA         | SPEN         | RX9            | SREN          | CREN         | —            | FERR            | OERR           | RX9D            | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG         | Serial por   | t receive re   | gister        |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA         | CSRC         | TX9            | TXEN          | SYNC         | —            | —               | TRMT           | TX9D            | 00001x                        | 00001u                              |

| 16h                | TXREG         | Serial por   | t transmit re  | egister       |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG         | Baud rate    | generator      | register      |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |               |              |                |               |              |              |                 |                |                 |                               |                                     |

| 10h                | DDRC          | Data dire    | ction registe  | er for PORT   | 2            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC         | RC7/<br>AD7  | RC6/<br>AD6    | RC5/<br>AD5   | RC4/<br>AD4  | RC3/<br>AD3  | RC2/<br>AD2     | RC1/<br>AD1    | RC0/<br>AD0     | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD          | Data dire    | ction registe  | er for PORTI  | )            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 4.01-              | PORTD         | RD7/<br>AD15 | RD6/<br>AD14   | RD5/<br>AD13  | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10    | RD1/<br>AD9    | RD0/<br>AD8     | xxxx xxxx                     | uuuu uuuu                           |

| 13h                |               |              |                |               |              |              |                 |                |                 | 111                           | 111                                 |

| 13h<br>14h         | DDRE          | Data dire    |                |               |              |              |                 | -              |                 |                               |                                     |

|                    | DDRE<br>PORTE | Data dire    | _              | _             | _            | _            | RE2/WR          | RE1/OE         | RE0/ALE         | xxx                           | uuu                                 |

| 14h                |               | RBIF         | —<br>TMR3IF    | —<br>TMR2IF   | —<br>TMR1IF  | —<br>CA2IF   | RE2/WR<br>CA1IF | RE1/OE<br>TXIF | RE0/ALE<br>RCIF | xxx<br>0000 0010              | uuu<br>0000 0010                    |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1:

from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 2:

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

4:

The following values are for both TBLPTRL and TBLPTRH: All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

5: The PRODL and PRODH registers are not implemented on the PIC17C42.

#### 6.2.2.1 ALU STATUS REGISTER (ALUSTA)

The ALUSTA register contains the status bits of the Arithmetic and Logic Unit and the mode control bits for the indirect addressing register.

As with all the other registers, the ALUSTA register can be the destination for any instruction. If the ALUSTA register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Therefore, the result of an instruction with the ALUSTA register as destination may be different than intended.

For example, CLRF ALUSTA will clear the upper four bits and set the Z bit. This leaves the ALUSTA register as 0000u1uu (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions be used to alter the ALUSTA register because these instructions do not affect any status bit. To see how other instructions affect the status bits, see the "Instruction Set Summary."

| Note | 1: The C and DC bits operate as a borrow<br>out bit in subtraction. See the SUBLW and<br>SUBWF instructions for examples. |

|------|---------------------------------------------------------------------------------------------------------------------------|

| Note | 2: The overflow bit will be set if the 2's com-<br>plement result exceeds +127 or is less<br>than -128.                   |

Arithmetic and Logic Unit (ALU) is capable of carrying out arithmetic or logical operations on two operands or a single operand. All single operand instructions operate either on the WREG register or a file register. For two operand instructions, one of the operands is the WREG register and the other one is either a file register or an 8-bit immediate constant.

| FS3      | FS2                                  | FS1                                                                | FS0                                                  | OV                                                      | Z                                   | DC                       | С          | R = Readable bit                                                  |

|----------|--------------------------------------|--------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|-------------------------------------|--------------------------|------------|-------------------------------------------------------------------|

| bit7     | 1                                    | 1                                                                  |                                                      |                                                         |                                     | I                        | bit0       | W = Writable bit<br>-n = Value at POR reset<br>(x = unknown)      |

| bit 7-6: | 01 = Pos                             | FSR1 Mo<br>t auto-dect<br>t auto-incre<br>t value de               | rement FS<br>ement FSI                               | R1 value<br>R1 value                                    |                                     |                          |            |                                                                   |

| bit 5-4: | 01 = Pos                             | FSR0 Mo<br>t auto-deci<br>t auto-incre<br>0 value de               | rement FS<br>ement FSI                               | R0 value<br>R0 value                                    |                                     |                          |            |                                                                   |

| bit 3:   | which cau<br>1 = Overfl              | s used for<br>uses the si                                          | gn bit (bit7<br>ed for sign                          | ') to chang                                             |                                     |                          |            | overflow of the 7-bit magnitude,                                  |

| bit 2:   |                                      | esult of an                                                        |                                                      |                                                         | peration is operation is            |                          |            |                                                                   |

| bit 1:   | For ADDW<br>1 = A carr $0 = No ca$   | •                                                                  | LW instruc<br>the 4th lo<br>m the 4th                | w order bi<br>low order                                 | t of the res<br>bit of the re<br>I. |                          | d          |                                                                   |

| bit 0:   | 1 = A carr<br>Note that<br>(RRCF, RL | F and ADD<br>y-out from<br>a subtrac<br>CF) instru-<br>rry-out fro | the most<br>tion is exe<br>ctions, this<br>m the mos | significant<br>cuted by a<br>bit is load<br>t significa | ded with eit<br>nt bit of the       | two's com<br>her the hig | plement of | the second operand. For rotate<br>der bit of the source register. |

#### FIGURE 6-7: ALUSTA REGISTER (ADDRESS: 04h, UNBANKED)

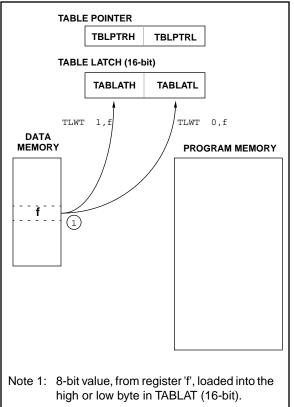

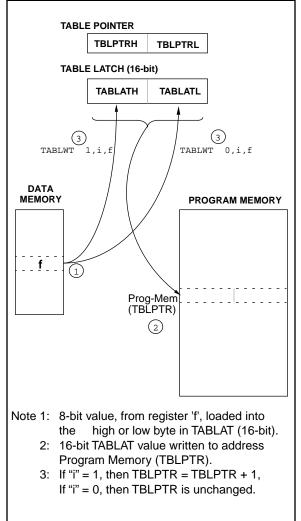

## 7.0 TABLE READS AND TABLE WRITES

The PIC17C4X has four instructions that allow the processor to move data from the data memory space to the program memory space, and vice versa. Since the program memory space is 16-bits wide and the data memory space is 8-bits wide, two operations are required to move 16-bit values to/from the data memory.

The TLWT t,f and TABLWT t,i,f instructions are used to write data from the data memory space to the program memory space. The TLRD t,f and TABLRD t,i,f instructions are used to write data from the program memory space to the data memory space.

The program memory can be internal or external. For the program memory access to be external, the device needs to be operating in extended microcontroller or microprocessor mode.

Figure 7-1 through Figure 7-4 show the operation of these four instructions.

## FIGURE 7-2: TABLWT INSTRUCTION OPERATION

© 1996 Microchip Technology Inc.

# 11.0 TIMER0

The Timer0 module consists of a 16-bit timer/counter, TMR0. The high byte is TMR0H and the low byte is TMR0L. A software programmable 8-bit prescaler makes an effective 24-bit overflow timer. The clock source is also software programmable as either the internal instruction clock or the RA1/T0CKI pin. The control bits for this module are in register T0STA (Figure 11-1).

| R/W - 0        | R/W - 0                                                              | R/W - 0                                          | R/W - 0                                                            | R/W - 0                    | R/W - 0                  | R/W - 0     | U - 0     |                                                                                                      |

|----------------|----------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------|----------------------------|--------------------------|-------------|-----------|------------------------------------------------------------------------------------------------------|

| INTEDG<br>bit7 | TOSE                                                                 | TOCS                                             | PS3                                                                | PS2                        | PS1                      | PS0         | —<br>bit0 | R = Readable bit<br>W = Writable bit<br>U = Unimplemented,<br>Read as '0'<br>-n = Value at POR reset |

| bit 7:         | <b>INTEDG</b> : R<br>This bit sele<br>1 = Rising e<br>0 = Falling e  | ects the ed<br>edge of RA                        | ge upon w<br>0/INT pin g                                           | hich the in<br>generates i | terrupt is d<br>nterrupt | etected     |           | -n = value al POR lesel                                                                              |

| bit 6:         |                                                                      | ects the ed<br>S = 0<br>edge of RA<br>edge of RA | ge upon w<br>1/T0CKI pi                                            | hich TMR(                  | nts TMR0 a               | and/or gene |           | CKIF interrupt<br>CKIF interrupt                                                                     |

| bit 5:         | <b>TOCS</b> : Time<br>This bit sele<br>1 = Internal<br>0 = TOCKI     | ects the clo<br>instruction                      | ck source                                                          | for TMR0.                  |                          |             |           |                                                                                                      |

| bit 4-1:       | <b>PS3:PS0</b> : T<br>These bits                                     |                                                  |                                                                    |                            | R0.                      |             |           |                                                                                                      |

|                | PS3:PS0                                                              | Pre                                              | scale Valu                                                         | е                          |                          |             |           |                                                                                                      |

|                | 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1xxx |                                                  | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 |                            |                          |             |           |                                                                                                      |

| bit 0:         | Unimplem                                                             | <b>ented</b> : Rea                               | id as '0'                                                          |                            |                          |             |           |                                                                                                      |

### FIGURE 11-1: T0STA REGISTER (ADDRESS: 05h, UNBANKED)

#### © 1996 Microchip Technology Inc.

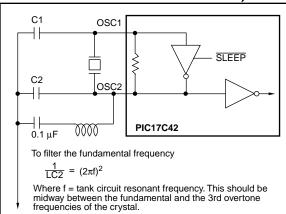

#### FIGURE 14-3: CRYSTAL OPERATION, OVERTONE CRYSTALS (XT OSC CONFIGURATION)

## TABLE 14-2: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Oscillator<br>Type | Resonator<br>Frequency         | Capacitor Range<br>C1 = C2               |

|--------------------|--------------------------------|------------------------------------------|

| LF                 | 455 kHz<br>2.0 MHz             | 15 - 68 pF<br>10 - 33 pF                 |

| ХТ                 | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 22 - 68 pF<br>33 - 100 pF<br>33 - 100 pF |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

#### **Resonators Used:**

| 455 kHz                                           | Panasonic EFO-A455K04B | ± 0.3% |  |

|---------------------------------------------------|------------------------|--------|--|

| 2.0 MHz                                           | Murata Erie CSA2.00MG  | ± 0.5% |  |

| 4.0 MHz                                           | Murata Erie CSA4.00MG  | ± 0.5% |  |

| 8.0 MHz                                           | Murata Erie CSA8.00MT  | ± 0.5% |  |

| 16.0 MHz                                          | Murata Erie CSA16.00MX | ± 0.5% |  |

| Resonators used did not have built-in capacitors. |                        |        |  |

# TABLE 14-3:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Freq                  | C1               | C2             |

|-------------|-----------------------|------------------|----------------|

| LF          | 32 kHz <sup>(1)</sup> | 100-150 pF       | 100-150 pF     |

|             | 1 MHz                 | 10-33 pF         | 10-33 pF       |

|             | 2 MHz                 | 10-33 pF         | 10-33 pF       |

| XT          | 2 MHz                 | 47-100 pF        | 47-100 pF      |

|             | 4 MHz                 | 15-68 pF         | 15-68 pF       |

|             | 8 MHz <sup>(2)</sup>  | 15-47 pF         | 15-47 pF       |

|             | 16 MHz                | TBD              | TBD            |

|             | 25 MHz                | 15-47 pF         | 15-47 pF       |

|             | 32 MHz <sup>(3)</sup> | <sub>0</sub> (3) | <sub>(3)</sub> |

Higher capacitance increases the stability of the oscillator but also increases the start-up time and the oscillator current. These values are for design guidance only. Rs may be required in XT mode to avoid overdriving the crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values for external components.

- Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

- Rs of 330Ω is required for a capacitor combination of 15/15 pF.

- 3: Only the capacitance of the board was present.

#### **Crystals Used:**

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM     |

|------------|-----------------------|--------------|

| 1.0 MHz    | ECS-10-13-1           | $\pm$ 50 PPM |

| 2.0 MHz    | ECS-20-20-1           | $\pm$ 50 PPM |

| 4.0 MHz    | ECS-40-20-1           | ± 50 PPM     |

| 8.0 MHz    | ECS ECS-80-S-4        | ± 50 PPM     |

|            | ECS-80-18-1           |              |

| 16.0 MHz   | ECS-160-20-1          | TBD          |

| 25 MHz     | CTS CTS25M            | $\pm$ 50 PPM |

| 32 MHz     | CRYSTEK HF-2          | $\pm$ 50 PPM |

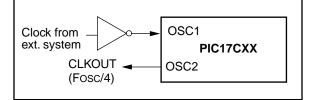

#### 14.2.3 EXTERNAL CLOCK OSCILLATOR

In the EC oscillator mode, the OSC1 input can be driven by CMOS drivers. In this mode, the OSC1/CLKIN pin is hi-impedance and the OSC2/CLK-OUT pin is the CLKOUT output (4 Tosc).

#### FIGURE 14-4: EXTERNAL CLOCK INPUT OPERATION (EC OSC CONFIGURATION)

### 14.3 Watchdog Timer (WDT)

The Watchdog Timer's function is to recover from software malfunction. The WDT uses an internal free running on-chip RC oscillator for its clock source. This does not require any external components. This RC oscillator is separate from the RC oscillator of the OSC1/CLKIN pin. That means that the WDT will run, even if the clock on the OSC1/CLKIN and OSC2/CLK-OUT pins of the device has been stopped, for example, by execution of a SLEEP instruction. During normal operation and SLEEP mode, a WDT time-out generates a device RESET. The WDT can be permanently disabled by programming the configuration bits WDTPS1:WDTPS0 as '00' (Section 14.1).

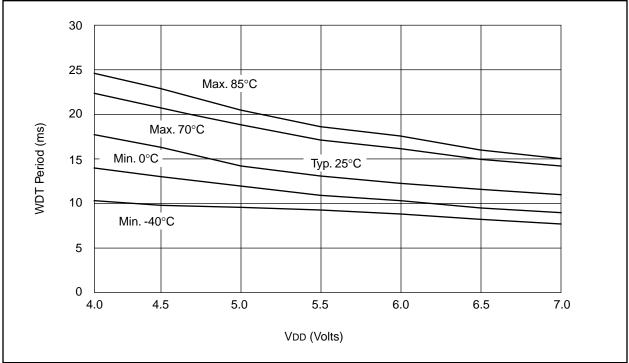

Under normal operation, the WDT must be cleared on a regular interval. This time is less the minimum WDT overflow time. Not clearing the WDT in this time frame will cause the WDT to overflow and reset the device.

#### 14.3.1 WDT PERIOD

The WDT has a nominal time-out period of 12 ms, (with postscaler = 1). The time-out periods vary with temperature, VDD and process variations from part to part (see DC specs). If longer time-out periods are desired, a postscaler with a division ratio of up to 1:256 can be assigned to the WDT. Thus, typical time-out periods up to 3.0 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the postscaler (if assigned to the WDT) and prevent it from timing out thus generating a device RESET condition.

The  $\overline{\text{TO}}$  bit in the CPUSTA register will be cleared upon a WDT time-out.

#### 14.3.2 CLEARING THE WDT AND POSTSCALER

The WDT and postscaler are cleared when:

- The device is in the reset state

- A SLEEP instruction is executed

- A CLRWDT instruction is executed

- Wake-up from SLEEP by an interrupt

The WDT counter/postscaler will start counting on the first edge after the device exits the reset state.

#### 14.3.3 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worst case conditions (VDD = Min., Temperature = Max., max. WDT postscaler) it may take several seconds before a WDT time-out occurs.

The WDT and postscaler is the Power-up Timer during the Power-on Reset sequence.

#### 14.3.4 WDT AS NORMAL TIMER

When the WDT is selected as a normal timer, the clock source is the device clock. Neither the WDT nor the postscaler are directly readable or writable. The overflow time is 65536 Tosc cycles. On overflow, the  $\overline{\text{TO}}$  bit is cleared (device is not reset). The CLRWDT instruction can be used to set the  $\overline{\text{TO}}$  bit. This allows the WDT to be a simple overflow timer. When in sleep, the WDT does not increment.

| ADDLW ADD Literal to WREG |                                      |                      |       |                  |  |

|---------------------------|--------------------------------------|----------------------|-------|------------------|--|

| Syntax:                   | [label] A                            | DLW                  | k     |                  |  |

| Operands:                 | $0 \le k \le 25$                     | 5                    |       |                  |  |

| Operation:                | (WREG) -                             | + k $\rightarrow$ (V | VREG) |                  |  |

| Status Affected:          | OV, C, DC                            | C, Z                 |       |                  |  |

| Encoding:                 | 1011                                 | 0001                 | kkkk  | kkkk             |  |

| Description:              | The conten<br>8-bit literal<br>WREG. |                      |       |                  |  |

| Words:                    | 1                                    |                      |       |                  |  |

| Cycles:                   | 1                                    |                      |       |                  |  |

| Q Cycle Activity:         |                                      |                      |       |                  |  |

| Q1                        | Q2                                   | Q3                   | 3     | Q4               |  |

| Decode                    | Read<br>literal 'k'                  | Execu                |       | Write to<br>WREG |  |

| Example:                  | ADDLW                                | 0x15                 |       |                  |  |

| Before Instruc<br>WREG =  |                                      |                      |       |                  |  |

| ADDWF                         | ADD WRE                                    | EG to f                                                           |            |                       |  |  |

|-------------------------------|--------------------------------------------|-------------------------------------------------------------------|------------|-----------------------|--|--|

| Syntax:                       | [ <i>label</i> ] A[                        | DDWF f                                                            | f,d        |                       |  |  |

| Operands:                     | $0 \le f \le 255$ $d \in [0,1]$            | $\begin{array}{l} 0 \leq f \leq 255 \\ d \in \ [0,1] \end{array}$ |            |                       |  |  |

| Operation:                    | (WREG) +                                   | - (f) $\rightarrow$ (de                                           | est)       |                       |  |  |

| Status Affected:              | OV, C, DC                                  | , Z                                                               |            |                       |  |  |

| Encoding:                     | 0000                                       | 111d                                                              | ffff       | ffff                  |  |  |

| Description:                  | Add WREG<br>result is sto<br>result is sto | red in WRE                                                        | EG. If 'd' | is 1 the              |  |  |

| Words:                        | 1                                          |                                                                   |            |                       |  |  |

| Cycles:                       | 1                                          | 1                                                                 |            |                       |  |  |

| Q Cycle Activity:             |                                            |                                                                   |            |                       |  |  |

| Q1                            | Q2                                         | Q3                                                                |            | Q4                    |  |  |

| Decode                        | Read<br>register 'f'                       | Execute                                                           |            | /rite to<br>stination |  |  |

| Example:                      | ADDWF                                      | REG, 0                                                            |            |                       |  |  |

| Before Instru<br>WREG<br>REG  | iction<br>= 0x17<br>= 0xC2                 |                                                                   |            |                       |  |  |

| After Instruct<br>WREG<br>REG | tion<br>= 0xD9<br>= 0xC2                   |                                                                   |            |                       |  |  |

After Instruction WREG = 0x25

| ANDWF                                                         | AND WRE                                                  | EG with                     | f                    |                       |  |  |

|---------------------------------------------------------------|----------------------------------------------------------|-----------------------------|----------------------|-----------------------|--|--|

| Syntax:                                                       | [ <i>label</i> ] A                                       | NDWF                        | f,d                  |                       |  |  |

| Operands:                                                     | $0 \le f \le 255$ $d \in [0,1]$                          | 5                           |                      |                       |  |  |

| Operation:                                                    | (WREG) .                                                 | AND. (f)                    | $\rightarrow$ (dest) | )                     |  |  |

| Status Affected:                                              | Z                                                        |                             |                      |                       |  |  |

| Encoding:                                                     | 0000                                                     | 101d                        | ffff                 | ffff                  |  |  |

| Description:                                                  | The conten<br>register 'f'.<br>in WREG. I<br>back in reg | lf 'd' is 0<br>f 'd' is 1 t | the result           | is stored             |  |  |

| Words:                                                        | 1                                                        |                             |                      |                       |  |  |

| Cycles:                                                       | 1                                                        | 1                           |                      |                       |  |  |

| Q Cycle Activity:                                             |                                                          |                             |                      |                       |  |  |

| Q1                                                            | Q2                                                       | Q3                          | 8                    | Q4                    |  |  |

| Decode                                                        | Read<br>register 'f'                                     | Execu                       |                      | Vrite to<br>stination |  |  |

| Example:                                                      | ANDWF                                                    | REG, 1                      |                      |                       |  |  |

| Before Instru<br>WREG<br>REG<br>After Instruct<br>WREG<br>REG | = 0x17<br>= 0xC2                                         |                             |                      |                       |  |  |

| BCF         |                   | Bit Clear                        | Bit Clear f   |       |     |                     |  |  |

|-------------|-------------------|----------------------------------|---------------|-------|-----|---------------------|--|--|

| Syntax:     |                   | [ <i>label</i> ] E               | BCF f,I       | С     |     |                     |  |  |

| Operands:   |                   | $0 \le f \le 25$ $0 \le b \le 7$ | 5             |       |     |                     |  |  |

| Operation:  |                   | $0 \rightarrow (f < b >$         | -)            |       |     |                     |  |  |

| Status Affe | cted:             | None                             |               |       |     |                     |  |  |

| Encoding:   |                   | 1000                             | 1bbb          | fff   | f   | ffff                |  |  |

| Description | :                 | Bit 'b' in re                    | gister 'f' is | clear | ed. |                     |  |  |

| Words:      |                   | 1                                | 1             |       |     |                     |  |  |

| Cycles:     |                   | 1                                | 1             |       |     |                     |  |  |

| Q Cycle Ac  | Q Cycle Activity: |                                  |               |       |     |                     |  |  |

| Q           | 1                 | Q2                               | Q3            |       | Q4  |                     |  |  |

| Deco        | ode               | Read<br>register 'f'             | Execute       |       |     | Write<br>gister 'f' |  |  |

| Example:    | Example:          |                                  | FLAG_R        | EG,   | 7   |                     |  |  |

| After Ir    | AG_RI             | $\Xi G = 0xC7$                   |               |       |     |                     |  |  |

| FL.         |                   | _0 = 0,47                        |               |       |     |                     |  |  |

| INC               | F                               | In                  | Increment f               |              |                                              |                       |

|-------------------|---------------------------------|---------------------|---------------------------|--------------|----------------------------------------------|-----------------------|

| Synt              | tax:                            | [ /                 | [ <i>label</i> ] INCF f,d |              |                                              |                       |

| Operands:         |                                 |                     | 0 ≤ f ≤ 255<br>d ∈ [0,1]  |              |                                              |                       |

| Ope               | ration:                         | (f)                 | + 1 $\rightarrow$         | (dest)       |                                              |                       |

| Stat              | us Affected:                    | 0                   | V, C, D0                  | C, Z         |                                              |                       |

| Enco              | oding:                          |                     | 0001                      | 010d         | ffff                                         | ffff                  |

| Description:      |                                 |                     | ented. If                 | 'd' is 0 the | ster 'f' are<br>e result is<br>e result is p | placed in             |

| Wor               | ds:                             | 1                   |                           |              |                                              |                       |

| Cycl              | es:                             | 1                   |                           |              |                                              |                       |

| Q Cycle Activity: |                                 |                     |                           |              |                                              |                       |

|                   | Q1                              |                     | Q2                        | Q            | 3                                            | Q4                    |

|                   | Decode                          |                     | Read<br>gister 'f'        | Exec         |                                              | Vrite to<br>stination |

| <u>Exa</u>        | <u>mple</u> :                   | IN                  | ICF                       | CNT,         | 1                                            |                       |

|                   | Before Instru                   | uctior              | า                         |              |                                              |                       |

|                   | CNT                             | =                   | 0xFF                      |              |                                              |                       |

|                   | Z<br>C                          | =                   | 0<br>?                    |              |                                              |                       |

|                   | After Instruct<br>CNT<br>Z<br>C | tion<br>=<br>=<br>= | 0x00<br>1<br>1            |              |                                              |                       |

| INCFSZ                                               | Incremen                                                                                                                                                                                                                                                                                          | t f, skip               | if O |                                            |

|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------|--------------------------------------------|

| Syntax:                                              | [ label ]                                                                                                                                                                                                                                                                                         | INCFSZ                  | f,d  |                                            |

| Operands:                                            | 0 ≤ f ≤ 255<br>d ∈ [0,1]                                                                                                                                                                                                                                                                          | 5                       |      |                                            |

| Operation:                                           | (f) + 1 $\rightarrow$ (skip if resu                                                                                                                                                                                                                                                               |                         |      |                                            |

| Status Affected:                                     | None                                                                                                                                                                                                                                                                                              |                         |      |                                            |

| Encoding:                                            | 0001                                                                                                                                                                                                                                                                                              | 111d                    | ffff | ffff                                       |

| Description:                                         | The contents of register 'f' are in-<br>mented. If 'd' is 0 the result is pla<br>WREG. If 'd' is 1 the result is pla-<br>back in register 'f'.<br>If the result is 0, the next instruct<br>which is already fetched, is disca<br>and an NOP is executed instead of<br>it a two-cycle instruction. |                         |      | placed in<br>blaced<br>uction,<br>scarded, |

| Words:                                               | 1                                                                                                                                                                                                                                                                                                 |                         |      |                                            |

| Cycles:                                              | 1(2)                                                                                                                                                                                                                                                                                              |                         |      |                                            |

| Q Cycle Activity:                                    |                                                                                                                                                                                                                                                                                                   |                         |      |                                            |

| Q1                                                   | Q2                                                                                                                                                                                                                                                                                                | Q3                      |      | Q4                                         |

| Decode                                               | Read<br>register 'f'                                                                                                                                                                                                                                                                              | Execu                   |      | Vrite to<br>stination                      |

| lf skip:                                             |                                                                                                                                                                                                                                                                                                   |                         |      |                                            |

| Q1                                                   | Q2                                                                                                                                                                                                                                                                                                | Q3                      |      | Q4                                         |

| Forced NOP                                           | NOP                                                                                                                                                                                                                                                                                               | Execu                   | te   | NOP                                        |

| Example:                                             | NZERO                                                                                                                                                                                                                                                                                             | INCFSZ<br>:<br>:        | CNT, | 1                                          |

| Before Instru<br>PC                                  |                                                                                                                                                                                                                                                                                                   | 6 (HERE)                |      |                                            |

| After Instruc<br>CNT<br>If CNT<br>PC<br>If CNT<br>PC | = CNT + 7<br>= 0;<br>= Address<br>≠ 0;                                                                                                                                                                                                                                                            | 1<br>S(ZERO)<br>S(NZERO | )    |                                            |

| NEGW         | V                            | Negate W                                                                                                                          |                                                             |

|--------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Syntax       | <b>K</b> :                   | [ <i>label</i> ] NEGW f,s                                                                                                         | ;                                                           |

| Opera        | nds:                         | 0 ≤ F ≤ 255<br>s ∈ [0,1]                                                                                                          |                                                             |

| Opera        | tion:                        | $\frac{\overline{WREG}}{\overline{WREG}} + 1 \to (f);$ $\overline{WREG} + 1 \to s$                                                |                                                             |

| Status       | Affected:                    | OV, C, DC, Z                                                                                                                      |                                                             |

| Encod        | ling:                        | 0010 110s f                                                                                                                       | fff ffff                                                    |

| Description: |                              | WREG is negated using<br>ment. If 's' is 0 the resul<br>WREG and data memo<br>'s' is 1 the result is plac<br>memory location 'f'. | t is placed in ry location 'f'. If                          |

| Words        | :                            | 1                                                                                                                                 |                                                             |

| Cycles       | 3:                           | 1                                                                                                                                 |                                                             |

| Q Cyc        | le Activity:                 |                                                                                                                                   |                                                             |

|              | Q1                           | Q2 Q3                                                                                                                             | Q4                                                          |

|              | Decode                       | Read Execute<br>register 'f'                                                                                                      | Write<br>register 'f'<br>and other<br>specified<br>register |

| Example:     |                              | NEGW REG, 0                                                                                                                       |                                                             |

| B            | efore Instru<br>WREG<br>REG  | ction<br>= 0011 1010 [0x3A],<br>= 1010 1011 [0xAB]                                                                                |                                                             |

| At           | fter Instruct<br>WREG<br>REG | ion<br>= 1100 0111 [0xC6]<br>= 1100 0111 [0xC6]                                                                                   |                                                             |

| NOF               | 2            | No Operation  |       |     |   |      |  |

|-------------------|--------------|---------------|-------|-----|---|------|--|

| Syntax:           |              | [ label ]     | NOP   |     |   |      |  |

| Ope               | rands:       | None          | None  |     |   |      |  |

| Ope               | ration:      | No opera      | tion  |     |   |      |  |

| Stat              | us Affected: | None          |       |     |   |      |  |

| Enc               | oding:       | 0000          | 0000  | 000 | 0 | 0000 |  |

| Des               | cription:    | No operation. |       |     |   |      |  |

| Wor               | ds:          | 1             | 1     |     |   |      |  |

| Cycl              | es:          | 1             | 1     |     |   |      |  |

| Q Cycle Activity: |              |               |       |     |   |      |  |

|                   | Q1           | Q2            | Q3    |     |   | Q4   |  |

|                   | Decode       | NOP           | Exect | ute |   | NOP  |  |

|                   |              |               |       |     |   |      |  |

Example:

None.

# Applicable Devices 42 R42 42A 43 R43 44

|           |       |                                | Standard Operating Conditions (unless otherwise stated)   |         |          |            |                                       |  |

|-----------|-------|--------------------------------|-----------------------------------------------------------|---------|----------|------------|---------------------------------------|--|

|           |       |                                | Operating temperature                                     |         |          |            |                                       |  |

| DC CHARA  | CTERI | STICS                          | $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial and |         |          |            |                                       |  |

|           |       |                                |                                                           |         | · ·      |            | $TA \leq +70^{\circ}C$ for commercial |  |

|           |       |                                | Operating                                                 | voltage | VDD rang | e as de    | escribed in Section 17.1              |  |

| Parameter |       |                                |                                                           |         |          |            |                                       |  |

| No.       | Sym   | Characteristic                 | Min                                                       | Тур†    | Max      | Units      | Conditions                            |  |

|           |       | Output Low Voltage             |                                                           |         |          |            |                                       |  |

| D080      | VOL   | I/O ports (except RA2 and RA3) | _                                                         | -       | 0.1VDD   | V          | IOL = 4 mA                            |  |

| D081      |       | with TTL buffer                | _                                                         | _       | 0.4      | V          | IOL = 6 mA, VDD = 4.5V                |  |

|           |       |                                |                                                           |         |          |            | Note 6                                |  |

| D082      |       | RA2 and RA3                    | _                                                         | _       | 3.0      | V          | IOL = 60.0 mA, VDD = 5.5V             |  |

| D083      |       | OSC2/CLKOUT                    | _                                                         | _       | 0.4      | v          | IOL = 2  mA,  VDD = 4.5  V            |  |

| 2000      |       | (RC and EC osc modes)          |                                                           |         | 0        |            |                                       |  |

|           |       | Output High Voltage (Note 3)   |                                                           |         |          |            |                                       |  |

| D090      | Vон   | I/O ports (except RA2 and RA3) | 0.9Vdd                                                    | _       | _        | v          | IOH = -2 mA                           |  |

| D091      | VOIT  | with TTL buffer                | 2.4                                                       |         |          |            | IOH = -6.0  mA,  VDD = 4.5  V         |  |

| 0001      |       |                                | 2.7                                                       |         |          | v          | Note 6                                |  |

| D092      |       | RA2 and RA3                    | _                                                         | _       | 12       | v          | Pulled-up to externally applied       |  |

| 0032      |       |                                | _                                                         |         | 12       | v          | voltage                               |  |

| D093      |       | OSC2/CLKOUT                    | 2.4                                                       | _       | _        | v          | IOH = -5  mA,  VDD = 4.5  V           |  |

| 0095      |       | (RC and EC osc modes)          | 2.4                                                       |         |          | v          | 10H = -3 HA, VDD = 4.3V               |  |

|           |       | Capacitive Loading Specs on    |                                                           |         |          |            |                                       |  |

|           |       | Output Pins                    |                                                           |         |          |            |                                       |  |

| D100      | Conce |                                |                                                           |         | 25 ++    | ~ <b>Г</b> | In EC or RC osc modes when            |  |

| 0100      | COSC2 | OSC2 pin                       | _                                                         | -       | 25 ††    | pF         |                                       |  |

|           |       |                                |                                                           |         |          |            | OSC2 pin is outputting<br>CLKOUT.     |  |

|           |       |                                |                                                           |         |          |            | External clock is used to drive       |  |

|           |       |                                |                                                           |         |          |            | OSC1.                                 |  |

| D101      | Сю    |                                |                                                           |         | 50 ±±    |            |                                       |  |

|           |       | All I/O pins and OSC2          | _                                                         | -       | 50 ††    | pF         |                                       |  |

| D400      | 0     | (in RC mode)                   |                                                           |         | 400 41   |            |                                       |  |

| D102      | CAD   | System Interface Bus           | -                                                         | -       | 100 ††   | pF         | In Microprocessor or                  |  |

|           |       | (PORTC, PORTD and PORTE)       |                                                           |         |          |            | Extended Microcontroller              |  |

|           |       |                                |                                                           |         |          |            | mode                                  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

the Design guidance to attain the AC timing specifications. These loads are not tested.

Note 1: In RC oscillator configuration, the OSC1 pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/Vpp pin may be kept in this range at times other than programming, but this is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

# Applicable Devices 42 R42 42A 43 R43 44

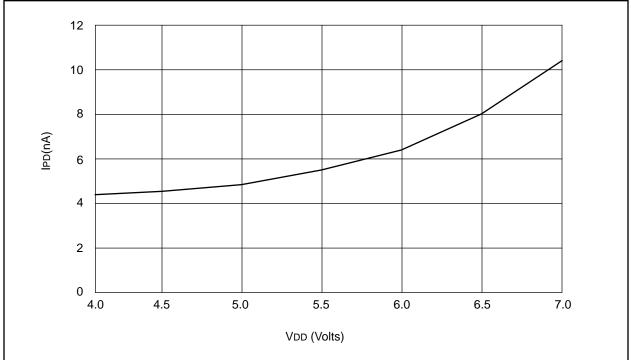

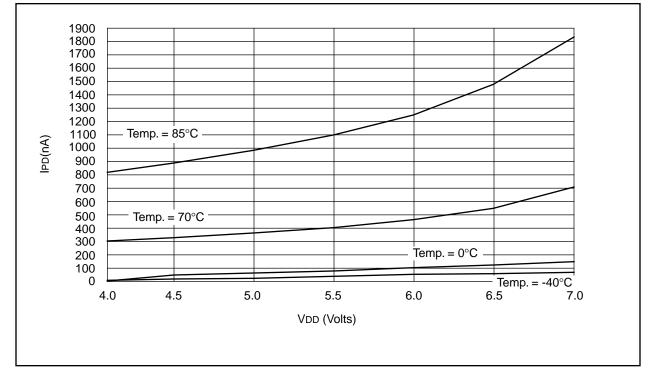

# FIGURE 18-9: TYPICAL IPD vs. VDD WATCHDOG DISABLED 25°C

FIGURE 18-10: MAXIMUM IPD vs. VDD WATCHDOG DISABLED

# Applicable Devices 42 R42 42A 43 R43 44

## FIGURE 18-13: WDT TIMER TIME-OUT PERIOD vs. VDD

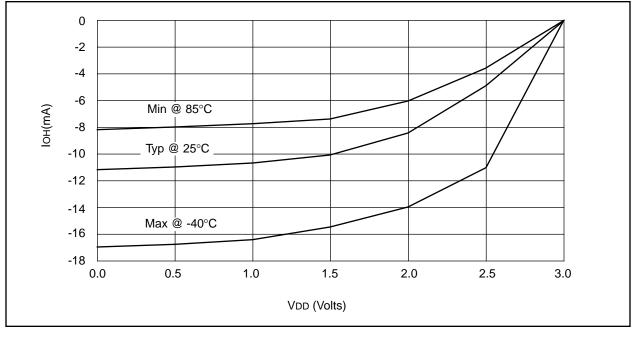

FIGURE 18-14: IOH vs. VOH, VDD = 3V

Applicable Devices 42 R42 42A 43 R43 44

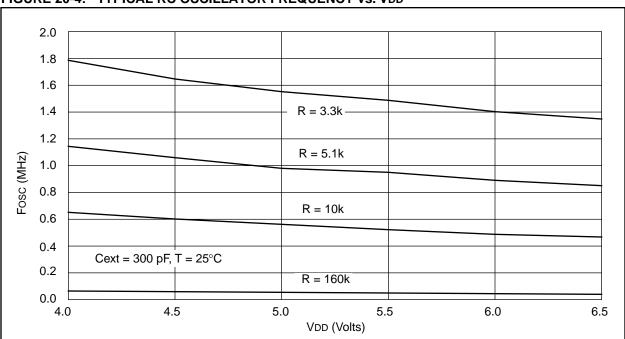

## FIGURE 20-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

## TABLE 20-2: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |       |

|--------|------|----------------------------|-------|

| 22 pF  | 10k  | 3.33 MHz                   | ± 12% |

|        | 100k | 353 kHz                    | ± 13% |

| 100 pF | 3.3k | 3.54 MHz                   | ± 10% |

|        | 5.1k | 2.43 MHz                   | ± 14% |

|        | 10k  | 1.30 MHz                   | ± 17% |

|        | 100k | 129 kHz                    | ± 10% |

| 300 pF | 3.3k | 1.54 MHz                   | ± 14% |

|        | 5.1k | 980 kHz                    | ± 12% |

|        | 10k  | 564 kHz                    | ± 16% |

|        | 160k | 35 kHz                     | ± 18% |

# **APPENDIX A: MODIFICATIONS**

The following is the list of modifications over the PIC16CXX microcontroller family:

- Instruction word length is increased to 16-bit. This allows larger page sizes both in program memory (8 Kwords verses 2 Kwords) and register file (256 bytes versus 128 bytes).

- 2. Four modes of operation: microcontroller, protected microcontroller, extended microcontroller, and microprocessor.

- 22 new instructions. The MOVF, TRIS and OPTION instructions have been removed.

- 4. 4 new instructions for transferring data between data memory and program memory. This can be used to "self program" the EPROM program memory.

- Single cycle data memory to data memory transfers possible (MOVPF and MOVFP instructions). These instructions do not affect the Working register (WREG).

- 6. W register (WREG) is now directly addressable.

- 7. A PC high latch register (PCLATH) is extended to 8-bits. The PCLATCH register is now both readable and writable.

- 8. Data memory paging is redefined slightly.

- 9. DDR registers replaces function of TRIS registers.

- 10. Multiple Interrupt vectors added. This can decrease the latency for servicing the interrupt.

- 11. Stack size is increased to 16 deep.

- 12. BSR register for data memory paging.

- 13. Wake up from SLEEP operates slightly differently.

- 14. The Oscillator Start-Up Timer (OST) and Power-Up Timer (PWRT) operate in parallel and not in series.

- 15. PORTB interrupt on change feature works on all eight port pins.

- 16. TMR0 is 16-bit plus 8-bit prescaler.

- 17. Second indirect addressing register added (FSR1 and FSR2). Configuration bits can select the FSR registers to auto-increment, auto-decrement, remain unchanged after an indirect address.

- 18. Hardware multiplier added (8 x 8  $\rightarrow$  16-bit) (PIC17C43 and PIC17C44 only).

- 19. Peripheral modules operate slightly differently.

- 20. Oscillator modes slightly redefined.

- 21. Control/Status bits and registers have been placed in different registers and the control bit for globally enabling interrupts has inverse polarity.

- 22. Addition of a test mode pin.

- 23. In-circuit serial programming is not implemented.

# **APPENDIX B: COMPATIBILITY**

To convert code written for PIC16CXX to PIC17CXX, the user should take the following steps:

- 1. Remove any TRIS and OPTION instructions, and implement the equivalent code.

- 2. Separate the interrupt service routine into its four vectors.

- 3. Replace:

4.

| <pre>MOVF REG1, W with: MOVFP REG1, WREG Replace: MOVF REG1, W MOVWF REG2 with: MOVPF REG1, REG2 ; Addr(REG1)&lt;20h or MOVFP REG1, REG2 ; Addr(REG2)&lt;20h</pre> |          |       |                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-----------------------|