Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 8MHz                                                                       |

| Connectivity               | UART/USART                                                                 |

| Peripherals                | POR, PWM, WDT                                                              |

| Number of I/O              | 33                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | OTP                                                                        |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 454 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                  |

| Data Converters            | -                                                                          |

| Oscillator Type            | External                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 44-TQFP                                                                    |

| Supplier Device Package    | 44-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc43-08i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 OVERVIEW

This data sheet covers the PIC17C4X group of the PIC17CXX family of microcontrollers. The following devices are discussed in this data sheet:

- PIC17C42

- PIC17CR42

- PIC17C42A

- PIC17C43

- PIC17CR43

- PIC17C44

The PIC17CR42, PIC17C42A, PIC17C43, PIC17CR43, and PIC17C44 devices include architectural enhancements over the PIC17C42. These enhancements will be discussed throughout this data sheet.

The PIC17C4X devices are 40/44-Pin, EPROM/ROM-based members of the versatile PIC17CXX family of low-cost, high-performance, CMOS, fully-static, 8-bit microcontrollers.

All PIC16/17 microcontrollers employ an advanced RISC architecture. The PIC17CXX has enhanced core features, 16-level deep stack, and multiple internal and external interrupt sources. The separate instruction and data buses of the Harvard architecture allow a 16-bit wide instruction word with a separate 8-bit wide data. The two stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches (which require two cycles). A total of 55 instructions (reduced instruction set) are available in the PIC17C42 and 58 instructions in all the other devices. Additionally, a large register set gives some of the architectural innovations used to achieve a very high performance. For mathematical intensive applications all devices, except the PIC17C42, have a single cycle 8 x 8 Hardware Multiplier.

PIC17CXX microcontrollers typically achieve a 2:1 code compression and a 4:1 speed improvement over other 8-bit microcontrollers in their class.

PIC17C4X devices have up to 454 bytes of RAM and 33 I/O pins. In addition, the PIC17C4X adds several peripheral features useful in many high performance applications including:

- · Four timer/counters

- Two capture inputs

- Two PWM outputs

- A Universal Synchronous Asynchronous Receiver Transmitter (USART)

These special features reduce external components, thus reducing cost, enhancing system reliability and reducing power consumption. There are four oscillator options, of which the single pin RC oscillator provides a low-cost solution, the LF oscillator is for low frequency crystals and minimizes power consumption, XT is a standard crystal, and the EC is for external clock input. The SLEEP (power-down) mode offers additional power saving. The user can wake-up the chip from SLEEP through several external and internal interrupts and device resets.

There are four configuration options for the device operational modes:

- Microprocessor

- Microcontroller

- Extended microcontroller

- Protected microcontroller

The microprocessor and extended microcontroller modes allow up to 64K-words of external program memory.

A highly reliable Watchdog Timer with its own on-chip RC oscillator provides protection against software malfunction.

Table 1-1 lists the features of the PIC17C4X devices.

A UV-erasable CERDIP-packaged version is ideal for code development while the cost-effective One-Time Programmable (OTP) version is suitable for production in any volume.

The PIC17C4X fits perfectly in applications ranging from precise motor control and industrial process control to automotive, instrumentation, and telecom applications. Other applications that require extremely fast execution of complex software programs or the flexibility of programming the software code as one of the last steps of the manufacturing process would also be well suited. The EPROM technology makes customization of application programs (with unique security codes, combinations, model numbers, parameter storage, etc.) fast and convenient. Small footprint package options make the PIC17C4X ideal for applications with space limitations that require high performance. High speed execution, powerful peripheral features, flexible I/O, and low power consumption all at low cost make the PIC17C4X ideal for a wide range of embedded control applications.

# 1.1 Family and Upward Compatibility

Those users familiar with the PIC16C5X and PIC16CXX families of microcontrollers will see the architectural enhancements that have been implemented. These enhancements allow the device to be more efficient in software and hardware requirements. Please refer to Appendix A for a detailed list of enhancements and modifications. Code written for PIC16C5X or PIC16CXX can be easily ported to PIC17CXX family of devices (Appendix B).

# 1.2 Development Support

The PIC17CXX family is supported by a full-featured macro assembler, a software simulator, an in-circuit emulator, a universal programmer, a "C" compiler, and fuzzy logic support tools.

<sup>© 1996</sup> Microchip Technology Inc.

NOTES:

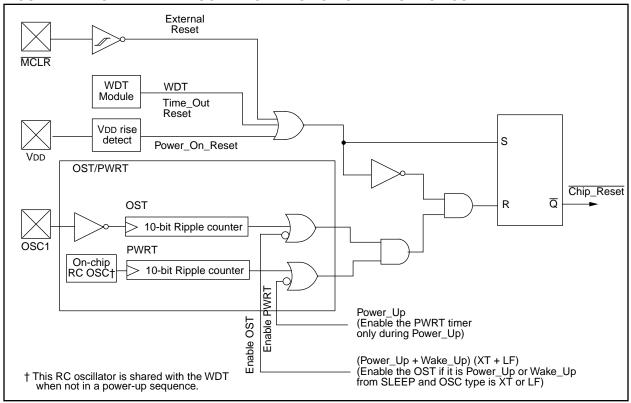

# 4.0 RESET

The PIC17CXX differentiates between various kinds of reset:

- Power-on Reset (POR)

- MCLR reset during normal operation

- WDT Reset (normal operation)

Some registers are not affected in any reset condition; their status is unknown on POR and unchanged in any other reset. Most other registers are forced to a "reset state" on Power-on Reset (POR), on  $\overline{\text{MCLR}}$  or WDT Reset and on  $\overline{\text{MCLR}}$  reset during SLEEP. They are not affected by a WDT Reset during SLEEP, since this reset is viewed as the resumption of normal operation. The  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different reset situations as indicated in Table 4-3. These bits are used in software to determine the nature of reset. See Table 4-4 for a full description of reset states of all registers.

**Note:** While the device is in a reset state, the internal phase clock is held in the Q1 state. Any processor mode that allows external execution will force the RE0/ALE pin as a low output and the RE1/OE and RE2/WR pins as high outputs.

A simplified block diagram of the on-chip reset circuit is shown in Figure 4-1.

# 4.1 <u>Power-on Reset (POR), Power-up</u> <u>Timer (PWRT), and Oscillator Start-up</u> <u>Timer (OST)</u>

# 4.1.1 POWER-ON RESET (POR)

The Power-on Reset circuit holds the device in reset until VDD is above the trip point (in the range of 1.4V -2.3V). The PIC17C42 does not produce an internal reset when VDD declines. All other devices will produce an internal reset for both rising and falling VDD. To take advantage of the POR, just tie the MCLR/VPP pin directly (or through a resistor) to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A minimum rise time for VDD is required. See Electrical Specifications for details.

# 4.1.2 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 96 ms time-out (nominal) on power-up. This occurs from rising edge of the POR signal and after the first rising edge of  $\overline{\text{MCLR}}$  (detected high). The Power-up Timer operates on an internal RC oscillator. The chip is kept in RESET as long as the PWRT is active. In most cases the PWRT delay allows the VDD to rise to an acceptable level.

The power-up time delay will vary from chip to chip and to VDD and temperature. See DC parameters for details.

# FIGURE 4-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

© 1996 Microchip Technology Inc.

| TABLE 6-3: | SPECIAL FUNCTION REGISTERS |

|------------|----------------------------|

|------------|----------------------------|

| Address            | Name          | Bit 7                                    | Bit 6                                                                  | Bit 5        | Bit 4        | Bit 3        | Bit 2           | Bit 1          | Bit 0           | Value on<br>Power-on<br>Reset | Value on all<br>other<br>resets (3) |

|--------------------|---------------|------------------------------------------|------------------------------------------------------------------------|--------------|--------------|--------------|-----------------|----------------|-----------------|-------------------------------|-------------------------------------|

| Unbank             | ed            | •                                        |                                                                        |              |              | •            |                 |                | •               |                               |                                     |

| 00h                | INDF0         | Uses con                                 | tents of FSI                                                           | R0 to addres | s data mem   | ory (not a p | hysical regis   | ster)          |                 |                               |                                     |

| 01h                | FSR0          | Indirect d                               | ata memory                                                             | address po   | inter 0      |              |                 |                |                 | XXXX XXXX                     | uuuu uuuu                           |

| 02h                | PCL           | Low orde                                 | r 8-bits of P                                                          | 0000 0000    | 0000 0000    |              |                 |                |                 |                               |                                     |

| 03h <sup>(1)</sup> | PCLATH        | Holding re                               | egister for u                                                          | 0000 0000    | uuuu uuuu    |              |                 |                |                 |                               |                                     |

| 04h                | ALUSTA        | FS3                                      | FS2                                                                    | FS1          | FS0          | OV           | Z               | DC             | С               | 1111 xxxx                     | 1111 uuuu                           |

| 05h                | TOSTA         | INTEDG                                   | TOSE                                                                   | TOCS         | PS3          | PS2          | PS1             | PS0            | —               | 0000 000-                     | 0000 000-                           |

| 06h <b>(2)</b>     | CPUSTA        | _                                        | _                                                                      | STKAV        | GLINTD       | TO           | PD              | _              | _               | 11 11                         | 11 qq                               |

| 07h                | INTSTA        | PEIF                                     | TOCKIF                                                                 | T0IF         | INTF         | PEIE         | TOCKIE          | TOIE           | INTE            | 0000 0000                     | 0000 0000                           |

| 08h                | INDF1         | Uses con                                 | Uses contents of FSR1 to address data memory (not a physical register) |              |              |              |                 |                |                 |                               |                                     |

| 09h                | FSR1          | Indirect d                               | ata memory                                                             | xxxx xxxx    | uuuu uuuu    |              |                 |                |                 |                               |                                     |

| 0Ah                | WREG          | Working register                         |                                                                        |              |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

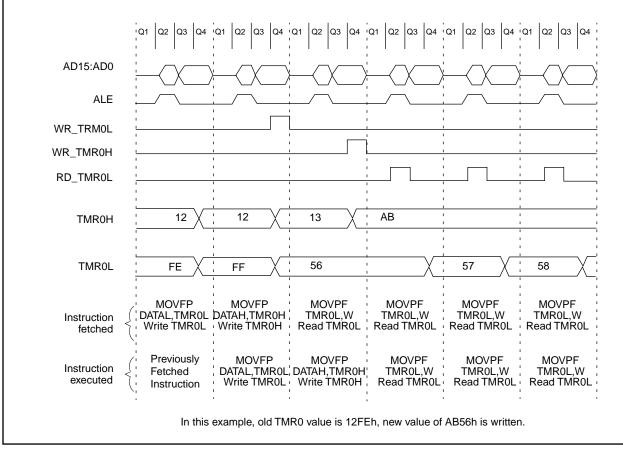

| 0Bh                | TMR0L         | TMR0 register; low byte                  |                                                                        |              |              |              |                 |                | xxxx xxxx       | uuuu uuuu                     |                                     |

| 0Ch                | TMR0H         | TMR0 register; high byte                 |                                                                        |              |              |              |                 |                | xxxx xxxx       | uuuu uuuu                     |                                     |

| 0Dh                | TBLPTRL       | Low byte of program memory table pointer |                                                                        |              |              |              |                 |                |                 | (4)                           | (4)                                 |

| 0Eh                | TBLPTRH       | High byte                                | High byte of program memory table pointer                              |              |              |              |                 |                |                 |                               | (4)                                 |

| 0Fh                | BSR           | Bank sele                                | ect register                                                           |              |              |              |                 |                |                 | 0000 0000                     | 0000 0000                           |

| Bank 0             |               | 1                                        |                                                                        |              |              |              |                 |                |                 | I                             |                                     |

| 10h                | PORTA         | RBPU                                     | _                                                                      | RA5          | RA4          | RA3          | RA2             | RA1/T0CKI      | RA0/INT         | 0-xx xxxx                     | 0-uu uuuu                           |

| 11h                | DDRB          | Data dire                                | ction registe                                                          | er for PORTE | 3            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 12h                | PORTB         | PORTB d                                  | ata latch                                                              |              |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 13h                | RCSTA         | SPEN                                     | RX9                                                                    | SREN         | CREN         | —            | FERR            | OERR           | RX9D            | 0000 -00x                     | 0000 -00u                           |

| 14h                | RCREG         | Serial por                               | t receive re                                                           | gister       |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 15h                | TXSTA         | CSRC                                     | TX9                                                                    | TXEN         | SYNC         | —            | —               | TRMT           | TX9D            | 00001x                        | 00001u                              |

| 16h                | TXREG         | Serial por                               | t transmit re                                                          | egister      |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| 17h                | SPBRG         | Baud rate                                | generator                                                              | register     |              |              |                 |                |                 | xxxx xxxx                     | uuuu uuuu                           |

| Bank 1             |               |                                          |                                                                        |              |              |              |                 |                |                 |                               |                                     |

| 10h                | DDRC          | Data dire                                | ction registe                                                          | er for PORT  | 2            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 11h                | PORTC         | RC7/<br>AD7                              | RC6/<br>AD6                                                            | RC5/<br>AD5  | RC4/<br>AD4  | RC3/<br>AD3  | RC2/<br>AD2     | RC1/<br>AD1    | RC0/<br>AD0     | xxxx xxxx                     | uuuu uuuu                           |

| 12h                | DDRD          | Data dire                                | ction registe                                                          | er for PORTI | )            |              |                 |                |                 | 1111 1111                     | 1111 1111                           |

| 4.01-              | PORTD         | RD7/<br>AD15                             | RD6/<br>AD14                                                           | RD5/<br>AD13 | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10    | RD1/<br>AD9    | RD0/<br>AD8     | xxxx xxxx                     | uuuu uuuu                           |

| 13h                |               | Data dira                                | ction reaiste                                                          | er for PORTE | -            |              |                 | 1              |                 | 111                           | 111                                 |

| 13h<br>14h         | DDRE          | Data dire                                |                                                                        |              |              |              |                 | -              |                 |                               |                                     |

|                    | DDRE<br>PORTE | Data dire                                | _                                                                      | _            | _            | _            | RE2/WR          | RE1/OE         | RE0/ALE         | xxx                           | uuu                                 |

| 14h                |               | RBIF                                     | —<br>TMR3IF                                                            | —<br>TMR2IF  | —<br>TMR1IF  | —<br>CA2IF   | RE2/WR<br>CA1IF | RE1/OE<br>TXIF | RE0/ALE<br>RCIF | xxx<br>0000 0010              | uuu<br>0000 0010                    |

x = unknown, u = unchanged, - = unimplemented read as '0', q - value depends on condition. Shaded cells are unimplemented, read as '0'. The upper byte of the program counter is not directly accessible. PCLATH is a holding register for PC<15:8> whose contents are updated Legend: Note 1:

from or transferred to the upper byte of the program counter. The TO and PD status bits in CPUSTA are not affected by a MCLR reset. 2:

3: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

4:

The following values are for both TBLPTRL and TBLPTRH: All PIC17C4X devices (Power-on Reset 0000 0000) and (All other resets 0000 0000) except the PIC17C42 (Power-on Reset xxxx xxxx) and (All other resets uuuu uuuu)

5: The PRODL and PRODH registers are not implemented on the PIC17C42.

# TABLE 9-7: PORTD FUNCTIONS

| Name     | Bit  | Buffer Type | Function                                     |

|----------|------|-------------|----------------------------------------------|

| RD0/AD8  | bit0 | TTL         | Input/Output or system bus address/data pin. |

| RD1/AD9  | bit1 | TTL         | Input/Output or system bus address/data pin. |

| RD2/AD10 | bit2 | TTL         | Input/Output or system bus address/data pin. |

| RD3/AD11 | bit3 | TTL         | Input/Output or system bus address/data pin. |

| RD4/AD12 | bit4 | TTL         | Input/Output or system bus address/data pin. |

| RD5/AD13 | bit5 | TTL         | Input/Output or system bus address/data pin. |

| RD6/AD14 | bit6 | TTL         | Input/Output or system bus address/data pin. |

| RD7/AD15 | bit7 | TTL         | Input/Output or system bus address/data pin. |

Legend: TTL = TTL input.

# TABLE 9-8: REGISTERS/BITS ASSOCIATED WITH PORTD

| Address     | Name  | Bit 7        | Bit 6         | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1       | Bit 0       | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|--------------|---------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------------------------|-----------------------------------------|

| 13h, Bank 1 | PORTD | RD7/<br>AD15 | RD6/<br>AD14  | RD5/<br>AD13 | RD4/<br>AD12 | RD3/<br>AD11 | RD2/<br>AD10 | RD1/<br>AD9 | RD0/<br>AD8 | XXXX XXXX                     | uuuu uuuu                               |

| 12h, Bank 1 | DDRD  | Data direc   | ction registe | er for PORTI | 5            |              |              |             |             | 1111 1111                     | 1111 1111                               |

Legend: x = unknown, u = unchanged.

Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

NOTES:

| Address       | Name   | Bit 7    | Bit 6          | Bit 5 | Bit 4  | Bit 3 | Bit 2         | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|--------|----------|----------------|-------|--------|-------|---------------|-------|-------|-------------------------------|-----------------------------------------|

| 05h, Unbanked | TOSTA  | INTEDG   | T0SE           | TOCS  | PS3    | PS2   | PS1           | PS0   |       | 0000 000-                     | 0000 000-                               |

| 06h, Unbanked | CPUSTA | —        | _              | STKAV | GLINTD | TO    | PD            | _     | _     | 11 11                         | 11 qq                                   |

| 07h, Unbanked | INTSTA | PEIF     | TOCKIF         | T0IF  | INTF   | PEIE  | <b>T0CKIE</b> | TOIE  | INTE  | 0000 0000                     | 0000 0000                               |

| 0Bh, Unbanked | TMR0L  | TMR0 reg | ister; low byt | e     |        |       |               |       |       | xxxx xxxx                     | uuuu uuuu                               |

| 0Ch, Unbanked | TMR0H  | TMR0 reg | ister; high by | /te   |        |       |               |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', g - value depends on condition, Shaded cells are not used by Timer0. Note 1: Other (non power-up) resets include: external reset through MCLR and the Watchdog Timer Reset.

# PIC17C4X

| BAUD<br>RATE | Fosc = 3 | 3 MHz  | SPBRG<br>value | Fosc = 2 | 5 MHz  | SPBRG<br>value | Fosc = 2 | 0 MHz  | SPBRG<br>value | Fosc = 1 | 6 MHz  | SPBRG<br>value |

|--------------|----------|--------|----------------|----------|--------|----------------|----------|--------|----------------|----------|--------|----------------|

| (K)          | KBAUD    | %ERROR | (decimal)      |

| 0.3          | NA       | _      | _              | NA       | _      | _              | NA       | _      | _              | NA       |        | _              |

| 1.2          | NA       | _      | _              |

| 2.4          | NA       | _      | _              | NA       | _      | _              | NA       | _      | _              | NA       | —      | _              |

| 9.6          | NA       | —      | —              |

| 19.2         | NA       | _      | —              | NA       | —      | —              | 19.53    | +1.73  | 255            | 19.23    | +0.16  | 207            |

| 76.8         | 77.10    | +0.39  | 106            | 77.16    | +0.47  | 80             | 76.92    | +0.16  | 64             | 76.92    | +0.16  | 51             |

| 96           | 95.93    | -0.07  | 85             | 96.15    | +0.16  | 64             | 96.15    | +0.16  | 51             | 95.24    | -0.79  | 41             |

| 300          | 294.64   | -1.79  | 27             | 297.62   | -0.79  | 20             | 294.1    | -1.96  | 16             | 307.69   | +2.56  | 12             |

| 500          | 485.29   | -2.94  | 16             | 480.77   | -3.85  | 12             | 500      | 0      | 9              | 500      | 0      | 7              |

| HIGH         | 8250     | _      | 0              | 6250     | _      | 0              | 5000     | _      | 0              | 4000     | _      | 0              |

| LOW          | 32.22    | _      | 255            | 24.41    | _      | 255            | 19.53    | _      | 255            | 15.625   | _      | 255            |

| BAUD                                                                 | Fosc = 10 M                                                    | Hz                                              | SPBRG                                               | Fosc = 7.159                                                         | MHz                                        | SPBRG                                             | SPBRG                                                       |                 |                             |

|----------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------|-------------------------------------------------------------|-----------------|-----------------------------|

| RATE<br>(K)                                                          | KBAUD                                                          | %ERROR                                          | value<br>(decimal)                                  | KBAUD                                                                | %ERROR                                     | value<br>(decimal)                                | KBAUD                                                       | %ERROR          | value<br>(decimal)          |

| 0.3                                                                  | NA                                                             | _                                               | _                                                   | NA                                                                   | _                                          | _                                                 | NA                                                          | _               | _                           |

| 1.2                                                                  | NA                                                             | _                                               | _                                                   | NA                                                                   | _                                          | _                                                 | NA                                                          | _               | _                           |

| 2.4                                                                  | NA                                                             | _                                               | _                                                   | NA                                                                   | _                                          | _                                                 | NA                                                          | _               | _                           |

| 9.6                                                                  | 9.766                                                          | +1.73                                           | 255                                                 | 9.622                                                                | +0.23                                      | 185                                               | 9.6                                                         | 0               | 131                         |

| 19.2                                                                 | 19.23                                                          | +0.16                                           | 129                                                 | 19.24                                                                | +0.23                                      | 92                                                | 19.2                                                        | 0               | 65                          |

| 76.8                                                                 | 75.76                                                          | -1.36                                           | 32                                                  | 77.82                                                                | +1.32                                      | 22                                                | 79.2                                                        | +3.13           | 15                          |

| 96                                                                   | 96.15                                                          | +0.16                                           | 25                                                  | 94.20                                                                | -1.88                                      | 18                                                | 97.48                                                       | +1.54           | 12                          |

| 300                                                                  | 312.5                                                          | +4.17                                           | 7                                                   | 298.3                                                                | -0.57                                      | 5                                                 | 316.8                                                       | +5.60           | 3                           |

| 500                                                                  | 500                                                            | 0                                               | 4                                                   | NA                                                                   | _                                          | _                                                 | NA                                                          | _               | _                           |

| HIGH                                                                 | 2500                                                           | _                                               | 0                                                   | 1789.8                                                               | _                                          | 0                                                 | 1267                                                        | _               | 0                           |

| LOW                                                                  | 9.766                                                          | —                                               | 255                                                 | 6.991                                                                | —                                          | 255                                               | 4.950                                                       | —               | 255                         |

|                                                                      | Fosc = 3.579                                                   | NAL 1-                                          |                                                     | Fosc = 1 MH                                                          | -                                          |                                                   | Fosc = 32.76                                                | 9 VU7           |                             |

| BAUD                                                                 | FOSC = 3.579                                                   | MHZ                                             | SPBRG                                               |                                                                      | Z                                          | SPBRG                                             | 030 = 32.70                                                 |                 | SPBRG                       |

| BAUD<br>RATE<br>(K)                                                  | KBAUD                                                          | MHZ<br>%ERROR                                   | SPBRG<br>value<br>(decimal)                         | KBAUD                                                                | 2<br>%ERROR                                | SPBRG<br>value<br>(decimal)                       | KBAUD                                                       | %ERROR          | SPBRG<br>value<br>(decimal) |

| RATE                                                                 |                                                                |                                                 | value                                               |                                                                      |                                            | value                                             |                                                             |                 | value                       |

| RATE<br>(K)                                                          | KBAUD                                                          |                                                 | value                                               | KBAUD                                                                |                                            | value                                             | KBAUD                                                       | %ERROR          | value<br>(decimal)          |

| RATE<br>(K)<br>0.3                                                   | KBAUD                                                          |                                                 | value                                               | KBAUD<br>NA                                                          | %ERROR                                     | value<br>(decimal)                                | KBAUD<br>0.303                                              | %ERROR<br>+1.14 | value<br>(decimal)<br>26    |

| RATE<br>(K)<br>0.3<br>1.2                                            | KBAUD<br>NA<br>NA                                              |                                                 | value                                               | KBAUD<br>NA<br>1.202                                                 | %ERROR<br>                                 | value<br>(decimal)<br>—<br>207                    | KBAUD<br>0.303<br>1.170                                     | %ERROR<br>+1.14 | value<br>(decimal)<br>26    |

| RATE<br>(K)<br>0.3<br>1.2<br>2.4                                     | KBAUD<br>NA<br>NA<br>NA                                        | %ERROR<br>                                      | value<br>(decimal)<br>—<br>—<br>—                   | KBAUD<br>NA<br>1.202<br>2.404                                        | %ERROR<br><br>+0.16<br>+0.16               | value<br>(decimal)<br><br>207<br>103              | KBAUD<br>0.303<br>1.170<br>NA                               | %ERROR<br>+1.14 | value<br>(decimal)<br>26    |

| RATE<br>(K)<br>0.3<br>1.2<br>2.4<br>9.6                              | KBAUD<br>NA<br>NA<br>NA<br>9.622                               | %ERROR<br>—<br>—<br>+0.23                       | value<br>(decimal)<br>—<br>—<br>—<br>92             | KBAUD<br>NA<br>1.202<br>2.404<br>9.615                               | %ERROR<br>+0.16<br>+0.16<br>+0.16          | value<br>(decimal)<br>—<br>207<br>103<br>25       | KBAUD<br>0.303<br>1.170<br>NA<br>NA                         | %ERROR<br>+1.14 | value<br>(decimal)<br>26    |

| RATE<br>(K)<br>0.3<br>1.2<br>2.4<br>9.6<br>19.2                      | KBAUD<br>NA<br>NA<br>9.622<br>19.04                            | %ERROR<br>—<br>—<br>+0.23<br>-0.83              | value<br>(decimal)<br>—<br>—<br>92<br>46            | KBAUD<br>NA<br>1.202<br>2.404<br>9.615<br>19.24                      | %ERROR<br>+0.16<br>+0.16<br>+0.16<br>+0.16 | value<br>(decimal)<br>—<br>207<br>103<br>25<br>12 | KBAUD<br>0.303<br>1.170<br>NA<br>NA<br>NA                   | %ERROR<br>+1.14 | value<br>(decimal)<br>26    |

| RATE<br>(K)<br>0.3<br>1.2<br>2.4<br>9.6<br>19.2<br>76.8              | KBAUD<br>NA<br>NA<br>9.622<br>19.04<br>74.57                   | %ERROR<br>—<br>—<br>+0.23<br>-0.83<br>-2.90     | value<br>(decimal)<br>—<br>—<br>—<br>92<br>46<br>11 | KBAUD<br>NA<br>1.202<br>2.404<br>9.615<br>19.24<br>83.34             | %ERROR<br>+0.16<br>+0.16<br>+0.16<br>+0.16 | value<br>(decimal)<br>—<br>207<br>103<br>25<br>12 | KBAUD<br>0.303<br>1.170<br>NA<br>NA<br>NA<br>NA             | %ERROR<br>+1.14 | value<br>(decimal)<br>26    |

| RATE<br>(K)<br>0.3<br>1.2<br>2.4<br>9.6<br>19.2<br>76.8<br>96        | KBAUD<br>NA<br>NA<br>9.622<br>19.04<br>74.57<br>99.43          | %ERROR<br>—<br>+0.23<br>-0.83<br>-2.90<br>_3.57 | value<br>(decimal)<br>—<br>—<br>92<br>46<br>11<br>8 | KBAUD<br>NA<br>1.202<br>2.404<br>9.615<br>19.24<br>83.34<br>NA       | %ERROR<br>+0.16<br>+0.16<br>+0.16<br>+0.16 | value<br>(decimal)<br>—<br>207<br>103<br>25<br>12 | KBAUD<br>0.303<br>1.170<br>NA<br>NA<br>NA<br>NA<br>NA       | %ERROR<br>+1.14 | value<br>(decimal)<br>26    |

| RATE<br>(K)<br>0.3<br>1.2<br>2.4<br>9.6<br>19.2<br>76.8<br>96<br>300 | KBAUD<br>NA<br>NA<br>9.622<br>19.04<br>74.57<br>99.43<br>298.3 | %ERROR<br>—<br>+0.23<br>-0.83<br>-2.90<br>_3.57 | value<br>(decimal)<br>—<br>—<br>92<br>46<br>11<br>8 | KBAUD<br>NA<br>1.202<br>2.404<br>9.615<br>19.24<br>83.34<br>NA<br>NA | %ERROR<br>+0.16<br>+0.16<br>+0.16<br>+0.16 | value<br>(decimal)<br>—<br>207<br>103<br>25<br>12 | KBAUD<br>0.303<br>1.170<br>NA<br>NA<br>NA<br>NA<br>NA<br>NA | %ERROR<br>+1.14 | value<br>(decimal)<br>26    |

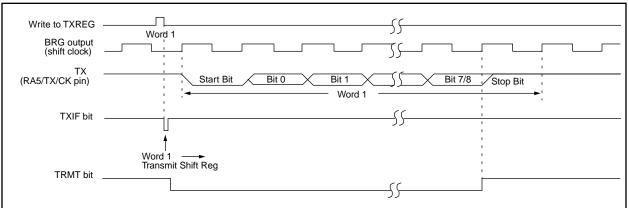

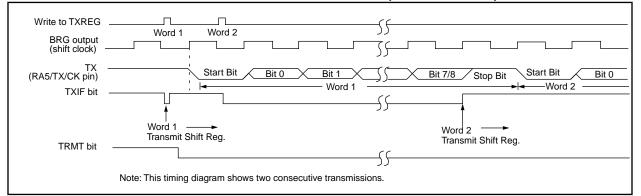

# FIGURE 13-5: ASYNCHRONOUS MASTER TRANSMISSION

# FIGURE 13-6: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

# TABLE 13-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address     | Name  | Bit 7       | Bit 6       | Bit 5    | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-------------|-------------|----------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR   | RBIF        | TMR3IF      | TMR2IF   | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA | SPEN        | RX9         | SREN     | CREN   | —     | FERR  | OERR  | RX9D  | x00- 0000                     | 0000 -00u                               |

| 16h, Bank 0 | TXREG | Serial port | transmit re | egister  |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE   | RBIE        | TMR3IE      | TMR2IE   | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA | CSRC        | TX9         | TXEN     | SYNC   | —     | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | SPBRG | Baud rate   | generator   | register |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

# 14.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits to deal with the needs of real time applications. The PIC17CXX family has a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving operating modes and offer code protection. These are:

- OSC selection

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- · Code protection

The PIC17CXX has a Watchdog Timer which can be shut off only through EPROM bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 96 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. With these two timers on-chip, most applications need no external reset circuitry.

The SLEEP mode is designed to offer a very low current power-down mode. The user can wake from SLEEP through external reset, Watchdog Timer Reset or through an interrupt. Several oscillator options are also made available to allow the part to fit the application. The RC oscillator option saves system cost while the LF crystal option saves power. Configuration bits are used to select various options. This configuration word has the format shown in Figure 14-1.

| <u>R/P - 1</u><br>PM2 <sup>(1)</sup> | U - x                                                       | U - x                                  | <u>U-x</u>                             | U - x       | U - x   | <u>U-x</u> | U - x         |                                                                                                                 |

|--------------------------------------|-------------------------------------------------------------|----------------------------------------|----------------------------------------|-------------|---------|------------|---------------|-----------------------------------------------------------------------------------------------------------------|

| bit15-7                              |                                                             |                                        | _                                      |             |         |            | bit0          |                                                                                                                 |

| U - x                                | R/P - 1                                                     | U - x                                  | <u>R/P - 1</u>                         | R/P - 1     | R/P - 1 | R/P - 1    | R/P - 1       | R = Readable bit                                                                                                |

| <br>bit15-7                          | PM1                                                         |                                        | PM0                                    | WDTPS1      | WDTPS0  | FOSC1      | FOSC0<br>bit0 | P = Programmable bit $P = Programmable bit$ $U = Unimplemented$ $- n = Value for Erased Device$ $(x = unknown)$ |

| bit 15-9:                            | Unimpler                                                    | nented: R                              | ead as a                               | '1'         |         |            |               |                                                                                                                 |

|                                      |                                                             | rocontrolle<br>ended mic<br>de protect | er mode<br>crocontrol<br>ed microc     | ontroller m | ode     |            |               |                                                                                                                 |

| bit 7, 5:                            | Unimpler                                                    | nented: R                              | ead as a                               | '0'         |         |            |               |                                                                                                                 |

| bit 3-2:                             | 11 = WD<br>10 = WD<br>01 = WD                               | Γ enabled<br>Γ enabled<br>Γ enabled    | , postscal<br>, postscal<br>, postscal | er = 256    |         |            |               |                                                                                                                 |

| bit 1-0:                             | FOSC1:F<br>11 = EC (<br>10 = XT (<br>01 = RC (<br>00 = LF ( | oscillator<br>oscillator<br>oscillator | scillator S                            | elect bits  |         |            |               |                                                                                                                 |

|                                      |                                                             |                                        |                                        |             |         |            |               |                                                                                                                 |

# FIGURE 14-1: CONFIGURATION WORD

<sup>© 1996</sup> Microchip Technology Inc.

# PIC17C4X

| BTFSS Bit Test, skip if Set                                                                            |           |                                                                                                                                                                                                                                                            |                   |              |         |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|---------|--|--|--|--|

| Syntax:                                                                                                |           | [label]                                                                                                                                                                                                                                                    | [label] BTFSS f,b |              |         |  |  |  |  |

| Operands                                                                                               | 8:        |                                                                                                                                                                                                                                                            | $0 \le f \le 127$ |              |         |  |  |  |  |

|                                                                                                        |           | 0 ≤ b < 7                                                                                                                                                                                                                                                  | $0 \le b < 7$     |              |         |  |  |  |  |

| Operation                                                                                              | n:        | skip if (f<                                                                                                                                                                                                                                                | :b>) = 1          |              |         |  |  |  |  |

| Status Af                                                                                              | fected:   | None                                                                                                                                                                                                                                                       |                   |              |         |  |  |  |  |

| Encoding                                                                                               | :         | 1001                                                                                                                                                                                                                                                       | 0bbb              | ffff         | ffff    |  |  |  |  |

| Descriptio                                                                                             | on:       | If bit 'b' in register 'f' is 1 then the next<br>instruction is skipped.<br>If bit 'b' is 1, then the next instruction<br>fetched during the current instruction exe-<br>cution, is discarded and an NOP is exe-<br>cuted instead, making this a two-cycle |                   |              |         |  |  |  |  |

|                                                                                                        |           | instruction                                                                                                                                                                                                                                                |                   | y this a two | J-Cycle |  |  |  |  |

| Words:                                                                                                 |           | 1                                                                                                                                                                                                                                                          | 1                 |              |         |  |  |  |  |

| Cycles:                                                                                                |           | 1(2)                                                                                                                                                                                                                                                       |                   |              |         |  |  |  |  |

| Q Cycle A                                                                                              | Activity: |                                                                                                                                                                                                                                                            |                   |              |         |  |  |  |  |

|                                                                                                        | Q1        | Q2                                                                                                                                                                                                                                                         | Q3                | 1            | Q4      |  |  |  |  |

| De                                                                                                     | ecode     | Read<br>register 'f'                                                                                                                                                                                                                                       | Execu             | ute          | NOP     |  |  |  |  |

| lf skip:                                                                                               |           |                                                                                                                                                                                                                                                            |                   |              |         |  |  |  |  |

|                                                                                                        | Q1        | Q2                                                                                                                                                                                                                                                         | Q3                |              | Q4      |  |  |  |  |

| Forc                                                                                                   | ed NOP    | NOP                                                                                                                                                                                                                                                        | Execu             | ute          | NOP     |  |  |  |  |

| <u>Example</u> :                                                                                       |           | HERE<br>FALSE<br>TRUE                                                                                                                                                                                                                                      | BTFSS<br>:<br>:   | FLAG,1       |         |  |  |  |  |

| Before Instruction<br>PC = address (HERE)                                                              |           |                                                                                                                                                                                                                                                            |                   |              |         |  |  |  |  |

| After Instruction<br>If FLAG<1> = 0;<br>PC = address (FALSE)<br>If FLAG<1> = 1;<br>PC = address (TRUE) |           |                                                                                                                                                                                                                                                            |                   |              |         |  |  |  |  |

| BTG                | Bit Toggl               | e f                                |             |                         |  |  |  |

|--------------------|-------------------------|------------------------------------|-------------|-------------------------|--|--|--|

| Syntax:            | [label] E               | [label] BTG f,b                    |             |                         |  |  |  |

| Operands:          | 0 ≤ f ≤ 25<br>0 ≤ b < 7 | $0 \le f \le 255$<br>$0 \le b < 7$ |             |                         |  |  |  |

| Operation:         | $(\overline{f}) \to$    | (f <b>)</b>                        |             |                         |  |  |  |

| Status Affected:   | None                    |                                    |             |                         |  |  |  |

| Encoding:          | 0011                    | 1bbb                               | ffff        | ffff                    |  |  |  |

| Description:       | Bit 'b' in da inverted. | ta memory                          | location 'f | f' is                   |  |  |  |

| Words:             | 1                       |                                    |             |                         |  |  |  |

| Cycles:            | 1                       |                                    |             |                         |  |  |  |

| Q Cycle Activity:  |                         |                                    |             |                         |  |  |  |

| Q1                 | Q2                      | Q3                                 | (           |                         |  |  |  |

|                    |                         |                                    |             | Q4                      |  |  |  |

| Decode             | Read<br>register 'f'    | Execute                            | -           | Q4<br>/rite<br>ster 'f' |  |  |  |

| Decode<br>Example: | register 'f'            | Execute                            | regi        | /rite                   |  |  |  |

|                    | BTG                     |                                    | regi<br>4   | /rite                   |  |  |  |

# PIC17C4X

| MOVLR                                                                                 | Move Literal to high nibble in BSR                                                                                                                                                                                                                                          |                  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|--|--|

| Syntax:                                                                               | [ <i>label</i> ] MOVLR k                                                                                                                                                                                                                                                    |                  |  |  |  |  |  |

| Operands:                                                                             | $0 \le k \le 15$                                                                                                                                                                                                                                                            | $0 \le k \le 15$ |  |  |  |  |  |

| Operation:                                                                            | $k \rightarrow (BSR < 7:4>)$                                                                                                                                                                                                                                                |                  |  |  |  |  |  |

| Status Affected:                                                                      | None                                                                                                                                                                                                                                                                        |                  |  |  |  |  |  |

| Encoding:                                                                             | 1011 101x kkkk uuuu                                                                                                                                                                                                                                                         |                  |  |  |  |  |  |

| Description:                                                                          | The 4-bit literal 'k' is loaded into the<br>most significant 4-bits of the Bank<br>Select Register (BSR). Only the high<br>4-bits of the Bank Select Register<br>are affected. The lower half of the<br>BSR is unchanged. The assembler<br>will encode the "u" fields as 0. |                  |  |  |  |  |  |

| Words:                                                                                | 1                                                                                                                                                                                                                                                                           |                  |  |  |  |  |  |

| Cycles:                                                                               | 1                                                                                                                                                                                                                                                                           |                  |  |  |  |  |  |

| Q Cycle Activity:                                                                     |                                                                                                                                                                                                                                                                             |                  |  |  |  |  |  |

| Q1                                                                                    | Q2 Q3 Q4                                                                                                                                                                                                                                                                    |                  |  |  |  |  |  |

| Decode                                                                                | Read literal         Execute         Write           'k:u'         literal 'k' to         BSR<7:4>                                                                                                                                                                          |                  |  |  |  |  |  |

| Example:                                                                              | MOVLR 5                                                                                                                                                                                                                                                                     |                  |  |  |  |  |  |

| Before Instruction<br>BSR register = 0x22<br>After Instruction<br>BSR register = 0x52 |                                                                                                                                                                                                                                                                             |                  |  |  |  |  |  |

| Note: This i                                                                          | instruction is not available in th<br>C42 device.                                                                                                                                                                                                                           | e                |  |  |  |  |  |

| MOVLW             | Move Lite            | Move Literal to WREG                           |      |                  |  |  |  |

|-------------------|----------------------|------------------------------------------------|------|------------------|--|--|--|

| Syntax:           | [ label ]            | MOVLW                                          | / k  |                  |  |  |  |

| Operands:         | $0 \le k \le 25$     | 55                                             |      |                  |  |  |  |

| Operation:        | $k \rightarrow (WR)$ | EG)                                            |      |                  |  |  |  |

| Status Affected:  | None                 |                                                |      |                  |  |  |  |

| Encoding:         | 1011                 | 0000                                           | kkkł | k kkkk           |  |  |  |

| Description:      | The eight b<br>WREG. | The eight bit literal 'k' is loaded into WREG. |      |                  |  |  |  |

| Words:            | 1                    |                                                |      |                  |  |  |  |

| Cycles:           | 1                    |                                                |      |                  |  |  |  |

| Q Cycle Activity: |                      |                                                |      |                  |  |  |  |

| Q1                | Q2                   | Q3                                             | 3    | Q4               |  |  |  |

| Decode            | Read<br>literal 'k'  | Execu                                          | ute  | Write to<br>WREG |  |  |  |

| Example:          | MOVLW                | 0x5A                                           |      |                  |  |  |  |

| After Instruction |                      |                                                |      |                  |  |  |  |

WREG = 0x5A

# TABLE 17-1:CROSS REFERENCE OF DEVICE SPECS FOR OSCILLATOR CONFIGURATIONS<br/>AND FREQUENCIES OF OPERATION (COMMERCIAL DEVICES)

| OSC | PIC17C42-16                              | PIC17C42-25                              |

|-----|------------------------------------------|------------------------------------------|

| RC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 6 mA max.                           | IDD: 6 mA max.                           |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 4 MHz max.                         | Freq: 4 MHz max.                         |

| XT  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| EC  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 24 mA max.                          | IDD: 38 mA max.                          |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 16 MHz max.                        | Freq: 25 MHz max.                        |

| LF  | VDD: 4.5V to 5.5V                        | VDD: 4.5V to 5.5V                        |

|     | IDD: 150 μA max. at 32 kHz (WDT enabled) | IDD: 150 μA max. at 32 kHz (WDT enabled) |

|     | IPD: 5 μA max. at 5.5V (WDT disabled)    | IPD: 5 μA max. at 5.5V (WDT disabled)    |

|     | Freq: 2 MHz max.                         | Freq: 2 MHz max.                         |

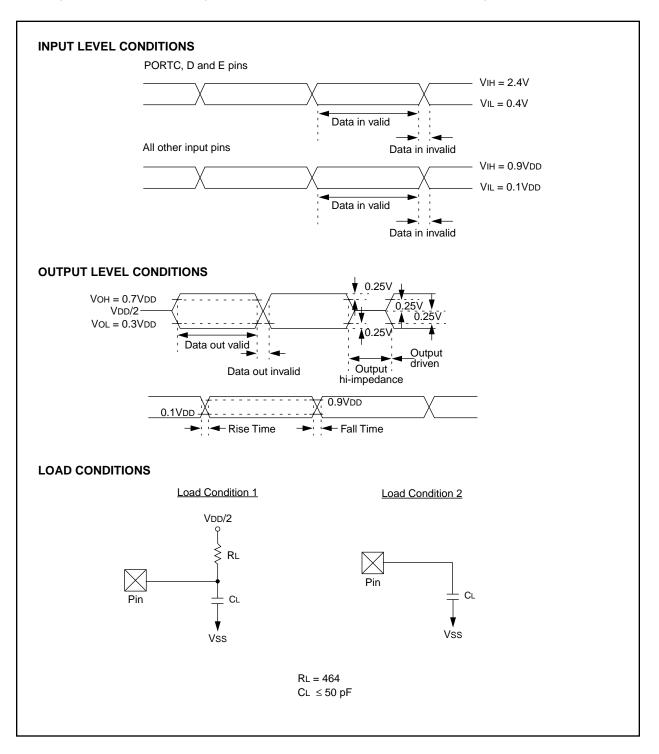

# FIGURE 17-1: PARAMETER MEASUREMENT INFORMATION

All timings are measure between high and low measurement points as indicated in the figures below.

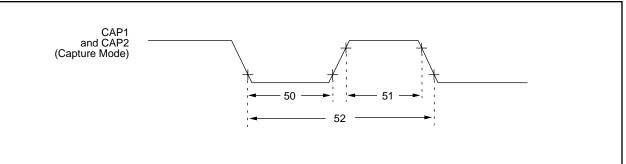

# FIGURE 17-7: CAPTURE TIMINGS

# TABLE 17-7: CAPTURE REQUIREMENTS

| Parameter |      |                                       |                     |      |     |       |                                 |

|-----------|------|---------------------------------------|---------------------|------|-----|-------|---------------------------------|

| No.       | Sym  | Characteristic                        | Min                 | Тур† | Max | Units | Conditions                      |

| 50        | TccL | Capture1 and Capture2 input low time  | 10 *                | —    | —   | ns    |                                 |

| 51        | TccH | Capture1 and Capture2 input high time | 10 *                | —    | _   | ns    |                                 |

| 52        | TccP | Capture1 and Capture2 input period    | <u>2 Tcy</u> §<br>N | —    | —   | ns    | N = prescale value<br>(4 or 16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

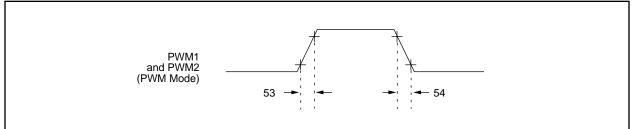

# FIGURE 17-8: PWM TIMINGS

# TABLE 17-8: PWM REQUIREMENTS

| Parameter<br>No. | Sym  | Characteristic                 | Min | Тур† | Max   | Units | Conditions |

|------------------|------|--------------------------------|-----|------|-------|-------|------------|

| 53               | TccR | PWM1 and PWM2 output rise time | _   | 10 * | 35 *§ | ns    |            |

| 54               | TccF | PWM1 and PWM2 output fall time | —   | 10 * | 35 *§ | ns    |            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

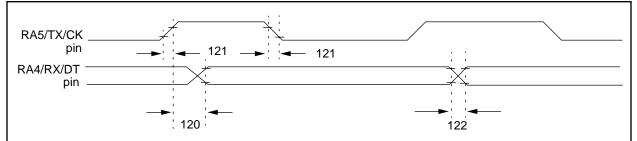

# FIGURE 17-9: USART MODULE: SYNCHRONOUS TRANSMISSION (MASTER/SLAVE) TIMING

# TABLE 17-9: SERIAL PORT SYNCHRONOUS TRANSMISSION REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                             | Min | Тур† | Мах | Units | Conditions |

|------------------|----------|------------------------------------------------------------|-----|------|-----|-------|------------|

| 120              | TckH2dtV | SYNC XMIT (MASTER & SLAVE)<br>Clock high to data out valid | _   | _    | 65  | ns    |            |

| 121              | TckRF    | Clock out rise time and fall time (Master Mode)            | _   | 10   | 35  | ns    |            |

| 122              | TdtRF    | Data out rise time and fall time                           |     | 10   | 35  | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

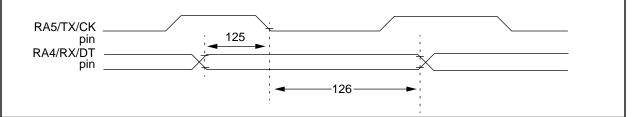

# FIGURE 17-10: USART MODULE: SYNCHRONOUS RECEIVE (MASTER/SLAVE) TIMING

# TABLE 17-10: SERIAL PORT SYNCHRONOUS RECEIVE REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                   | Min | Тур† | Max | Units | Conditions |

|------------------|----------|------------------------------------------------------------------|-----|------|-----|-------|------------|

| 125              | TdtV2ckL | SYNC RCV (MASTER & SLAVE)<br>Data hold before CK↓ (DT hold time) | 15  | _    | _   | ns    |            |

| 126              | TckL2dtl | Data hold after CK $\downarrow$ (DT hold time)                   | 15  | —    | _   | ns    |            |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

# PIC17C4X

# Applicable Devices 42 R42 42A 43 R43 44

# 19.4 <u>Timing Parameter Symbology</u>

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2 | opS                                  | 3. Tcc:st | (I <sup>2</sup> C specifications only) |

|----------|--------------------------------------|-----------|----------------------------------------|

| 2. TppS  |                                      | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т        |                                      |           |                                        |

| F        | Frequency                            | Т         | Time                                   |

| Lowerc   | ase symbols (pp) and their meanings: |           |                                        |

| рр       |                                      |           |                                        |

| ad       | Address/Data                         | ost       | Oscillator Start-Up Timer              |

| al       | ALE                                  | pwrt      | Power-Up Timer                         |

| сс       | Capture1 and Capture2                | rb        | PORTB                                  |

| ck       | CLKOUT or clock                      | rd        | RD                                     |

| dt       | Data in                              | rw        | RD or WR                               |

| in       | INT pin                              | tO        | TOCKI                                  |

| io       | I/O port                             | t123      | TCLK12 and TCLK3                       |

| mc       | MCLR                                 | wdt       | Watchdog Timer                         |

| oe       | ŌĒ                                   | wr        | WR                                     |

| os       | OSC1                                 |           |                                        |

| Upperc   | ase symbols and their meanings:      |           |                                        |

| S        |                                      |           |                                        |

| D        | Driven                               | L         | Low                                    |

| E        | Edge                                 | Р         | Period                                 |

| F        | Fall                                 | R         | Rise                                   |

| Н        | High                                 | V         | Valid                                  |

| 1        | Invalid (Hi-impedance)               | Z         | Hi-impedance                           |

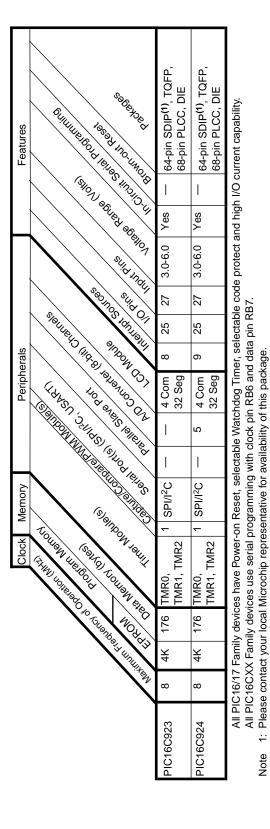

# E.7 <u>PIC16C9XX Family Of Devices</u>

# **ON-LINE SUPPORT**