Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessorPICCore Size8-BitSpeed8MHz         |                    |

|------------------------------------------------------------------------|--------------------|

| Core Size 8-Bit                                                        |                    |

|                                                                        |                    |

| Speed 8MHz                                                             |                    |

|                                                                        |                    |

| Connectivity UART/USART                                                |                    |

| Peripherals POR, PWM, WDT                                              |                    |

| Number of I/O 33                                                       |                    |

| Program Memory Size 8KB (4K x 16)                                      |                    |

| Program Memory Type OTP                                                |                    |

| EEPROM Size -                                                          |                    |

| RAM Size 454 x 8                                                       |                    |

| Voltage - Supply (Vcc/Vdd) 2.5V ~ 6V                                   |                    |

| Data Converters -                                                      |                    |

| Oscillator Type External                                               |                    |

| Operating Temperature -40°C ~ 85°C (TA)                                |                    |

| Mounting Type Surface Mount                                            |                    |

| Package / Case 44-LCC (J-Lead)                                         |                    |

| Supplier Device Package44-PLCC (16.59x16.59)                           |                    |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology | y/pic17lc43t-08i-l |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1-1: PIC17CXX FAMILY OF DEVICES

| Features                                                                |          | PIC17C42             | PIC17CR42            | PIC17C42A                 | PIC17C43             | PIC17CR43   | PIC17C44    |

|-------------------------------------------------------------------------|----------|----------------------|----------------------|---------------------------|----------------------|-------------|-------------|

| Maximum Frequency of O                                                  | peration | 25 MHz               | 33 MHz               | 33 MHz                    | 33 MHz               | 33 MHz      | 33 MHz      |

| Operating Voltage Range                                                 |          | 4.5 - 5.5V           | 2.5 - 6.0V           | 2.5 - 6.0V 2.5 - 6.0V 2.5 |                      | 2.5 - 6.0V  | 2.5 - 6.0V  |

| Program Memory x16                                                      | (EPROM)  | 2K                   | -                    | 2K                        | 4K                   | -           | 8K          |

|                                                                         | (ROM)    | -                    | 2K                   | -                         | -                    | 4K          | -           |

| Data Memory (bytes)                                                     |          | 232                  | 232                  | 232                       | 454                  | 454         | 454         |

| Hardware Multiplier (8 x 8                                              | )        | -                    | Yes                  | Yes                       | Yes                  | Yes         | Yes         |

| Timer0 (16-bit + 8-bit post                                             | scaler)  | Yes                  | Yes                  | Yes                       | Yes                  | Yes         | Yes         |

| Timer1 (8-bit)                                                          |          | Yes                  | Yes                  | Yes                       | Yes                  | Yes         | Yes         |

| Timer2 (8-bit)                                                          |          | Yes                  | Yes                  | Yes                       | Yes                  | Yes         | Yes         |

| Timer3 (16-bit)                                                         |          | Yes                  | Yes                  | Yes                       | Yes Yes              |             | Yes         |

| Capture inputs (16-bit)                                                 |          | 2                    | 2                    | 2                         | 2                    | 2           | 2           |

| PWM outputs (up to 10-bit                                               | t)       | 2                    | 2                    | 2                         | 2                    | 2           | 2           |

| USART/SCI                                                               |          | Yes                  | Yes                  | Yes                       | Yes                  | Yes         | Yes         |

| Power-on Reset                                                          |          | Yes                  | Yes                  | Yes                       | s Yes Yes            |             | Yes         |

| Watchdog Timer                                                          |          | Yes                  | Yes                  | Yes                       | Yes Yes              |             | Yes         |

| External Interrupts                                                     |          | Yes                  | Yes                  | Yes                       | Yes                  | Yes         | Yes         |

| Interrupt Sources                                                       |          | 11                   | 11                   | 11                        | 11                   | 11          | 11          |

| Program Memory Code P                                                   | rotect   | Yes                  | Yes                  | Yes                       | Yes                  | Yes         | Yes         |

| I/O Pins                                                                |          | 33                   | 33                   | 33                        | 33                   | 33          | 33          |

| I/O High Current Capabil-                                               | Source   | 25 mA                | 25 mA                | 25 mA                     | 25 mA                | 25 mA       | 25 mA       |

| ity Sink 25 mA <sup>(1)</sup> 25 mA <sup>(1)</sup> 25 mA <sup>(1)</sup> |          | 25 mA <sup>(1)</sup> | 25 mA <sup>(1)</sup> | 25 mA <sup>(1)</sup>      | 25 mA <sup>(1)</sup> |             |             |

| Package Types                                                           |          | 40-pin DIP           | 40-pin DIP           | 40-pin DIP                |                      |             | 40-pin DIP  |

|                                                                         |          | 44-pin PLCC          | 44-pin PLCC          | 44-pin PLCC 44-pin PL     |                      | 44-pin PLCC | 44-pin PLCC |

|                                                                         |          | 44-pin MQFP          | 44-pin MQFP          |                           |                      | 44-pin MQFP | 44-pin MQFP |

|                                                                         |          |                      | 44-pin TQFP          | 44-pin TQFP               | 44-pin TQFP          | 44-pin TQFP | 44-pin TQFP |

Note 1: Pins RA2 and RA3 can sink up to 60 mA.

NOTES:

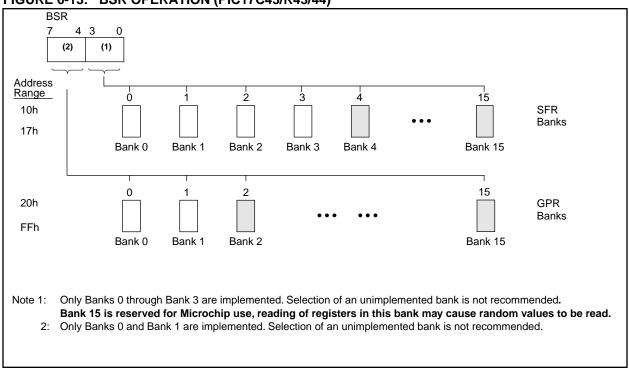

#### 6.8 Bank Select Register (BSR)

The BSR is used to switch between banks in the data memory area (Figure 6-13). In the PIC17C42, PIC17CR42, and PIC17C42A only the lower nibble is implemented. While in the PIC17C43, PIC17CR43, and PIC17C44 devices, the entire byte is implemented. The lower nibble is used to select the peripheral register bank. The upper nibble is used to select the general purpose memory bank.

All the Special Function Registers (SFRs) are mapped into the data memory space. In order to accommodate the large number of registers, a banking scheme has been used. A segment of the SFRs, from address 10h to address 17h, is banked. The lower nibble of the bank select register (BSR) selects the currently active "peripheral bank." Effort has been made to group the peripheral registers of related functionality in one bank. However, it will still be necessary to switch from bank to bank in order to address all peripherals related to a single task. To assist this, a MOVLB bank instruction is in the instruction set. For the PIC17C43, PIC17CR43, and PIC17C44 devices, the need for a large general purpose memory space dictated a general purpose RAM banking scheme. The upper nibble of the BSR selects the currently active general purpose RAM bank. To assist this, a MOVLR bank instruction has been provided in the instruction set.

If the currently selected bank is not implemented (such as Bank 13), any read will read all '0's. Any write is completed to the bit bucket and the ALU status bits will be set/cleared as appropriate.

**Note:** Registers in Bank 15 in the Special Function Register area, are reserved for Microchip use. Reading of registers in this bank may cause random values to be read.

#### FIGURE 6-13: BSR OPERATION (PIC17C43/R43/44)

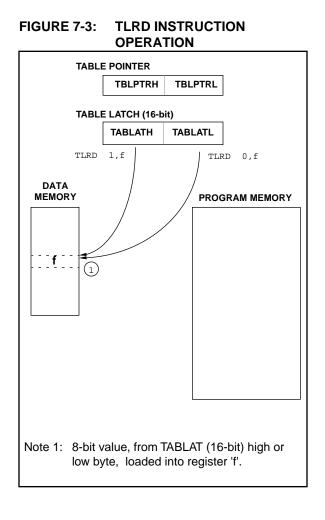

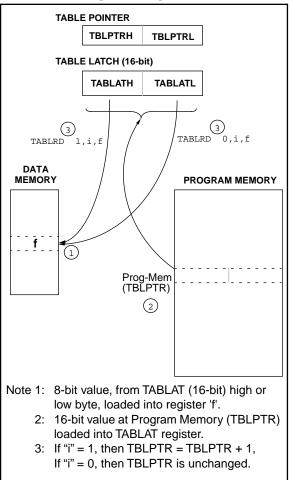

#### FIGURE 7-4: TABLRD INSTRUCTION OPERATION

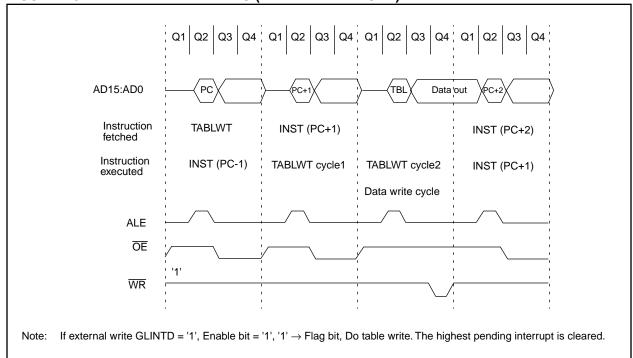

#### 7.2 <u>Table Writes to External Memory</u>

Table writes to external memory are always two-cycle instructions. The second cycle writes the data to the external memory location. The sequence of events for an external memory write are the same for an internal write.

| Note: | If an interrupt is pending or occurs during the TABLWT, the two cycle table write |

|-------|-----------------------------------------------------------------------------------|

|       | completes. The RA0/INT, TMR0, or T0CKI                                            |

|       | interrupt flag is automatically cleared or                                        |

|       | the pending peripheral interrupt is                                               |

|       | acknowledged.                                                                     |

7.2.2 TABLE WRITE CODE

The "i" operand of the TABLWT instruction can specify that the value in the 16-bit TBLPTR register is automatically incremented for the next write. In Example 7-1, the TBLPTR register is not automatically incremented.

#### EXAMPLE 7-1: TABLE WRITE

| CLRWDT |                 | ; | Clear WDT      |

|--------|-----------------|---|----------------|

| MOVLW  | HIGH (TBL_ADDR) | ; | Load the Table |

| MOVWF  | TBLPTRH         | ; | address        |

| MOVLW  | LOW (TBL_ADDR)  | ; |                |

| MOVWF  | TBLPTRL         | ; |                |

| MOVLW  | HIGH (DATA)     | ; | Load HI byte   |

| TLWT   | 1, WREG         | ; | in TABLATCH    |

| MOVLW  | LOW (DATA)      | ; | Load LO byte   |

| TABLWT | 0,0,WREG        | ; | in TABLATCH    |

|        |                 | ; | and write to   |

|        |                 | ; | program memory |

|        |                 | ; | (Ext. SRAM)    |

|        |                 |   |                |

#### FIGURE 7-5: TABLWT WRITE TIMING (EXTERNAL MEMORY)

NOTES:

#### 13.1 USART Baud Rate Generator (BRG)

The BRG supports both the Asynchronous and Synchronous modes of the USART. It is a dedicated 8-bit baud rate generator. The SPBRG register controls the period of a free running 8-bit timer. Table 13-1 shows the formula for computation of the baud rate for different USART modes. These only apply when the USART is in synchronous master mode (internal clock) and asynchronous mode.

Given the desired baud rate and Fosc, the nearest integer value between 0 and 255 can be calculated using the formula below. The error in baud rate can then be determined.

#### TABLE 13-1: BAUD RATE FORMULA

| SYNC | Mode         | Baud Rate      |

|------|--------------|----------------|

| 0    | Asynchronous | Fosc/(64(X+1)) |

| 1    | Synchronous  | Fosc/(4(X+1))  |

X = value in SPBRG (0 to 255)

Example 13-1 shows the calculation of the baud rate error for the following conditions:

Fosc = 16 MHz Desired Baud Rate = 9600 SYNC = 0

#### EXAMPLE 13-1: CALCULATING BAUD RATE ERROR

Desired Baud rate=Fosc / (64 (X + 1))

$9600 = \frac{16000000}{(64 (X + 1))}$

X = 25.042 = 25

Calculated Baud Rate=16000000 / (64 (25 + 1))

= 9615

- Error = <u>(Calculated Baud Rate Desired Baud Rate)</u> Desired Baud Rate

- = (9615 9600) / 9600

- = 0.16%

Writing a new value to the SPBRG, causes the BRG timer to be reset (or cleared), this ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

#### TABLE 13-2: REGISTERS ASSOCIATED WITH BAUD RATE GENERATOR

| Address     | Name                                           | Bit 7 | Bit 6                        | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|------------------------------------------------|-------|------------------------------|-------|-------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 13h, Bank 0 | RCSTA                                          | SPEN  | RX9                          | SREN  | CREN  | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0 | TXSTA                                          | CSRC  | CSRC TX9 TXEN SYNC TRMT TX9D |       |       |       |       |       |       |                               | 00001u                                  |

| 17h, Bank 0 | 17h, Bank 0 SPBRG Baud rate generator register |       |                              |       |       |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used by the Baud Rate Generator. $Note 1: Other (non power-up) resets include: external reset through <math>\overline{MCLR}$  and Watchdog Timer Reset.

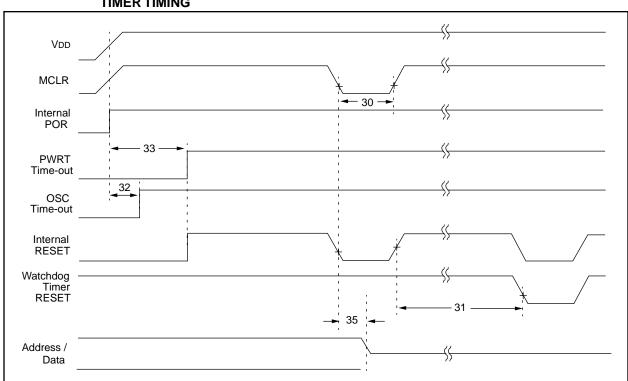

## FIGURE 17-4: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

## TABLE 17-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                   | Min   | Тур†        | Max   | Units | Conditions         |

|------------------|----------|--------------------------------------------------|-------|-------------|-------|-------|--------------------|

| 30               | TmcL     | MCLR Pulse Width (low)                           | 100 * | _           |       | ns    |                    |

| 31               | Twdt     | Watchdog Timer Time-out Period<br>(Prescale = 1) | 5 *   | 12          | 25 *  | ms    |                    |

| 32               | Tost     | Oscillation Start-up Timer Period                |       | 1024 Tosc § |       | ms    | Tosc = OSC1 period |

| 33               | Tpwrt    | Power-up Timer Period                            | 40 *  | 96          | 200 * | ms    |                    |

| 35               | TmcL2adI | MCLR to System Interface bus (AD15:AD0) invalid  | _     | —           | 100 * | ns    |                    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

§ This specification ensured by design.

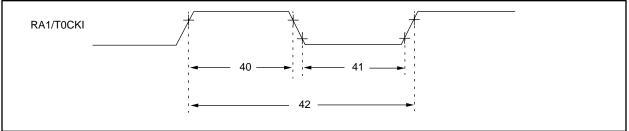

#### FIGURE 17-5: TIMER0 CLOCK TIMINGS

#### TABLE 17-5: TIMER0 CLOCK REQUIREMENTS

| Parameter |      |                        |                |                   |      |     |       |                    |

|-----------|------|------------------------|----------------|-------------------|------|-----|-------|--------------------|

| No.       | Sym  | Characteristic         |                | Min               | Тур† | Max | Units | Conditions         |

| 40        | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5TCY + 20 §     | —    | _   | ns    |                    |

|           |      |                        | With Prescaler | 10*               | —    | —   | ns    |                    |

| 41        | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20 §     | —    | —   | ns    |                    |

|           |      |                        | With Prescaler | 10*               | —    | —   | ns    |                    |

| 42        | Tt0P | T0CKI Period           | ·              | <u>Tcy + 40</u> § | —    | —   | ns    | N = prescale value |

|           |      |                        |                | N                 |      |     |       | (1, 2, 4,, 256)    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

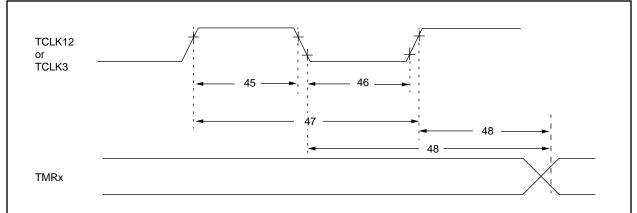

#### FIGURE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK TIMINGS

#### TABLE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK REQUIREMENTS

| Parameter |           |                                                               |                        | Тур |          |       |                                    |

|-----------|-----------|---------------------------------------------------------------|------------------------|-----|----------|-------|------------------------------------|

| No.       | Sym       | Characteristic                                                | Min                    | †   | Max      | Units | Conditions                         |

| 45        | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5 TCY + 20 §         |     | _        | ns    |                                    |

| 46        | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5 TCY + 20 §         |     |          | ns    |                                    |

| 47        | Tt123P    | TCLK12 and TCLK3 input period                                 | <u>Tcy + 40</u> §<br>N |     |          | ns    | N = prescale value<br>(1, 2, 4, 8) |

| 48        | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc §                |     | 6 Tosc § | _     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

## 19.1 DC CHARACTERISTICS:

#### PIC17CR42/42A/43/R43/44-16 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-25 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-33 (Commercial, Industrial)

| DC CHARACI       | FEDIOTI | <u></u>                                                          | Standard Operating Conditions (unless otherwise stated) Operating temperature |      |      |       |                                           |  |  |  |

|------------------|---------|------------------------------------------------------------------|-------------------------------------------------------------------------------|------|------|-------|-------------------------------------------|--|--|--|

| DC CHARACI       | ERISTI  | 63                                                               |                                                                               |      |      | -40°C |                                           |  |  |  |

|                  |         | i                                                                |                                                                               |      |      | 0°C   | $\leq$ TA $\leq$ +70°C for commercial     |  |  |  |

| Parameter<br>No. | Sym     | Characteristic                                                   | Min                                                                           | Тур† | Мах  | Units | Conditions                                |  |  |  |

| D001             | Vdd     | Supply Voltage                                                   | 4.5                                                                           | -    | 6.0  | V     |                                           |  |  |  |

| D002             | Vdr     | RAM Data Retention<br>Voltage (Note 1)                           | 1.5 *                                                                         | -    | -    | V     | Device in SLEEP mode                      |  |  |  |

| D003             | VPOR    | VDD start voltage to<br>ensure internal<br>Power-on Reset signal | _                                                                             | Vss  | -    | V     | See section on Power-on Reset for details |  |  |  |

| D004             | Svdd    | VDD rise rate to<br>ensure internal<br>Power-on Reset signal     | 0.060 *                                                                       | _    | _    | mV/ms | See section on Power-on Reset for details |  |  |  |

| D010             | IDD     | Supply Current                                                   | _                                                                             | 3    | 6    | mA    | Fosc = 4 MHz (Note 4)                     |  |  |  |

| D011             |         | (Note 2)                                                         | _                                                                             | 6    | 12 * | mA    | Fosc = 8 MHz                              |  |  |  |

| D012             |         |                                                                  | -                                                                             | 11   | 24 * | mA    | Fosc = 16 MHz                             |  |  |  |

| D013             |         |                                                                  | -                                                                             | 19   | 38   | mA    | Fosc = 25 MHz                             |  |  |  |

| D015             |         |                                                                  | -                                                                             | 25   | 50   | mA    | Fosc = 33 MHz                             |  |  |  |

| D014             |         |                                                                  | -                                                                             | 95   | 150  | μA    | Fosc = 32 kHz,                            |  |  |  |

|                  |         |                                                                  |                                                                               |      |      |       | WDT enabled (EC osc configuration)        |  |  |  |

| D020             | IPD     | Power-down                                                       | _                                                                             | 10   | 40   | μA    | VDD = 5.5V, WDT enabled                   |  |  |  |

| D021             |         | Current (Note 3)                                                 | -                                                                             | < 1  | 5    | μA    | VDD = 5.5V, WDT disabled                  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in SLEEP mode without losing RAM data.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors such as I/O pin loading and switching rate, oscillator type, internal code execution pattern, and temperature also have an impact on the current consumption.

The test conditions for all IDD measurements in active operation mode are:

OSC1 = external square wave, from rail to rail; all I/O pins tristated, pulled to VDD or VSS, T0CKI = VDD,  $\overline{MCLR}$  = VDD; WDT enabled/disabled as specified.

Current consumed from the oscillator and I/O's driving external capacitive or resistive loads needs to be considered.

For the RC oscillator, the current through the external pull-up resistor (R) can be estimated as:  $VDD / (2 \bullet R)$ . For capacitive loads, the current can be estimated (for an individual I/O pin) as (CL • VDD) • f

CL = Total capacitive load on the I/O pin; f = average frequency the I/O pin switches.

The capacitive currents are most significant when the device is configured for external execution (includes extended microcontroller mode).

- 3: The power down current in SLEEP mode does not depend on the oscillator type. Power-down current is measured with the part in SLEEP mode, with all I/O pins in hi-impedance state and tied to VDD and Vss.

- 4: For RC osc configuration, current through Rext is not included. The current through the resistor can be estimated by the formula IR = VDD/2Rext (mA) with Rext in kOhm.

#### 19.3 DC CHARACTERISTICS:

#### PIC17CR42/42A/43/R43/44-16 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-25 (Commercial, Industrial) PIC17CR42/42A/43/R43/44-33 (Commercial, Industrial) PIC17LCR42/42A/43/R43/44-08 (Commercial, Industrial)

Standard Operating Conditions (unless otherwise stated) Operating temperature

#### DC CHARACTERISTICS

-40°C  $\leq$  TA  $\leq$  +85°C for industrial and 0°C  $\leq$  TA  $\leq$  +70°C for commercial

|                  | $0^{\circ}C \leq TA \leq +70^{\circ}C$ for commercial<br>Operating voltage VDD range as described in Section 19.1 |                                |             |           |            |         |                                                                                 |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|--------------------------------|-------------|-----------|------------|---------|---------------------------------------------------------------------------------|--|

| Demonst          |                                                                                                                   | 1                              | Operating v | oitage VI | טט range a | is desc | cribed in Section 19.1                                                          |  |

| Parameter<br>No. | Sym                                                                                                               | Characteristic                 | Min         | Тур†      | Мах        | Units   | Conditions                                                                      |  |

|                  |                                                                                                                   | Input Low Voltage              |             |           |            |         |                                                                                 |  |

|                  | VIL                                                                                                               | I/O ports                      |             |           |            |         |                                                                                 |  |

| D030             |                                                                                                                   | with TTL buffer                | Vss         | -         | 0.8        | V       | $4.5V \le VDD \le 5.5V$                                                         |  |

|                  |                                                                                                                   |                                | Vss         | -         | 0.2Vdd     | V       | $2.5V \le VDD \le 4.5V$                                                         |  |

| D031             |                                                                                                                   | with Schmitt Trigger buffer    | Vss         | -         | 0.2Vdd     | V       |                                                                                 |  |

| D032             |                                                                                                                   | MCLR, OSC1 (in EC and RC mode) | Vss         | -         | 0.2Vdd     | V       | Note1                                                                           |  |

| D033             |                                                                                                                   | OSC1 (in XT, and LF mode)      | -           | 0.5Vdd    | _          | V       |                                                                                 |  |

|                  |                                                                                                                   | Input High Voltage             |             |           |            |         |                                                                                 |  |

|                  | VIH                                                                                                               | I/O ports                      |             |           |            |         |                                                                                 |  |

| D040             |                                                                                                                   | with TTL buffer                | 2.0         | -         | Vdd        | V       | $4.5V \le VDD \le 5.5V$                                                         |  |

|                  |                                                                                                                   |                                | 1+0.2VDD    | -         | Vdd        | V       | $2.5V \le VDD \le 4.5V$                                                         |  |

| D041             |                                                                                                                   | with Schmitt Trigger buffer    | 0.8Vdd      | -         | Vdd        | V       |                                                                                 |  |

| D042             |                                                                                                                   | MCLR                           | 0.8Vdd      | _         | Vdd        | V       | Note1                                                                           |  |

| D043             |                                                                                                                   | OSC1 (XT, and LF mode)         | -           | 0.5Vdd    | _          | V       |                                                                                 |  |

| D050             | VHYS                                                                                                              | Hysteresis of                  | 0.15Vdd *   | _         | -          | V       |                                                                                 |  |

|                  |                                                                                                                   | Schmitt Trigger inputs         |             |           |            |         |                                                                                 |  |

|                  |                                                                                                                   | Input Leakage Current          |             |           |            |         |                                                                                 |  |

| Daga             |                                                                                                                   | (Notes 2, 3)                   |             |           |            |         |                                                                                 |  |

| D060             | lı∟                                                                                                               | I/O ports (except RA2, RA3)    | _           | _         | ±1         | μΑ      | Vss ≤ VPIN ≤ VDD,<br>I/O Pin at hi-impedance<br>PORTB weak pull-ups<br>disabled |  |

| D061             |                                                                                                                   | MCLR                           | -           | -         | <u>+2</u>  | μA      | VPIN = Vss or VPIN = VDD                                                        |  |

| D062             |                                                                                                                   | RA2, RA3                       |             |           | ±2         | μA      | $Vss \le Vra2$ , $Vra3 \le 12V$                                                 |  |

| D063             |                                                                                                                   | OSC1, TEST (EC, RC modes)      | -           | -         | ±1         | μA      | $Vss \le VPIN \le VDD$                                                          |  |

| D063B            |                                                                                                                   | OSC1, TEST (XT, LF modes)      | -           | -         | VPIN       | μA      | $R_F \ge 1 M\Omega$ , see Figure 14.2                                           |  |

| D064             |                                                                                                                   | MCLR                           | -           | -         | 10         | μA      | VMCLR = VPP = 12V<br>(when not programming)                                     |  |

| D070             | IPURB                                                                                                             | PORTB weak pull-up current     | 60          | 200       | 400        | μA      | VPIN = VSS, $\overline{\text{RBPU}} = 0$<br>4.5V $\leq$ VDD $\leq$ 6.0V         |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

Negative current is defined as coming out of the pin.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

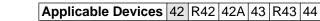

## Applicable Devices 42 R42 42A 43 R43 44

#### 19.5 <u>Timing Diagrams and Specifications</u>

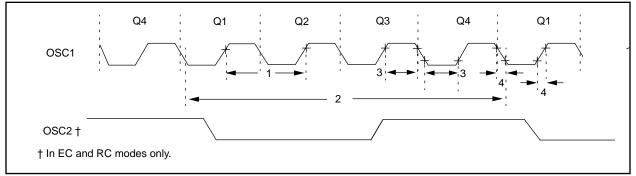

#### FIGURE 19-2: EXTERNAL CLOCK TIMING

#### TABLE 19-2: EXTERNAL CLOCK TIMING REQUIREMENTS

| Param<br>No. | Sym   | Characteristic                     | Min   | Тур†   | Max   | Units | Conditions                                        |

|--------------|-------|------------------------------------|-------|--------|-------|-------|---------------------------------------------------|

|              | Fosc  | External CLKIN Frequency           | DC    | _      | 8     | MHz   | EC osc mode - 08 devices (8 MHz devices)          |

|              |       | (Note 1)                           | DC    | _      | 16    | MHz   | - 16 devices (16 MHz devices)                     |

|              |       | (                                  | DC    | _      | 25    | MHz   | - 25 devices (25 MHz devices)                     |

|              |       |                                    | DC    | —      | 33    | MHz   | - 33 devices (33 MHz devices)                     |

|              |       | Oscillator Frequency               | DC    | _      | 4     | MHz   | RC osc mode                                       |

|              |       | (Note 1)                           | 1     | _      | 8     | MHz   | XT osc mode - 08 devices (8 MHz devices)          |

|              |       |                                    | 1     | _      | 16    | MHz   | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 1     | _      | 25    | MHz   | - 25 devices (25 MHz devices)                     |

|              |       |                                    | 1     | _      | 33    | MHz   | - 33 devices (33 MHz devices)                     |

|              |       |                                    | DC    | —      | 2     | MHz   | LF osc mode                                       |

| 1            | Tosc  | External CLKIN Period              | 125   | _      | —     | ns    | EC osc mode - 08 devices (8 MHz devices)          |

|              |       | (Note 1)                           | 62.5  | _      | —     | ns    | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 40    | _      | —     | ns    | - 25 devices (25 MHz devices)                     |

|              |       |                                    | 30.3  | —      | —     | ns    | - 33 devices (33 MHz devices)                     |

|              |       | Oscillator Period                  | 250   | _      | —     | ns    | RC osc mode                                       |

|              |       | (Note 1)                           | 125   | _      | 1,000 | ns    | XT osc mode - 08 devices (8 MHz devices)          |

|              |       |                                    | 62.5  | _      | 1,000 | ns    | - 16 devices (16 MHz devices)                     |

|              |       |                                    | 40    | —      | 1,000 | ns    | <ul> <li>- 25 devices (25 MHz devices)</li> </ul> |

|              |       |                                    | 30.3  | —      | 1,000 | ns    | - 33 devices (33 MHz devices)                     |

|              |       |                                    | 500   | —      | —     | ns    | LF osc mode                                       |

| 2            | Тсү   | Instruction Cycle Time<br>(Note 1) | 121.2 | 4/Fosc | DC    | ns    |                                                   |

| 3            | TosL, | Clock in (OSC1)                    | 10 ±  | _      | _     | ns    | EC oscillator                                     |

|              | TosH  | high or low time                   | · '   |        |       |       |                                                   |

| 4            | TosR, | Clock in (OSC1)                    | _     | _      | 5‡    | ns    | EC oscillator                                     |

|              | TosF  | rise or fall time                  |       |        |       |       |                                                   |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKIN pin. When an external clock input is used, the "max." cycle time limit is "DC" (no clock) for all devices.

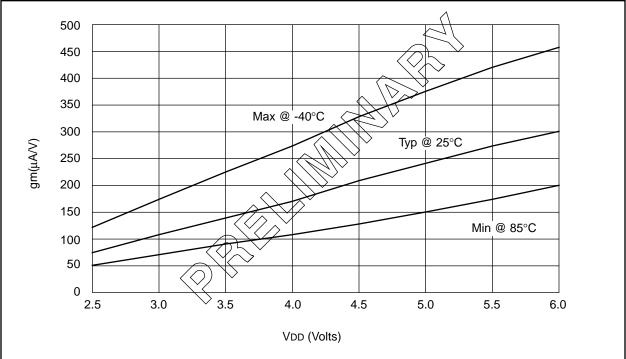

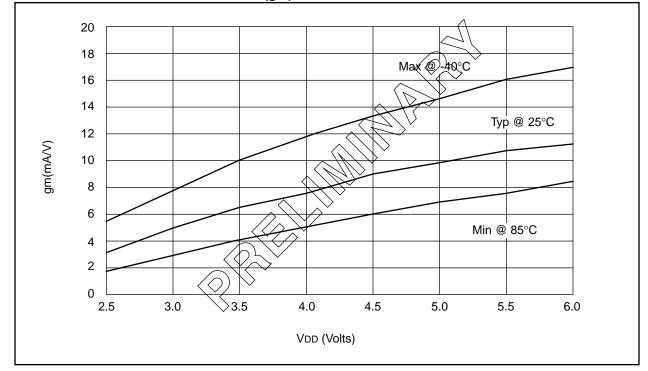

FIGURE 20-6: TRANSCONDUCTANCE (gm) OF XT OSCILLATOR vs. VDD

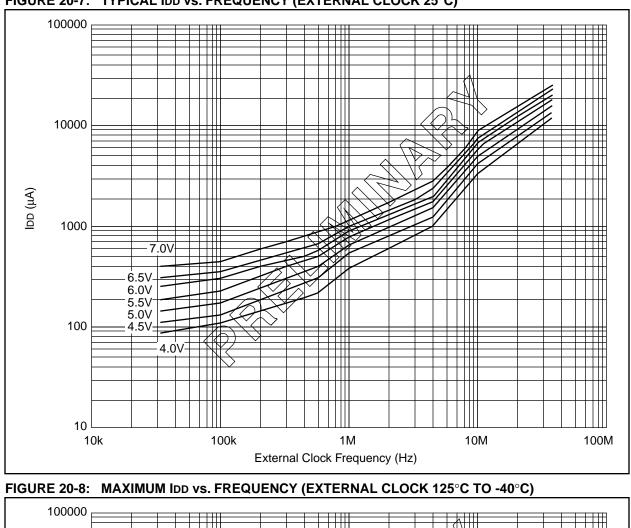

## Applicable Devices 42 R42 42A 43 R43 44

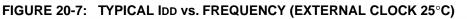

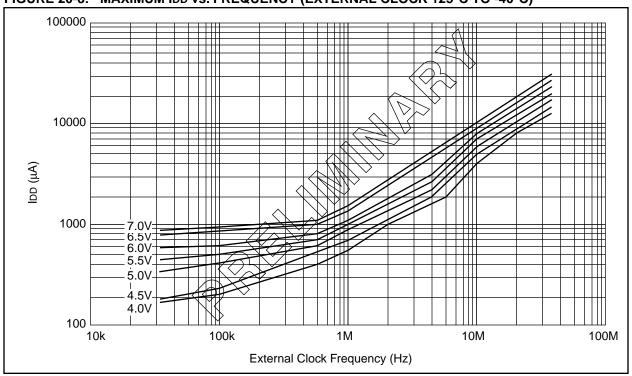

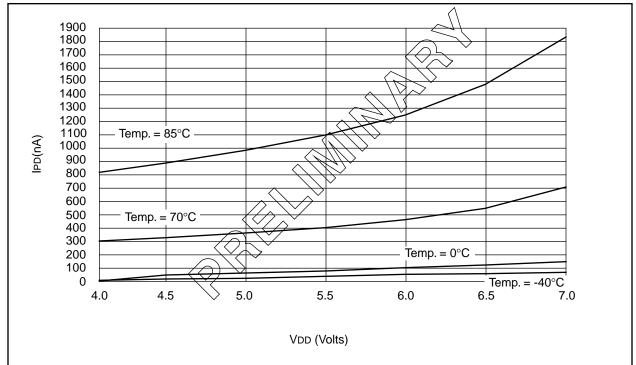

#### FIGURE 20-9: TYPICAL IPD vs. VDD WATCHDOG DISABLED 25°C

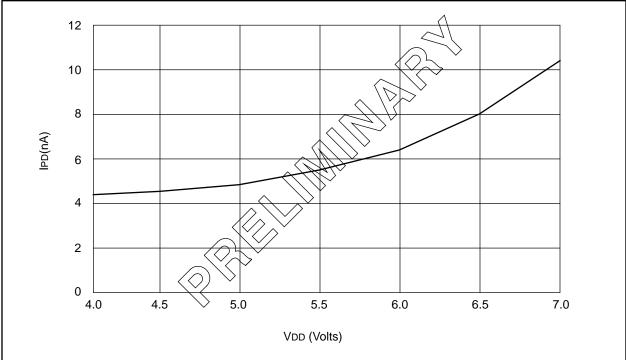

FIGURE 20-10: MAXIMUM IPD vs. VDD WATCHDOG DISABLED

## Applicable Devices 42 R42 42A 43 R43 44

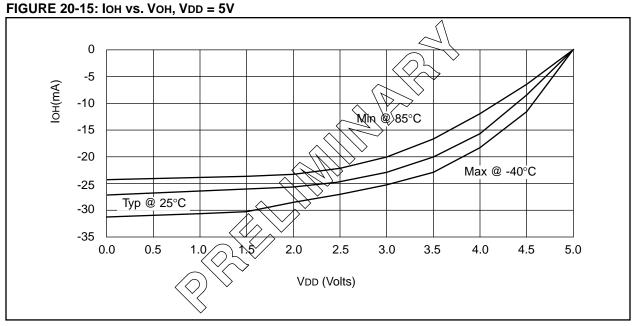

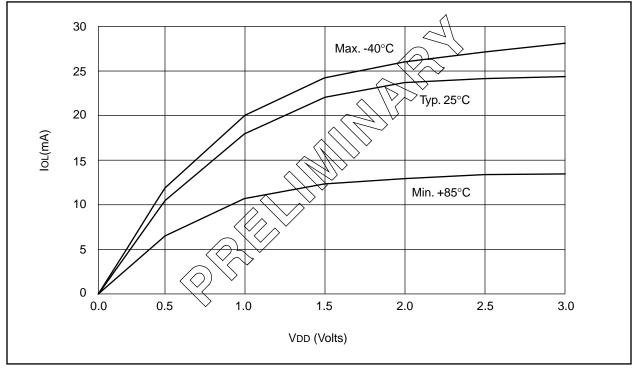

FIGURE 20-16: IOL vs. VOL, VDD = 3V

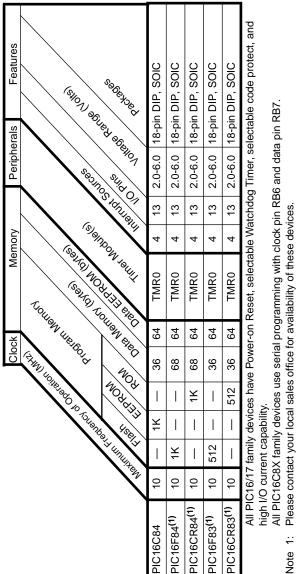

#### E.6 **PIC16C8X Family of Devices**

÷ Note

| WDT                        | 99, 103 |

|----------------------------|---------|

| Clearing the WDT           | 103     |

| Normal Timer               | 103     |

| Period                     | 103     |

| Programming Considerations | 103     |

| WDTPS0                     |         |

| WDTPS1                     |         |

| WREG                       |         |

## Χ

| XORLW    | 41 |

|----------|----|

| XORWF 14 | 41 |

## Ζ

| Z         |  |

|-----------|--|

| Zero (Z)9 |  |

#### LIST OF EXAMPLES

| Example 3-1:  | Signed Math                          | 9   |

|---------------|--------------------------------------|-----|

| Example 3-2:  | Instruction Pipeline Flow            |     |

| Example 5-1:  | Saving STATUS and WREG in RAM        |     |

| Example 6-1:  | Indirect Addressing                  |     |

| Example 7-1:  | Table Write                          |     |

| Example 7-2:  | Table Read                           |     |

| Example 8-1:  | 8 x 8 Multiply Routine               |     |

| Example 8-2:  | 8 x 8 Signed Multiply Routine        |     |

| Example 8-3:  | 16 x 16 Multiply Routine             |     |

| Example 8-4:  | 16 x 16 Signed Multiply Routine      | 51  |

| Example 9-1:  | Initializing PORTB                   |     |

| Example 9-2:  | Initializing PORTC                   |     |

| Example 9-3:  | Initializing PORTD                   |     |

| Example 9-4:  | Initializing PORTE                   |     |

| Example 9-5:  | Read Modify Write Instructions on an |     |

|               | I/O Port                             | 64  |

| Example 11-1: | 16-Bit Read                          | 69  |

| Example 11-2: | 16-Bit Write                         | 69  |

| Example 12-1: | Sequence to Read Capture Registers.  | 78  |

| Example 12-2: | Writing to TMR3                      | 80  |

| Example 12-3: | Reading from TMR3                    | 80  |

|               | Calculating Baud Rate Error          |     |

| Example F-1:  | PIC17C42 to Sleep                    | 223 |

|               |                                      |     |

#### LIST OF FIGURES

| Figure 3-1:  | PIC17C42 Block Diagram               | 10 |

|--------------|--------------------------------------|----|

| Figure 3-2:  | PIC17CR42/42A/43/R43/44 Block        |    |

|              | Diagram                              | 11 |

| Figure 3-3:  | Clock/Instruction Cycle              | 14 |

| Figure 4-1:  | Simplified Block Diagram of On-chip  |    |

|              | Reset Circuit                        | 15 |

| Figure 4-2:  | Time-Out Sequence on Power-Up        |    |

|              | (MCLR Tied to VDD)                   | 17 |

| Figure 4-3:  | Time-Out Sequence on Power-Up        |    |

|              | (MCLR NOT Tied to VDD)               | 17 |

| Figure 4-4:  | Slow Rise Time (MCLR Tied to VDD)    | 17 |

| Figure 4-5:  | Oscillator Start-Up Time             | 18 |

| Figure 4-6:  | Using On-Chip POR                    | 18 |

| Figure 4-7:  | Brown-out Protection Circuit 1       | 18 |

| Figure 4-8:  | PIC17C42 External Power-On Reset     |    |

|              | Circuit (For Slow VDD Power-Up)      | 18 |

| Figure 4-9:  | Brown-out Protection Circuit 2       |    |

| Figure 5-1:  | Interrupt Logic                      | 21 |

| Figure 5-2:  | INTSTA Register (Address: 07h,       |    |

|              | Unbanked)                            |    |

| Figure 5-3:  | PIE Register (Address: 17h, Bank 1)  |    |

| Figure 5-4:  | PIR Register (Address: 16h, Bank 1)  |    |

| Figure 5-5:  | INT Pin / T0CKI Pin Interrupt Timing |    |

| Figure 6-1:  | Program Memory Map and Stack         |    |

| Figure 6-2:  | Memory Map in Different Modes        | 30 |

| Figure 6-3:  | External Program Memory Access       |    |

|              | Waveforms                            | 31 |

| Figure 6-4:  | Typical External Program Memory      |    |

|              | Connection Diagram                   |    |

| Figure 6-5:  | PIC17C42 Register File Map           | 33 |

| Figure 6-6:  | PIC17CR42/42A/43/R43/44 Register     |    |

|              | File Map                             | 33 |

| Figure 6-7:  | ALUSTA Register (Address: 04h,       |    |

|              | Unbanked)                            | 36 |

| Figure 6-8:  | CPUSTA Register (Address: 06h,       |    |

|              | Unbanked)                            | 37 |

| Figure 6-9:  | T0STA Register (Address: 05h,        |    |

|              | Unbanked)                            |    |

| Figure 6-10: | Indirect Addressing                  |    |

| Figure 6-11: | Program Counter Operation            | 41 |

|              |                                      |    |

### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (602) 786-7578.

Please list the following information, and use this outline to provide us with your comments about this Data Sheet.

| To:     |         | Technical Publications Manager Total Pages Sent                                           |

|---------|---------|-------------------------------------------------------------------------------------------|

| RE<br>_ |         | Reader Response                                                                           |

| Fro     | om:     | Name                                                                                      |

|         |         | Company                                                                                   |

|         |         | Address<br>City / State / ZIP / Country                                                   |

|         |         | Telephone: () FAX: ()                                                                     |

| Ар      | plica   | ation (optional):                                                                         |

| Wo      | buld    | you like a reply?YN                                                                       |

| De      | vice    | E: PIC17C4X Literature Number: DS30412C                                                   |

|         |         | ions:                                                                                     |

|         |         |                                                                                           |

| 1.      | W       | hat are the best features of this document?                                               |

|         |         |                                                                                           |

| 2       | —<br>Ho | ow does this document meet your hardware and software development needs?                  |

| ۷.      |         | Sw does this document meet your hardware and software development needs:                  |

|         |         |                                                                                           |

| 3.      | Do      | o you find the organization of this data sheet easy to follow? If not, why?               |

|         |         |                                                                                           |

|         |         |                                                                                           |

| 4.      | W       | hat additions to the data sheet do you think would enhance the structure and subject?     |

|         |         |                                                                                           |

| ~       |         |                                                                                           |

| 5.      | vvi     | hat deletions from the data sheet could be made without affecting the overall usefulness? |

|         |         |                                                                                           |

| 6.      | ls      | there any incorrect or misleading information (what and where)?                           |

|         |         |                                                                                           |

|         |         |                                                                                           |

| 7.      | Ho      | ow would you improve this document?                                                       |

|         |         |                                                                                           |

|         |         |                                                                                           |

| 8.      | Ho      | ow would you improve our software, systems, and silicon products?                         |

NOTES: