Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 44-QFP                                                                    |

| Supplier Device Package    | 44-MQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc44-08-pq |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 PIC17C4X DEVICE VARIETIES

A variety of frequency ranges and packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in the PIC17C4X Product Selection System section at the end of this data sheet. When placing orders, please use the "PIC17C4X Product Identification System" at the back of this data sheet to specify the correct part number.

For the PIC17C4X family of devices, there are four device "types" as indicated in the device number:

- C, as in PIC17C42. These devices have EPROM type memory and operate over the standard voltage range.

- 2. LC, as in PIC17LC42. These devices have EPROM type memory, operate over an extended voltage range, and reduced frequency range.

- 3. **CR**, as in PIC17**CR**42. These devices have ROM type memory and operate over the standard voltage range.

- 4. LCR, as in PIC17LCR42. These devices have ROM type memory, operate over an extended voltage range, and reduced frequency range.

#### 2.1 UV Erasable Devices

The UV erasable version, offered in CERDIP package, is optimal for prototype development and pilot programs.

The UV erasable version can be erased and reprogrammed to any of the configuration modes. Microchip's PRO MATE<sup>TM</sup> programmer supports programming of the PIC17C4X. Third party programmers also are available; refer to the *Third Party Guide* for a list of sources.

#### 2.2 <u>One-Time-Programmable (OTP)</u> <u>Devices</u>

The availability of OTP devices is especially useful for customers expecting frequent code changes and updates.

The OTP devices, packaged in plastic packages, permit the user to program them once. In addition to the program memory, the configuration bits must also be programmed.

#### 2.3 <u>Quick-Turnaround-Production (QTP)</u> <u>Devices</u>

Microchip offers a QTP Programming Service for factory production orders. This service is made available for users who choose not to program a medium to high quantity of units and whose code patterns have stabilized. The devices are identical to the OTP devices but with all EPROM locations and configuration options already programmed by the factory. Certain code and prototype verification procedures apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.4 <u>Serialized Quick-Turnaround</u> <u>Production (SQTP<sup>SM</sup>) Devices</u>

Microchip offers a unique programming service where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number which can serve as an entry-code, password or ID number.

ROM devices do not allow serialization information in the program memory space.

For information on submitting ROM code, please contact your regional sales office.

#### 2.5 Read Only Memory (ROM) Devices

Microchip offers masked ROM versions of several of the highest volume parts, thus giving customers a low cost option for high volume, mature products.

For information on submitting ROM code, please contact your regional sales office.

#### 5.3 <u>Peripheral Interrupt Request Register</u> (PIR)

This register contains the individual flag bits for the peripheral interrupts.

**Note:** These bits will be set by the specified condition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the interrupt flag to ensure that the program does not immediately branch to the peripheral interrupt service routine.

## FIGURE 5-4: PIR REGISTER (ADDRESS: 16h, BANK 1)

|        | 0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 R-0                                                                                                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RBIF   |                                                                                                                                                                                                                                                                              |

| bit7   | bit0 W = Writable bit<br>-n = Value at POR reset                                                                                                                                                                                                                             |

| bit 7: | <b>RBIF</b> : PORTB Interrupt on Change Flag bit<br>1 = One of the PORTB inputs changed (Software must end the mismatch condition)<br>0 = None of the PORTB inputs have changed                                                                                              |

| bit 6: | TMR3IF: Timer3 Interrupt Flag bit<br>If Capture1 is enabled (CA1/PR3 = 1)<br>1 = Timer3 overflowed<br>0 = Timer3 did not overflow                                                                                                                                            |

|        | If Capture1 is disabled (CA1/ $\overline{PR3}$ = 0)<br>1 = Timer3 value has rolled over to 0000h from equalling the period register (PR3H:PR3L) value<br>0 = Timer3 value has not rolled over to 0000h from equalling the period register (PR3H:PR3L) value                  |

| bit 5: | <b>TMR2IF</b> : Timer2 Interrupt Flag bit<br>1 = Timer2 value has rolled over to 0000h from equalling the period register (PR2) value<br>0 = Timer2 value has not rolled over to 0000h from equalling the period register (PR2) value                                        |

| bit 4: | <b>TMR1IF</b> : Timer1 Interrupt Flag bit<br>If Timer1 is in 8-bit mode (T16 = 0)<br>1 = Timer1 value has rolled over to 0000h from equalling the period register (PR) value<br>0 = Timer1 value has not rolled over to 0000h from equalling the period register (PR2) value |

|        | If Timer1 is in 16-bit mode (T16 = 1)<br>1 = TMR1:TMR2 value has rolled over to 0000h from equalling the period register (PR1:PR2) value<br>0 = TMR1:TMR2 value has not rolled over to 0000h from equalling the period register (PR1:PR2) value                              |

| bit 3: | <b>CA2IF</b> : Capture2 Interrupt Flag bit<br>1 = Capture event occurred on RB1/CAP2 pin<br>0 = Capture event did not occur on RB1/CAP2 pin                                                                                                                                  |

| bit 2: | <b>CA1IF</b> : Capture1 Interrupt Flag bit<br>1 = Capture event occurred on RB0/CAP1 pin<br>0 = Capture event did not occur on RB0/CAP1 pin                                                                                                                                  |

| bit 1: | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = Transmit buffer is empty<br>0 = Transmit buffer is full                                                                                                                                                               |

| bit 0: | RCIF: USART Receive Interrupt Flag bit<br>1 = Receive buffer is full<br>0 = Receive buffer is empty                                                                                                                                                                          |

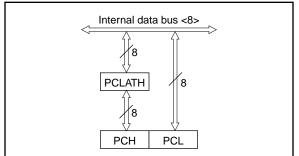

#### 6.7 Program Counter Module

The Program Counter (PC) is a 16-bit register. PCL, the low byte of the PC, is mapped in the data memory. PCL is readable and writable just as is any other register. PCH is the high byte of the PC and is not directly addressable. Since PCH is not mapped in data or program memory, an 8-bit register PCLATH (PC high latch) is used as a holding latch for the high byte of the PC. PCLATH is mapped into data memory. The user can read or write PCH through PCLATH.

The 16-bit wide PC is incremented after each instruction fetch during Q1 unless:

- Modified by GOTO, CALL, LCALL, RETURN, RETLW, or RETFIE instruction

- · Modified by an interrupt response

- Due to destination write to PCL by an instruction

"Skips" are equivalent to a forced NOP cycle at the skipped address.

Figure 6-11 and Figure 6-12 show the operation of the program counter for various situations.

#### FIGURE 6-11: PROGRAM COUNTER OPERATION

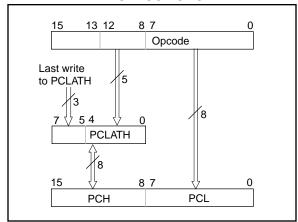

FIGURE 6-12: PROGRAM COUNTER USING THE CALL AND GOTO INSTRUCTIONS

Using Figure 6-11, the operations of the PC and PCLATH for different instructions are as follows:

- a) <u>LCALL instructions</u>: An 8-bit destination address is provided in the instruction (opcode). PCLATH is unchanged. PCLATH → PCH Opcode<7:0> → PCL

- b) Read instructions on PCL: Any instruction that reads PCL. PCL  $\rightarrow$  data bus  $\rightarrow$  ALU or destination PCH  $\rightarrow$  PCLATH

- c) <u>Write instructions on PCL</u>: Any instruction that writes to PCL. 8-bit data  $\rightarrow$  data bus  $\rightarrow$  PCL PCLATH  $\rightarrow$  PCH

- d) <u>Read-Modify-Write instructions on PCL:</u> Any instruction that does a read-write-modify operation on PCL, such as ADDWF PCL. Read: PCL → data bus → ALU Write: 8-bit result → data bus → PCL

- $\mathsf{PCLATH} \to \mathsf{PCH}$

- e) <u>RETURN instruction:</u> PCH  $\rightarrow$  PCLATH Stack<MRU>  $\rightarrow$  PC<15:0>

Using Figure 6-12, the operation of the PC and PCLATH for GOTO and CALL instructions is a follows:

CALL, GOTO instructions: A 13-bit destination address is provided in the instruction (opcode). Opcode<12:0>  $\rightarrow$  PC <12:0>

$PC<15:13> \rightarrow PCLATH<7:5>$

Opcode<12:8>  $\rightarrow$  PCLATH <4:0>

The read-modify-write only affects the PCL with the result. PCH is loaded with the value in the PCLATH. For example, ADDWF PCL will result in a jump within the current page. If PC = 03F0h, WREG = 30h and PCLATH = 03h before instruction, PC = 0320h after the instruction. To accomplish a true 16-bit computed jump, the user needs to compute the 16-bit destination address, write the high byte to PCLATH and then write the low value to PCL.

The following PC related operations do not change PCLATH:

- a) LCALL, RETLW, and RETFIE instructions.

- b) Interrupt vector is forced onto the PC.

- c) Read-modify-write instructions on PCL (e.g.BSF PCL).

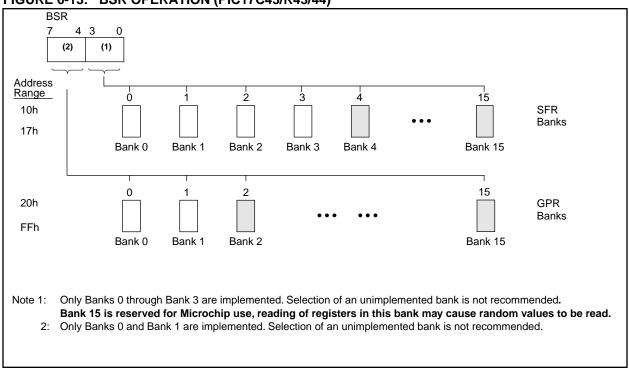

#### 6.8 Bank Select Register (BSR)

The BSR is used to switch between banks in the data memory area (Figure 6-13). In the PIC17C42, PIC17CR42, and PIC17C42A only the lower nibble is implemented. While in the PIC17C43, PIC17CR43, and PIC17C44 devices, the entire byte is implemented. The lower nibble is used to select the peripheral register bank. The upper nibble is used to select the general purpose memory bank.

All the Special Function Registers (SFRs) are mapped into the data memory space. In order to accommodate the large number of registers, a banking scheme has been used. A segment of the SFRs, from address 10h to address 17h, is banked. The lower nibble of the bank select register (BSR) selects the currently active "peripheral bank." Effort has been made to group the peripheral registers of related functionality in one bank. However, it will still be necessary to switch from bank to bank in order to address all peripherals related to a single task. To assist this, a MOVLB bank instruction is in the instruction set. For the PIC17C43, PIC17CR43, and PIC17C44 devices, the need for a large general purpose memory space dictated a general purpose RAM banking scheme. The upper nibble of the BSR selects the currently active general purpose RAM bank. To assist this, a MOVLR bank instruction has been provided in the instruction set.

If the currently selected bank is not implemented (such as Bank 13), any read will read all '0's. Any write is completed to the bit bucket and the ALU status bits will be set/cleared as appropriate.

**Note:** Registers in Bank 15 in the Special Function Register area, are reserved for Microchip use. Reading of registers in this bank may cause random values to be read.

#### FIGURE 6-13: BSR OPERATION (PIC17C43/R43/44)

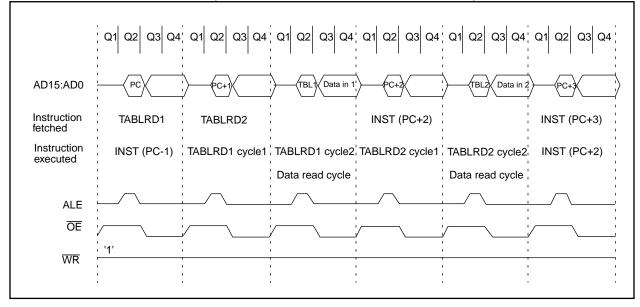

#### 7.3 <u>Table Reads</u>

FIGURE 7-7:

The table read allows the program memory to be read. This allows constant data to be stored in the program memory space, and retrieved into data memory when needed. Example 7-2 reads the 16-bit value at program memory address TBLPTR. After the dummy byte has been read from the TABLATH, the TABLATH is loaded with the 16-bit data from program memory address TBLPTR + 1. The first read loads the data into the latch, and can be considered a dummy read (unknown data loaded into 'f'). INDF0 should be configured for either auto-increment or auto-decrement.

# + 1. The first read loads the data into TABLRD 0,1,INDF0 ; Read LO byte ; of TABLATCH and ; of TABLATCH and ; Update TABLATCH auto-increment or auto-decrement.

MOVLW

MOVWF

MOVLW

MOVWF

TLRD

TABLRD

EXAMPLE 7-2: TABLE READ

LOW (TBL\_ADDR)

TBLPTRH

TBLPTRL

0,0,DUMMY

1, INDF0

HIGH (TBL\_ADDR) ; Load the Table

;

;

;

;

address

; Dummy read,

; Read HI byte

; Updates TABLATCH

of TABLATCH

#### Q4 | AD15:AD0 Data in PC PC-TBL PC4 Instruction TABLRD INST (PC+1) INST (PC+2) fetched Instruction INST (PC-1) TABLRD cycle1 TABLRD cycle2 INST (PC+1) executed Data read cycle ALE ŌĒ $\overline{\mathsf{WR}}$

#### FIGURE 7-8: TABLRD TIMING (CONSECUTIVE TABLRD INSTRUCTIONS)

DS30412C-page 48

Example 8-4 shows the sequence to do an 16 x 16 signed multiply. Equation 8-2 shows the algorithm that used. The 32-bit result is stored in four registers RES3:RES0. To account for the sign bits of the arguments, each argument pairs most significant bit (MSb) is tested and the appropriate subtractions are done.

| EQUATION 8-2: | 16 x 16 SIGNED |

|---------------|----------------|

|               | MULTIPLICATION |

|               | ALGORITHM      |

RES3:RES0

- = ARG1H:ARG1L \* ARG2H:ARG2L

- - (-1 \* ARG1H<7> \* ARG2H:ARG2L \* 2<sup>16</sup>)

# EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY

|     |          | ROUTI       | N | E                |

|-----|----------|-------------|---|------------------|

|     | MOVFP    | ARG1L, WREG |   |                  |

|     | MULWF    | ARG2L       | ; | ARG1L * ARG2L -> |

|     |          |             |   | PRODH:PRODL      |

|     | MOVPF    | PRODH, RES1 |   |                  |

|     |          | PRODL, RESO |   |                  |

| ;   |          | - ,         |   |                  |

|     | MOVFP    | ARG1H, WREG |   |                  |

|     |          |             |   | ARG1H * ARG2H -> |

|     | 110201   | into bii    | ; |                  |

|     | MOVPF    | PRODH, RES3 |   | TRODUCTRODE      |

|     |          | PRODL, RES2 |   |                  |

| ;   | 110 11 1 | TRODE, REDZ | ' |                  |

| '   | MOVFP    | ARG1L, WREG |   |                  |

|     |          |             |   | ARG1L * ARG2H -> |

|     | HOLMI    | 111(0211    | ; |                  |

|     | MOVFP    | PRODL, WREG |   | TRODITITRODE     |

|     |          |             |   | Add cross        |

|     |          |             |   |                  |

|     |          |             | ; | products         |

|     |          |             |   |                  |

|     |          | WREG, F     | ; |                  |

|     | ADDWFC   | RES3, F     | ; |                  |

| ;   | NOTED    |             |   |                  |

|     |          | ARG1H, WREG | ' |                  |

|     | MULWF    | ARG2L       |   | ARG1H * ARG2L -> |

|     |          |             | , | PRODH:PRODL      |

|     | MOMED    |             |   |                  |

|     |          | PRODL, WREG |   | Add man          |

|     | ADDWF    | RES1, F     |   |                  |

|     |          | PRODH, WREG |   | products         |

|     |          |             | ; |                  |

|     | CLRF     | WREG, F     | ; |                  |

|     | ADDWFC   | RES3, F     | ; |                  |

| ;   |          |             |   |                  |

|     |          | ARG2H, 7    | ' | ARG2H:ARG2L neg? |

|     |          |             |   | no, check ARG1   |

|     | MOVFP    | ARG1L, WREG |   |                  |

|     |          | RES2        | ; |                  |

|     | MOVFP    | ARG1H, WREG | ; |                  |

|     | SUBWFB   | RES3        |   |                  |

| ;   |          |             |   |                  |

| SIC | GN_ARG1  |             |   |                  |

|     |          |             |   | ARG1H:ARG1L neg? |

|     | GOTO     | CONT_CODE   |   | no, done         |

|     |          | ARG2L, WREG |   |                  |

|     | SUBWF    | RES2        | ; |                  |

|     | MOVFP    | ARG2H, WREG | ; |                  |

|     | SUBWFB   | RES3        |   |                  |

| ;   |          |             |   |                  |

| COI | NT_CODE  |             |   |                  |

|     | :        |             |   |                  |

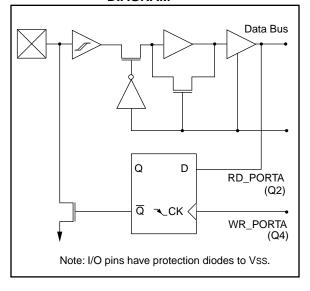

FIGURE 9-2: RA2 AND RA3 BLOCK DIAGRAM

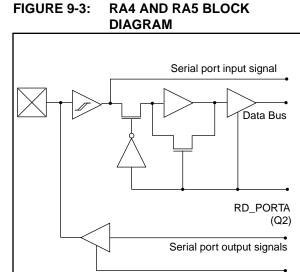

$\overline{OE}$  = SPEN,SYNC,TXEN,  $\overline{CREN}$ ,  $\overline{SREN}$  for RA4  $\overline{OE}$  = SPEN ( $\overline{SYNC}$ +SYNC, $\overline{CSRC}$ ) for RA5

Note: I/O pins have protection diodes to VDD and VSS.

| TABLE 9-1: | PO | RTA FUNCTI | ONS |

|------------|----|------------|-----|

|            |    |            |     |

. . . . .

\_ \_ \_ \_ \_ . . . . . . . . . . . . . .

| Name      | Bit0 | Buffer Type | Function                                                                            |

|-----------|------|-------------|-------------------------------------------------------------------------------------|

| RA0/INT   | bit0 | ST          | Input or external interrupt input.                                                  |

| RA1/T0CKI | bit1 | ST          | Input or clock input to the TMR0 timer/counter, and/or an external interrupt input. |

| RA2       | bit2 | ST          | Input/Output. Output is open drain type.                                            |

| RA3       | bit3 | ST          | Input/Output. Output is open drain type.                                            |

| RA4/RX/DT | bit4 | ST          | Input or USART Asynchronous Receive or USART Synchronous Data.                      |

| RA5/TX/CK | bit5 | ST          | Input or USART Asynchronous Transmit or USART Synchronous Clock.                    |

| RBPU      | bit7 |             | Control bit for PORTB weak pull-ups.                                                |

Legend: ST = Schmitt Trigger input.

#### TABLE 9-2: REGISTERS/BITS ASSOCIATED WITH PORTA

| Address       | Name  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1     | Bit 0   | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|---------------|-------|--------|-------|-------|-------|-------|-------|-----------|---------|-------------------------------|-----------------------------------------|

| 10h, Bank 0   | PORTA | RBPU   | _     | RA5   | RA4   | RA3   | RA2   | RA1/T0CKI | RA0/INT | 0-xx xxxx                     | 0-uu uuuu                               |

| 05h, Unbanked | TOSTA | INTEDG | T0SE  | TOCS  | PS3   | PS2   | PS1   | PS0       | _       | 0000 000-                     | 0000 000-                               |

| 13h, Bank 0   | RCSTA | SPEN   | RC9   | SREN  | CREN  | —     | FERR  | OERR      | RC9D    | 0000 -00x                     | 0000 -00u                               |

| 15h, Bank 0   | TXSTA | CSRC   | TX9   | TXEN  | SYNC  | —     | —     | TRMT      | TX9D    | 00001x                        | 0000lu                                  |

Legend: x = unknown, u = unchanged, - = unimplemented reads as '0'. Shaded cells are not used by PORTA. Note 1: Other (non power-up) resets include: external reset through  $\overline{MCLR}$  and the Watchdog Timer Reset. NOTES:

| BAUD        | SPBRG  |        | FOSC = 25 MHz SPBR |        |        | Fosc = 2           | 0 MHz | SPBRG  |                    |       | SPBRG  |                    |

|-------------|--------|--------|--------------------|--------|--------|--------------------|-------|--------|--------------------|-------|--------|--------------------|

| RATE<br>(K) | KBAUD  | %ERROR | value<br>(decimal) | KBAUD  | %ERROR | value<br>(decimal) | KBAUD | %ERROR | value<br>(decimal) | KBAUD | %ERROR | value<br>(decimal) |

| 0.3         | NA     | _      | —                  | NA     | _      |                    | NA    | _      | _                  | NA    | _      | -                  |

| 1.2         | NA     | _      | _                  | NA     | _      | _                  | 1.221 | +1.73  | 255                | 1.202 | +0.16  | 207                |

| 2.4         | 2.398  | -0.07  | 214                | 2.396  | 0.14   | 162                | 2.404 | +0.16  | 129                | 2.404 | +0.16  | 103                |

| 9.6         | 9.548  | -0.54  | 53                 | 9.53   | -0.76  | 40                 | 9.469 | -1.36  | 32                 | 9.615 | +0.16  | 25                 |

| 19.2        | 19.09  | -0.54  | 26                 | 19.53  | +1.73  | 19                 | 19.53 | +1.73  | 15                 | 19.23 | +0.16  | 12                 |

| 76.8        | 73.66  | -4.09  | 6                  | 78.13  | +1.73  | 4                  | 78.13 | +1.73  | 3                  | 83.33 | +8.51  | 2                  |

| 96          | 103.12 | +7.42  | 4                  | 97.65  | +1.73  | 3                  | 104.2 | +8.51  | 2                  | NA    | _      | _                  |

| 300         | 257.81 | -14.06 | 1                  | 390.63 | +30.21 | 0                  | 312.5 | +4.17  | 0                  | NA    | _      | -                  |

| 500         | 515.62 | +3.13  | 0                  | NA     | _      | _                  | NA    | _      | _                  | NA    | _      | -                  |

| HIGH        | 515.62 | _      | 0                  | _      | _      | 0                  | 312.5 | _      | 0                  | 250   | _      | 0                  |

| LOW         | 2.014  | —      | 255                | 1.53   | —      | 255                | 1.221 | —      | 255                | 0.977 | _      | 255                |

## TABLE 13-4: BAUD RATES FOR ASYNCHRONOUS MODE

| BAUD        | BAUD<br>RATE Fosc = 10 MHz SPB |        |                    | Fosc = 7.159       | ) MHz  | SPBRG<br>value     | SPBRG<br>value |        |                    |

|-------------|--------------------------------|--------|--------------------|--------------------|--------|--------------------|----------------|--------|--------------------|

| (K)         | KBAUD                          | %ERROR | (decimal)          | KBAUD              | %ERROR | (decimal)          | KBAUD          | %ERROR | (decimal)          |

| 0.3         | NA                             | _      | _                  | NA                 | _      | _                  | 0.31           | +3.13  | 255                |

| 1.2         | 1.202                          | +0.16  | 129                | 1.203              | _0.23  | 92                 | 1.2            | 0      | 65                 |

| 2.4         | 2.404                          | +0.16  | 64                 | 2.380              | -0.83  | 46                 | 2.4            | 0      | 32                 |

| 9.6         | 9.766                          | +1.73  | 15                 | 9.322              | -2.90  | 11                 | 9.9            | -3.13  | 7                  |

| 19.2        | 19.53                          | +1.73  | 7                  | 18.64              | -2.90  | 5                  | 19.8           | +3.13  | 3                  |

| 76.8        | 78.13                          | +1.73  | 1                  | NA                 | _      | —                  | 79.2           | +3.13  | 0                  |

| 96          | NA                             | —      | —                  | NA                 | —      | —                  | NA             | —      | —                  |

| 300         | NA                             | _      | —                  | NA                 | _      | —                  | NA             | _      | _                  |

| 500         | NA                             | _      | _                  | NA                 | _      | _                  | NA             | _      | _                  |

| HIGH        | 156.3                          | _      | 0                  | 111.9              | _      | 0                  | 79.2           | _      | 0                  |

| LOW         | 0.610                          | —      | 255                | 0.437              | —      | 255                | 0.309          | _      | 2 <b>55</b>        |

| BAUD        | Fosc = 3.579                   | MHz    | SPBRG              | Fosc = 1 MHz SPBRG |        |                    | FOSC = 32.76   | SPBRG  |                    |

| RATE<br>(K) | KBAUD                          | %ERROR | value<br>(decimal) | KBAUD              | %ERROR | value<br>(decimal) | KBAUD          | %ERROR | value<br>(decimal) |

| 0.3         | 0.301                          | +0.23  | 185                | 0.300              | +0.16  | 51                 | 0.256          | -14.67 | 1                  |

| 1.2         | 1.190                          | -0.83  | 46                 | 1.202              | +0.16  | 12                 | NA             | —      | —                  |

| 2.4         | 2.432                          | +1.32  | 22                 | 2.232              | -6.99  | 6                  | NA             | —      | —                  |

| 9.6         | 9.322                          | -2.90  | 5                  | NA                 | _      | _                  | NA             | _      | _                  |

| 19.2        | 18.64                          | -2.90  | 2                  | NA                 | —      | —                  | NA             | —      | —                  |

| 76.8        | NA                             | —      | —                  | NA                 | —      | —                  | NA             | —      | —                  |

| 96          | NA                             | _      | _                  | NA                 | _      | _                  | NA             | _      | _                  |

| 300         | NA                             | —      | —                  | NA                 | —      | —                  | NA             | —      | —                  |

| 500         | NA                             | —      | —                  | NA                 | —      | —                  | NA             | —      | —                  |

| HIGH        | 55.93                          | _      | 0                  | 15.63              | _      | 0                  | 0.512          | _      | 0                  |

| l mon       |                                |        |                    |                    |        |                    |                |        |                    |

#### 13.2.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown in Figure 13-4. The data comes in the RA4/RX/DT pin and drives the data recovery block. The data recovery block is actually a high speed shifter operating at 16 times the baud rate, whereas the main receive serial shifter operates at the bit rate or at Fosc.

Once asynchronous mode is selected, reception is enabled by setting bit CREN (RCSTA<4>).

The heart of the receiver is the receive (serial) shift register (RSR). After sampling the stop bit, the received data in the RSR is transferred to the RCREG (if it is empty). If the transfer is complete, the interrupt bit RCIF (PIR<0>) is set. The actual interrupt can be enabled/disabled by setting/clearing the RCIE (PIE<0>) bit. RCIF is a read only bit which is cleared by the hardware. It is cleared when RCREG has been read and is empty. RCREG is a double buffered register; (i.e. it is a two deep FIFO). It is possible for two bytes of data to be received and transferred to the RCREG FIFO and a third byte begin shifting to the RSR. On detection of the stop bit of the third byte, if the RCREG is still full, then the overrun error bit, OERR (RCSTA<1>) will be set. The word in the RSR will be lost. RCREG can be read twice to retrieve the two bytes in the FIFO. The OERR bit has to be cleared in software which is done by resetting the receive logic (CREN is set). If the OERR bit is set, transfers from the RSR to RCREG are inhibited, so it is essential to clear the OERR bit if it is set. The framing error bit FERR (RCSTA<2>) is set if a stop bit is not detected.

FIGURE 13-7: RX PIN SAMPLING SCHEME

Note: The FERR and the 9th receive bit are buffered the same way as the receive data. Reading the RCREG register will allow the RX9D and FERR bits to be loaded with values for the next received Received data; therefore, it is essential for the user to read the RCSTA register before reading RCREG in order not to lose the old FERR and RX9D information.

#### 13.2.3 SAMPLING

The data on the RA4/RX/DT pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the RA4/RX/DT pin. The sampling is done on the seventh, eighth and ninth falling edges of a x16 clock (Figure 11-3).

The x16 clock is a free running clock, and the three sample points occur at a frequency of every 16 falling edges.

| RX                          |   | Start bit                              |     |  |  |  |  |

|-----------------------------|---|----------------------------------------|-----|--|--|--|--|

| (RA4/RX/DT pin)<br>baud CLK | - | Baud CLK for all but start bit         |     |  |  |  |  |

| Jaud CLK                    | 1 |                                        |     |  |  |  |  |

| x16 CLK                     |   | 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 1 | 2 3 |  |  |  |  |

|                             |   |                                        |     |  |  |  |  |

|                             |   | Samples                                |     |  |  |  |  |

#### 14.4.2 MINIMIZING CURRENT CONSUMPTION

To minimize current consumption, all I/O pins should be either at VDD, or VSS, with no external circuitry drawing current from the I/O pin. I/O pins that are hi-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should be at VDD or VSS. The contributions from on-chip pull-ups on PORTB should also be considered, and disabled when possible.

#### 14.5 <u>Code Protection</u>

The code in the program memory can be protected by selecting the microcontroller in code protected mode (PM2:PM0 = '000').

| Note: | PM2 d  | oes not | exist on th | e PIC17C42. To  |

|-------|--------|---------|-------------|-----------------|

|       | select | code    | protected   | microcontroller |

|       |        |         | 10 = 00'.   |                 |

In this mode, instructions that are in the on-chip program memory space, can continue to read or write the program memory. An instruction that is executed outside of the internal program memory range will be inhibited from writing to or reading from program memory.

**Note:** Microchip does not recommend code protecting windowed devices.

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

# TABLE 15-2: PIC17CXX INSTRUCTION SET

| Mnemonic,<br>Operands |       | Description                           | Cycles | 16-bit Opcoo   | le   | Status<br>Affected | Notes |

|-----------------------|-------|---------------------------------------|--------|----------------|------|--------------------|-------|

|                       |       |                                       |        | MSb            | LSb  |                    |       |

| BYTE-ORIE             |       | TILE REGISTER OPERATIONS              | •      |                |      |                    | •     |

| ADDWF                 | f,d   | ADD WREG to f                         | 1      | 0000 111d ffff | ffff | OV,C,DC,Z          |       |

| ADDWFC                | f,d   | ADD WREG and Carry bit to f           | 1      | 0001 000d ffff | ffff | OV,C,DC,Z          |       |

| ANDWF                 | f,d   | AND WREG with f                       | 1      | 0000 101d ffff | ffff | Z                  |       |

| CLRF                  | f,s   | Clear f, or Clear f and Clear WREG    | 1      | 0010 100s ffff | ffff | None               | 3     |

| COMF                  | f,d   | Complement f                          | 1      | 0001 001d ffff | ffff | Z                  |       |

| CPFSEQ                | f     | Compare f with WREG, skip if f = WREG | 1 (2)  | 0011 0001 ffff | ffff | None               | 6,8   |

| CPFSGT                | f     | Compare f with WREG, skip if f > WREG | 1 (2)  | 0011 0010 ffff | ffff | None               | 2,6,8 |

| CPFSLT                | f     | Compare f with WREG, skip if f < WREG | 1 (2)  | 0011 0000 ffff | ffff | None               | 2,6,8 |

| DAW                   | f,s   | Decimal Adjust WREG Register          | 1      | 0010 111s ffff | ffff | C                  | 3     |

| DECF                  | f,d   | Decrement f                           | 1      | 0000 011d ffff | ffff | OV,C,DC,Z          |       |

| DECFSZ                | f,d   | Decrement f, skip if 0                | 1 (2)  | 0001 011d ffff | ffff | None               | 6,8   |

| DCFSNZ                | f,d   | Decrement f, skip if not 0            | 1 (2)  | 0010 011d ffff | ffff | None               | 6,8   |

| INCF                  | f,d   | Increment f                           | 1      | 0001 010d ffff | ffff | OV,C,DC,Z          |       |

| INCFSZ                | f,d   | Increment f, skip if 0                | 1 (2)  | 0001 111d ffff | ffff | None               | 6,8   |

| INFSNZ                | f,d   | Increment f, skip if not 0            | 1 (2)  | 0010 010d ffff | ffff | None               | 6,8   |

| IORWF                 | f,d   | Inclusive OR WREG with f              | 1      | 0000 100d ffff | ffff | Z                  |       |

| MOVFP                 | f,p   | Move f to p                           | 1      | 011p pppp ffff | ffff | None               |       |

| MOVPF                 | p,f   | Move p to f                           | 1      | 010p pppp ffff | ffff | Z                  |       |

| MOVWF                 | f     | Move WREG to f                        | 1      | 0000 0001 ffff | ffff | None               |       |

| MULWF                 | f     | Multiply WREG with f                  | 1      | 0011 0100 ffff | ffff | None               | 9     |

| NEGW                  | f,s   | Negate WREG                           | 1      | 0010 110s ffff | ffff | OV,C,DC,Z          | 1,3   |

| NOP                   | —     | No Operation                          | 1      | 0000 0000 0000 | 0000 | None               |       |

| RLCF                  | f,d   | Rotate left f through Carry           | 1      | 0001 101d ffff | ffff | С                  |       |

| RLNCF                 | f,d   | Rotate left f (no carry)              | 1      | 0010 001d ffff | ffff | None               |       |

| RRCF                  | f,d   | Rotate right f through Carry          | 1      | 0001 100d ffff | ffff | C                  |       |

| RRNCF                 | f,d   | Rotate right f (no carry)             | 1      | 0010 000d ffff | ffff | None               |       |

| SETF                  | f,s   | Set f                                 | 1      | 0010 101s ffff | ffff | None               | 3     |

| SUBWF                 | f,d   | Subtract WREG from f                  | 1      | 0000 010d ffff | ffff | OV,C,DC,Z          | 1     |

| SUBWFB                | f,d   | Subtract WREG from f with Borrow      | 1      | 0000 001d ffff | ffff | OV,C,DC,Z          | 1     |

| SWAPF                 | f,d   | Swap f                                | 1      | 0001 110d ffff | ffff | None               |       |

| TABLRD                | t,i,f | Table Read                            | 2 (3)  | 1010 10ti ffff | ffff | None               | 7     |

Legend: Refer to Table 15-1 for opcode field descriptions.

- Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- 5: Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

| Mnemonic,  |        | Description                                   | Cycles | 16-bit Opcode |      |      |      | Status    | Notes |

|------------|--------|-----------------------------------------------|--------|---------------|------|------|------|-----------|-------|

| Operands   |        |                                               |        | MSb           | MSb  |      | LSb  | Affected  |       |

| TABLWT     | t,i,f  | Table Write                                   | 2      | 1010          | 11ti | ffff | ffff | None      | 5     |

| TLRD       | t,f    | Table Latch Read                              | 1      | 1010          | 00tx | ffff | ffff | None      |       |

| TLWT       | t,f    | Table Latch Write                             | 1      | 1010          | 01tx | ffff | ffff | None      |       |

| TSTFSZ     | f      | Test f, skip if 0                             | 1 (2)  | 0011          | 0011 | ffff | ffff | None      | 6,8   |

| XORWF      | f,d    | Exclusive OR WREG with f                      | 1      | 0000          | 110d | ffff | ffff | Z         |       |

| BIT-ORIENT | ED FIL | E REGISTER OPERATIONS                         | 1      |               |      |      |      |           |       |

| BCF        | f,b    | Bit Clear f                                   | 1      | 1000          | 1bbb | ffff | ffff | None      |       |

| BSF        | f,b    | Bit Set f                                     | 1      | 1000          | 0bbb | ffff | ffff | None      |       |

| BTFSC      | f,b    | Bit test, skip if clear                       | 1 (2)  | 1001          | 1bbb | ffff | ffff | None      | 6,8   |

| BTFSS      | f,b    | Bit test, skip if set                         | 1 (2)  | 1001          | 0bbb | ffff | ffff | None      | 6,8   |

| BTG        | f,b    | Bit Toggle f                                  | 1      | 0011          | 1bbb | ffff | ffff | None      |       |

| LITERAL AN | ID CO  | NTROL OPERATIONS                              |        |               |      |      |      |           |       |

| ADDLW      | k      | ADD literal to WREG                           | 1      | 1011          | 0001 | kkkk | kkkk | OV,C,DC,Z |       |

| ANDLW      | k      | AND literal with WREG                         | 1      | 1011          | 0101 | kkkk | kkkk | Z         |       |

| CALL       | k      | Subroutine Call                               | 2      | 111k          | kkkk | kkkk | kkkk | None      | 7     |

| CLRWDT     | _      | Clear Watchdog Timer                          | 1      | 0000          | 0000 | 0000 | 0100 | TO,PD     |       |

| GOTO       | k      | Unconditional Branch                          | 2      | 110k          | kkkk | kkkk | kkkk | None      | 7     |

| IORLW      | k      | Inclusive OR literal with WREG                | 1      | 1011          | 0011 | kkkk | kkkk | Z         |       |

| LCALL      | k      | Long Call                                     | 2      | 1011          | 0111 | kkkk | kkkk | None      | 4,7   |

| MOVLB      | k      | Move literal to low nibble in BSR             | 1      | 1011          | 1000 | uuuu | kkkk | None      |       |

| MOVLR      | k      | Move literal to high nibble in BSR            | 1      | 1011          | 101x | kkkk | uuuu | None      | 9     |

| MOVLW      | k      | Move literal to WREG                          | 1      | 1011          | 0000 | kkkk | kkkk | None      |       |

| MULLW      | k      | Multiply literal with WREG                    | 1      | 1011          | 1100 | kkkk | kkkk | None      | 9     |

| RETFIE     | _      | Return from interrupt (and enable interrupts) | 2      | 0000          | 0000 | 0000 | 0101 | GLINTD    | 7     |

| RETLW      | k      | Return literal to WREG                        | 2      | 1011          | 0110 | kkkk | kkkk | None      | 7     |

| RETURN     | _      | Return from subroutine                        | 2      | 0000          | 0000 | 0000 | 0010 | None      | 7     |

| SLEEP      | _      | Enter SLEEP Mode                              | 1      | 0000          | 0000 | 0000 | 0011 | TO, PD    |       |

| SUBLW      | k      | Subtract WREG from literal                    | 1      | 1011          | 0010 | kkkk | kkkk | OV,C,DC,Z |       |

| XORLW      | k      | Exclusive OR literal with WREG                | 1      | 1011          | 0100 | kkkk | kkkk | Z         |       |

## TABLE 15-2: PIC17CXX INSTRUCTION SET (Cont.'d)

Legend: Refer to Table 15-1 for opcode field descriptions.

Note 1: 2's Complement method.

- 2: Unsigned arithmetic.

- 3: If s = '1', only the file is affected: If s = '0', both the WREG register and the file are affected; If only the Working register (WREG) is required to be affected, then f = WREG must be specified.

- 4: During an LCALL, the contents of PCLATH are loaded into the MSB of the PC and kkkk kkkk is loaded into the LSB of the PC (PCL)

- Multiple cycle instruction for EPROM programming when table pointer selects internal EPROM. The instruction is terminated by an interrupt event. When writing to external program memory, it is a two-cycle instruction.

- 6: Two-cycle instruction when condition is true, else single cycle instruction.

- 7: Two-cycle instruction except for TABLRD to PCL (program counter low byte) in which case it takes 3 cycles.

- 8: A "skip" means that instruction fetched during execution of current instruction is not executed, instead an NOP is executed.

- 9: These instructions are not available on the PIC17C42.

# PIC17C4X

| MOVLR                                                                                 | Move Literal to high nibble in BSR                                                                                                                                                                                                                                          |                                                                                                                                                                                             |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:                                                                               | [ <i>label</i> ] MOVLR k                                                                                                                                                                                                                                                    |                                                                                                                                                                                             |  |  |  |  |  |  |

| Operands:                                                                             | $0 \le k \le 15$                                                                                                                                                                                                                                                            |                                                                                                                                                                                             |  |  |  |  |  |  |

| Operation:                                                                            | $k \rightarrow (BSR < 7:4>)$                                                                                                                                                                                                                                                |                                                                                                                                                                                             |  |  |  |  |  |  |

| Status Affected:                                                                      | None                                                                                                                                                                                                                                                                        |                                                                                                                                                                                             |  |  |  |  |  |  |

| Encoding:                                                                             | 1011 101x kkkk uuuu                                                                                                                                                                                                                                                         |                                                                                                                                                                                             |  |  |  |  |  |  |

| Description:                                                                          | The 4-bit literal 'k' is loaded into the<br>most significant 4-bits of the Bank<br>Select Register (BSR). Only the high<br>4-bits of the Bank Select Register<br>are affected. The lower half of the<br>BSR is unchanged. The assembler<br>will encode the "u" fields as 0. | most significant 4-bits of the Bank<br>Select Register (BSR). Only the high<br>4-bits of the Bank Select Register<br>are affected. The lower half of the<br>BSR is unchanged. The assembler |  |  |  |  |  |  |

| Words:                                                                                | 1                                                                                                                                                                                                                                                                           |                                                                                                                                                                                             |  |  |  |  |  |  |

| Cycles:                                                                               | 1                                                                                                                                                                                                                                                                           |                                                                                                                                                                                             |  |  |  |  |  |  |

| Q Cycle Activity:                                                                     |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                             |  |  |  |  |  |  |

| Q1                                                                                    | Q2 Q3 Q4                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                           |  |  |  |  |  |  |

| Decode                                                                                | Read literal Execute Write   'k:u' literal 'k' to BSR<7:4>                                                                                                                                                                                                                  |                                                                                                                                                                                             |  |  |  |  |  |  |

| Example:                                                                              | MOVLR 5                                                                                                                                                                                                                                                                     |                                                                                                                                                                                             |  |  |  |  |  |  |

| Before Instruction<br>BSR register = 0x22<br>After Instruction<br>BSR register = 0x52 |                                                                                                                                                                                                                                                                             |                                                                                                                                                                                             |  |  |  |  |  |  |

| Note: This i                                                                          | instruction is not available in th<br>C42 device.                                                                                                                                                                                                                           | e                                                                                                                                                                                           |  |  |  |  |  |  |

| MOVLW             | Move Literal to WREG                           |                          |      |                  |  |  |  |  |

|-------------------|------------------------------------------------|--------------------------|------|------------------|--|--|--|--|

| Syntax:           | [ label ]                                      | [ <i>label</i> ] MOVLW k |      |                  |  |  |  |  |

| Operands:         | $0 \le k \le 25$                               | $0 \le k \le 255$        |      |                  |  |  |  |  |

| Operation:        | $k \rightarrow (WR)$                           | $k \rightarrow (WREG)$   |      |                  |  |  |  |  |

| Status Affected:  | None                                           | None                     |      |                  |  |  |  |  |

| Encoding:         | 1011                                           | 0000                     | kkkł | k kkkk           |  |  |  |  |

| Description:      | The eight bit literal 'k' is loaded into WREG. |                          |      |                  |  |  |  |  |

| Words:            | 1                                              |                          |      |                  |  |  |  |  |

| Cycles:           | 1                                              |                          |      |                  |  |  |  |  |

| Q Cycle Activity: |                                                |                          |      |                  |  |  |  |  |

| Q1                | Q2                                             | Q3                       | 3    | Q4               |  |  |  |  |

| Decode            | Read<br>literal 'k'                            | Execu                    | ute  | Write to<br>WREG |  |  |  |  |

| Example:          | MOVLW                                          | 0x5A                     |      |                  |  |  |  |  |

| After Instruct    | ion                                            |                          |      |                  |  |  |  |  |

WREG = 0x5A

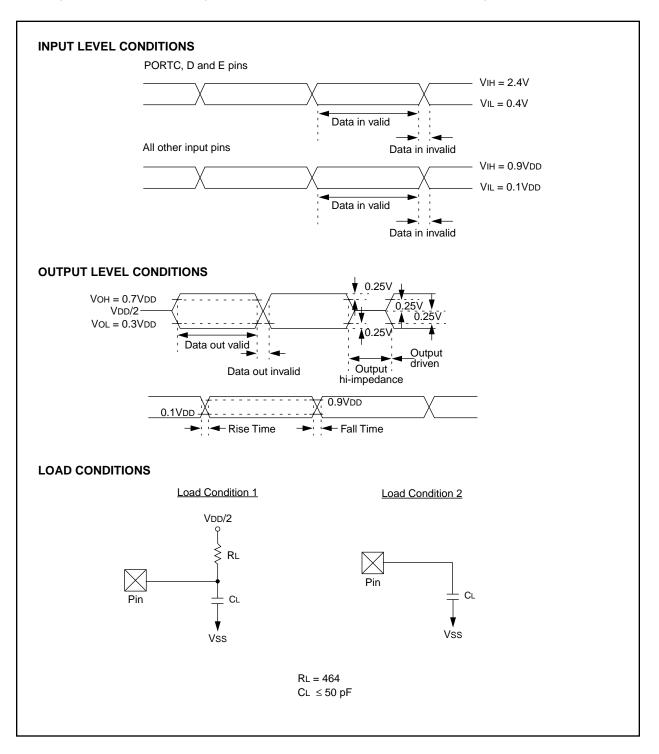

#### FIGURE 17-1: PARAMETER MEASUREMENT INFORMATION

All timings are measure between high and low measurement points as indicated in the figures below.

# PIC17C4X

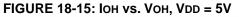

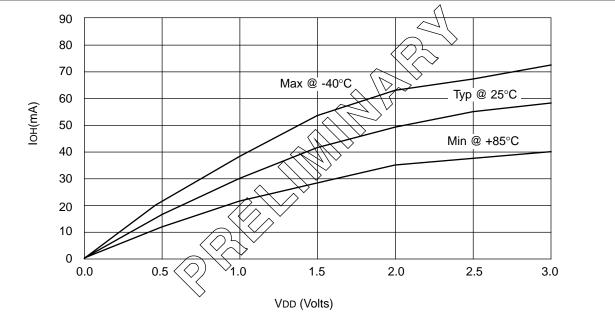

## Applicable Devices 42 R42 42A 43 R43 44

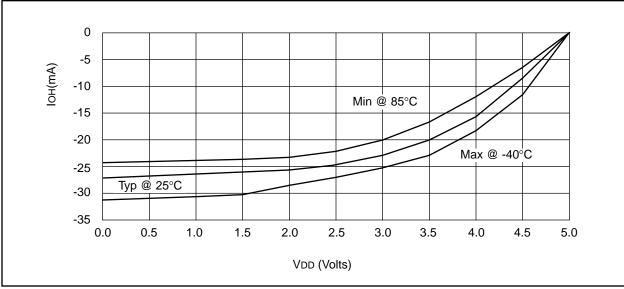

FIGURE 18-16: IOL vs. VOL, VDD = 3V

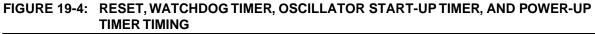

# TABLE 19-4:RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP<br/>TIMER REQUIREMENTS

| Parameter<br>No. | Sym      | Characteristic                                                                                                      |  |   | Тур†      | Max   | Units | Conditions         |  |

|------------------|----------|---------------------------------------------------------------------------------------------------------------------|--|---|-----------|-------|-------|--------------------|--|

| 30               | TmcL     | MCLR Pulse Width (low)                                                                                              |  |   | _         | _     | ns    | VDD = 5V           |  |

| 31               | Twdt     | Watchdog Timer Time-out Period<br>(Prescale = 1)                                                                    |  |   | 12        | 25 *  | ms    | VDD = 5V           |  |

| 32               | Tost     | Oscillation Start-up Timer Period                                                                                   |  |   | 1024Tosc§ | _     | ms    | Tosc = OSC1 period |  |

| 33               | Tpwrt    | Power-up Timer Period                                                                                               |  |   | 96        | 200 * | ms    | VDD = 5V           |  |

| 35               | TmcL2adl | TmcL2adIMCLR to System Inter-<br>face bus (AD15:AD0>)PIC17CR42/42A/<br>43/R43/44InvalidPIC17LCR42/<br>42A/43/R43/44 |  | — | _         | 100 * | ns    |                    |  |

|                  |          |                                                                                                                     |  | — | —         | 120 * | ns    |                    |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

§ This specification ensured by design.

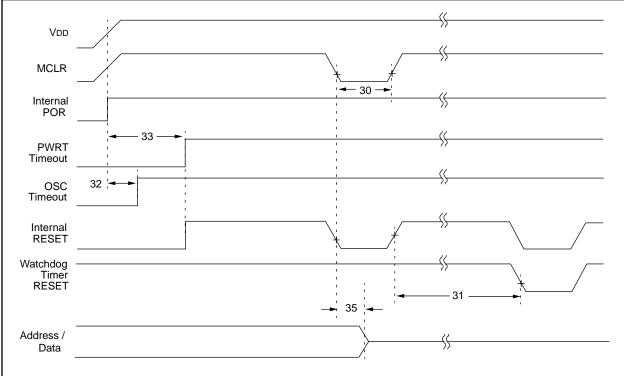

# TABLE 19-12: MEMORY INTERFACE READ REQUIREMENTS (NOT SUPPORTED IN PIC17LC4X DEVICES)

| Parameter<br>No. | Sym      | Characteristic                                            | Min           | Тур†      | Max          | Units | Conditions |

|------------------|----------|-----------------------------------------------------------|---------------|-----------|--------------|-------|------------|

| 150              | TadV2alL | AD15:AD0 (address) valid to ALE↓<br>(address setup time)  | 0.25Tcy - 10  | _         | _            | ns    |            |

| 151              | TalL2adl | ALE↓ to address out invalid (address hold time)           | 5*            |           | _            | ns    |            |

| 160              | TadZ2oeL | AD15:AD0 hi-impedance to $\overline{\text{OE}}\downarrow$ | 0*            | _         | —            | ns    |            |

| 161              | ToeH2adD | OE↑ to AD15:AD0 driven                                    | 0.25Tcy - 15  | _         | _            | ns    |            |

| 162              | TadV2oeH | Data in valid before OE↑<br>(data setup time)             | 35            | _         | _            | ns    |            |

| 163              | ToeH2adI | OE↑to data in invalid (data hold time)                    | 0             | _         | _            | ns    |            |

| 164              | TalH     | ALE pulse width                                           | —             | 0.25Tcy § | —            | ns    |            |

| 165              | ToeL     | OE pulse width                                            | 0.5Tcy - 35 § | _         | _            | ns    |            |

| 166              | TalH2alH | ALE↑ to ALE↑(cycle time)                                  | —             | TCY §     | _            | ns    |            |

| 167              | Тасс     | Address access time                                       | _             | _         | 0.75Tcy - 30 | ns    |            |

| 168              | Тое      | Output enable access time<br>(OE low to Data Valid)       | _             | _         | 0.5Tcy - 45  | ns    |            |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

\*

## FIGURE 20-17: IOL vs. VOL, VDD = 5V

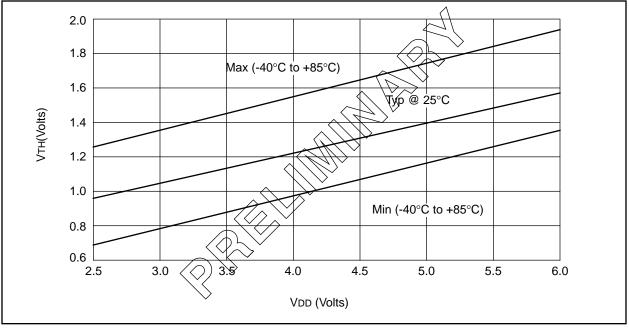

#### FIGURE 20-18: VTH (INPUT THRESHOLD VOLTAGE) OF I/O PINS (TTL) VS. VDD

# PIC17C4X

| Figure 6-12:                                                                                   | Program Counter using The CALL and                      |

|------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Figure 6-13:                                                                                   | GOTO Instructions                                       |

| Figure 7-1:                                                                                    | TLWT Instruction Operation43                            |

| Figure 7-2:                                                                                    | TABLWT Instruction Operation                            |

| Figure 7-3:                                                                                    | TLRD Instruction Operation                              |

| Figure 7-4:                                                                                    | TABLRD Instruction Operation                            |

|                                                                                                |                                                         |

| Figure 7-5:                                                                                    | TABLWT Write Timing                                     |

| Figure 7-6:                                                                                    | (External Memory) 46<br>Consecutive TABLWT Write Timing |

|                                                                                                | (External Memory)47                                     |

| Figure 7-7:                                                                                    | TABLRD Timing48                                         |

| Figure 7-8:                                                                                    | TABLRD Timing (Consecutive TABLRD                       |

| 0                                                                                              | Instructions)                                           |

| Figure 9-1:                                                                                    | RA0 and RA1 Block Diagram53                             |

| Figure 9-2:                                                                                    | RA2 and RA3 Block Diagram                               |

|                                                                                                |                                                         |

| Figure 9-3:                                                                                    | RA4 and RA5 Block Diagram54                             |

| Figure 9-4:                                                                                    | Block Diagram of RB<7:4> and RB<1:0><br>Port Pins       |

| Figure 9-5:                                                                                    | Block Diagram of RB3 and RB2 Port Pins56                |

| 0                                                                                              |                                                         |

| Figure 9-6:                                                                                    | Block Diagram of RC<7:0> Port Pins                      |

| Figure 9-7:                                                                                    | PORTD Block Diagram                                     |

|                                                                                                | (in I/O Port Mode)60                                    |

| Figure 9-8:                                                                                    | PORTE Block Diagram                                     |

|                                                                                                | (in I/O Port Mode)                                      |

| Figure 9-9:                                                                                    | Successive I/O Operation                                |

| Figure 11-1:                                                                                   | T0STA Register (Address: 05h,                           |

| rigulo II I.                                                                                   | Unbanked)                                               |

| Figure 11-2:                                                                                   | Timer0 Module Block Diagram                             |

| 0                                                                                              |                                                         |

| Figure 11-3:                                                                                   | TMR0 Timing with External Clock                         |

|                                                                                                | (Increment on Falling Edge)68                           |

| Figure 11-4:                                                                                   | TMR0 Timing: Write High or Low Byte 69                  |

| Figure 11-5:                                                                                   | TMR0 Read/Write in Timer Mode70                         |

| Figure 12-1:                                                                                   | TCON1 Register (Address: 16h, Bank 3) 71                |

| Figure 12-2:                                                                                   | TCON2 Register (Address: 17h, Bank 3) 72                |

| Figure 12-3:                                                                                   | Timer1 and Timer2 in Two 8-bit                          |

| •                                                                                              | Timer/Counter Mode73                                    |

| Figure 12-4:                                                                                   | TMR1 and TMR2 in 16-bit Timer/Counter                   |

| 3.                                                                                             | Mode74                                                  |

| Figure 12-5:                                                                                   | Simplified PWM Block Diagram75                          |

| Figure 12-6:                                                                                   | PWM Output                                              |

| Figure 12-7:                                                                                   | Timer3 with One Capture and One                         |

| rigute 12-7.                                                                                   | Period Register Block Diagram                           |

|                                                                                                |                                                         |

| Figure 12-8:                                                                                   | Timer3 with Two Capture Registers                       |

| -                                                                                              | Block Diagram                                           |

| Figure 12-9:                                                                                   | TMR1, TMR2, and TMR3 Operation in                       |

|                                                                                                | External Clock Mode80                                   |

| Figure 12-10:                                                                                  | TMR1, TMR2, and TMR3 Operation in                       |

|                                                                                                | Timer Mode81                                            |

| Figure 13-1:                                                                                   | TXSTA Register (Address: 15h, Bank 0) 83                |

| Figure 13-2:                                                                                   | RCSTA Register (Address: 13h, Bank 0) 84                |

| Figure 13-3:                                                                                   | USART Transmit                                          |

| Figure 13-4:                                                                                   | USART Receive85                                         |

| Figure 13-5:                                                                                   |                                                         |

| Figure 13-5:<br>Figure 13-6:                                                                   | Acynchronouic Mactor Transmission 00                    |

|                                                                                                | Asynchronous Master Transmission                        |

| riguie 10-0.                                                                                   | Asynchronous Master Transmission                        |

| -                                                                                              | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:                                                                                   | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:<br>Figure 13-8:                                                                   | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:                                                                                   | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:<br>Figure 13-8:                                                                   | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:<br>Figure 13-8:<br>Figure 13-9:                                                   | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:<br>Figure 13-8:<br>Figure 13-9:<br>Figure 13-10:                                  | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:<br>Figure 13-8:<br>Figure 13-9:                                                   | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:<br>Figure 13-8:<br>Figure 13-9:<br>Figure 13-10:<br>Figure 13-11:                 | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:<br>Figure 13-8:<br>Figure 13-9:<br>Figure 13-10:<br>Figure 13-11:<br>Figure 14-1: | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 13-7:<br>Figure 13-8:<br>Figure 13-9:<br>Figure 13-10:<br>Figure 13-11:                 | Asynchronous Master Transmission<br>(Back to Back)      |

| Figure 14-3:  | Crystal Operation, Overtone Crystals   |     |

|---------------|----------------------------------------|-----|

|               | (XT OSC Configuration)                 | 101 |

| Figure 14-4:  | External Clock Input Operation         |     |

|               | (EC OSC Configuration)                 | 101 |

| Figure 14-5:  | External Parallel Resonant Crystal     |     |

|               | Oscillator Circuit                     | 102 |

| Figure 14-6:  | External Series Resonant Crystal       |     |

|               | Oscillator Circuit                     | 102 |

| Figure 14-7:  | RC Oscillator Mode                     |     |

| Figure 14-8:  | Watchdog Timer Block Diagram           | 104 |

| Figure 14-9:  | Wake-up From Sleep Through Interrupt   | 105 |

| Figure 15-1:  | General Format for Instructions        | 108 |

| Figure 15-2:  | Q Cycle Activity                       |     |

| Figure 17-1:  | Parameter Measurement Information      |     |

| Figure 17-2:  | External Clock Timing                  | 155 |

| Figure 17-3:  | CLKOUT and I/O Timing                  |     |

| Figure 17-4:  | Reset, Watchdog Timer,                 |     |

|               | Oscillator Start-Up Timer and          |     |

|               | Power-Up Timer Timing                  | 157 |

| Figure 17-5:  | Timer0 Clock Timings                   |     |

| Figure 17-6:  | Timer1, Timer2, And Timer3 Clock       | 100 |

| Figure 17-0.  | Timings                                | 150 |

| Figure 17-7:  | Capture Timings                        |     |

|               |                                        |     |

| Figure 17-8:  | PWM Timings                            | 159 |

| Figure 17-9:  | USART Module: Synchronous              |     |

|               | Transmission (Master/Slave) Timing     | 160 |

| Figure 17-10  | ,<br>,                                 |     |

|               | (Master/Slave) Timing                  |     |

| Figure 17-11  |                                        |     |

| Figure 17-12  | : Memory Interface Read Timing         | 162 |

| Figure 18-1:  | Typical RC Oscillator Frequency        |     |

|               | vs. Temperature                        | 163 |

| Figure 18-2:  | Typical RC Oscillator Frequency        |     |

| •             | vs. VDD                                | 164 |

| Figure 18-3:  | Typical RC Oscillator Frequency        |     |

| 0             | vs. VDD                                | 164 |

| Figure 18-4:  | Typical RC Oscillator Frequency        |     |

| 0             | vs. VDD                                | 165 |

| Figure 18-5:  | Transconductance (gm) of LF Oscillator |     |

| <b>J</b>      | vs. VDD                                | 166 |

| Figure 18-6:  | Transconductance (gm) of XT Oscillator |     |

|               | vs. VDD                                | 166 |

| Figure 18-7:  | Typical IDD vs. Frequency (External    | 100 |

| rigulo lo l.  | Clock 25°C)                            | 167 |

| Figure 18-8:  | Maximum IDD vs. Frequency (External    | 107 |

| Figure 10-0.  |                                        | 167 |

| Figure 19 0.  | Clock 125°C to -40°C)                  | 107 |

| Figure 18-9:  | Typical IPD vs. VDD Watchdog           | 400 |

| E:            | Disabled 25°C                          | 100 |

| Figure 18-10  |                                        | 400 |