#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | UART/USART                                                                |

| Peripherals                | POR, PWM, WDT                                                             |

| Number of I/O              | 33                                                                        |

| Program Memory Size        | 16KB (8K x 16)                                                            |

| Program Memory Type        | ОТР                                                                       |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 454 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 6V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | External                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 40-DIP (0.600", 15.24mm)                                                  |

| Supplier Device Package    | 40-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic17lc44-08i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

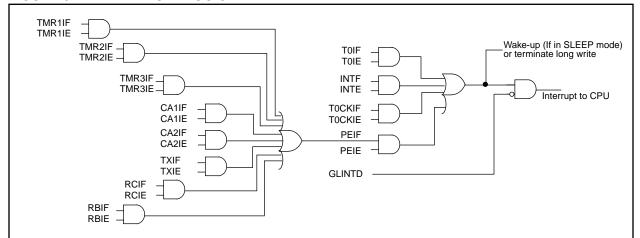

### 5.0 INTERRUPTS

The PIC17C4X devices have 11 sources of interrupt:

- External interrupt from the RA0/INT pin

- Change on RB7:RB0 pins

- TMR0 Overflow

- TMR1 Overflow

- TMR2 Overflow

- TMR3 Overflow

- USART Transmit buffer empty

- USART Receive buffer full

- Capture1

- Capture2

- T0CKI edge occurred

There are four registers used in the control and status of interrupts. These are:

- CPUSTA

- INTSTA

- PIE

- PIR

The CPUSTA register contains the GLINTD bit. This is the Global Interrupt Disable bit. When this bit is set, all interrupts are disabled. This bit is part of the controller core functionality and is described in the Memory Organization section. When an interrupt is responded to, the GLINTD bit is automatically set to disable any further interrupt, the return address is pushed onto the stack and the PC is loaded with the interrupt vector address. There are four interrupt vectors. Each vector address is for a specific interrupt source (except the peripheral interrupts which have the same vector address). These sources are:

- External interrupt from the RA0/INT pin

- TMR0 Overflow

- T0CKI edge occurred

- Any peripheral interrupt

When program execution vectors to one of these interrupt vector addresses (except for the peripheral interrupt address), the interrupt flag bit is automatically cleared. Vectoring to the peripheral interrupt vector address does not automatically clear the source of the interrupt. In the peripheral interrupt service routine, the source(s) of the interrupt can be determined by testing the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid infinite interrupt requests.

All of the individual interrupt flag bits will be set regardless of the status of their corresponding mask bit or the GLINTD bit.

For external interrupt events, there will be an interrupt latency. For two cycle instructions, the latency could be one instruction cycle longer.

The "return from interrupt" instruction, RETFIE, can be used to mark the end of the interrupt service routine. When this instruction is executed, the stack is "POPed", and the GLINTD bit is cleared (to re-enable interrupts).

### FIGURE 5-1: INTERRUPT LOGIC

© 1996 Microchip Technology Inc.

### 5.3 <u>Peripheral Interrupt Request Register</u> (PIR)

This register contains the individual flag bits for the peripheral interrupts.

**Note:** These bits will be set by the specified condition, even if the corresponding interrupt enable bit is cleared (interrupt disabled), or the GLINTD bit is set (all interrupts disabled). Before enabling an interrupt, the user may wish to clear the interrupt flag to ensure that the program does not immediately branch to the peripheral interrupt service routine.

### FIGURE 5-4: PIR REGISTER (ADDRESS: 16h, BANK 1)

|        | 0 R/W-0 R/W-0 R/W-0 R/W-0 R-1 R-0                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| RBIF   |                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

| bit7   | bit0 W = Writable bit<br>-n = Value at POR reset                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| bit 7: | <b>RBIF</b> : PORTB Interrupt on Change Flag bit<br>1 = One of the PORTB inputs changed (Software must end the mismatch condition)<br>0 = None of the PORTB inputs have changed                                                                                              |  |  |  |  |  |  |  |  |  |

| bit 6: | TMR3IF: Timer3 Interrupt Flag bit<br>If Capture1 is enabled (CA1/PR3 = 1)<br>1 = Timer3 overflowed<br>0 = Timer3 did not overflow                                                                                                                                            |  |  |  |  |  |  |  |  |  |

|        | If Capture1 is disabled (CA1/ $\overline{PR3}$ = 0)<br>1 = Timer3 value has rolled over to 0000h from equalling the period register (PR3H:PR3L) value<br>0 = Timer3 value has not rolled over to 0000h from equalling the period register (PR3H:PR3L) value                  |  |  |  |  |  |  |  |  |  |

| bit 5: | <b>TMR2IF</b> : Timer2 Interrupt Flag bit<br>1 = Timer2 value has rolled over to 0000h from equalling the period register (PR2) value<br>0 = Timer2 value has not rolled over to 0000h from equalling the period register (PR2) value                                        |  |  |  |  |  |  |  |  |  |

| bit 4: | <b>TMR1IF</b> : Timer1 Interrupt Flag bit<br>If Timer1 is in 8-bit mode (T16 = 0)<br>1 = Timer1 value has rolled over to 0000h from equalling the period register (PR) value<br>0 = Timer1 value has not rolled over to 0000h from equalling the period register (PR2) value |  |  |  |  |  |  |  |  |  |

|        | If Timer1 is in 16-bit mode (T16 = 1)<br>1 = TMR1:TMR2 value has rolled over to 0000h from equalling the period register (PR1:PR2) value<br>0 = TMR1:TMR2 value has not rolled over to 0000h from equalling the period register (PR1:PR2) value                              |  |  |  |  |  |  |  |  |  |

| bit 3: | <b>CA2IF</b> : Capture2 Interrupt Flag bit<br>1 = Capture event occurred on RB1/CAP2 pin<br>0 = Capture event did not occur on RB1/CAP2 pin                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 2: | <b>CA1IF</b> : Capture1 Interrupt Flag bit<br>1 = Capture event occurred on RB0/CAP1 pin<br>0 = Capture event did not occur on RB0/CAP1 pin                                                                                                                                  |  |  |  |  |  |  |  |  |  |

| bit 1: | <b>TXIF</b> : USART Transmit Interrupt Flag bit<br>1 = Transmit buffer is empty<br>0 = Transmit buffer is full                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| bit 0: | RCIF: USART Receive Interrupt Flag bit<br>1 = Receive buffer is full<br>0 = Receive buffer is empty                                                                                                                                                                          |  |  |  |  |  |  |  |  |  |

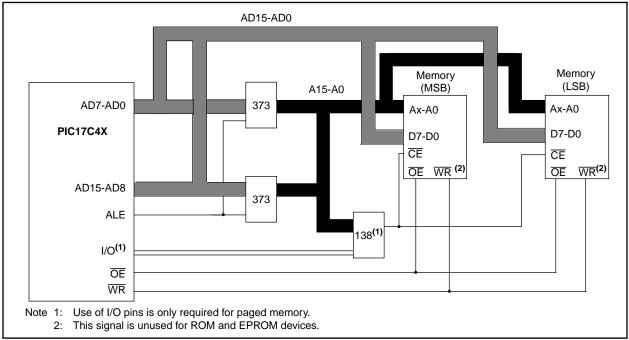

### 6.1.2 EXTERNAL MEMORY INTERFACE

When either microprocessor or extended microcontroller mode is selected, PORTC, PORTD and PORTE are configured as the system bus. PORTC and PORTD are the multiplexed address/data bus and PORTE is for the control signals. External components are needed to demultiplex the address and data. This can be done as shown in Figure 6-4. The waveforms of address and data are shown in Figure 6-3. For complete timings, please refer to the electrical specification section.

### FIGURE 6-3: EXTERNAL PROGRAM MEMORY ACCESS WAVEFORMS

| :      | Q1   Q2   Q3   Q4   | Q1   Q2   Q3   Q4   Q1 |

|--------|---------------------|------------------------|

| AD     | X                   |                        |

| <15:0> | Address out Data in | Address out Data out   |

| ALE    |                     |                        |

| OE;    | '4'                 | · · · ·                |

| WR     | '1'                 | <u> </u>               |

|        | Read cycle          | Write cycle            |

|        |                     | , white cycle          |

The system bus requires that there is no bus conflict (minimal leakage), so the output value (address) will be capacitively held at the desired value.

As the speed of the processor increases, external EPROM memory with faster access time must be used. Table 6-2 lists external memory speed requirements for a given PIC17C4X device frequency.

In extended microcontroller mode, when the device is executing out of internal memory, the control signals will continue to be active. That is, they indicate the action that is occurring in the internal memory. The external memory access is ignored.

This following selection is for use with Microchip EPROMs. For interfacing to other manufacturers memory, please refer to the electrical specifications of the desired PIC17C4X device, as well as the desired memory device to ensure compatibility.

| TABLE 6-2: | EPROM MEMORY ACCESS  |

|------------|----------------------|

|            | TIME ORDERING SUFFIX |

| PIC17C4X                | Instruction         | EPRON    | I Suffix             |

|-------------------------|---------------------|----------|----------------------|

| Oscillator<br>Frequency | Cycle<br>Time (Tcy) | PIC17C42 | PIC17C43<br>PIC17C44 |

| 8 MHz                   | 500 ns              | -25      | -25                  |

| 16 MHz                  | 250 ns              | -12      | -15                  |

| 20 MHz                  | 200 ns              | -90      | -10                  |

| 25 MHz                  | 160 ns              | N.A.     | -70                  |

| 33 MHz                  | 121 ns              | N.A.     | (1)                  |

Note 1: The access times for this requires the use of fast SRAMS.

**Note:** The external memory interface is not supported for the LC devices.

FIGURE 6-4: TYPICAL EXTERNAL PROGRAM MEMORY CONNECTION DIAGRAM

© 1996 Microchip Technology Inc.

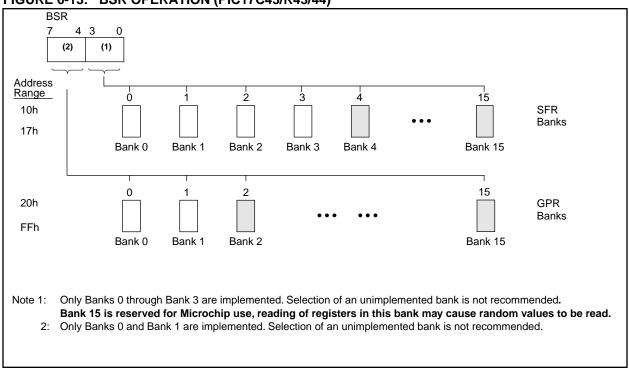

### 6.8 Bank Select Register (BSR)

The BSR is used to switch between banks in the data memory area (Figure 6-13). In the PIC17C42, PIC17CR42, and PIC17C42A only the lower nibble is implemented. While in the PIC17C43, PIC17CR43, and PIC17C44 devices, the entire byte is implemented. The lower nibble is used to select the peripheral register bank. The upper nibble is used to select the general purpose memory bank.

All the Special Function Registers (SFRs) are mapped into the data memory space. In order to accommodate the large number of registers, a banking scheme has been used. A segment of the SFRs, from address 10h to address 17h, is banked. The lower nibble of the bank select register (BSR) selects the currently active "peripheral bank." Effort has been made to group the peripheral registers of related functionality in one bank. However, it will still be necessary to switch from bank to bank in order to address all peripherals related to a single task. To assist this, a MOVLB bank instruction is in the instruction set. For the PIC17C43, PIC17CR43, and PIC17C44 devices, the need for a large general purpose memory space dictated a general purpose RAM banking scheme. The upper nibble of the BSR selects the currently active general purpose RAM bank. To assist this, a MOVLR bank instruction has been provided in the instruction set.

If the currently selected bank is not implemented (such as Bank 13), any read will read all '0's. Any write is completed to the bit bucket and the ALU status bits will be set/cleared as appropriate.

**Note:** Registers in Bank 15 in the Special Function Register area, are reserved for Microchip use. Reading of registers in this bank may cause random values to be read.

### FIGURE 6-13: BSR OPERATION (PIC17C43/R43/44)

Example 8-4 shows the sequence to do an 16 x 16 signed multiply. Equation 8-2 shows the algorithm that used. The 32-bit result is stored in four registers RES3:RES0. To account for the sign bits of the arguments, each argument pairs most significant bit (MSb) is tested and the appropriate subtractions are done.

| EQUATION 8-2: | 16 x 16 SIGNED |

|---------------|----------------|

|               | MULTIPLICATION |

|               | ALGORITHM      |

RES3:RES0

- = ARG1H:ARG1L \* ARG2H:ARG2L

- - (-1 \* ARG1H<7> \* ARG2H:ARG2L \* 2<sup>16</sup>)

## EXAMPLE 8-4: 16 x 16 SIGNED MULTIPLY

|     |          | ROUTI       | N | E                |

|-----|----------|-------------|---|------------------|

|     | MOVFP    | ARG1L, WREG |   |                  |

|     | MULWF    | ARG2L       | ; | ARG1L * ARG2L -> |

|     |          |             |   | PRODH:PRODL      |

|     | MOVPF    | PRODH, RES1 |   |                  |

|     |          | PRODL, RESO |   |                  |

| ;   |          | - ,         |   |                  |

|     | MOVFP    | ARG1H, WREG |   |                  |

|     |          |             |   | ARG1H * ARG2H -> |

|     | 110201   | into bii    | ; |                  |

|     | MOVPF    | PRODH, RES3 |   | TRODUCTRODE      |

|     |          | PRODL, RES2 |   |                  |

| ;   | 110 11 1 | TRODE, REDZ | ' |                  |

| '   | MOVFP    | ARG1L, WREG |   |                  |

|     |          |             |   | ARG1L * ARG2H -> |

|     | HOLMI    | 1110211     | ; |                  |

|     | MOVFP    | PRODL, WREG |   | TRODITITRODE     |

|     |          |             |   | Add cross        |

|     |          |             |   |                  |

|     |          |             | ; | products         |

|     |          |             |   |                  |

|     |          | WREG, F     | ; |                  |

|     | ADDWFC   | RES3, F     | ; |                  |

| ;   | NOTED    |             |   |                  |

|     |          | ARG1H, WREG | ' |                  |

|     | MULWF    | ARG2L       |   | ARG1H * ARG2L -> |

|     |          |             | , | PRODH:PRODL      |

|     | MOMED    |             |   |                  |

|     |          | PRODL, WREG |   | Add among        |

|     | ADDWF    | RES1, F     |   |                  |

|     |          | PRODH, WREG |   | products         |

|     |          |             | ; |                  |

|     | CLRF     | WREG, F     | ; |                  |

|     | ADDWFC   | RES3, F     | ; |                  |

| ;   |          |             |   |                  |

|     |          | ARG2H, 7    | ' | ARG2H:ARG2L neg? |

|     |          |             |   | no, check ARG1   |

|     | MOVFP    | ARG1L, WREG |   |                  |

|     |          | RES2        | ; |                  |

|     | MOVFP    | ARG1H, WREG | ; |                  |

|     | SUBWFB   | RES3        |   |                  |

| ;   |          |             |   |                  |

| SIC | GN_ARG1  |             |   |                  |

|     |          |             |   | ARG1H:ARG1L neg? |

|     | GOTO     | CONT_CODE   |   | no, done         |

|     |          | ARG2L, WREG |   |                  |

|     | SUBWF    | RES2        | ; |                  |

|     | MOVFP    | ARG2H, WREG | ; |                  |

|     | SUBWFB   | RES3        |   |                  |

| ;   |          |             |   |                  |

| COI | NT_CODE  |             |   |                  |

|     | :        |             |   |                  |

### 9.5 I/O Programming Considerations

### 9.5.1 BI-DIRECTIONAL I/O PORTS

Any instruction which writes, operates internally as a read followed by a write operation. For example, the BCF and BSF instructions read the register into the CPU, execute the bit operation, and write the result back to the register. Caution must be used when these instructions are applied to a port with both inputs and outputs defined. For example, a BSF operation on bit5 of PORTB will cause all eight bits of PORTB to be read into the CPU. Then the BSF operation takes place on bit5 and PORTB is written to the output latches. If another bit of PORTB is used as a bi-directional I/O pin (e.g. bit0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and re-written to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the input mode, no problem occurs. However, if bit0 is switched into output mode later on, the content of the data latch may now be unknown.

Reading a port reads the values of the port pins. Writing to the port register writes the value to the port latch. When using read-modify-write instructions (BCF, BSF, BTG, etc.) on a port, the value of the port pins is read, the desired operation is performed with this value, and the value is then written to the port latch.

Example 9-5 shows the effect of two sequential read-modify-write instructions on an I/O port.

### EXAMPLE 9-5: READ MODIFY WRITE INSTRUCTIONS ON AN I/O PORT

; Initial PORT settings: PORTB<7:4> Inputs PORTB<3:0> Outputs ; ; PORTB<7:6> have pull-ups and are ; not connected to other circuitry ; PORT latch PORT pins ; ; \_\_\_\_\_ \_\_\_\_\_ ; PORTB, 7 BCF 01pp pppp 11pp pppp BCF PORTB, 6 10pp pppp 11pp pppp ; BCF DDRB, 7 10pp pppp 11pp pppp BCF DDRB, 6 10pp pppp 10pp pppp ; ; Note that the user may have expected the ; pin values to be 00pp pppp. The 2nd BCF ; caused RB7 to be latched as the pin value ; (High).

Note: A pin actively outputting a Low or High should not be driven from external devices in order to change the level on this pin (i.e. "wired-or", "wired-and"). The resulting high output currents may damage the device.

### 9.5.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 9-9). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should be such to allow the pin voltage to stabilize (load dependent) before executing the instruction that reads the values on that I/O port. Otherwise, the previous state of that pin may be read into the CPU rather than the "new" state. When in doubt, it is better to separate these instructions with a NOP or another instruction not accessing this I/O port.

### FIGURE 9-9: SUCCESSIVE I/O OPERATION

| Instruction<br>fetched  | Q1  Q2  Q3  Q4<br>PC<br>MOVWF PORTB<br>write to<br>PORTB | PC + 1                           | Q1 Q2 Q3 Q4 Q1 Q2 Q3 Q4<br><u>PC+2</u> <u>PC+3</u><br>NOP NOP | Note:<br>This example shows a write to PORTB<br>followed by a read from PORTB.<br>Note that:<br>data setup time = (0.25 Tcy - TPD)<br>where TcY = instruction cycle.<br>TPD = propagation delay |

|-------------------------|----------------------------------------------------------|----------------------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB7:RB0                 |                                                          |                                  | X                                                             | Therefore, at higher clock<br>frequencies, a write followed by a                                                                                                                                |

|                         |                                                          |                                  | Port pin<br>sampled here                                      | read may be problematic.                                                                                                                                                                        |

| Instruction<br>executed |                                                          | MOVWF PORTB<br>write to<br>PORTB | MOVF PORTB,W NOP                                              |                                                                                                                                                                                                 |

|                         |                                                          |                                  | · · · · ·                                                     |                                                                                                                                                                                                 |

### 10.0 OVERVIEW OF TIMER RESOURCES

The PIC17C4X has four timer modules. Each module can generate an interrupt to indicate that an event has occurred. These timers are called:

- Timer0 16-bit timer with programmable 8-bit

- prescaler

- Timer1 8-bit timer

- Timer2 8-bit timer

- Timer3 16-bit timer

For enhanced time-base functionality, two input Captures and two Pulse Width Modulation (PWM) outputs are possible. The PWMs use the TMR1 and TMR2 resources and the input Captures use the TMR3 resource.

### 10.1 <u>Timer0 Overview</u>

The Timer0 module is a simple 16-bit overflow counter. The clock source can be either the internal system clock (Fosc/4) or an external clock.

The Timer0 module also has a programmable prescaler option. The PS3:PS0 bits (T0STA<4:1>) determine the prescaler value. TMR0 can increment at the following rates: 1:1, 1:2, 1:4, 1:8, 1:16, 1:32, 1:64, 1:128, 1:256.

When TImer0's clock source is an external clock, the Timer0 module can be selected to increment on either the rising or falling edge.

Synchronization of the external clock occurs after the prescaler. When the prescaler is used, the external clock frequency may be higher then the device's frequency. The maximum frequency is 50 MHz, given the high and low time requirements of the clock.

### 10.2 <u>Timer1 Overview</u>

The TImer0 module is an 8-bit timer/counter with an 8bit period register (PR1). When the TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the Timer2 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR1 register is the LSB and TMR2 is the MSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

### 10.3 <u>Timer2 Overview</u>

The TMR2 module is an 8-bit timer/counter with an 8bit period register (PR2). When the TMR2 value rolls over from the period match value to 0h, the TMR2IF flag is set, and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB4/TCLK12 pin, which can also be selected to be the clock for the TMR1 module.

TMR1 can be concatenated to TMR2 to form a 16-bit timer. The TMR2 register is the MSB and TMR1 is the LSB. When in the 16-bit timer mode, there is a corresponding 16-bit period register (PR2:PR1). When the TMR2:TMR1 value rolls over from the period match value to 0h, the TMR1IF flag is set, and an interrupt will be generated when enabled.

### 10.4 <u>Timer3 Overview</u>

The TImer3 module is a 16-bit timer/counter with a 16bit period register. When the TMR3H:TMR3L value rolls over to 0h, the TMR3IF bit is set and an interrupt will be generated when enabled. In counter mode, the clock comes from the RB5/TCLK3 pin.

When operating in the dual capture mode, the period registers become the second 16-bit capture register.

### 10.5 Role of the Timer/Counters

The timer modules are general purpose, but have dedicated resources associated with them. Tlmer1 and Timer2 are the time-bases for the two Pulse Width Modulation (PWM) outputs, while Timer3 is the timebase for the two input captures.

© 1996 Microchip Technology Inc.

NOTES:

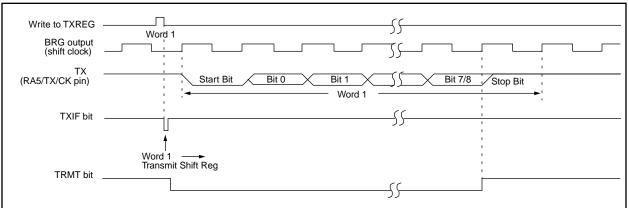

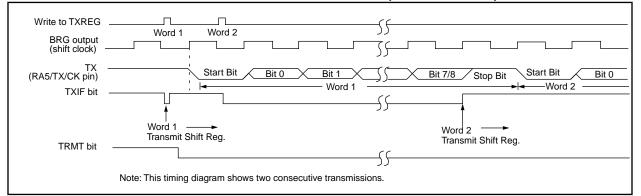

### FIGURE 13-5: ASYNCHRONOUS MASTER TRANSMISSION

### FIGURE 13-6: ASYNCHRONOUS MASTER TRANSMISSION (BACK TO BACK)

### TABLE 13-5: REGISTERS ASSOCIATED WITH ASYNCHRONOUS TRANSMISSION

| Address     | Name  | Bit 7       | Bit 6                         | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-------------|-------------------------------|--------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR   | RBIF        | TMR3IF                        | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA | SPEN        | RX9                           | SREN   | CREN   | —     | FERR  | OERR  | RX9D  | x00- 0000                     | 0000 -00u                               |

| 16h, Bank 0 | TXREG | Serial port | Serial port transmit register |        |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE   | RBIE        | TMR3IE                        | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA | CSRC        | TX9                           | TXEN   | SYNC   | —     | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | SPBRG | Baud rate   | Baud rate generator register  |        |        |       |       |       |       | xxxx xxxx                     | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for asynchronous transmission.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

| Address     | Name  | Bit 7     | Bit 6                        | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-on<br>Reset | Value on all<br>other resets<br>(Note1) |

|-------------|-------|-----------|------------------------------|--------|--------|-------|-------|-------|-------|-------------------------------|-----------------------------------------|

| 16h, Bank 1 | PIR   | RBIF      | TMR3IF                       | TMR2IF | TMR1IF | CA2IF | CA1IF | TXIF  | RCIF  | 0000 0010                     | 0000 0010                               |

| 13h, Bank 0 | RCSTA | SPEN      | RX9                          | SREN   | CREN   | _     | FERR  | OERR  | RX9D  | 0000 -00x                     | 0000 -00u                               |

| 14h, Bank 0 | RCREG | RX7       | RX6                          | RX5    | RX4    | RX3   | RX2   | RX1   | RX0   | xxxx xxxx                     | uuuu uuuu                               |

| 17h, Bank 1 | PIE   | RBIE      | TMR3IE                       | TMR2IE | TMR1IE | CA2IE | CA1IE | TXIE  | RCIE  | 0000 0000                     | 0000 0000                               |

| 15h, Bank 0 | TXSTA | CSRC      | TX9                          | TXEN   | SYNC   | -     | —     | TRMT  | TX9D  | 00001x                        | 00001u                                  |

| 17h, Bank 0 | SPBRG | Baud rate | Baud rate generator register |        |        |       |       |       |       |                               | uuuu uuuu                               |

Legend: x = unknown, u = unchanged, - = unimplemented read as a '0', shaded cells are not used for synchronous master reception.

Note 1: Other (non power-up) resets include: external reset through MCLR and Watchdog Timer Reset.

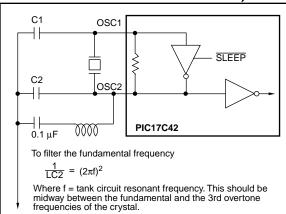

### FIGURE 14-3: CRYSTAL OPERATION, OVERTONE CRYSTALS (XT OSC CONFIGURATION)

### TABLE 14-2: CAPACITOR SELECTION FOR CERAMIC RESONATORS

| Oscillator<br>Type | Resonator<br>Frequency         | Capacitor Range<br>C1 = C2               |

|--------------------|--------------------------------|------------------------------------------|

| LF                 | 455 kHz<br>2.0 MHz             | 15 - 68 pF<br>10 - 33 pF                 |

| ХТ                 | 4.0 MHz<br>8.0 MHz<br>16.0 MHz | 22 - 68 pF<br>33 - 100 pF<br>33 - 100 pF |

Higher capacitance increases the stability of the oscillator but also increases the start-up time. These values are for design guidance only. Since each resonator has its own characteristics, the user should consult the resonator manufacturer for appropriate values of external components.

### **Resonators Used:**

| 455 kHz                                           | Panasonic EFO-A455K04B | ± 0.3% |  |  |

|---------------------------------------------------|------------------------|--------|--|--|

| 2.0 MHz                                           | Murata Erie CSA2.00MG  | ± 0.5% |  |  |

| 4.0 MHz                                           | Murata Erie CSA4.00MG  | ± 0.5% |  |  |

| 8.0 MHz                                           | Murata Erie CSA8.00MT  | ± 0.5% |  |  |

| 16.0 MHz                                          | Murata Erie CSA16.00MX | ± 0.5% |  |  |

| Resonators used did not have built-in capacitors. |                        |        |  |  |

## TABLE 14-3:CAPACITOR SELECTION<br/>FOR CRYSTAL OSCILLATOR

| Osc<br>Type | Freq                  | C1               | C2             |

|-------------|-----------------------|------------------|----------------|

| LF          | 32 kHz <sup>(1)</sup> | 100-150 pF       | 100-150 pF     |

|             | 1 MHz                 | 10-33 pF         | 10-33 pF       |

|             | 2 MHz                 | 10-33 pF         | 10-33 pF       |

| XT          | 2 MHz                 | 47-100 pF        | 47-100 pF      |

|             | 4 MHz                 | 15-68 pF         | 15-68 pF       |

|             | 8 MHz <sup>(2)</sup>  | 15-47 pF         | 15-47 pF       |

|             | 16 MHz                | TBD              | TBD            |

|             | 25 MHz                | 15-47 pF         | 15-47 pF       |

|             | 32 MHz <sup>(3)</sup> | <sub>0</sub> (3) | <sub>(3)</sub> |

Higher capacitance increases the stability of the oscillator but also increases the start-up time and the oscillator current. These values are for design guidance only. Rs may be required in XT mode to avoid overdriving the crystals with low drive level specification. Since each crystal has its own characteristics, the user should consult the crystal manufacturer for appropriate values for external components.

- Note 1: For VDD > 4.5V, C1 = C2  $\approx$  30 pF is recommended.

- Rs of 330Ω is required for a capacitor combination of 15/15 pF.

- 3: Only the capacitance of the board was present.

### **Crystals Used:**

| 32.768 kHz | Epson C-001R32.768K-A | ± 20 PPM     |

|------------|-----------------------|--------------|

| 1.0 MHz    | ECS-10-13-1           | $\pm$ 50 PPM |

| 2.0 MHz    | ECS-20-20-1           | $\pm$ 50 PPM |

| 4.0 MHz    | ECS-40-20-1           | ± 50 PPM     |

| 8.0 MHz    | ECS ECS-80-S-4        | ± 50 PPM     |

|            | ECS-80-18-1           |              |

| 16.0 MHz   | ECS-160-20-1          | TBD          |

| 25 MHz     | CTS CTS25M            | $\pm$ 50 PPM |

| 32 MHz     | CRYSTEK HF-2          | $\pm$ 50 PPM |

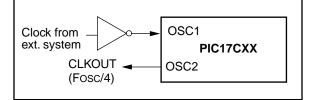

### 14.2.3 EXTERNAL CLOCK OSCILLATOR

In the EC oscillator mode, the OSC1 input can be driven by CMOS drivers. In this mode, the OSC1/CLKIN pin is hi-impedance and the OSC2/CLK-OUT pin is the CLKOUT output (4 Tosc).

### FIGURE 14-4: EXTERNAL CLOCK INPUT OPERATION (EC OSC CONFIGURATION)

# PIC17C4X

| CALL                                | Subroutir                                                                | ne Call                                                                                                                                                                                                                                                 |              | CLF                                                                                                                                                                                                           | RF                                       | Clear f              |        |                                                                                                                                                                      |                       |  |  |  |

|-------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--|--|--|

| Syntax:                             | [label] (                                                                | CALL k                                                                                                                                                                                                                                                  |              | Syn                                                                                                                                                                                                           | tax:                                     | [ <i>label</i> ] CL  | RF f,s |                                                                                                                                                                      |                       |  |  |  |

| Operands:                           | $0 \le k \le 40$                                                         | 95                                                                                                                                                                                                                                                      |              | Ope                                                                                                                                                                                                           | erands:                                  | $0 \le f \le 25$     | 5      |                                                                                                                                                                      |                       |  |  |  |

| Operation:                          | k<12:8> –                                                                | PC+ 1 $\rightarrow$ TOS, k $\rightarrow$ PC<12:0>,<br>k<12:8> $\rightarrow$ PCLATH<4:0>;<br>PC<15:13> $\rightarrow$ PCLATH<7:5>                                                                                                                         |              | $k < 12:8 \rightarrow PCLATH < 4:0 >;$                                                                                                                                                                        |                                          |                      |        | $\begin{array}{l} 00h \rightarrow f,  s \in  [0,1] \\ 00h \rightarrow dest \end{array}$                                                                              |                       |  |  |  |

| Status Affecte                      |                                                                          |                                                                                                                                                                                                                                                         | 1<7.02       | Stat                                                                                                                                                                                                          | tus Affected:                            | None                 |        |                                                                                                                                                                      |                       |  |  |  |

|                                     |                                                                          |                                                                                                                                                                                                                                                         |              | ר Enc                                                                                                                                                                                                         | oding:                                   | 0010                 | 100s   | ffff                                                                                                                                                                 | ffff                  |  |  |  |

| Encoding:<br>Description:           | Subroutine<br>return addr<br>the stack. T<br>PC bits<12<br>bits of the F | 111k         kkkk         kkkk         kkkk           Subroutine call within 8K page. First, return address (PC+1) is pushed onto the stack. The 13-bit value is loaded into PC bits<12:0>. Then the upper-eight bits of the PC are copied into PCLATH. |              | Subroutine call within 8K page. First,<br>return address (PC+1) is pushed onto<br>the stack. The 13-bit value is loaded into<br>PC bits<12:0>. Then the upper-eight<br>bits of the PC are copied into PCLATH. |                                          |                      |        | Clears the contents of the specified reg-<br>ister(s).<br>s = 0: Data memory location 'f' and<br>WREG are cleared.<br>s = 1: Data memory location 'f' is<br>cleared. |                       |  |  |  |

|                                     |                                                                          | wo-cycle instru                                                                                                                                                                                                                                         |              | Woi                                                                                                                                                                                                           | rds:                                     | 1                    |        |                                                                                                                                                                      |                       |  |  |  |

|                                     | See LCALL<br>space.                                                      | for calls outsid                                                                                                                                                                                                                                        | le 8K memory | Сус                                                                                                                                                                                                           | les:                                     | 1                    |        |                                                                                                                                                                      |                       |  |  |  |

| Words:                              | 1                                                                        |                                                                                                                                                                                                                                                         |              | QC                                                                                                                                                                                                            | cycle Activity:                          |                      |        |                                                                                                                                                                      |                       |  |  |  |

| Cycles:                             | 2                                                                        |                                                                                                                                                                                                                                                         |              |                                                                                                                                                                                                               | Q1                                       | Q2                   | Q      |                                                                                                                                                                      | Q4                    |  |  |  |

| Q Cycle Activ                       | ity:                                                                     |                                                                                                                                                                                                                                                         |              |                                                                                                                                                                                                               | Decode                                   | Read<br>register 'f' | Exec   |                                                                                                                                                                      | Write<br>register 'f' |  |  |  |

| Q1                                  | Q2                                                                       | Q3                                                                                                                                                                                                                                                      | Q4           |                                                                                                                                                                                                               |                                          |                      |        |                                                                                                                                                                      | and other             |  |  |  |

| Decode                              | e Read literal<br>'k'<7:0>                                               | Execute                                                                                                                                                                                                                                                 | NOP          |                                                                                                                                                                                                               |                                          |                      |        |                                                                                                                                                                      | specified<br>register |  |  |  |

| Forced N                            | OP NOP                                                                   | Execute                                                                                                                                                                                                                                                 | NOP          | <u>Exa</u>                                                                                                                                                                                                    | mple:                                    | CLRF                 | FLAC   | G_REG                                                                                                                                                                |                       |  |  |  |

| <u>Example</u> :<br>Before In<br>PC |                                                                          | CALL THE                                                                                                                                                                                                                                                | RE           |                                                                                                                                                                                                               | Before Instru<br>FLAG_R<br>After Instruc | EG = 0               | κ5Α    |                                                                                                                                                                      |                       |  |  |  |

| After Inst<br>PC                    |                                                                          | ERE)                                                                                                                                                                                                                                                    |              |                                                                                                                                                                                                               | FLAG_R                                   | EG = 0>              | (00    |                                                                                                                                                                      |                       |  |  |  |

PC = Address(THERE) TOS = Address(HERE + 1) MPASM allow full symbolic debugging from the Microchip Universal Emulator System (PICMASTER).

MPASM has the following features to assist in developing software for specific use applications.

- Provides translation of Assembler source code to object code for all Microchip microcontrollers.

- Macro assembly capability.

- Produces all the files (Object, Listing, Symbol, and special) required for symbolic debug with Microchip's emulator systems.

- Supports Hex (default), Decimal and Octal source and listing formats.

MPASM provides a rich directive language to support programming of the PIC16/17. Directives are helpful in making the development of your assemble source code shorter and more maintainable.

### 16.11 Software Simulator (MPLAB-SIM)

The MPLAB-SIM Software Simulator allows code development in a PC host environment. It allows the user to simulate the PIC16/17 series microcontrollers on an instruction level. On any given instruction, the user may examine or modify any of the data areas or provide external stimulus to any of the pins. The input/ output radix can be set by the user and the execution can be performed in; single step, execute until break, or in a trace mode.

MPLAB-SIM fully supports symbolic debugging using MPLAB-C and MPASM. The Software Simulator offers the low cost flexibility to develop and debug code outside of the laboratory environment making it an excellent multi-project software development tool.

### 16.12 C Compiler (MPLAB-C)

The MPLAB-C Code Development System is a complete 'C' compiler and integrated development environment for Microchip's PIC16/17 family of micro-controllers. The compiler provides powerful integration capabilities and ease of use not found with other compilers.

For easier source level debugging, the compiler provides symbol information that is compatible with the MPLAB IDE memory display (PICMASTER emulator software versions 1.13 and later).

### 16.13 <u>Fuzzy Logic Development System</u> (*fuzzy*TECH-MP)

*fuzzy*TECH-MP fuzzy logic development tool is available in two versions - a low cost introductory version, MP Explorer, for designers to gain a comprehensive working knowledge of fuzzy logic system design; and a full-featured version, *fuzzy*TECH-MP, edition for implementing more complex systems.

Both versions include Microchip's *fuzzy*LAB<sup>™</sup> demonstration board for hands-on experience with fuzzy logic systems implementation.

### 16.14 <u>MP-DriveWay™ – Application Code</u> <u>Generator</u>

MP-DriveWay is an easy-to-use Windows-based Application Code Generator. With MP-DriveWay you can visually configure all the peripherals in a PIC16/17 device and, with a click of the mouse, generate all the initialization and many functional code modules in C language. The output is fully compatible with Microchip's MPLAB-C C compiler. The code produced is highly modular and allows easy integration of your own code. MP-DriveWay is intelligent enough to maintain your code through subsequent code generation.

### 16.15 <u>SEEVAL® Evaluation and</u> <u>Programming System</u>

The SEEVAL SEEPROM Designer's Kit supports all Microchip 2-wire and 3-wire Serial EEPROMs. The kit includes everything necessary to read, write, erase or program special features of any Microchip SEEPROM product including Smart Serials<sup>™</sup> and secure serials. The Total Endurance<sup>™</sup> Disk is included to aid in tradeoff analysis and reliability calculations. The total kit can significantly reduce time-to-market and result in an optimized system.

### 16.16 <u>TrueGauge<sup>®</sup> Intelligent Battery</u> <u>Management</u>

The TrueGauge development tool supports system development with the MTA11200B TrueGauge Intelligent Battery Management IC. System design verification can be accomplished before hardware prototypes are built. User interface is graphically-oriented and measured data can be saved in a file for exporting to Microsoft Excel.

### 16.17 <u>KEELOQ<sup>®</sup> Evaluation and</u> <u>Programming Tools</u>

KEELOQ evaluation and programming tools support Microchips HCS Secure Data Products. The HCS evaluation kit includes an LCD display to show changing codes, a decoder to decode transmissions, and a programming interface to program test transmitters.

### Applicable Devices 42 R42 42A 43 R43 44

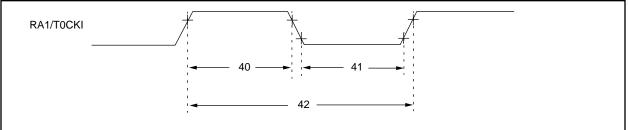

### FIGURE 17-5: TIMER0 CLOCK TIMINGS

### TABLE 17-5: TIMER0 CLOCK REQUIREMENTS

| Parameter<br>No. | Sum  | Characteristic         |                | Min               | Tunt | Мах   | Unito | Conditions         |

|------------------|------|------------------------|----------------|-------------------|------|-------|-------|--------------------|

| NO.              | Sym  | Characteristic         |                | IVIIII            | Typ† | IVIAX | Units | Conditions         |

| 40               | Tt0H | T0CKI High Pulse Width | No Prescaler   | 0.5TCY + 20 §     | _    | _     | ns    |                    |

|                  |      |                        | With Prescaler | 10*               | —    | —     | ns    |                    |

| 41               | Tt0L | T0CKI Low Pulse Width  | No Prescaler   | 0.5Tcy + 20 §     | —    | —     | ns    |                    |

|                  |      |                        | With Prescaler | 10*               | —    | —     | ns    |                    |

| 42               | Tt0P | T0CKI Period           | •              | <u>Tcy + 40</u> § | —    | —     | ns    | N = prescale value |

|                  |      |                        |                | N                 |      |       |       | (1, 2, 4,, 256)    |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

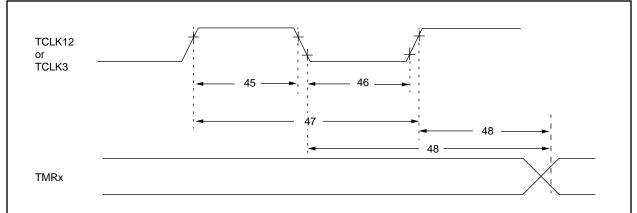

### FIGURE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK TIMINGS

### TABLE 17-6: TIMER1, TIMER2, AND TIMER3 CLOCK REQUIREMENTS

| Parameter |           |                                                               |                        | Тур |          |       |                                    |

|-----------|-----------|---------------------------------------------------------------|------------------------|-----|----------|-------|------------------------------------|

| No.       | Sym       | Characteristic                                                | Min                    | †   | Max      | Units | Conditions                         |

| 45        | Tt123H    | TCLK12 and TCLK3 high time                                    | 0.5 TCY + 20 §         |     | _        | ns    |                                    |

| 46        | Tt123L    | TCLK12 and TCLK3 low time                                     | 0.5 TCY + 20 §         |     |          | ns    |                                    |

| 47        | Tt123P    | TCLK12 and TCLK3 input period                                 | <u>Tcy + 40</u> §<br>N |     |          | ns    | N = prescale value<br>(1, 2, 4, 8) |

| 48        | TckE2tmrl | Delay from selected External Clock Edge to<br>Timer increment | 2Tosc §                |     | 6 Tosc § | _     |                                    |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

§ This specification ensured by design.

# PIC17C4X

Applicable Devices 42 R42 42A 43 R43 44

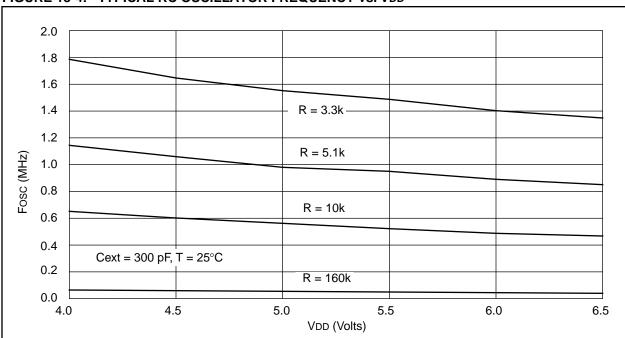

### FIGURE 18-4: TYPICAL RC OSCILLATOR FREQUENCY vs. VDD

### TABLE 18-2: RC OSCILLATOR FREQUENCIES

| Cext   | Rext | Average<br>Fosc @ 5V, 25°C |       |  |

|--------|------|----------------------------|-------|--|

| 22 pF  | 10k  | 3.33 MHz                   | ± 12% |  |

|        | 100k | 353 kHz                    | ± 13% |  |

| 100 pF | 3.3k | 3.54 MHz                   | ± 10% |  |

|        | 5.1k | 2.43 MHz                   | ± 14% |  |

|        | 10k  | 1.30 MHz                   | ± 17% |  |

|        | 100k | 129 kHz                    | ± 10% |  |

| 300 pF | 3.3k | 1.54 MHz                   | ± 14% |  |

|        | 5.1k | 980 kHz                    | ± 12% |  |

|        | 10k  | 564 kHz                    | ± 16% |  |

|        | 160k | 35 kHz                     | ± 18% |  |

| Applicable Devices | 42 | R42 | 42A | 43 | R43 | 44 |

|--------------------|----|-----|-----|----|-----|----|

|                    |    |     |     |    |     |    |

| DC CHARACTERISTICS |       |                                                       | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature |           |         |                       |                                                          |  |  |

|--------------------|-------|-------------------------------------------------------|----------------------------------------------------------------------------------|-----------|---------|-----------------------|----------------------------------------------------------|--|--|

|                    |       |                                                       | _                                                                                |           |         |                       | ≤ +40°C                                                  |  |  |

|                    |       | Operating v                                           | oltage VD                                                                        | D range a | as desc | ribed in Section 19.1 |                                                          |  |  |

| Parameter          |       |                                                       |                                                                                  |           |         |                       |                                                          |  |  |

| No.                | Sym   | Characteristic                                        | Min                                                                              | Typ†      | Max     | Units                 | Conditions                                               |  |  |

|                    |       | Internal Program Memory<br>Programming Specs (Note 4) |                                                                                  |           |         |                       |                                                          |  |  |

| D110               | VPP   | Voltage on MCLR/VPP pin                               | 12.75                                                                            | _         | 13.25   | V                     | Note 5                                                   |  |  |

| D111               | Vddp  | Supply voltage during                                 | 4.75                                                                             | 5.0       | 5.25    | V                     |                                                          |  |  |

| D112               | IPP   | Current into MCLR/VPP pin                             | _                                                                                | 25 ‡      | 50 ‡    | mA                    |                                                          |  |  |

| D113               | Iddp  | Supply current during programming                     | -                                                                                | -         | 30 ‡    | mA                    |                                                          |  |  |

| D114               | TPROG | Programming pulse width                               | 10                                                                               | 100       | 1000    | μs                    | Terminated via internal/<br>external interrupt or a rese |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

t These parameters are for design guidance only and are not tested, nor characterized.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended that the PIC17CXX devices be driven with external clock in RC mode.

The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

4: These specifications are for the programming of the on-chip program memory EPROM through the use of the table write instructions. The complete programming specifications can be found in: PIC17CXX Programming Specifications (Literature number DS30139).

5: The MCLR/VPP pin may be kept in this range at times other than programming, but is not recommended.

6: For TTL buffers, the better of the two specifications may be used.

Note: When using the Table Write for internal programming, the device temperature must be less than 40°C.

| Asynchronous Master Transmission90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Asynchronous Reception92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Back to Back Asynchronous Master Transmission 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Interrupt (INT, TMR0 Pins)26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| PIC17C42 Capture 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| PIC17C42 CLKOUT and I/O 156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PIC17C42 Memory Interface Read 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PIC17C42 Memory Interface Write 161                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| PIC17C42 PWM Timing159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PIC17C42 RESET, Watchdog Timer, Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Start-up Timer and Power-up Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PIC17C42 Timer0 Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PIC17C42 Timer1, Timer2 and Timer3 Clock 158                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |