# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                       |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB, USB OTG                |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT      |

| Number of I/O              | 36                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                       |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 16K × 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                           |

| Data Converters            | A/D - 16bit; D/A - 12bit                                               |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-QFN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl26z128vft4r |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Symbol             | Description                                                   | Min. | Тур. | Max. | Unit | Notes |

|--------------------|---------------------------------------------------------------|------|------|------|------|-------|

| $V_{LVDH}$         | Falling low-voltage detect threshold — high range (LVDV = 01) | 2.48 | 2.56 | 2.64 | V    | _     |

|                    | Low-voltage warning thresholds — high range                   |      |      |      |      | 1     |

| $V_{LVW1H}$        | • Level 1 falling (LVWV = 00)                                 | 2.62 | 2.70 | 2.78 | v    |       |

| $V_{LVW2H}$        | <ul> <li>Level 2 falling (LVWV = 01)</li> </ul>               | 2.72 | 2.80 | 2.88 | v    |       |

| V <sub>LVW3H</sub> | <ul> <li>Level 3 falling (LVWV = 10)</li> </ul>               | 2.82 | 2.90 | 2.98 | v    |       |

| $V_{\rm LVW4H}$    | • Level 4 falling (LVWV = 11)                                 | 2.92 | 3.00 | 3.08 | v    |       |

| V <sub>HYSH</sub>  | Low-voltage inhibit reset/recover hysteresis — high range     | _    | ±60  | _    | mV   | _     |

| V <sub>LVDL</sub>  | Falling low-voltage detect threshold — low range (LVDV=00)    | 1.54 | 1.60 | 1.66 | V    | -     |

|                    | Low-voltage warning thresholds — low range                    |      |      |      |      | 1     |

| $V_{LVW1L}$        | • Level 1 falling (LVWV = 00)                                 | 1.74 | 1.80 | 1.86 | v    |       |

| $V_{LVW2L}$        | <ul> <li>Level 2 falling (LVWV = 01)</li> </ul>               | 1.84 | 1.90 | 1.96 | v    |       |

| $V_{LVW3L}$        | <ul> <li>Level 3 falling (LVWV = 10)</li> </ul>               | 1.94 | 2.00 | 2.06 | v    |       |

| $V_{LVW4L}$        | • Level 4 falling (LVWV = 11)                                 | 2.04 | 2.10 | 2.16 | v    |       |

| V <sub>HYSL</sub>  | Low-voltage inhibit reset/recover hysteresis — low range      | —    | ±40  | -    | mV   | -     |

| V <sub>BG</sub>    | Bandgap voltage reference                                     | 0.97 | 1.00 | 1.03 | V    | -     |

| t <sub>LPO</sub>   | Internal low power oscillator period — factory trimmed        | 900  | 1000 | 1100 | μs   | -     |

| Table 6 | V <sub>DD</sub> supply LVD and POR | operating require | ments (continued) |

|---------|------------------------------------|-------------------|-------------------|

|         | VDD Supply LVD and I On V          | operating require | mente (continueu) |

1. Rising thresholds are falling threshold + hysteresis voltage

### 2.2.3 Voltage and current operating behaviors Table 7. Voltage and current operating behaviors

| Symbol           | Description                                                                                            | Min.                  | Max. | Unit | Notes |

|------------------|--------------------------------------------------------------------------------------------------------|-----------------------|------|------|-------|

| V <sub>OH</sub>  | Output high voltage — Normal drive pad (except RESET_b)                                                |                       |      |      | 1, 2  |

|                  |                                                                                                        | V <sub>DD</sub> – 0.5 | —    | V    |       |

|                  | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}, \text{ I}_{\text{OH}} = -5 \text{ mA}$    | V <sub>DD</sub> – 0.5 | —    | V    |       |

|                  | • $1.71 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}, \text{ I}_{\text{OH}} = -2.5 \text{ mA}$ |                       |      |      |       |

| V <sub>OH</sub>  | Output high voltage — High drive pad (except                                                           |                       |      |      | 1, 2  |

|                  | RESET_b)                                                                                               | V <sub>DD</sub> – 0.5 | —    | V    |       |

|                  | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V, I <sub>OH</sub> = -20 mA                                  | V <sub>DD</sub> – 0.5 | _    | v    |       |

|                  | • 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 2.7 V, I <sub>OH</sub> = -10 mA                                 |                       |      |      |       |

| I <sub>ОНТ</sub> | Output high current total for all ports                                                                | -                     | 100  | mA   |       |

Table continues on the next page...

| Symbol | Description                     | Min. | Тур. | Max. | Unit | Notes |

|--------|---------------------------------|------|------|------|------|-------|

|        | <ul> <li>VLLS0 → RUN</li> </ul> |      |      |      |      |       |

|        |                                 | —    | 106  | 120  | μs   |       |

|        | <ul> <li>VLLS1 → RUN</li> </ul> |      |      |      |      |       |

|        |                                 | —    | 105  | 117  | μs   |       |

|        | <ul> <li>VLLS3 → RUN</li> </ul> |      |      |      |      |       |

|        |                                 | —    | 47   | 54   | μs   |       |

|        | • LLS → RUN                     |      |      |      |      |       |

|        |                                 | —    | 4.5  | 5.0  | μs   |       |

|        | <ul> <li>VLPS → RUN</li> </ul>  |      |      |      |      |       |

|        |                                 | —    | 4.5  | 5.0  | μs   |       |

|        | • STOP → RUN                    |      |      |      |      |       |

|        |                                 |      | 4.5  | 5.0  | μs   |       |

Table 8. Power mode transition operating behaviors (continued)

1. Normal boot (FTFA\_FOPT[LPBOOT]=11).

### 2.2.5 Power consumption operating behaviors

The maximum values stated in the following table represent characterized results equivalent to the mean plus three times the standard deviation (mean + 3 sigma).

| Symbol                | Description                                                                                                                                                                                                  | Temp. | Тур. | Max      | Unit | Note |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|----------|------|------|

| I <sub>DDA</sub>      | Analog supply current                                                                                                                                                                                        | —     | _    | See note | mA   | 1    |

| IDD_RUNCO_CM          | Run mode current in compute<br>operation - 48 MHz core / 24 MHz<br>flash/ bus disabled, LPTMR running<br>using 4 MHz internal reference clock,<br>CoreMark® benchmark code<br>executing from flash, at 3.0 V | _     | 6.1  | _        | mA   | 2    |

| I <sub>DD_RUNCO</sub> | Run mode current in compute<br>operation - 48 MHz core / 24 MHz<br>flash / bus clock disabled, code of<br>while(1) loop executing from flash, at<br>3.0 V                                                    | -     | 3.8  | 4.4      | mA   | 3    |

| I <sub>DD_RUN</sub>   | Run mode current - 48 MHz core / 24<br>MHz bus and flash, all peripheral<br>clocks disabled, code executing from<br>flash, at 3.0 V                                                                          | _     | 4.6  | 5.2      | mA   | 3    |

Table 9. Power consumption operating behaviors

Table continues on the next page...

9

| Symbol                | Description                           | Temp.     | Тур.  | Max   | Unit | Note |

|-----------------------|---------------------------------------|-----------|-------|-------|------|------|

|                       |                                       | at 85 °C  | 21.13 | 39.13 | μA   |      |

|                       |                                       | at 105 °C | 45.85 | 85.45 | μA   |      |

| I <sub>DD_LLS</sub>   | Low leakage stop mode current at 3.0  | at 25 °C  | 1.98  | 2.65  | μA   | —    |

|                       | V                                     | at 50 °C  | 3.13  | 4.35  | μA   |      |

|                       |                                       | at 70 °C  | 5.65  | 8.34  | μA   |      |

|                       |                                       | at 85 °C  | 9.58  | 14.29 | μA   | -    |

|                       |                                       | at 105 °C | 20.52 | 31.74 | μA   |      |

| I <sub>DD_VLLS3</sub> | Very low-leakage stop mode 3 current  | at 25 °C  | 1.46  | 2.06  | μA   | —    |

|                       | at 3.0 V                              | at 50 °C  | 2.29  | 3.22  | μA   | -    |

|                       |                                       | at 70 °C  | 4.10  | 5.90  | μA   |      |

|                       |                                       | at 85 °C  | 6.93  | 10.02 | μA   |      |

|                       |                                       | at 105 °C | 14.80 | 22.12 | μA   | -    |

| I <sub>DD_VLLS1</sub> | Very low-leakage stop mode 1 current  | at 25 °C  | 0.71  | 1.20  | μA   | —    |

|                       | at 3.0V                               | at 50 °C  | 1.10  | 1.71  | μA   | -    |

|                       |                                       | at 70 °C  | 2.09  | 3.03  | μA   | -    |

|                       |                                       | at 85 °C  | 3.80  | 5.42  | μA   | -    |

|                       |                                       | at 105 °C | 8.84  | 12.98 | μA   |      |

| IDD_VLLS0             | Very low-leakage stop mode 0 current  | at 25 °C  | 0.40  | 0.88  | μA   | _    |

|                       | (SMC_STOPCTRL[PORPO] = 0) at<br>3.0 V | at 50 °C  | 0.80  | 1.40  | μA   | -    |

|                       | 5.0 V                                 | at 70 °C  | 1.79  | 2.72  | μA   |      |

|                       |                                       | at 85 °C  | 3.50  | 5.10  | μA   |      |

|                       |                                       | at 105 °C | 8.54  | 12.63 | μA   |      |

| IDD_VLLS0             | Very low-leakage stop mode 0 current  | at 25 °C  | 0.23  | 0.69  | μA   | 7    |

|                       | (SMC_STOPCTRL[PORPO] = 1) at<br>3.0 V | at 50 °C  | 0.61  | 1.19  | μA   | 1    |

|                       | 0.0 V                                 | at 70 °C  | 1.59  | 2.50  | μA   | 1    |

|                       |                                       | at 85 °C  | 3.30  | 4.89  | μA   |      |

|                       |                                       | at 105 °C | 8.36  | 12.41 | μA   | 1    |

### Table 9. Power consumption operating behaviors (continued)

1. The analog supply current is the sum of the active or disabled current for each of the analog modules on the device. See each module's specification for its supply current.

2. MCG configured for PEE mode. CoreMark benchmark compiled using IAR 6.40 with optimization level high, optimized for balanced.

- 3. MCG configured for FEI mode.

- 4. Incremental current consumption from peripheral activity is not included.

- 5. MCG configured for BLPI mode. CoreMark benchmark compiled using IAR 6.40 with optimization level high, optimized for balanced.

- 6. MCG configured for BLPI mode.

- 7. No brownout.

| Symbol                     | Description                                                                                                                                                                                       |                                                                                                            |     | ٦   | empera | ature (° | C)  |     | Unit |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|-----|--------|----------|-----|-----|------|

|                            |                                                                                                                                                                                                   |                                                                                                            | -40 | 25  | 50     | 70       | 85  | 105 |      |

| I <sub>IREFSTEN4MHz</sub>  | 4 MHz internal reference clock<br>Measured by entering STOP o<br>with 4 MHz IRC enabled.                                                                                                          |                                                                                                            | 56  | 56  | 56     | 56       | 56  | 56  | μA   |

| I <sub>IREFSTEN32KHz</sub> |                                                                                                                                                                                                   |                                                                                                            |     | 52  | 52     | 52       | 52  | 52  | μA   |

| I <sub>EREFSTEN4MHz</sub>  |                                                                                                                                                                                                   | External 4 MHz crystal clock adder.<br>Measured by entering STOP or VLPS mode<br>with the crystal enabled. |     | 228 | 237    | 245      | 251 | 258 | μA   |

| I <sub>EREFSTEN32KHz</sub> |                                                                                                                                                                                                   |                                                                                                            | 440 | 490 | 540    | 560      | 570 | 580 | nA   |

|                            | adder by means of the VLLS<br>OSC0_CR[EREFSTEN and EREFSTEN] bits. Measured LLS                                                                                                                   |                                                                                                            | 440 | 490 | 540    | 560      | 570 | 580 |      |

|                            |                                                                                                                                                                                                   |                                                                                                            | 490 | 490 | 540    | 560      | 570 | 680 |      |

|                            | by entering all modes with the                                                                                                                                                                    | VLPS                                                                                                       | 510 | 560 | 560    | 560      | 610 | 680 |      |

|                            | crystal enabled.                                                                                                                                                                                  | STOP                                                                                                       | 510 | 560 | 560    | 560      | 610 | 680 |      |

| I <sub>CMP</sub>           | CMP peripheral adder measured by placing<br>the device in VLLS1 mode with CMP enabled<br>using the 6-bit DAC and a single external<br>input for compare. Includes 6-bit DAC power<br>consumption. |                                                                                                            |     | 22  | 22     | 22       | 22  | 22  | μA   |

| I <sub>RTC</sub>           | RTC peripheral adder measure<br>the device in VLLS1 mode with<br>kHz crystal enabled by means<br>RTC_CR[OSCE] bit and the R<br>for 1 minute. Includes ERCLK3<br>external crystal) power consum    | of the<br>TC ALARM set<br>32K (32 kHz                                                                      | 432 | 357 | 388    | 475      | 532 | 810 | nA   |

| I <sub>UART</sub>          | UART peripheral adder<br>measured by placing the<br>device in STOP or VLPS<br>mode with selected clock<br>source waiting for RX data at                                                           | MCGIRCLK<br>(4 MHz<br>internal<br>reference<br>clock)                                                      | 66  | 66  | 66     | 66       | 66  | 66  | μA   |

|                            | 115200 baud rate. Includes<br>selected clock source power<br>consumption.                                                                                                                         | 115200 baud rate. Includes<br>selected clock source power (4 MHz                                           |     | 237 | 246    | 254      | 260 | 268 |      |

| I <sub>TPM</sub>           | TPM peripheral adderMCGIRCLKmeasured by placing the(4 MHzdevice in STOP or VLPSinternalmode with selected clockreferencesource configured for outputclock)                                        |                                                                                                            | 86  | 86  | 86     | 86       | 86  | 86  | μA   |

|                            | compare generating 100 Hz<br>clock signal. No load is<br>placed on the I/O generating<br>the clock signal. Includes<br>selected clock source and I/O<br>switching currents.                       | OSCERCLK<br>(4 MHz<br>external<br>crystal)                                                                 | 235 | 256 | 265    | 274      | 280 | 287 |      |

### Table 10. Low power mode peripheral adders — typical value

Table continues on the next page...

| Symbol          | bol Description Temperature (°C)                                                                                                                                                                                   |     |     |     |     |     | Unit |    |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|------|----|

|                 |                                                                                                                                                                                                                    | -40 | 25  | 50  | 70  | 85  | 105  |    |

| I <sub>BG</sub> | Bandgap adder when BGEN bit is set and device is placed in VLPx, LLS, or VLLSx mode.                                                                                                                               | 45  | 45  | 45  | 45  | 45  | 45   | μA |

| IADC            | ADC peripheral adder combining the measured values at $V_{DD}$ and $V_{DDA}$ by placing the device in STOP or VLPS mode. ADC is configured for low power mode using the internal clock and continuous conversions. | 366 | 366 | 366 | 366 | 366 | 366  | μA |

Table 10.

Low power mode peripheral adders — typical value (continued)

## 2.2.5.1 Diagram: Typical IDD\_RUN operating behavior

The following data was measured under these conditions:

- MCG in FBE for run mode, and BLPE for VLPR mode

- USB regulator disabled

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFA

application code. The reported emission level is the value of the maximum measured emission, rounded up to the next whole number, from among the measured orientations in each frequency range.

- 2.  $V_{DD} = 3.3 \text{ V}$ ,  $T_A = 25 \text{ °C}$ ,  $f_{OSC} = 8 \text{ MHz}$  (crystal),  $f_{SYS} = 48 \text{ MHz}$ ,  $f_{BUS} = 24 \text{ MHz}$

- 3. Specified according to Annex D of IEC Standard 61967-2, Measurement of Radiated Emissions TEM Cell and Wideband TEM Cell Method

## 2.2.7 Designing with radiated emissions in mind

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions:

- 1. Go to www.freescale.com.

- 2. Perform a keyword search for "EMC design."

## 2.2.8 Capacitance attributes

### Table 12. Capacitance attributes

| Symbol          | Description       | Min. | Max. | Unit |

|-----------------|-------------------|------|------|------|

| C <sub>IN</sub> | Input capacitance | —    | 7    | pF   |

# 2.3 Switching specifications

## 2.3.1 Device clock specifications

Table 13. Device clock specifications

| Symbol               | Description                                            | Min. | Max. | Unit |

|----------------------|--------------------------------------------------------|------|------|------|

|                      | Normal run mode                                        | •    |      |      |

| f <sub>SYS</sub>     | System and core clock                                  | _    | 48   | MHz  |

| f <sub>BUS</sub>     | Bus clock                                              | _    | 24   | MHz  |

| f <sub>FLASH</sub>   | Flash clock                                            | —    | 24   | MHz  |

| f <sub>SYS_USB</sub> | System and core clock when Full Speed USB in operation | 20   | _    | MHz  |

| f <sub>LPTMR</sub>   | LPTMR clock                                            | —    | 24   | MHz  |

|                      | VLPR and VLPS modes <sup>1</sup>                       |      |      |      |

| f <sub>SYS</sub>     | System and core clock                                  | —    | 4    | MHz  |

| f <sub>BUS</sub>     | Bus clock                                              | _    | 1    | MHz  |

| f <sub>FLASH</sub>   | Flash clock                                            | -    | 1    | MHz  |

| f <sub>LPTMR</sub>   | LPTMR clock <sup>2</sup>                               | —    | 24   | MHz  |

Table continues on the next page...

### 2.4.2 Thermal attributes Table 16. Thermal attributes

| Board type        | Symbol            | Description                                                                                              | 64 LQFP | 48 QFN | 32 QFN | Unit | Notes |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|---------|--------|--------|------|-------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 71      | 83     | 98     | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 53      | 30     | 34     | °C/W |       |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 59      | 68     | 82     | °C/W |       |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 46      | 24     | 28     | °C/W |       |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 35      | 12     | 13     | °C/W | 2     |

| _                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 21      | 2.3    | 2.3    | °C/W | 3     |

| _                 | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package<br>top outside center (natural<br>convection) | 6       | 5      | 8      | °C/W | 4     |

- 1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air).

- 2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

# **3** Peripheral operating requirements and behaviors

# 3.1 Core modules

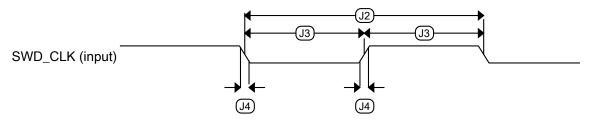

## 3.1.1 SWD electricals

| Symbol     | Description                                     | Min. | Max. | Unit |

|------------|-------------------------------------------------|------|------|------|

|            | Operating voltage                               | 1.71 | 3.6  | V    |

| J1         | SWD_CLK frequency of operation                  |      |      |      |

|            | Serial wire debug                               | 0    | 25   | MHz  |

| J2         | SWD_CLK cycle period                            | 1/J1 | _    | ns   |

| JЗ         | SWD_CLK clock pulse width                       |      |      |      |

|            | Serial wire debug                               | 20   | _    | ns   |

| J4         | SWD_CLK rise and fall times                     | _    | 3    | ns   |

| <b>J</b> 9 | SWD_DIO input data setup time to SWD_CLK rise   | 10   | _    | ns   |

| J10        | SWD_DIO input data hold time after SWD_CLK rise | 0    | —    | ns   |

| J11        | SWD_CLK high to SWD_DIO data valid              | —    | 32   | ns   |

| J12        | SWD_CLK high to SWD_DIO high-Z                  | 5    | _    | ns   |

Table 17. SWD full voltage range electricals

Figure 4. Serial wire clock input timing

| Symbol                       | Description                                                                                            | Min. | Тур.            | Max. | Unit | Notes |

|------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------------|------|------|-------|

|                              | • 24 MHz                                                                                               |      | 1.5             |      | mA   |       |

|                              | • 32 MHz                                                                                               |      |                 |      |      |       |

| I <sub>DDOSC</sub>           | Supply current — high gain mode (HGO=1)                                                                |      |                 |      |      | 1     |

|                              | • 32 kHz                                                                                               | —    | 25              | _    | μA   |       |

|                              | • 4 MHz                                                                                                | —    | 400             | _    | μA   |       |

|                              | • 8 MHz (RANGE=01)                                                                                     | —    | 500             | _    | μA   |       |

|                              | • 16 MHz                                                                                               | —    | 2.5             | _    | mA   |       |

|                              | • 24 MHz                                                                                               | —    | 3               | _    | mA   |       |

|                              | • 32 MHz                                                                                               | —    | 4               | _    | mA   |       |

| C <sub>x</sub>               | EXTAL load capacitance                                                                                 |      |                 |      |      | 2, 3  |

| Cy                           | XTAL load capacitance                                                                                  | _    | —               | —    |      | 2, 3  |

| R <sub>F</sub>               | Feedback resistor — low-frequency, low-power mode (HGO=0)                                              | _    |                 |      | MΩ   | 2, 4  |

|                              | Feedback resistor — low-frequency, high-gain mode (HGO=1)                                              | —    | 10              | _    | MΩ   |       |

|                              | Feedback resistor — high-frequency, low-power mode (HGO=0)                                             | _    |                 |      | MΩ   |       |

|                              | Feedback resistor — high-frequency, high-gain mode (HGO=1)                                             | _    | 1               | _    | MΩ   |       |

| R <sub>S</sub>               | Series resistor — low-frequency, low-power<br>mode (HGO=0)                                             | —    | _               | _    | kΩ   |       |

|                              | Series resistor — low-frequency, high-gain<br>mode (HGO=1)                                             | —    | 200             | _    | kΩ   |       |

|                              | Series resistor — high-frequency, low-power<br>mode (HGO=0)                                            | _    | _               | _    | kΩ   |       |

|                              | Series resistor — high-frequency, high-gain<br>mode (HGO=1)                                            |      |                 |      |      |       |

|                              |                                                                                                        | _    | 0               | _    | kΩ   |       |

| V <sub>pp</sub> <sup>5</sup> | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, low-power mode<br>(HGO=0)  | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — low-frequency, high-gain mode<br>(HGO=1)  | _    | V <sub>DD</sub> | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, low-power mode<br>(HGO=0) | _    | 0.6             | _    | V    |       |

|                              | Peak-to-peak amplitude of oscillation (oscillator<br>mode) — high-frequency, high-gain mode<br>(HGO=1) | _    | V <sub>DD</sub> | _    | V    |       |

### Table 19. Oscillator DC electrical specifications (continued)

V<sub>DD</sub>=3.3 V, Temperature =25 °C

See crystal or resonator manufacturer's recommendation

|                     |                                 | a                                               |      |                        |                 |                  |                                                                              |

|---------------------|---------------------------------|-------------------------------------------------|------|------------------------|-----------------|------------------|------------------------------------------------------------------------------|

| Symbol              | Description                     | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup>      | Max.            | Unit             | Notes                                                                        |

| INL                 | Integral non-<br>linearity      | 12-bit modes                                    | _    | ±1.0                   | –2.7 to<br>+1.9 | LSB <sup>4</sup> | 5                                                                            |

|                     |                                 | <ul> <li>&lt;12-bit modes</li> </ul>            | _    | ±0.5                   | –0.7 to<br>+0.5 |                  |                                                                              |

| E <sub>FS</sub>     | Full-scale error                | 12-bit modes                                    | _    | -4                     | -5.4            | LSB <sup>4</sup> | V <sub>ADIN</sub> =                                                          |

|                     |                                 | <li>&lt;12-bit modes</li>                       | _    | -1.4                   | -1.8            |                  | V <sub>DDA</sub> <sup>5</sup>                                                |

| EQ                  | Quantization                    | 16-bit modes                                    | _    | -1 to 0                | —               | LSB <sup>4</sup> |                                                                              |

|                     | error                           | • ≤13-bit modes                                 | —    | -                      | ±0.5            |                  |                                                                              |

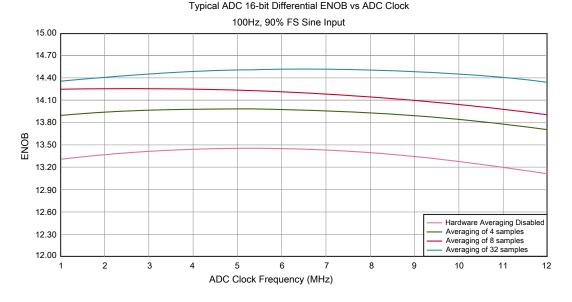

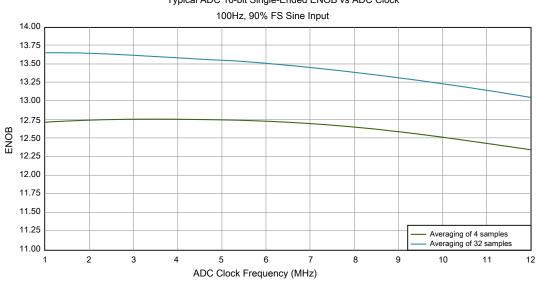

| ENOB                | Effective number                | 16-bit differential mode                        | 12.8 | 14.5                   |                 | bits             | 6                                                                            |

|                     | of bits                         | • Avg = 32                                      | 11.9 | 13.8                   | _               | bits             |                                                                              |

|                     |                                 | • Avg = 4                                       |      |                        |                 |                  |                                                                              |

|                     |                                 | 10 bit single and shows de                      | 12.2 | 13.9                   | _               | bits             |                                                                              |

|                     |                                 | 16-bit single-ended mode                        | 11.4 | 13.1                   | _               | bits             |                                                                              |

|                     |                                 | • Avg = 32                                      |      |                        |                 |                  |                                                                              |

|                     |                                 | • Avg = 4                                       |      |                        |                 |                  |                                                                              |

| SINAD               | Signal-to-noise plus distortion | See ENOB                                        | 6.02 | 2 × ENOB +             | 1.76            | dB               |                                                                              |

| THD                 | Total harmonic                  | 16-bit differential mode                        | _    | -94                    | _               | dB               | 7                                                                            |

|                     | distortion                      | • Avg = 32                                      |      |                        |                 |                  |                                                                              |

|                     |                                 |                                                 | _    | -85                    | _               | dB               |                                                                              |

|                     |                                 | 16-bit single-ended mode                        |      |                        |                 |                  |                                                                              |

|                     |                                 | • Avg = 32                                      |      |                        |                 |                  |                                                                              |

| SFDR                | Spurious free                   | 16-bit differential mode                        | 82   | 95                     | _               | dB               | 7                                                                            |

|                     | dynamic range                   | • Avg = 32                                      | 70   |                        |                 |                  |                                                                              |

|                     |                                 | 16 bit single anded made                        | 78   | 90                     | _               | dB               |                                                                              |

|                     |                                 | 16-bit single-ended mode                        |      |                        |                 |                  |                                                                              |

|                     |                                 | • Avg = 32                                      |      |                        |                 |                  |                                                                              |

| EIL                 | Input leakage<br>error          |                                                 |      | $I_{In} \times R_{AS}$ |                 | mV               | I <sub>In</sub> =<br>leakage<br>current                                      |

|                     |                                 |                                                 |      |                        |                 |                  | (refer to<br>the MCU's<br>voltage<br>and<br>current<br>operating<br>ratings) |

|                     | Temp sensor<br>slope            | Across the full temperature range of the device | 1.55 | 1.62                   | 1.69            | mV/°C            | 8                                                                            |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage          | 25 °C                                           | 706  | 716                    | 726             | mV               | 8                                                                            |

Table 26. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

### Peripheral operating requirements and behaviors

- 1. All accuracy numbers assume the ADC is calibrated with V<sub>REFH</sub> = V<sub>DDA</sub>

- 2. Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- 3. The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

- 4. 1 LSB =  $(V_{\text{REFH}} V_{\text{REFL}})/2^{N}$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Typical ADC 16-bit Single-Ended ENOB vs ADC Clock

## NOTE

The MCGPLLCLK meets the USB jitter specifications for certification with the use of an external clock/crystal for both Device and Host modes.

The MCGFLLCLK does not meet the USB jitter specifications for certification.

### 3.8.2 USB VREG electrical specifications Table 30. USB VREG electrical specifications

| Symbol                                         | Description                                                                                                                                           | Min.     | Typ. <sup>1</sup> | Max.       | Unit     | Notes |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------------|------------|----------|-------|

| VREGIN                                         | Input supply voltage                                                                                                                                  | 2.7      | —                 | 5.5        | V        |       |

| I <sub>DDon</sub>                              | Quiescent current — Run mode, load current<br>equal zero, input supply (VREGIN) > 3.6 V                                                               | _        | 125               | 186        | μA       |       |

| I <sub>DDstby</sub>                            | Quiescent current — Standby mode, load current equal zero                                                                                             | _        | 1.1               | 10         | μA       |       |

| I <sub>DDoff</sub>                             | <ul> <li>Quiescent current — Shutdown mode</li> <li>VREGIN = 5.0 V and temperature=25 °C</li> <li>Across operating voltage and temperature</li> </ul> | _        | 650<br>—          | 4          | nA<br>μA |       |

| I <sub>LOADrun</sub>                           | Maximum load current — Run mode                                                                                                                       |          |                   | 120        | mA       |       |

| I <sub>LOADstby</sub><br>V <sub>Reg33out</sub> | Maximum load current — Standby mode<br>Regulator output voltage — Input supply<br>(VREGIN) > 3.6 V                                                    |          |                   | 1          | mA       |       |

|                                                | <ul><li>Run mode</li><li>Standby mode</li></ul>                                                                                                       | 3<br>2.1 | 3.3<br>2.8        | 3.6<br>3.6 | V<br>V   |       |

| V <sub>Reg33out</sub>                          | Regulator output voltage — Input supply<br>(VREGIN) < 3.6 V, pass-through mode                                                                        | 2.1      | _                 | 3.6        | V        | 2     |

| C <sub>OUT</sub>                               | External output capacitor                                                                                                                             | 1.76     | 2.2               | 8.16       | μF       |       |

| ESR                                            | External output capacitor equivalent series resistance                                                                                                | 1        | —                 | 100        | mΩ       |       |

| I <sub>LIM</sub>                               | Short circuit current                                                                                                                                 | _        | 290               | _          | mA       |       |

1. Typical values assume VREGIN = 5.0 V, Temp = 25  $^\circ\text{C}$  unless otherwise stated.

2. Operating in pass-through mode: regulator output voltage equal to the input voltage minus a drop proportional to ILoad.

### Peripheral operating requirements and behaviors

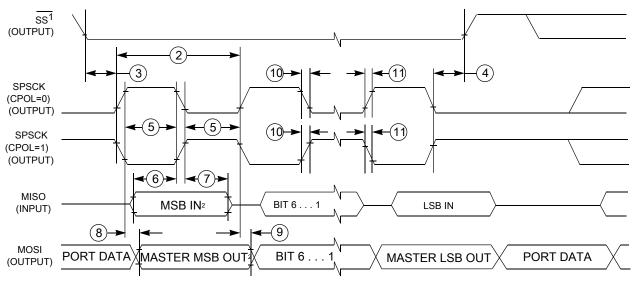

1.If configured as output

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

### Figure 14. SPI master mode timing (CPHA = 1)

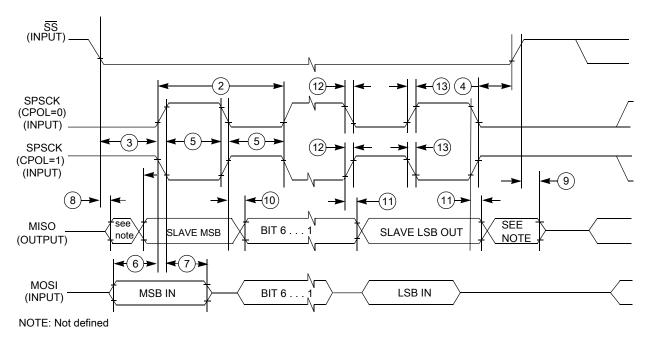

| Table 33. | SPI slave mode timing on slew rate disabled pads |

|-----------|--------------------------------------------------|

|-----------|--------------------------------------------------|

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  | —                        | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | —                        | t <sub>periph</sub> | —    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | —                        | ns                  | —    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2.5                      | _                        | ns                  | —    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 3.5                      | _                        | ns                  | —    |

| 8    | t <sub>a</sub>      | Slave access time              | _                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | —                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 31                       | ns                  | —    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | _                        | t <sub>periph</sub> - 25 | ns                  | —    |

|      | t <sub>FI</sub>     | Fall time input                | ]                        |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 25                       | ns                  | _    |

|      | t <sub>FO</sub>     | Fall time output               | ]                        |                          |                     |      |

1. For SPI0  $f_{periph}$  is the bus clock (f\_{BUS}). For SPI1  $f_{periph}$  is the system clock (f\_{SYS}).

- 2.  $t_{periph} = 1/f_{periph}$

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

| Num. | Symbol              | Description                    | Min.                     | Max.                     | Unit                | Note |

|------|---------------------|--------------------------------|--------------------------|--------------------------|---------------------|------|

| 1    | f <sub>op</sub>     | Frequency of operation         | 0                        | f <sub>periph</sub> /4   | Hz                  | 1    |

| 2    | t <sub>SPSCK</sub>  | SPSCK period                   | 4 x t <sub>periph</sub>  |                          | ns                  | 2    |

| 3    | t <sub>Lead</sub>   | Enable lead time               | 1                        | —                        | t <sub>periph</sub> | _    |

| 4    | t <sub>Lag</sub>    | Enable lag time                | 1                        | —                        | t <sub>periph</sub> | —    |

| 5    | t <sub>WSPSCK</sub> | Clock (SPSCK) high or low time | t <sub>periph</sub> - 30 | _                        | ns                  | —    |

| 6    | t <sub>SU</sub>     | Data setup time (inputs)       | 2                        | —                        | ns                  | _    |

| 7    | t <sub>HI</sub>     | Data hold time (inputs)        | 7                        | _                        | ns                  | _    |

| 8    | t <sub>a</sub>      | Slave access time              | —                        | t <sub>periph</sub>      | ns                  | 3    |

| 9    | t <sub>dis</sub>    | Slave MISO disable time        | —                        | t <sub>periph</sub>      | ns                  | 4    |

| 10   | t <sub>v</sub>      | Data valid (after SPSCK edge)  | —                        | 122                      | ns                  | _    |

| 11   | t <sub>HO</sub>     | Data hold time (outputs)       | 0                        | _                        | ns                  | —    |

| 12   | t <sub>RI</sub>     | Rise time input                | —                        | t <sub>periph</sub> - 25 | ns                  | —    |

|      | t <sub>FI</sub>     | Fall time input                |                          |                          |                     |      |

| 13   | t <sub>RO</sub>     | Rise time output               | —                        | 36                       | ns                  | _    |

|      | t <sub>FO</sub>     | Fall time output               |                          |                          |                     |      |

Table 34. SPI slave mode timing on slew rate enabled pads

1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

- 2.  $t_{periph} = 1/f_{periph}$

- 3. Time to data active from high-impedance state

- 4. Hold time to high-impedance state

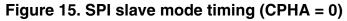

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)              | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 30   | -    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   |      | -    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | _    |      | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 0    | —    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 30   | —    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                    |      | _    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>    | —    | 72   | ns          |

# Table 39. I2S/SAI slave mode timing in VLPR, VLPW, and VLPS modes (full voltage range)(continued)

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

# 3.9 Human-machine interfaces (HMI)

# 3.9.1 TSI electrical specifications

### Table 40. TSI electrical specifications

| Sy   | ymbol | Description                         | Min. | Тур. | Max. | Unit |

|------|-------|-------------------------------------|------|------|------|------|

| TSI_ | _RUNF | Fixed power consumption in run mode | _    | 100  |      | μA   |

Table continues on the next page ...

| 64<br>LQFP | 48<br>QFN | 32<br>QFN | Pin Name | Default                             | ALT0                                | ALT1  | ALT2      | ALT3     | ALT4           | ALT5      | ALT6             | ALT7    |

|------------|-----------|-----------|----------|-------------------------------------|-------------------------------------|-------|-----------|----------|----------------|-----------|------------------|---------|

| 1          | _         | 1         | PTE0     | DISABLED                            |                                     | PTE0  | SPI1_MISO | UART1_TX | RTC_<br>CLKOUT | CMP0_OUT  | I2C1_SDA         |         |

| 2          | _         | -         | PTE1     | DISABLED                            |                                     | PTE1  | SPI1_MOSI | UART1_RX |                | SPI1_MISO | I2C1_SCL         |         |

| 3          | 1         | _         | VDD      | VDD                                 | VDD                                 |       | _         | _        |                | _         | _                |         |

| 4          | 2         | 2         | VSS      | VSS                                 | VSS                                 |       |           |          |                |           |                  |         |

| 5          | 3         | 3         | USB0_DP  | USB0_DP                             | USB0_DP                             |       |           |          |                |           |                  |         |

| 6          | 4         | 4         | USB0_DM  | USB0_DM                             | USB0_DM                             |       |           |          |                |           |                  |         |

| 7          | 5         | 5         | VOUT33   | VOUT33                              | VOUT33                              |       |           |          |                |           |                  |         |

| 8          | 6         | 6         | VREGIN   | VREGIN                              | VREGIN                              |       |           |          |                |           |                  |         |

| 9          | 7         | -         | PTE20    | ADC0_DP0/<br>ADC0_SE0               | ADC0_DP0/<br>ADC0_SE0               | PTE20 |           | TPM1_CH0 | UART0_TX       |           |                  |         |

| 10         | 8         | _         | PTE21    | ADC0_DM0/<br>ADC0_SE4a              | ADC0_DM0/<br>ADC0_SE4a              | PTE21 |           | TPM1_CH1 | UART0_RX       |           |                  |         |

| 11         | _         | _         | PTE22    | ADC0_DP3/<br>ADC0_SE3               | ADC0_DP3/<br>ADC0_SE3               | PTE22 |           | TPM2_CH0 | UART2_TX       |           |                  |         |

| 12         | _         | _         | PTE23    | ADC0_DM3/<br>ADC0_SE7a              | ADC0_DM3/<br>ADC0_SE7a              | PTE23 |           | TPM2_CH1 | UART2_RX       |           |                  |         |

| 13         | 9         | 7         | VDDA     | VDDA                                | VDDA                                |       |           |          |                |           |                  |         |

| 14         | 10        | _         | VREFH    | VREFH                               | VREFH                               |       |           |          |                |           |                  |         |

| 15         | 11        | -         | VREFL    | VREFL                               | VREFL                               |       |           |          |                |           |                  |         |

| 16         | 12        | 8         | VSSA     | VSSA                                | VSSA                                |       |           |          |                |           |                  |         |

| 17         | 13        | -         | PTE29    | CMP0_IN5/<br>ADC0_SE4b              | CMP0_IN5/<br>ADC0_SE4b              | PTE29 |           | TPM0_CH2 | TPM_CLKIN0     |           |                  |         |

| 18         | 14        | 9         | PTE30    | DAC0_OUT/<br>ADC0_SE23/<br>CMP0_IN4 | DAC0_OUT/<br>ADC0_SE23/<br>CMP0_IN4 | PTE30 |           | TPM0_CH3 | TPM_CLKIN1     |           |                  |         |

| 19         | _         | _         | PTE31    | DISABLED                            |                                     | PTE31 |           | TPM0_CH4 |                |           |                  |         |

| 20         | 15        | -         | PTE24    | DISABLED                            |                                     | PTE24 |           | TPM0_CH0 |                | I2C0_SCL  |                  |         |

| 21         | 16        | _         | PTE25    | DISABLED                            |                                     | PTE25 |           | TPM0_CH1 |                | I2C0_SDA  |                  |         |

| 22         | 17        | 10        | PTA0     | SWD_CLK                             | TSI0_CH1                            | PTA0  |           | TPM0_CH5 |                |           |                  | SWD_CLK |

| 23         | 18        | 11        | PTA1     | DISABLED                            | TSI0_CH2                            | PTA1  | UART0_RX  | TPM2_CH0 |                |           |                  |         |

| 24         | 19        | 12        | PTA2     | DISABLED                            | TSI0_CH3                            | PTA2  | UART0_TX  | TPM2_CH1 |                |           |                  |         |

| 25         | 20        | 13        | PTA3     | SWD_DIO                             | TSI0_CH4                            | PTA3  | I2C1_SCL  | TPM0_CH0 |                |           |                  | SWD_DIO |

| 26         | 21        | 14        | PTA4     | NMI_b                               | TSI0_CH5                            | PTA4  | I2C1_SDA  | TPM0_CH1 |                |           |                  | NMI_b   |

| 27         | -         | -         | PTA5     | DISABLED                            |                                     | PTA5  | USB_CLKIN | TPM0_CH2 |                |           | I2S0_TX_<br>BCLK |         |

| 28         | -         | _         | PTA12    | DISABLED                            |                                     | PTA12 |           | TPM1_CH0 |                |           | I2S0_TXD0        |         |

| 29         | _         | _         | PTA13    | DISABLED                            |                                     | PTA13 |           | TPM1_CH1 |                |           | I2S0_TX_FS       |         |

| 30         | 22        | 15        | VDD      | VDD                                 | VDD                                 |       |           |          |                |           |                  |         |

| 31         | 23        | 16        | VSS      | VSS                                 | VSS                                 |       |           |          |                |           |                  |         |

| 32         | 24        | 17        | PTA18    | EXTAL0                              | EXTAL0                              | PTA18 |           | UART1_RX | TPM_CLKIN0     |           |                  |         |

| 33         | 25        | 18        | PTA19    | XTAL0                               | XTAL0                               | PTA19 |           | UART1_TX | TPM_CLKIN1     |           | LPTMR0_<br>ALT1  |         |

Kinetis KL26 Sub-Family, Rev5 08/2014.

# 7.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

# 7.2 Format

Part numbers for this device have the following format:

Q KL## A FFF R T PP CC N

# 7.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                 | Values                                                                                                                 |

|-------|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status        | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>                             |

| KL##  | Kinetis family              | • KL26                                                                                                                 |

| A     | Key attribute               | • Z = Cortex-M0+                                                                                                       |

| FFF   | Program flash memory size   | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> <li>128 = 128 KB</li> </ul>                                               |

| R     | Silicon revision            | <ul> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                    |

| Т     | Temperature range (°C)      | • V = -40 to 105                                                                                                       |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | • 4 = 48 MHz                                                                                                           |

| N     | Packaging type              | R = Tape and reel                                                                                                      |

# 7.4 Example

This is an example part number:

MKL26Z128VFM4

# 8 Terminology and guidelines

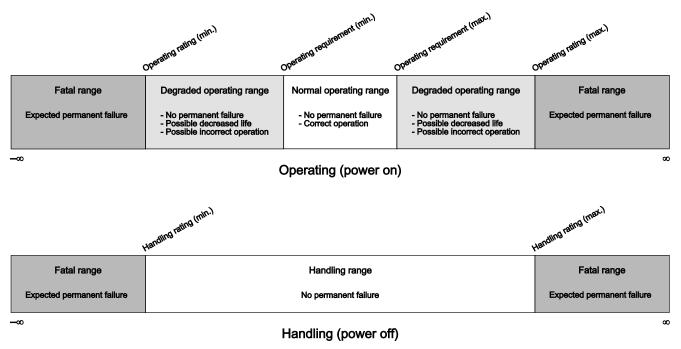

# 8.1 Definition: Operating requirement

An *operating requirement* is a specified value or range of values for a technical characteristic that you must guarantee during operation to avoid incorrect operation and possibly decreasing the useful life of the chip.

## 8.1.1 Example

This is an example of an operating requirement:

| Symbol          | Description                  | Min. | Max. | Unit |

|-----------------|------------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply<br>voltage | 0.9  | 1.1  | V    |

# 8.2 Definition: Operating behavior

Unless otherwise specified, an *operating behavior* is a specified value or range of values for a technical characteristic that are guaranteed during operation if you meet the operating requirements and any other specified conditions.

# 8.3 Definition: Attribute

An *attribute* is a specified value or range of values for a technical characteristic that are guaranteed, regardless of whether you meet the operating requirements.

## 8.3.1 Example

This is an example of an attribute:

| Symbol | Description                        | Min. | Max. | Unit |

|--------|------------------------------------|------|------|------|

| CIN_D  | Input capacitance:<br>digital pins | —    | 7    | pF   |

# 8.4 Definition: Rating

A *rating* is a minimum or maximum value of a technical characteristic that, if exceeded, may cause permanent chip failure:

- Operating ratings apply during operation of the chip.

- *Handling ratings* apply when the chip is not powered.

## 8.4.1 Example

This is an example of an operating rating:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

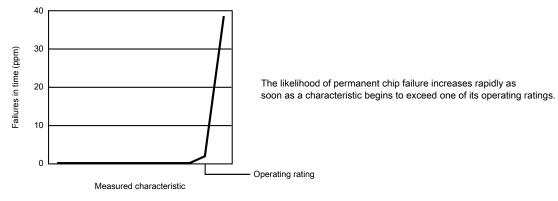

# 8.5 Result of exceeding a rating

# 8.6 Relationship between ratings and operating requirements

# 8.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

- Never exceed any of the chip's ratings.

- During normal operation, don't exceed any of the chip's operating requirements.

- If you must exceed an operating requirement at times other than during normal operation (for example, during power sequencing), limit the duration as much as possible.

# 8.8 Definition: Typical value

A *typical value* is a specified value for a technical characteristic that:

- Lies within the range of values specified by the operating behavior

- Given the typical manufacturing process, is representative of that characteristic during operation when you meet the typical-value conditions or other specified conditions

Typical values are provided as design guidelines and are neither tested nor guaranteed.