Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014.10                    |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Active                                                               |

| Core Processor             | ARM® Cortex®-M0+                                                     |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 48MHz                                                                |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART, USB, USB OTG              |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT    |

| Number of I/O              | 23                                                                   |

| Program Memory Size        | 32KB (32K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 4K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                         |

| Data Converters            | A/D - 16bit; D/A - 12bit                                             |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                   |

| Mounting Type              | Surface Mount, Wettable Flank                                        |

| Package / Case             | 32-VFQFN Exposed Pad                                                 |

| Supplier Device Package    | 32-HVQFN (5x5)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mkl26z32vfm4 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Ratings

## 1.1 Thermal handling ratings

#### Table 1. Thermal handling ratings

| Symbol           | Description                   | Min. | Max. | Unit | Notes |

|------------------|-------------------------------|------|------|------|-------|

| T <sub>STG</sub> | Storage temperature           | -55  | 150  | °C   | 1     |

| T <sub>SDR</sub> | Solder temperature, lead-free | _    | 260  | °C   | 2     |

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

## **1.2 Moisture handling ratings**

#### Table 2. Moisture handling ratings

| Symbol | Description                | Min. | Max. | Unit | Notes |

|--------|----------------------------|------|------|------|-------|

| MSL    | Moisture sensitivity level | _    | 3    | —    | 1     |

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices.

# 1.3 ESD handling ratings

Table 3. ESD handling ratings

| Symbol           | Description                                           | Min.  | Max.  | Unit | Notes |

|------------------|-------------------------------------------------------|-------|-------|------|-------|

| V <sub>HBM</sub> | Electrostatic discharge voltage, human body model     | -2000 | +2000 | V    | 1     |

| V <sub>CDM</sub> | Electrostatic discharge voltage, charged-device model | -500  | +500  | V    | 2     |

| I <sub>LAT</sub> | Latch-up current at ambient temperature of 105 °C     | -100  | +100  | mA   | 3     |

1. Determined according to JEDEC Standard JESD22-A114, *Electrostatic Discharge (ESD) Sensitivity Testing Human Body Model (HBM)*.

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

## 1.4 Voltage and current operating ratings

Table 4. Voltage and current operating ratings

| Symbol              | Description                                                               | Min.                  | Max.                  | Unit |

|---------------------|---------------------------------------------------------------------------|-----------------------|-----------------------|------|

| V <sub>DD</sub>     | Digital supply voltage                                                    | -0.3                  | 3.8                   | V    |

| I <sub>DD</sub>     | Digital supply current                                                    | _                     | 120                   | mA   |

| V <sub>IO</sub>     | IO pin input voltage                                                      | -0.3                  | V <sub>DD</sub> + 0.3 | V    |

| Ι <sub>D</sub>      | Instantaneous maximum current single pin limit (applies to all port pins) | -25                   | 25                    | mA   |

| V <sub>DDA</sub>    | Analog supply voltage                                                     | V <sub>DD</sub> – 0.3 | V <sub>DD</sub> + 0.3 | V    |

| V <sub>USB_DP</sub> | USB_DP input voltage                                                      | -0.3                  | 3.63                  | V    |

| $V_{USB_{DM}}$      | USB_DM input voltage                                                      | -0.3                  | 3.63                  | V    |

| V <sub>REGIN</sub>  | USB regulator input                                                       | -0.3                  | 6.0                   | V    |

# 2 General

## 2.1 AC electrical characteristics

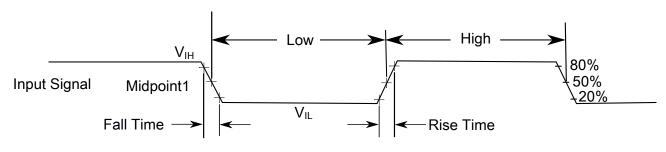

Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured at the 20% and 80% points, as shown in the following figure.

The midpoint is V<sub>IL</sub> + (V<sub>IH</sub> - V<sub>IL</sub>) / 2

#### Figure 1. Input signal measurement reference

All digital I/O switching characteristics, unless otherwise specified, assume the output pins have the following characteristics.

- C<sub>L</sub>=30 pF loads

- Slew rate disabled

- Normal drive strength

| Symbol                    | Description                                                                                                                                                                                                                      | Temp.     | Тур.  | Max   | Unit | Note |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------|-------|------|------|

| I <sub>DD_RUN</sub>       | Run mode current - 48 MHz core / 24                                                                                                                                                                                              | at 25 °C  | 6.0   | 6.2   | mA   | 3, 4 |

|                           | MHz bus and flash, all peripheral clocks enabled, code executing from                                                                                                                                                            | at 70 °C  | 6.2   | 6.4   | mA   |      |

|                           | flash, at 3.0 V                                                                                                                                                                                                                  | at 125 °C | 6.2   | 6.5   | mA   |      |

| I <sub>DD_WAIT</sub>      | Wait mode current - core disabled / 48<br>MHz system / 24 MHz bus / flash<br>disabled (flash doze enabled), all<br>peripheral clocks disabled, at 3.0 V                                                                          | _         | 2.7   | 3.2   | mA   | 3    |

| I <sub>DD_WAIT</sub>      | Wait mode current - core disabled / 24<br>MHz system / 24 MHz bus / flash<br>disabled (flash doze enabled), all<br>peripheral clocks disabled, at 3.0 V                                                                          | _         | 2.1   | 2.6   | mA   | 3    |

| I <sub>DD_PSTOP2</sub>    | Stop mode current with partial stop 2<br>clocking option - core and system<br>disabled / 10.5 MHz bus, at 3.0 V                                                                                                                  | —         | 1.5   | 2.0   | mA   | 3    |

| I <sub>DD_VLPRCO_CM</sub> | Very-low-power run mode current in<br>compute operation - 4 MHz core / 0.8<br>MHz flash / bus clock disabled,<br>LPTMR running with 4 MHz internal<br>reference clock, CoreMark benchmark<br>code executing from flash, at 3.0 V | _         | 732   | _     | μA   | 5    |

| I <sub>DD_VLPRCO</sub>    | Very low power run mode current in<br>compute operation - 4 MHz core / 0.8<br>MHz flash / bus clock disabled, code<br>executing from flash, at 3.0 V                                                                             |           | 161   | 329   | μA   | 6    |

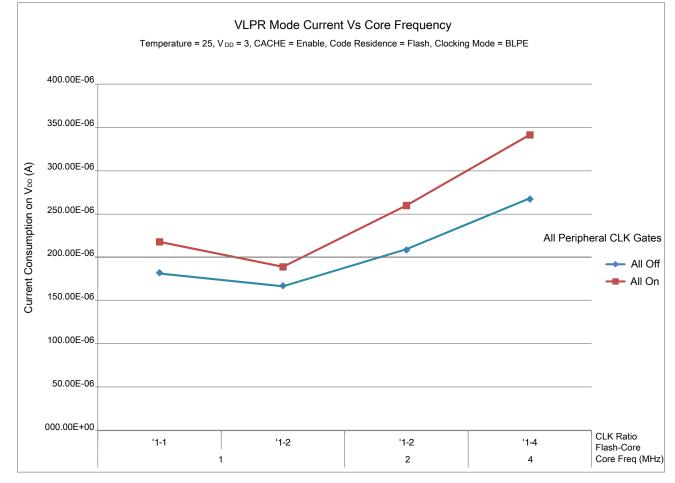

| I <sub>DD_VLPR</sub>      | Very low power run mode current - 4<br>MHz core / 0.8 MHz bus and flash, all<br>peripheral clocks disabled, code<br>executing from flash, at 3.0 V                                                                               | _         | 185   | 352   | μA   | 6    |

| I <sub>DD_VLPR</sub>      | Very low power run mode current - 4<br>MHz core / 0.8 MHz bus and flash, all<br>peripheral clocks enabled, code<br>executing from flash, at 3.0 V                                                                                | _         | 255   | 421   | μA   | 4, 6 |

| I <sub>DD_VLPW</sub>      | Very low power wait mode current -<br>core disabled / 4 MHz system / 0.8<br>MHz bus / flash disabled (flash doze<br>enabled), all peripheral clocks<br>disabled, at 3.0 V                                                        | _         | 110   | 281   | μA   | 6    |

| I <sub>DD_STOP</sub>      | Stop mode current at 3.0 V                                                                                                                                                                                                       | at 25 °C  | 305   | 326   | μA   |      |

|                           |                                                                                                                                                                                                                                  | at 50 °C  | 317   | 344   | μA   |      |

|                           |                                                                                                                                                                                                                                  | at 70 °C  | 337   | 380   | μA   |      |

|                           |                                                                                                                                                                                                                                  | at 85 °C  | 364   | 428   | μA   |      |

|                           |                                                                                                                                                                                                                                  | at 105 °C | 429   | 553   | μA   | 1    |

| I <sub>DD_VLPS</sub>      | Very-low-power stop mode current at                                                                                                                                                                                              | at 25 °C  | 2.69  | 4.14  | μA   | _    |

|                           | 3.0 V                                                                                                                                                                                                                            | at 50 °C  | 5.54  | 9.80  | μA   | 1    |

|                           |                                                                                                                                                                                                                                  | at 70 °C  | 11.80 | 21.94 | μA   | 1    |

### Table 9. Power consumption operating behaviors (continued)

| Symbol                     | Description                                                                                                                                                                 |                                                                                                                                                                                                                                                           |     | ٦   | empera | ature (° | C)  |     | Unit |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------|----------|-----|-----|------|

|                            |                                                                                                                                                                             |                                                                                                                                                                                                                                                           | -40 | 25  | 50     | 70       | 85  | 105 |      |

| I <sub>IREFSTEN4MHz</sub>  | 4 MHz internal reference clock<br>Measured by entering STOP o<br>with 4 MHz IRC enabled.                                                                                    |                                                                                                                                                                                                                                                           | 56  | 56  | 56     | 56       | 56  | 56  | μA   |

| I <sub>IREFSTEN32KHz</sub> | 32 kHz internal reference clock<br>Measured by entering STOP n<br>32 kHz IRC enabled.                                                                                       |                                                                                                                                                                                                                                                           | 52  | 52  | 52     | 52       | 52  | 52  | μA   |

| I <sub>EREFSTEN4MHz</sub>  | External 4 MHz crystal clock adder.<br>Measured by entering STOP or VLPS mode<br>with the crystal enabled.                                                                  |                                                                                                                                                                                                                                                           | 206 | 228 | 237    | 245      | 251 | 258 | μA   |

| I <sub>EREFSTEN32KHz</sub> |                                                                                                                                                                             |                                                                                                                                                                                                                                                           | 440 | 490 | 540    | 560      | 570 | 580 | nA   |

|                            | adder by means of the<br>OSC0_CR[EREFSTEN and                                                                                                                               | VLLS3                                                                                                                                                                                                                                                     | 440 | 490 | 540    | 560      | 570 | 580 |      |

|                            | EREFSTEN] bits. Measured                                                                                                                                                    | LLS                                                                                                                                                                                                                                                       | 490 | 490 | 540    | 560      | 570 | 680 |      |

|                            | by entering all modes with the                                                                                                                                              | VLPS                                                                                                                                                                                                                                                      | 510 | 560 | 560    | 560      | 610 | 680 |      |

|                            | crystal enabled.                                                                                                                                                            | STOP                                                                                                                                                                                                                                                      | 510 | 560 | 560    | 560      | 610 | 680 |      |

| I <sub>CMP</sub>           | CMP peripheral adder measur<br>the device in VLLS1 mode with<br>using the 6-bit DAC and a sing<br>input for compare. Includes 6-b<br>consumption.                           | CMP enabled                                                                                                                                                                                                                                               | 22  | 22  | 22     | 22       | 22  | 22  | μA   |

| I <sub>RTC</sub>           | the device in VLLS1 mode with<br>kHz crystal enabled by means<br>RTC_CR[OSCE] bit and the R                                                                                 | RTC peripheral adder measured by placing<br>the device in VLLS1 mode with external 32<br>kHz crystal enabled by means of the<br>RTC_CR[OSCE] bit and the RTC ALARM set<br>for 1 minute. Includes ERCLK32K (32 kHz<br>external ervictal) power consumption |     | 357 | 388    | 475      | 532 | 810 | nA   |

| I <sub>UART</sub>          | UART peripheral adder<br>measured by placing the<br>device in STOP or VLPS<br>mode with selected clock<br>source waiting for RX data at                                     | MCGIRCLK<br>(4 MHz<br>internal<br>reference<br>clock)                                                                                                                                                                                                     | 66  | 66  | 66     | 66       | 66  | 66  | μA   |

|                            | 115200 baud rate. Includes<br>selected clock source power<br>consumption.                                                                                                   | OSCERCLK<br>(4 MHz<br>external<br>crystal)                                                                                                                                                                                                                | 214 | 237 | 246    | 254      | 260 | 268 |      |

| I <sub>TPM</sub>           | TPM peripheral adder<br>measured by placing the<br>device in STOP or VLPS<br>mode with selected clock<br>source configured for output                                       | MCGIRCLK<br>(4 MHz<br>internal<br>reference<br>clock)                                                                                                                                                                                                     | 86  | 86  | 86     | 86       | 86  | 86  | μA   |

|                            | compare generating 100 Hz<br>clock signal. No load is<br>placed on the I/O generating<br>the clock signal. Includes<br>selected clock source and I/O<br>switching currents. | OSCERCLK<br>(4 MHz<br>external<br>crystal)                                                                                                                                                                                                                | 235 | 256 | 265    | 274      | 280 | 287 |      |

### Table 10. Low power mode peripheral adders — typical value

Figure 3. VLPR mode current vs. core frequency

### 2.2.6 EMC radiated emissions operating behaviors Table 11. EMC radiated emissions operating behaviors

| Symbol              | Description                        | Frequency<br>band<br>(MHz) | Тур. | Unit | Notes |

|---------------------|------------------------------------|----------------------------|------|------|-------|

| V <sub>RE1</sub>    | Radiated emissions voltage, band 1 | 0.15–50                    | 16   | dBµV | 1, 2  |

| V <sub>RE2</sub>    | Radiated emissions voltage, band 2 | 50–150                     | 18   | dBµV |       |

| V <sub>RE3</sub>    | Radiated emissions voltage, band 3 | 150–500                    | 11   | dBµV |       |

| V <sub>RE4</sub>    | Radiated emissions voltage, band 4 | 500–1000                   | 13   | dBµV |       |

| V <sub>RE_IEC</sub> | IEC level                          | 0.15–1000                  | М    | _    | 2, 3  |

Determined according to IEC Standard 61967-1, Integrated Circuits - Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 1: General Conditions and Definitions and IEC Standard 61967-2, Integrated Circuits -Measurement of Electromagnetic Emissions, 150 kHz to 1 GHz Part 2: Measurement of Radiated Emissions—TEM Cell and Wideband TEM Cell Method. Measurements were made while the microcontroller was running basic

#### 2.4.2 Thermal attributes Table 16. Thermal attributes

| Board type        | Symbol            | Description                                                                                              | 64 LQFP | 48 QFN | 32 QFN | Unit | Notes |

|-------------------|-------------------|----------------------------------------------------------------------------------------------------------|---------|--------|--------|------|-------|

| Single-layer (1S) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 71      | 83     | 98     | °C/W | 1     |

| Four-layer (2s2p) | R <sub>θJA</sub>  | Thermal resistance, junction to ambient (natural convection)                                             | 53      | 30     | 34     | °C/W |       |

| Single-layer (1S) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 59      | 68     | 82     | °C/W |       |

| Four-layer (2s2p) | R <sub>θJMA</sub> | Thermal resistance, junction to ambient (200 ft./min. air speed)                                         | 46      | 24     | 28     | °C/W |       |

| _                 | R <sub>θJB</sub>  | Thermal resistance, junction to board                                                                    | 35      | 12     | 13     | °C/W | 2     |

| _                 | R <sub>θJC</sub>  | Thermal resistance, junction to case                                                                     | 21      | 2.3    | 2.3    | °C/W | 3     |

| _                 | Ψ <sub>JT</sub>   | Thermal characterization<br>parameter, junction to package<br>top outside center (natural<br>convection) | 6       | 5      | 8      | °C/W | 4     |

- 1. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air), or EIA/JEDEC Standard JESD51-6, Integrated Circuit Thermal Test Method Environmental Conditions—Forced Convection (Moving Air).

- 2. Determined according to JEDEC Standard JESD51-8, Integrated Circuit Thermal Test Method Environmental Conditions—Junction-to-Board.

- 3. Determined according to Method 1012.1 of MIL-STD 883, *Test Method Standard, Microcircuits*, with the cold plate temperature used for the case temperature. The value includes the thermal resistance of the interface material between the top of the package and the cold plate.

- 4. Determined according to JEDEC Standard JESD51-2, Integrated Circuits Thermal Test Method Environmental Conditions—Natural Convection (Still Air).

# **3** Peripheral operating requirements and behaviors

## 3.1 Core modules

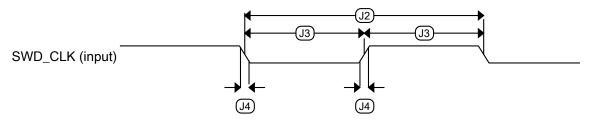

## 3.1.1 SWD electricals

| Symbol     | Description                                     | Min. | Max. | Unit |

|------------|-------------------------------------------------|------|------|------|

|            | Operating voltage                               | 1.71 | 3.6  | V    |

| J1         | SWD_CLK frequency of operation                  |      |      |      |

|            | Serial wire debug                               | 0    | 25   | MHz  |

| J2         | SWD_CLK cycle period                            | 1/J1 | _    | ns   |

| JЗ         | SWD_CLK clock pulse width                       |      |      |      |

|            | Serial wire debug                               | 20   | _    | ns   |

| J4         | SWD_CLK rise and fall times                     | _    | 3    | ns   |

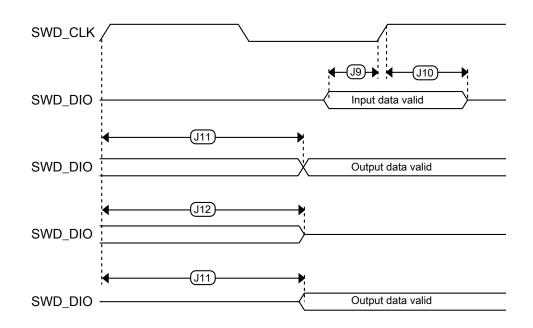

| <b>J</b> 9 | SWD_DIO input data setup time to SWD_CLK rise   | 10   | _    | ns   |

| J10        | SWD_DIO input data hold time after SWD_CLK rise | 0    | —    | ns   |

| J11        | SWD_CLK high to SWD_DIO data valid              | —    | 32   | ns   |

| J12        | SWD_CLK high to SWD_DIO high-Z                  | 5    | _    | ns   |

Table 17. SWD full voltage range electricals

Figure 4. Serial wire clock input timing

Figure 5. Serial wire data timing

## 3.2 System modules

There are no specifications necessary for the device's system modules.

## 3.3 Clock modules

## 3.3.1 MCG specifications

Table 18. MCG specifications

| Symbol                  | Description                                                                                                                  | Min.  | Тур.   | Max.    | Unit              | Notes |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------|-------|--------|---------|-------------------|-------|

| f <sub>ints_ft</sub>    | Internal reference frequency (slow clock) — factory trimmed at nominal V <sub>DD</sub> and 25 °C                             | —     | 32.768 | _       | kHz               |       |

| f <sub>ints_t</sub>     | Internal reference frequency (slow clock) — user trimmed                                                                     | 31.25 | —      | 39.0625 | kHz               |       |

| $\Delta_{fdco\_res\_t}$ | Resolution of trimmed average DCO output<br>frequency at fixed voltage and temperature —<br>using C3[SCTRIM] and C4[SCFTRIM] | _     | ± 0.3  | ± 0.6   | %f <sub>dco</sub> | 1     |

| Symbol                       | Description                                                                                                                     |                                                                                                 | Min.                            | Тур.      | Max.    | Unit                  | Notes |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------|-----------|---------|-----------------------|-------|

| $\Delta f_{dco_t}$           |                                                                                                                                 | trimmed average DCO output<br>Itage and temperature                                             | —                               | +0.5/-0.7 | ± 3     | %f <sub>dco</sub>     | 1, 2  |

| $\Delta f_{dco_t}$           |                                                                                                                                 | trimmed average DCO output<br>ed voltage and temperature                                        | —                               | ± 0.4     | ± 1.5   | %f <sub>dco</sub>     | 1, 2  |

| f <sub>intf_ft</sub>         |                                                                                                                                 | frequency (fast clock) —<br>nominal V <sub>DD</sub> and 25 °C                                   |                                 | 4         | —       | MHz                   |       |

| ∆f <sub>intf_ft</sub>        | (fast clock) over te                                                                                                            | on of internal reference clock<br>emperature and voltage —<br>nominal V <sub>DD</sub> and 25 °C | _                               | +1/-2     | ± 3     | %f <sub>intf_ft</sub> | 2     |

| f <sub>intf_t</sub>          | Internal reference<br>trimmed at nomina                                                                                         | frequency (fast clock) — user<br>al V <sub>DD</sub> and 25 °C                                   | 3                               | _         | 5       | MHz                   |       |

| f <sub>loc_low</sub>         | Loss of external cl<br>RANGE = 00                                                                                               | ock minimum frequency —                                                                         | (3/5) x<br>f <sub>ints_t</sub>  | _         | —       | kHz                   |       |

| f <sub>loc_high</sub>        | Loss of external cl<br>RANGE = 01, 10,                                                                                          | ock minimum frequency —<br>or 11                                                                | (16/5) x<br>f <sub>ints_t</sub> | _         | —       | kHz                   |       |

|                              |                                                                                                                                 | FI                                                                                              | L                               |           |         |                       |       |

| f <sub>fll_ref</sub>         | FLL reference free                                                                                                              | quency range                                                                                    | 31.25                           | —         | 39.0625 | kHz                   |       |

| f <sub>dco</sub>             | DCO output<br>frequency range                                                                                                   | Low range (DRS = 00)<br>640 × f <sub>fll_ref</sub>                                              | 20                              | 20.97     | 25      | MHz                   | 3, 4  |

|                              |                                                                                                                                 | Mid range (DRS = 01)<br>1280 × $f_{fll_ref}$                                                    | 40                              | 41.94     | 48      | MHz                   |       |

| f <sub>dco_t_DMX3</sub><br>2 | DCO output<br>frequency                                                                                                         | Low range (DRS = 00)<br>732 × f <sub>fll_ref</sub>                                              |                                 | 23.99     | _       | MHz                   | 5, 6  |

|                              |                                                                                                                                 | Mid range (DRS = 01)<br>1464 × f <sub>fll_ref</sub>                                             | _                               | 47.97     | _       | MHz                   |       |

| J <sub>cyc_fll</sub>         | FLL period jitter<br>• f <sub>VCO</sub> = 48 M                                                                                  | Hz                                                                                              | _                               | 180       | —       | ps                    | 7     |

| t <sub>fll_acquire</sub>     | FLL target frequer                                                                                                              | ncy acquisition time                                                                            |                                 | —         | 1       | ms                    | 8     |

|                              |                                                                                                                                 | PI                                                                                              | LL                              |           |         |                       |       |

| f <sub>vco</sub>             | VCO operating fre                                                                                                               | quency                                                                                          | 48.0                            | —         | 100     | MHz                   |       |

| I <sub>pll</sub>             |                                                                                                                                 | rent<br>Hz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =<br>V multiplier = 48)         | _                               | 1060      | —       | μΑ                    | 9     |

| I <sub>pll</sub>             | PLL operating current<br>• PLL at 48 MHz (f <sub>osc_hi_1</sub> = 8 MHz, f <sub>pll_ref</sub> =<br>2 MHz, VDIV multiplier = 24) |                                                                                                 | _                               | 600       | —       | μΑ                    | 9     |

| f <sub>pll_ref</sub>         | PLL reference free                                                                                                              | quency range                                                                                    | 2.0                             | _         | 4.0     | MHz                   |       |

| J <sub>cyc_pll</sub>         | PLL period jitter (F                                                                                                            | RMS)                                                                                            |                                 |           |         |                       | 10    |

| J <sub>cyc_pll</sub>         | • f <sub>vco</sub> = 48 MH                                                                                                      | łz                                                                                              | _                               | 120       | _       | ps                    |       |

|                              | 100 -                                                                                                                           |                                                                                                 |                                 |           |         |                       |       |

| Table 18. | MCG s | pecifications | (continued) | ) |

|-----------|-------|---------------|-------------|---|

|-----------|-------|---------------|-------------|---|

| Symbol                | Description                           | Min.   | Тур. | Max.                                                  | Unit | Notes |

|-----------------------|---------------------------------------|--------|------|-------------------------------------------------------|------|-------|

| J <sub>acc_pll</sub>  | PLL accumulated jitter over 1µs (RMS) |        |      |                                                       |      | 10    |

|                       | • f <sub>vco</sub> = 48 MHz           | —      | 1350 | _                                                     | ps   |       |

|                       | • f <sub>vco</sub> = 100 MHz          | -      | 600  | _                                                     | ps   |       |

| D <sub>lock</sub>     | Lock entry frequency tolerance        | ± 1.49 |      | ± 2.98                                                | %    |       |

| D <sub>unl</sub>      | Lock exit frequency tolerance         | ± 4.47 | _    | ± 5.97                                                | %    |       |

| t <sub>pll_lock</sub> | Lock detector detection time          | _      |      | $150 \times 10^{-6}$<br>+ 1075(1/<br>$f_{pll\_ref}$ ) | S    | 11    |

#### Table 18. MCG specifications (continued)

- 1. This parameter is measured with the internal reference (slow clock) being used as a reference to the FLL (FEI clock mode).

- 2. The deviation is relative to the factory trimmed frequency at nominal  $V_{DD}$  and 25 °C,  $f_{ints_{ft}}$ .

- 3. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32 = 0.

- The resulting system clock frequencies must not exceed their maximum specified values. The DCO frequency deviation (Δf<sub>dco\_t</sub>) over voltage and temperature must be considered.

- 5. These typical values listed are with the slow internal reference clock (FEI) using factory trim and DMX32 = 1.

- 6. The resulting clock frequency must not exceed the maximum specified clock frequency of the device.

- 7. This specification is based on standard deviation (RMS) of period or frequency.

- 8. This specification applies to any time the FLL reference source or reference divider is changed, trim value is changed, DMX32 bit is changed, DRS bits are changed, or changing from FLL disabled (BLPE, BLPI) to FLL enabled (FEI, FEE, FBE, FBI). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

- 9. Excludes any oscillator currents that are also consuming power while PLL is in operation.

- 10. This specification was obtained using a Freescale developed PCB. PLL jitter is dependent on the noise characteristics of each PCB and results will vary.

- 11. This specification applies to any time the PLL VCO divider or reference divider is changed, or changing from PLL disabled (BLPE, BLPI) to PLL enabled (PBE, PEE). If a crystal/resonator is being used as the reference, this specification assumes it is already running.

## **3.3.2 Oscillator electrical specifications**

## 3.3.2.1 Oscillator DC electrical specifications

| Symbol   | Description                             | Min. | Тур. | Max. | Unit | Notes |

|----------|-----------------------------------------|------|------|------|------|-------|

| $V_{DD}$ | Supply voltage                          | 1.71 | —    | 3.6  | V    |       |

| IDDOSC   | Supply current — low-power mode (HGO=0) |      |      |      |      | 1     |

|          | • 32 kHz                                | -    | 500  | —    | nA   |       |

|          | • 4 MHz                                 | _    | 200  | _    | μA   |       |

|          | • 8 MHz (RANGE=01)                      | _    | 300  | _    | μA   |       |

|          | • 16 MHz                                | _    | 950  | _    | μA   |       |

|          |                                         | _    | 1.2  | _    | mA   |       |

Table 19. Oscillator DC electrical specifications

### 3.4.1.1 Flash timing specifications — program and erase

The following specifications represent the amount of time the internal charge pumps are active and do not include command overhead.

| Symbol                | bol Description                    |   | Тур. | Max. | Unit | Notes |

|-----------------------|------------------------------------|---|------|------|------|-------|

| t <sub>hvpgm4</sub>   | Longword Program high-voltage time | — | 7.5  | 18   | μs   | —     |

| t <sub>hversscr</sub> | Sector Erase high-voltage time     | — | 13   | 113  | ms   | 1     |

| t <sub>hversall</sub> | Erase All high-voltage time        | _ | 52   | 452  | ms   | 1     |

Table 21. NVM program/erase timing specifications

1. Maximum time based on expectations at cycling end-of-life.

#### 3.4.1.2 Flash timing specifications — commands Table 22. Flash command timing specifications

| Symbol                | Description                                   | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-----------------------------------------------|------|------|------|------|-------|

| t <sub>rd1sec1k</sub> | Read 1s Section execution time (flash sector) | —    | —    | 60   | μs   | 1     |

| t <sub>pgmchk</sub>   | Program Check execution time                  | —    | —    | 45   | μs   | 1     |

| t <sub>rdrsrc</sub>   | Read Resource execution time                  | —    | —    | 30   | μs   | 1     |

| t <sub>pgm4</sub>     | Program Longword execution time               | —    | 65   | 145  | μs   | _     |

| t <sub>ersscr</sub>   | Erase Flash Sector execution time             | —    | 14   | 114  | ms   | 2     |

| t <sub>rd1all</sub>   | Read 1s All Blocks execution time             | —    | —    | 1.8  | ms   | _     |

| t <sub>rdonce</sub>   | Read Once execution time                      | —    | —    | 25   | μs   | 1     |

| t <sub>pgmonce</sub>  | Program Once execution time                   | —    | 65   | —    | μs   | _     |

| t <sub>ersall</sub>   | Erase All Blocks execution time               | —    | 88   | 650  | ms   | 2     |

| t <sub>vfykey</sub>   | Verify Backdoor Access Key execution time     | —    |      | 30   | μs   | 1     |

1. Assumes 25 MHz flash clock frequency.

2. Maximum times for erase parameters based on expectations at cycling end-of-life.

#### 3.4.1.3 Flash high voltage current behaviors Table 23. Flash high voltage current behaviors

| Symbol              | Description                                                           | Min. | Тур. | Max. | Unit |

|---------------------|-----------------------------------------------------------------------|------|------|------|------|

| I <sub>DD_PGM</sub> | Average current adder during high voltage flash programming operation | —    | 2.5  | 6.0  | mA   |

| I <sub>DD_ERS</sub> | Average current adder during high voltage flash erase operation       |      | 1.5  | 4.0  | mA   |

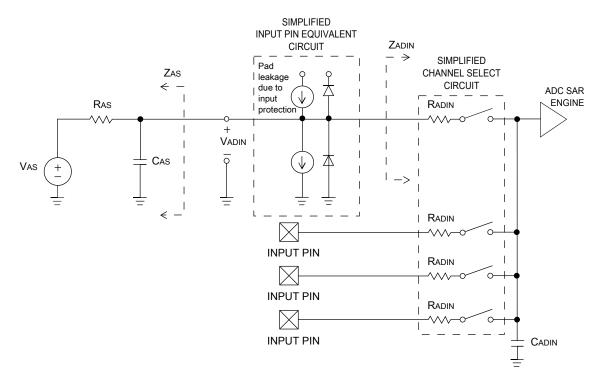

Figure 6. ADC input impedance equivalency diagram

### 3.6.1.2 16-bit ADC electrical characteristics

| Symbol               | Description                    | Conditions <sup>1</sup>              | Min.         | Typ. <sup>2</sup> | Max.            | Unit             | Notes                |

|----------------------|--------------------------------|--------------------------------------|--------------|-------------------|-----------------|------------------|----------------------|

| I <sub>DDA_ADC</sub> | Supply current                 |                                      | 0.215        | —                 | 1.7             | mA               | 3                    |

|                      | ADC                            | • ADLPC = 1, ADHSC =                 | 1.2          | 2.4               | 3.9             | MHz              | t <sub>ADACK</sub> = |

|                      | asynchronous<br>clock source   | 0                                    | 2.4          | 4.0               | 6.1             | MHz              | 1/f <sub>ADACK</sub> |

| CIOCK SOULCE         | • ADLPC = 1, ADHSC = 1         | 3.0                                  | 5.2          | 7.3               | MHz             |                  |                      |

| f <sub>ADACK</sub>   | f <sub>ADACK</sub>             | • ADLPC = 0, ADHSC = 0               | 4.4          | 6.2               | 9.5             | MHz              |                      |

|                      |                                | • ADLPC = 0, ADHSC = 1               |              |                   |                 |                  |                      |

|                      | Sample Time                    | See Reference Manual chapte          | r for sample | times             | 1               |                  | I                    |

| TUE                  | Total unadjusted               | 12-bit modes                         |              | ±4                | ±6.8            | LSB <sup>4</sup> | 5                    |

|                      | error                          | <ul> <li>&lt;12-bit modes</li> </ul> | _            | ±1.4              | ±2.1            |                  |                      |

| DNL                  | Differential non-<br>linearity | 12-bit modes                         |              | ±0.7              | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                    |

|                      |                                | • <12-bit modes                      | _            | ±0.2              | -0.3 to 0.5     |                  |                      |

| Table 26. | 16-bit ADC | characteristics | (V <sub>REFH</sub> = | V <sub>DDA</sub> , | $V_{REFL} = V_{2}$ | ssa) |

|-----------|------------|-----------------|----------------------|--------------------|--------------------|------|

|-----------|------------|-----------------|----------------------|--------------------|--------------------|------|

| Symbol             | Description                                         | Min.                  | Тур. | Max.            | Unit             |

|--------------------|-----------------------------------------------------|-----------------------|------|-----------------|------------------|

| $V_{DD}$           | Supply voltage                                      | 1.71                  | _    | 3.6             | V                |

| I <sub>DDHS</sub>  | Supply current, High-speed mode (EN=1, PMODE=1)     | —                     | _    | 200             | μA               |

| I <sub>DDLS</sub>  | Supply current, low-speed mode (EN=1, PMODE=0)      | —                     |      | 20              | μA               |

| V <sub>AIN</sub>   | Analog input voltage                                | $V_{SS} - 0.3$        |      | V <sub>DD</sub> | V                |

| V <sub>AIO</sub>   | Analog input offset voltage                         | —                     |      | 20              | mV               |

| V <sub>H</sub>     | Analog comparator hysteresis <sup>1</sup>           |                       |      |                 |                  |

|                    | • CR0[HYSTCTR] = 00                                 | —                     | 5    | _               | mV               |

|                    | • CR0[HYSTCTR] = 01                                 | —                     | 10   | _               | mV               |

|                    | • CR0[HYSTCTR] = 10                                 | —                     | 20   | _               | mV               |

|                    | • CR0[HYSTCTR] = 11                                 | —                     | 30   | _               | mV               |

| V <sub>CMPOh</sub> | Output high                                         | V <sub>DD</sub> – 0.5 |      |                 | V                |

| V <sub>CMPOI</sub> | Output low                                          | —                     |      | 0.5             | V                |

| t <sub>DHS</sub>   | Propagation delay, high-speed mode (EN=1, PMODE=1)  | 20                    | 50   | 200             | ns               |

| t <sub>DLS</sub>   | Propagation delay, low-speed mode (EN=1, PMODE=0)   | 80                    | 250  | 600             | ns               |

|                    | Analog comparator initialization delay <sup>2</sup> | _                     | _    | 40              | μs               |

| I <sub>DAC6b</sub> | 6-bit DAC current adder (enabled)                   | —                     | 7    | _               | μΑ               |

| INL                | 6-bit DAC integral non-linearity                    | -0.5                  | _    | 0.5             | LSB <sup>3</sup> |

| DNL                | 6-bit DAC differential non-linearity                | -0.3                  | _    | 0.3             | LSB              |

### 3.6.2 CMP and 6-bit DAC electrical specifications Table 27. Comparator and 6-bit DAC electrical specifications

1. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD}$ -0.6 V.

Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

3. 1 LSB = V<sub>reference</sub>/64

### 3.6.3.2 12-bit DAC operating behaviors Table 29. 12-bit DAC operating behaviors

| Symbol                     | Description                                                                            | Min.                      | Тур.     | Max.              | Unit   | Notes |

|----------------------------|----------------------------------------------------------------------------------------|---------------------------|----------|-------------------|--------|-------|

| I <sub>DDA_DACL</sub><br>P | Supply current — low-power mode                                                        |                           | —        | 250               | μΑ     |       |

| I <sub>DDA_DACH</sub><br>P | Supply current — high-speed mode                                                       | —                         | —        | 900               | μΑ     |       |

| t <sub>DACLP</sub>         | Full-scale settling time (0x080 to 0xF7F) — low-power mode                             | _                         | 100      | 200               | μs     | 1     |

| t <sub>DACHP</sub>         | Full-scale settling time (0x080 to 0xF7F) — high-power mode                            | —                         | 15       | 30                | μs     | 1     |

| t <sub>CCDACLP</sub>       | Code-to-code settling time (0xBF8 to<br>0xC08) — low-power mode and high-speed<br>mode | _                         | 0.7      | 1                 | μs     | 1     |

| V <sub>dacoutl</sub>       | DAC output voltage range low — high-<br>speed mode, no load, DAC set to 0x000          | _                         | —        | 100               | mV     |       |

| V <sub>dacouth</sub>       | DAC output voltage range high — high-<br>speed mode, no load, DAC set to 0xFFF         | V <sub>DACR</sub><br>-100 | —        | V <sub>DACR</sub> | mV     |       |

| INL                        | Integral non-linearity error — high speed mode                                         | —                         | —        | ±8                | LSB    | 2     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> > 2<br>V                          | —                         | —        | ±1                | LSB    | 3     |

| DNL                        | Differential non-linearity error — V <sub>DACR</sub> = VREF_OUT                        | _                         | —        | ±1                | LSB    | 4     |

| V <sub>OFFSET</sub>        | Offset error                                                                           | _                         | ±0.4     | ±0.8              | %FSR   | 5     |

| E <sub>G</sub>             | Gain error                                                                             | _                         | ±0.1     | ±0.6              | %FSR   | 5     |

| PSRR                       | Power supply rejection ratio, $V_{DDA} \ge 2.4 V$                                      | 60                        | —        | 90                | dB     |       |

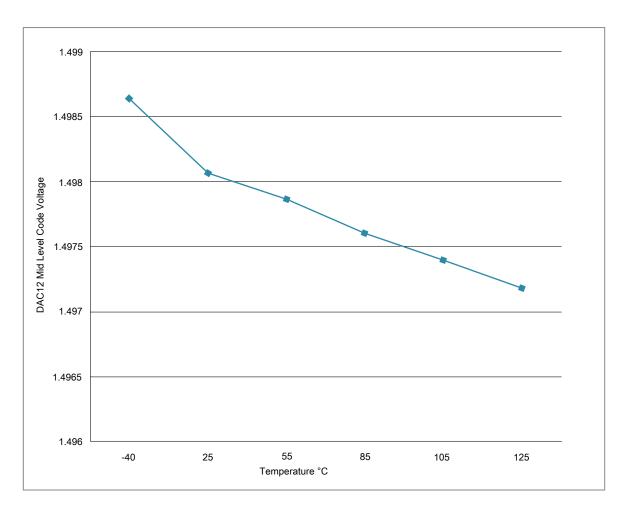

| T <sub>CO</sub>            | Temperature coefficient offset voltage                                                 | —                         | 3.7      | —                 | μV/C   | 6     |

| $T_{GE}$                   | Temperature coefficient gain error                                                     | —                         | 0.000421 | —                 | %FSR/C |       |

| Rop                        | Output resistance (load = $3 \text{ k}\Omega$ )                                        | —                         | —        | 250               | Ω      |       |

| SR                         | Slew rate -80h→ F7Fh→ 80h                                                              |                           |          |                   | V/µs   |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                       | 1.2                       | 1.7      | —                 |        |       |

|                            | <ul> <li>Low power (SP<sub>LP</sub>)</li> </ul>                                        | 0.05                      | 0.12     | —                 |        |       |

| BW                         | 3dB bandwidth                                                                          |                           |          |                   | kHz    |       |

|                            | <ul> <li>High power (SP<sub>HP</sub>)</li> </ul>                                       | 550                       |          | _                 |        |       |

|                            | • Low power (SP <sub>LP</sub> )                                                        | 40                        |          | _                 |        |       |

1. Settling within  $\pm 1$  LSB

2. The INL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV

3. The DNL is measured for 0 + 100 mV to  $V_{\text{DACR}}$  –100 mV

4. The DNL is measured for 0 + 100 mV to  $V_{DACR}$  –100 mV with  $V_{DDA}$  > 2.4 V 5. Calculated by a best fit curve from  $V_{SS}$  + 100 mV to  $V_{DACR}$  – 100 mV

6. V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

34

Figure 12. Offset at half scale vs. temperature

# 3.7 Timers

See General switching specifications.

# 3.8 Communication interfaces

## 3.8.1 USB electrical specifications

The USB electricals for the USB On-the-Go module conform to the standards documented by the Universal Serial Bus Implementers Forum. For the most up-to-date standards, visit **usb.org**.

| Num. | Symbol          | Description                   | Min. | Max.                     | Unit | Note |

|------|-----------------|-------------------------------|------|--------------------------|------|------|

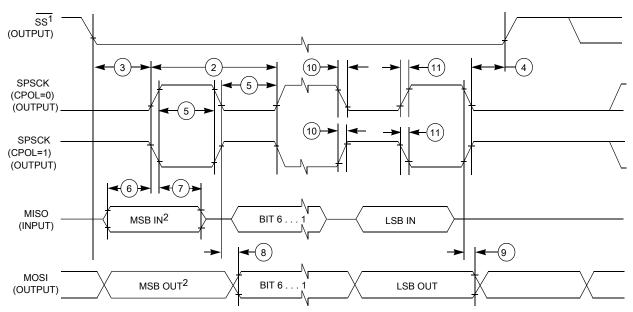

| 8    | t <sub>v</sub>  | Data valid (after SPSCK edge) | —    | 52                       | ns   | —    |

| 9    | t <sub>HO</sub> | Data hold time (outputs)      | 0    | —                        | ns   | —    |

| 10   | t <sub>RI</sub> | Rise time input               | —    | t <sub>periph</sub> - 25 | ns   | —    |

|      | t <sub>FI</sub> | Fall time input               |      |                          |      |      |

| 11   | t <sub>RO</sub> | Rise time output              | —    | 36                       | ns   | —    |

|      | t <sub>FO</sub> | Fall time output              |      |                          |      |      |

Table 32. SPI master mode timing on slew rate enabled pads (continued)

- 1. For SPI0  $f_{periph}$  is the bus clock ( $f_{BUS}$ ). For SPI1  $f_{periph}$  is the system clock ( $f_{SYS}$ ).

- 2.  $t_{periph} = 1/f_{periph}$

1. If configured as an output.

2. LSBF = 0. For LSBF = 1, bit order is LSB, bit 1, ..., bit 6, MSB.

#### Figure 13. SPI master mode timing (CPHA = 0)

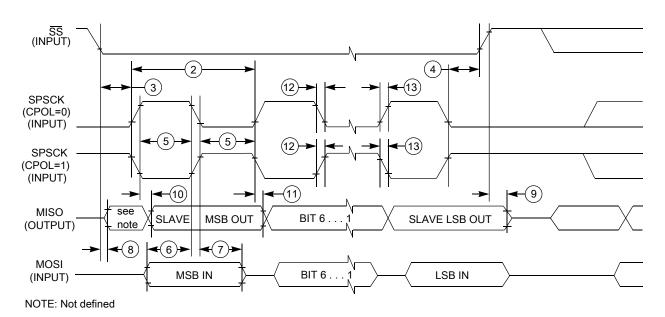

Figure 16. SPI slave mode timing (CPHA = 1)

### 3.8.4 Inter-Integrated Circuit Interface (I2C) timing Table 35. I2C timing

| Characteristic                                                                                     | Symbol                | Standa           | rd Mode           | Fast                               | Mode             | Unit |

|----------------------------------------------------------------------------------------------------|-----------------------|------------------|-------------------|------------------------------------|------------------|------|

|                                                                                                    |                       | Minimum          | Maximum           | Minimum                            | Maximum          |      |

| SCL Clock Frequency                                                                                | f <sub>SCL</sub>      | 0                | 100               | 0                                  | 400 <sup>1</sup> | kHz  |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. | t <sub>HD</sub> ; STA | 4                | _                 | 0.6                                | —                | μs   |

| LOW period of the SCL clock                                                                        | t <sub>LOW</sub>      | 4.7              | —                 | 1.3                                | —                | μs   |

| HIGH period of the SCL clock                                                                       | t <sub>HIGH</sub>     | 4                | —                 | 0.6                                | —                | μs   |

| Set-up time for a repeated START condition                                                         | t <sub>SU</sub> ; STA | 4.7              | _                 | 0.6                                | —                | μs   |

| Data hold time for I <sup>2</sup> C bus devices                                                    | t <sub>HD</sub> ; DAT | 0 <sup>2</sup>   | 3.45 <sup>3</sup> | 04                                 | 0.9 <sup>2</sup> | μs   |

| Data set-up time                                                                                   | t <sub>SU</sub> ; DAT | 250 <sup>5</sup> | —                 | 100 <sup>3</sup> , <sup>6</sup>    | —                | ns   |

| Rise time of SDA and SCL signals                                                                   | t <sub>r</sub>        | _                | 1000              | 20 +0.1C <sub>b</sub> <sup>7</sup> | 300              | ns   |

| Fall time of SDA and SCL signals                                                                   | t <sub>f</sub>        | _                | 300               | 20 +0.1C <sub>b</sub> <sup>6</sup> | 300              | ns   |

| Set-up time for STOP condition                                                                     | t <sub>SU</sub> ; STO | 4                | _                 | 0.6                                | _                | μs   |

| Bus free time between STOP and<br>START condition                                                  | t <sub>BUF</sub>      | 4.7              | _                 | 1.3                                | —                | μs   |

| Pulse width of spikes that must be<br>suppressed by the input filter                               | t <sub>SP</sub>       | N/A              | N/A               | 0                                  | 50               | ns   |

1. The maximum SCL Clock Frequency in Fast mode with maximum bus loading can only achieved when using the High drive pins (see Voltage and current operating behaviors) or when using the Normal drive pins and VDD ≥ 2.7 V

| Symbol    | Description                                                                        | Min. | Тур. | Max. | Unit |

|-----------|------------------------------------------------------------------------------------|------|------|------|------|

| TSI_RUNV  | Variable power consumption in run mode (depends on oscillator's current selection) | 1.0  |      | 128  | μA   |

| TSI_EN    | Power consumption in enable mode                                                   | —    | 100  | _    | μA   |

| TSI_DIS   | Power consumption in disable mode                                                  | —    | 1.2  | _    | μA   |

| TSI_TEN   | TSI analog enable time                                                             | —    | 66   | _    | μs   |

| TSI_CREF  | TSI reference capacitor                                                            | —    | 1.0  | _    | pF   |

| TSI_DVOLT | Voltage variation of VP & VM around nominal values                                 | 0.19 |      | 1.03 | V    |

#### Table 40. TSI electrical specifications (continued)

# 4 Dimensions

## 4.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to **freescale.com** and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |  |

|------------------------------------------|-------------------------------|--|

| 32-pin QFN                               | 98ASA00473D                   |  |

| 48-pin QFN                               | 98ASA00466D                   |  |

| 64-pin LQFP                              | 98ASS23234W                   |  |

# 5 Pinout

# 5.1 KL26 Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Control Module is responsible for selecting which ALT functionality is available on each pin.

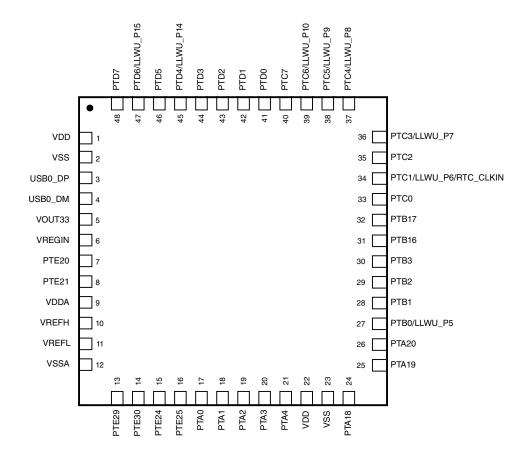

Figure 23. KL26 48-pin QFN pinout diagram

## 7.1 Description

Part numbers for the chip have fields that identify the specific part. You can use the values of these fields to determine the specific part you have received.

## 7.2 Format

Part numbers for this device have the following format:

Q KL## A FFF R T PP CC N

## 7.3 Fields

This table lists the possible values for each field in the part number (not all combinations are valid):

| Field | Description                 | Values                                                                                                                 |

|-------|-----------------------------|------------------------------------------------------------------------------------------------------------------------|

| Q     | Qualification status        | <ul> <li>M = Fully qualified, general market flow</li> <li>P = Prequalification</li> </ul>                             |

| KL##  | Kinetis family              | • KL26                                                                                                                 |

| A     | Key attribute               | • Z = Cortex-M0+                                                                                                       |

| FFF   | Program flash memory size   | <ul> <li>32 = 32 KB</li> <li>64 = 64 KB</li> <li>128 = 128 KB</li> </ul>                                               |

| R     | Silicon revision            | <ul> <li>(Blank) = Main</li> <li>A = Revision after main</li> </ul>                                                    |

| Т     | Temperature range (°C)      | • V = -40 to 105                                                                                                       |

| PP    | Package identifier          | <ul> <li>FM = 32 QFN (5 mm x 5 mm)</li> <li>FT = 48 QFN (7 mm x 7 mm)</li> <li>LH = 64 LQFP (10 mm x 10 mm)</li> </ul> |

| CC    | Maximum CPU frequency (MHz) | • 4 = 48 MHz                                                                                                           |

| N     | Packaging type              | R = Tape and reel                                                                                                      |

# 7.4 Example

This is an example part number:

MKL26Z128VFM4