# E·XFL

# XMOS - XS1-A8A-64-FB96-C5 Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | XCore                                                        |

| Core Size                  | 32-Bit 8-Core                                                |

| Speed                      | 500MIPS                                                      |

| Connectivity               | Configurable                                                 |

| Peripherals                |                                                              |

| Number of I/O              | 42                                                           |

| Program Memory Size        | 64KB (16K x 32)                                              |

| Program Memory Type        | SRAM                                                         |

| EEPROM Size                | -                                                            |

| RAM Size                   | -                                                            |

| Voltage - Supply (Vcc/Vdd) | 0.90V ~ 5.5V                                                 |

| Data Converters            | A/D 4x12b                                                    |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | 0°C ~ 70°C (TA)                                              |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 96-LFBGA                                                     |

| Supplier Device Package    | 96-FBGA (10x10)                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/xmos/xs1-a8a-64-fb96-c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

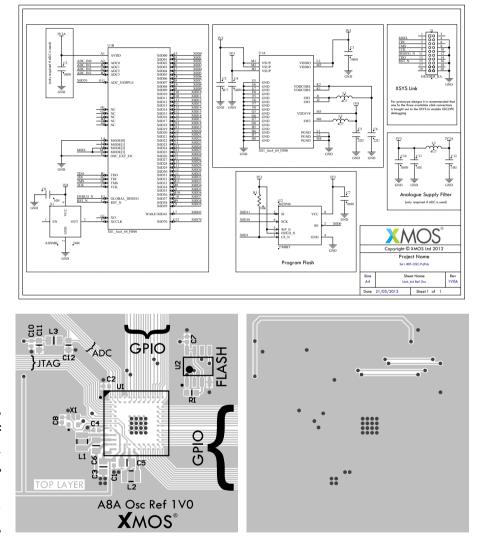

- Channels and channel ends Tasks running on logical cores communicate using channels formed between two channel ends. Data can be passed synchronously or asynchronously between the channel ends assigned to the communicating tasks. Section 7.5

- xCONNECT Switch and Links Between tiles, channel communications are implemented over a high performance network of xCONNECT Links and routed through a hardware xCONNECT Switch. Section 7.6

- Ports The I/O pins are connected to the processing cores by Hardware Response ports. The port logic can drive its pins high and low, or it can sample the value on its pins optionally waiting for a particular condition. Section 7.3

- Clock blocks xCORE devices include a set of programmable clock blocks that can be used to govern the rate at which ports execute. Section 7.4

- Memory Each xCORE Tile integrates a bank of SRAM for instructions and data, and a block of one-time programmable (OTP) memory that can be configured for system wide security features. Section 10

- PLL The PLL is used to create a high-speed processor clock given a low speed external oscillator. Section 8

- JTAG The JTAG module can be used for loading programs, boundary scan testing, in-circuit source-level debugging and programming the OTP memory. Section 14

#### 1.1 Software

Devices are programmed using C, C++ or xC (C with multicore extensions). XMOS provides tested and proven software libraries, which allow you to quickly add interface and processor functionality such as USB, Ethernet, PWM, graphics driver, and audio EQ to your applications.

#### 1.2 xTIMEcomposer Studio

The xTIMEcomposer Studio development environment provides all the tools you need to write and debug your programs, profile your application, and write images into flash memory or OTP memory on the device. Because xCORE devices operate deterministically, they can be simulated like hardware within xTIMEcomposer: uniquely in the embedded world, xTIMEcomposer Studio therefore includes a static timing analyzer, cycle-accurate simulator, and high-speed in-circuit instrumentation.

xTIMEcomposer can be driven from either a graphical development environment, or the command line. The tools are supported on Windows, Linux and MacOS X and available at no cost from xmos.com/downloads. Information on using the tools is provided in the xTIMEcomposer User Guide, X3766.

$-X \wedge () >$

# 4 Signal Description

This section lists the signals and I/O pins available on the XS1-A8A-64-FB96. The device provides a combination of 1 bit, 4bit, 8bit and 16bit ports, as well as wider ports that are fully or partially (gray) bonded out. All pins of a port provide either output or input, but signals in different directions cannot be mapped onto the same port.

Pins may have one or more of the following properties:

PD/PU: The IO pin a weak pull-down or pull-up resistor. On GPIO pins this resistor can be enabled.

| Power pins (9) |                               |      |            |  |  |

|----------------|-------------------------------|------|------------|--|--|

| Signal         | Function                      | Туре | Properties |  |  |

| AVSS           | Digital ground                | GND  |            |  |  |

| GND            | Digital ground                | GND  |            |  |  |

| PGND           | Power ground                  | GND  |            |  |  |

| SW1            | DCDC1 switched output voltage | PWR  |            |  |  |

| SW2            | DCDC2 switched output voltage | PWR  |            |  |  |

| VDD1V8         | 1v8 voltage supply            | PWR  |            |  |  |

| VDDCORE        | Core voltage supply           | PWR  |            |  |  |

| VDDIO          | Digital I/O power             | PWR  |            |  |  |

| VSUP           | Power supply (3V3/5V0)        | PWR  |            |  |  |

ST: The IO pin has a Schmitt Trigger on its input.

| Analog pins (6) |                              |       |            |  |

|-----------------|------------------------------|-------|------------|--|

| Signal          | Function                     | Туре  | Properties |  |

| ADC0            | Analog input                 | Input |            |  |

| ADC1            | Analog input                 | Input |            |  |

| ADC2            | Analog input                 | Input |            |  |

| ADC3            | Analog input                 | Input |            |  |

| ADC_SAMPLE      | Sample Analog input          | I/O   |            |  |

| AVDD            | Supply and reference voltage | PWR   |            |  |

| Clocks pins (4) |                                |        |            |  |  |

|-----------------|--------------------------------|--------|------------|--|--|

| Signal          | Function                       | Туре   | Properties |  |  |

| MODE[3:0]       | Boot mode select               | Input  | PU, ST     |  |  |

| OSC_EXT_N       | Use Silicon Oscillator         | Input  | ST         |  |  |

| XI/CLK          | Crystal Oscillator/Clock Input | Input  |            |  |  |

| хо              | Crystal Oscillator Output      | Output |            |  |  |

-XMOS

# 17 DC and Switching Characteristics

| Symbol | Parameter                                     | MIN  | TYP  | MAX  | UNITS | Notes |

|--------|-----------------------------------------------|------|------|------|-------|-------|

| VSUP   | Power Supply (3.3V Mode)                      | 3.00 | 3.30 | 3.60 | V     |       |

| V301   | Power Supply (5V Mode)                        | 4.50 | 5.00 | 5.50 | V     |       |

| VDDIO  | I/O supply voltage                            | 3.00 | 3.30 | 3.60 | V     |       |

| AVDD   | Analog Supply and Reference<br>Voltage        | 3.00 | 3.30 | 3.60 | V     |       |

| Cl     | xCORE Tile I/O load capacitance               |      |      | 25   | pF    |       |

| Та     | Ambient operating temperature<br>(Commercial) | 0    |      | 70   | °C    |       |

|        | Ambient operating temperature<br>(Industrial) | -40  |      | 85   | °C    |       |

| Tj     | Junction temperature                          |      |      | 125  | °C    |       |

| Tstg   | Storage temperature                           | -65  |      | 150  | °C    |       |

# 17.1 Operating Conditions

Figure 24: Operating conditions

# 17.2 DC1 Characteristics

| Symbol    | Parameter                           | MIN  | ТҮР  | MAX  | UNITS     | Notes |

|-----------|-------------------------------------|------|------|------|-----------|-------|

| VDDCORE   | Tile Supply Voltage                 | 0.90 | 1.00 | 1.10 | V         |       |

| V(RIPPLE) | Ripple Voltage (peak to peak)       |      | 10   | 40   | mV        |       |

| V(ACC)    | Voltage Accuracy                    | -5   |      | 5    | %         | А     |

| F(S)      | Switching Frequency                 |      | 1    |      | MHz       |       |

| F(SVAR)   | Variation in Switching<br>Frequency | -10  |      | 10   | %         |       |

| Effic     | Efficiency                          |      | 80   |      | %         |       |

| PGT(HIGH) | Powergood Threshold<br>(High)       |      | 95   |      | %/VDDCORE |       |

| PGT(LOW)  | Powergood Threshold<br>(Low)        |      | 80   |      | %/VDDCORE |       |

-XMOS<sup>®</sup>

Figure 25: DC1 characteristics

A If supplied externally.

| Symbol    | Parameter                           | MIN | ТҮР  | MAX | UNITS    | Notes |

|-----------|-------------------------------------|-----|------|-----|----------|-------|

| VDD1V8    | 1V8 Supply Voltage                  |     | 1.80 |     | V        |       |

| V(RIPPLE) | Ripple Voltage (peak to peak)       |     | 10   | 40  | mV       |       |

| V(ACC)    | Voltage Accuracy                    | -5  |      | 5   | %        | A     |

| F(S)      | Switching Frequency                 |     | 1    |     | MHz      |       |

| F(SVAR)   | Variation in Switching<br>Frequency | -10 |      | 10  | %        |       |

| Effic     | Efficiency                          |     | 80   |     | %        |       |

| PGT(HIGH) | Powergood Threshold<br>(High)       |     | 95   |     | %/VDD1V8 |       |

| PGT(LOW)  | Powergood Threshold<br>(Low)        |     | 80   |     | %/VDD1V8 |       |

## 17.3 DC2 Characteristics

Figure 26: DC2 characteristics

A If supplied externally.

# 17.4 ADC Characteristics

| Symbol    | Parameter                     | MIN | TYP | MAX  | UNITS  | Notes |

|-----------|-------------------------------|-----|-----|------|--------|-------|

| Ν         | Resolution                    |     | 12  |      | bits   |       |

| Fs        | Conversion Speed              |     |     | 1    | MSPS   |       |

| Nch       | Number of Channels            |     | 4   |      |        |       |

| Vin       | Input Range                   | 0   |     | AVDD | V      |       |

| DNL       | Differential Non Linearity    | -1  |     | 1.5  | LSB    |       |

| INL       | Integral Non Linearity        | -4  |     | 4    | LSB    |       |

| E(GAIN)   | Gain Error                    | -10 |     | 10   | LSB    |       |

| E(OFFSET) | Offset Error                  | -3  |     | 3    | mV     |       |

| T(PWRUP)  | Power time for ADC Clock Fclk |     |     | 7    | 1/Fclk |       |

| ENOB      | Effective Number of bits      |     | 10  |      |        |       |

-XMOS®

Figure 27: ADC characteristics

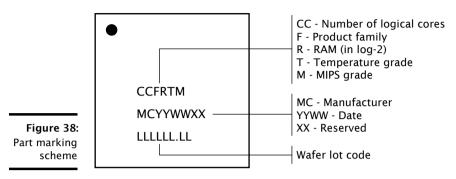

## 18.1 Part Marking

# 19 Ordering Information

|              | Product Code       | Marking | Qualification | Speed Grade |

|--------------|--------------------|---------|---------------|-------------|

|              | XS1-A8A-64-FB96-C5 | 8A6C5   | Commercial    | 500 MIPS    |

| Figure 39:   | XS1-A8A-64-FB96-I5 | 8A6I5   | Industrial    | 500 MIPS    |

| Orderable    | XS1-A8A-64-FB96-C4 | 8A6C4   | Commercial    | 400 MIPS    |

| part numbers | XS1-A8A-64-FB96-I4 | 8A6I4   | Industrial    | 400 MIPS    |

The response to the read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.3 Accessing digital and analogue node configuration registers

Node configuration registers can be accessed through the interconnect using the functions write\_node\_config\_reg(device, ...) and read\_node\_config\_reg(device, ...), where device is the name of the node. These functions implement the protocols described below.

Instead of using the functions above, a channel-end can be allocated to communicate with the node configuration registers. The destination of the channel-end should be set to OxnnnnC30C where nnnn is the node-identifier.

A write message comprises the following:

| control-token | 24-bit response        | 16-bit          | 32-bit | control-token |

|---------------|------------------------|-----------------|--------|---------------|

| 192           | channel-end identifier | register number | data   | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| control-token | 24-bit response        | 16-bit          | control-token |

|---------------|------------------------|-----------------|---------------|

| 193           | channel-end identifier | register number | 1             |

The response to a read message comprises either control token 3, 32-bit of data, and control-token 1 (for success), or control tokens 4 and 1 (for failure).

#### A.4 Accessing a register of an analogue peripheral

Peripheral registers can be accessed through the interconnect using the functions write\_periph\_32(device, peripheral, ...), read\_periph\_32(device, peripheral, ...)  $\leftrightarrow$ , write\_periph\_8(device, peripheral, ...), and read\_periph\_8(device, peripheral  $\leftrightarrow$ , ...); where device is the name of the analogue device, and peripheral is the number of the peripheral. These functions implement the protocols described below.

A channel-end should be allocated to communicate with the configuration registers. The destination of the channel-end should be set to 0xnnnnpp02 where nnnn is the node-identifier and pp is the peripheral identifier.

A write message comprises the following:

| control-token | 24-bit response        | 8-bit           | 8-bit | data | control-token |

|---------------|------------------------|-----------------|-------|------|---------------|

| 36            | channel-end identifier | register number | size  |      | 1             |

The response to a write message comprises either control tokens 3 and 1 (for success), or control tokens 4 and 1 (for failure).

A read message comprises the following:

| Bits  | Perm | Init | Description                                                                                                                                                                                                                                       |

|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:18 | RO   | -    | Reserved                                                                                                                                                                                                                                          |

| 17:16 | DRW  |      | If the debug interrupt was caused by a hardware breakpoint<br>or hardware watchpoint, this field contains the number of the<br>breakpoint or watchpoint. If multiple breakpoints or watch-<br>points trigger at once, the lowest number is taken. |

| 15:8  | DRW  |      | If the debug interrupt was caused by a logical core, this field<br>contains the number of that core. Otherwise this field is 0.                                                                                                                   |

| 7:3   | RO   | -    | Reserved                                                                                                                                                                                                                                          |

| 2:0   | DRW  | 0    | Indicates the cause of the debug interrupt<br>1: Host initiated a debug interrupt through JTAG<br>2: Program executed a DCALL instruction<br>3: Instruction breakpoint<br>4: Data watch point<br>5: Resource watch point                          |

**0x15:** Debug interrupt type

## B.17 Debug interrupt data: 0x16

On a data watchpoint, this register contains the effective address of the memory operation that triggered the debugger. On a resource watchpoint, it countains the resource identifier.

0x16 Debug interrupt data

| <b>0x16:</b><br>Debug | Bits | Perm | Init | Description |

|-----------------------|------|------|------|-------------|

| t data                | 31:0 | DRW  |      | Value.      |

## B.18 Debug core control: 0x18

This register enables the debugger to temporarily disable logical cores. When returning from the debug interrupts, the cores set in this register will not execute. This enables single stepping to be implemented.

**0x18:** Debug core control

| Bits | Perm | Init | Description                                                                                                                                                   |

|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:8 | RO   | -    | Reserved                                                                                                                                                      |

| 7:0  | DRW  |      | 1-hot vector defining which logical cores are stopped when not<br>in debug mode. Every bit which is set prevents the respective<br>logical core from running. |

# C xCORE Tile Configuration

The xCORE Tile control registers can be accessed using configuration reads and writes (use write\_tile\_config\_reg(tileref, ...) and read\_tile\_config\_reg(tileref,  $\rightarrow$  ...) for reads and writes).

| Number    | Perm | Description                                    |

|-----------|------|------------------------------------------------|

| 0x00      | RO   | Device identification                          |

| 0x01      | RO   | xCORE Tile description 1                       |

| 0x02      | RO   | xCORE Tile description 2                       |

| 0x04      | CRW  | Control PSwitch permissions to debug registers |

| 0x05      | CRW  | Cause debug interrupts                         |

| 0x06      | RW   | xCORE Tile clock divider                       |

| 0x07      | RO   | Security configuration                         |

| 0x10 0x13 | RO   | PLink status                                   |

| 0x20 0x27 | CRW  | Debug scratch                                  |

| 0x40      | RO   | PC of logical core 0                           |

| 0x41      | RO   | PC of logical core 1                           |

| 0x42      | RO   | PC of logical core 2                           |

| 0x43      | RO   | PC of logical core 3                           |

| 0x44      | RO   | PC of logical core 4                           |

| 0x45      | RO   | PC of logical core 5                           |

| 0x46      | RO   | PC of logical core 6                           |

| 0x47      | RO   | PC of logical core 7                           |

| 0x60      | RO   | SR of logical core 0                           |

| 0x61      | RO   | SR of logical core 1                           |

| 0x62      | RO   | SR of logical core 2                           |

| 0x63      | RO   | SR of logical core 3                           |

| 0x64      | RO   | SR of logical core 4                           |

| 0x65      | RO   | SR of logical core 5                           |

| 0x66      | RO   | SR of logical core 6                           |

| 0x67      | RO   | SR of logical core 7                           |

| 0x80 0x9F | RO   | Chanend status                                 |

-XMOS

Figure 42: Summary Bits

31:0

Bits

31:0

## C.16 PC of logical core 6: 0x46

**0x46:** PC of logical core 6

Perm

Init

Description

RO

Value.

#### C.17 PC of logical core 7: 0x47

0x47: PC of logical core 7

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

## C.18 SR of logical core 0: 0x60

Value of the SR of logical core 0

**0x60:** SR of logical core 0

| Perm | Init | Description |

|------|------|-------------|

| RO   |      | Value.      |

## C.19 SR of logical core 1: 0x61

**0x61:** SR of logical core 1

| 51:<br>cal | Bits | Perm | Init | Description |

|------------|------|------|------|-------------|

| 21         | 31:0 | RO   |      | Value.      |

## C.20 SR of logical core 2: 0x62

**0x62:** SR of logical core 2

| Bits | Perm | Init | Description |

|------|------|------|-------------|

| 31:0 | RO   |      | Value.      |

-**X**M(

#### C.21 SR of logical core 3: 0x63

Ox63: SR of logical core 3

Bits

Perm

Init

Description

31:0

RO

Value.

#### C.22 SR of logical core 4: 0x64

Ox64:<br/>SR of logical<br/>core 4BitsPermInitDescription31:0ROValue.

## C.23 SR of logical core 5: 0x65

| 0x65:         |      |      |      |             |

|---------------|------|------|------|-------------|

| SR of logical | Bits | Perm | Init | Description |

| core 5        | 31:0 | RO   |      | Value.      |

#### C.24 SR of logical core 6: 0x66

**0x66:** SR of logical core 6

Bits

31:0

| Perm | Init | Description |

|------|------|-------------|

| RO   |      | Value.      |

## C.25 SR of logical core 7: 0x67

| 0x67:         |      |      |      |             |

|---------------|------|------|------|-------------|

| SR of logical | Bits | Perm | Init | Description |

| core 7        | 31:0 | RO   |      | Value.      |

## C.26 Chanend status: 0x80 .. 0x9F

These registers record the status of each channel-end on the tile.

-XMOS

| Bits  | Perm | Init | Description                                                                                                    |  |

|-------|------|------|----------------------------------------------------------------------------------------------------------------|--|

| 31:26 | RO   | -    | Reserved                                                                                                       |  |

| 25:24 | RO   |      | 00 - ChannelEnd, 01 - ERROR, 10 - PSCTL, 11 - Idle.                                                            |  |

| 23:16 | RO   |      | Based on SRC_TARGET_TYPE value, it represents channelEnd ID or Idle status.                                    |  |

| 15:6  | RO   | -    | Reserved                                                                                                       |  |

| 5:4   | RO   |      | Two-bit network identifier                                                                                     |  |

| 3     | RO   | -    | Reserved                                                                                                       |  |

| 2     | RO   |      | 1 when the current packet is considered junk and will be thrown away.                                          |  |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                 |  |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch. |  |

**0x80 .. 0x9F:** Chanend status

#### D.11 Debug source: 0x1F

Contains the source of the most recent debug event.

| Bits | Perm | Init | Description                                                                        |

|------|------|------|------------------------------------------------------------------------------------|

| 31:5 | RO   | -    | Reserved                                                                           |

| 4    | RW   |      | If set, the external DEBUG_N pin is the source of the most recent debug interrupt. |

| 3:1  | RO   | -    | Reserved                                                                           |

| 0    | RW   |      | If set, the xCORE Tile is the source of the most recent debug interrupt.           |

0x1F: Debug source

## D.12 Link status, direction, and network: 0x20 .. 0x27

These registers contain status information for low level debugging (read-only), the network number that each link belongs to, and the direction that each link is part of. The registers control links C, D, A, B, G, H, E, and F in that order.

| Bits  | Perm | Init | Description                                                                                                                                                                              |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:26 | RO   | -    | Reserved                                                                                                                                                                                 |

| 25:24 | RO   |      | If this link is currently routing data into the switch, this field<br>specifies the type of link that the data is routed to:<br>0: plink<br>1: external link<br>2: internal control link |

| 23:16 | RO   | 0    | If the link is routing data into the switch, this field specifies the destination link number to which all tokens are sent.                                                              |

| 15:12 | RO   | -    | Reserved                                                                                                                                                                                 |

| 11:8  | RW   | 0    | The direction that this this link is associated with; set for rout-<br>ing.                                                                                                              |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                                 |

| 5:4   | RW   | 0    | Determines the network to which this link belongs, set for quality of service.                                                                                                           |

| 3     | RO   | -    | Reserved                                                                                                                                                                                 |

| 2     | RO   | 0    | Set to 1 if the current packet is junk and being thrown away. A packet is considered junk if, for example, it is not routable.                                                           |

| 1     | RO   | 0    | Set to 1 if the switch is routing data into the link, and if a route exists from another link.                                                                                           |

| 0     | RO   | 0    | Set to 1 if the link is routing data into the switch, and if a route is created to another link on the switch.                                                                           |

-XMOS

**0x20 .. 0x27** Link status, direction, and network

|                                           | Bits  | Perm | Init | Description                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------|-------|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | 31:25 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                                                |

|                                           | 24    | RW   |      | Tristate processor mode pins.                                                                                                                                                                                                                                                                                                           |

|                                           | 23:18 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                                                |

|                                           | 17:16 | RW   |      | Processor mode pins.                                                                                                                                                                                                                                                                                                                    |

|                                           | 15:2  | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                                                |

| <b>0x50:</b><br>Reset and<br>Mode Control | 1     | WO   | 0    | xCORE Tile reset. Set to 1 to initiate a reset of the xCORE Tile.<br>This bit is self clearing. A write to this configuration register<br>with this bit asserted results in no response packet being sent<br>to the sender regardless of whether or not a response was<br>requested.                                                    |

|                                           | 0     | WO   | 0    | System reset. Set to 1 to initiate a reset whose scope includes<br>most configuration and peripheral control registers. This bit is<br>self clearing. A write to this configuration register with this bit<br>asserted results in no response packet being sent to the sender<br>regardless of whether or not a response was requested. |

# E.5 System clock frequency: 0x51

| Bits | Perm | Init | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:7 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6:0  | RW   | 25   | Oscillator clock frequency in MHz rounded up to the nearest<br>integer value. Only values between 5 and 100 MHz are valid -<br>writes outside this range are ignored and will be NACKed.<br>This field must be set on start up of the device and any time that<br>the input oscillator clock frequency is changed. It must contain<br>the system clock frequency in MHz rounded up to the nearest<br>integer value. The following functions depend on the correct<br>frequency settings:<br>* Processor reset delay<br>* The watchdog clock<br>* The real-time clock when running in sleep mode |

-XMOS<sup>®</sup>

0x51: System clock frequency

| Bits  | Perm | Init | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|-------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:25 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 24    | RO   | 1    | Indicates that an ADC sample has been dropped. This bit is cleared on a read.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 23:18 | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 17:16 | RW   | 1    | <ul> <li>Number of bits per ADC sample. The ADC values are always left aligned:</li> <li>0: 8 bits samples - the least significant four bits of each sample are discarded.</li> <li>1: 16 bits samples - the sample is padded with four zero bits in bits 30. The most significant byte is transmitted first.</li> <li>2: reserved</li> <li>3: 32 bits samples - the sample is padded with 20 zero bits in bits 190. The most significant byte is transmitted first, hence the word can be input with a single 32-bit IN instruction.</li> </ul> |  |

| 15:8  | RW   | 1    | Number of samples to be transmitted per packet. The value 0 indicates that the packet will not be terminated until interrupted by an ADC control register access.                                                                                                                                                                                                                                                                                                                                                                                |  |

| 7:2   | RO   | -    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 1     | RW   | 0    | Set to 1 to switch the ADC to sample a 0.8V signal rather than<br>the external voltage. This can be used to calibrate the ADC.<br>When switching to and from calibration mode, one sample<br>value should be discarded. If a sample value x is measured<br>in calibration mode, then a scale factor $800000/x$ can be used<br>to translate subsequent measurements into microvolts (using<br>integer arithmetic).                                                                                                                                |  |

| 0     | RW   | 0    | Set to 1 to enable the ADC. Note that when enabled, the ADC control registers above are read-only. The ADC must be disabled whilst setting up the per-input-pin control. On enabling the ADC, six pulses must be generated to calibrate the ADC. These pulses will not generate packets on the selected channel-end. The seventh and further pulses will deliver samples to the selected channel-end. These six pulses have to be issued every time that this bit is changed from 0 to 1.                                                        |  |

0x20: ADC General Control

# G Deep sleep memory Configuration

This peripheral contains a 128 byte RAM that retains state whilst the main processor is put to sleep.

The *Deep sleep memory* is peripheral 3. The control registers are accessed using 8-bit reads and writes (use write\_periph\_8(device, 3, ...) and read\_periph\_8 ↔ (device, 3, ...) for reads and writes).

-XMOS"-

# I Real time clock Configuration

The *Real time clock* is peripheral 5. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 5, ...) and read\_periph\_32(device,  $\rightarrow$  5, ...) for reads and writes).

|            | Number | Perm | Description                                 |

|------------|--------|------|---------------------------------------------|

| Figure 48: | 0x00   | RW   | Real time counter least significant 32 bits |

| Summary    | 0x04   | RW   | Real time counter most significant 32 bits  |

#### I.1 Real time counter least significant 32 bits: 0x00

This registers contains the lower 32-bits of the real-time counter.

| <b>0x00:</b><br>Real time<br>counter least |      |      |      |                                                 |  |

|--------------------------------------------|------|------|------|-------------------------------------------------|--|

| significant 32<br>bits                     | Bits | Perm | Init | Description                                     |  |

|                                            | 31:0 | RO   | 0    | Least significant 32 bits of real-time counter. |  |

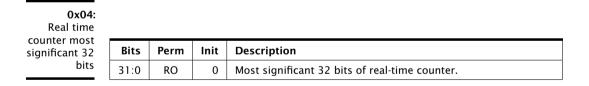

#### I.2 Real time counter most significant 32 bits: 0x04

This registers contains the upper 32-bits of the real-time counter.

# J Power control block Configuration

The *Power control block* is peripheral 6. The control registers are accessed using 32-bit reads and writes (use write\_periph\_32(device, 6, ...) and read\_periph\_32(  $\hookrightarrow$  device, 6, ...) for reads and writes).

#### J.5 Power supply states whilst WAKING1: 0x10

This register controls what state the power control block should be in when in the WAKING1 state. It also defines the minimum time that the system shall stay in this state. When the minimum time is expired, the next state is entered if all enabled power supplies are good.

| Bits  | Perm | Init | Description                                                                                                                                    |  |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:21 | RO   | -    | Reserved                                                                                                                                       |  |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state:<br>0: 1 clock cycles<br>1: 2 clock cycles<br>2: 4 clock cycles<br><br>31: 2147483648 clock cycles |  |

| 15    | RO   | -    | Reserved                                                                                                                                       |  |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                                   |  |

| 13:10 | RO   | -    | Reserved                                                                                                                                       |  |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                                              |  |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                                              |  |

| 7:6   | RO   | -    | Reserved                                                                                                                                       |  |

| 5     | RW   | 1    | Set to 1 to enable VOUT6 (IO supply).                                                                                                          |  |

| 4     | RW   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                                     |  |

| 3:2   | RO   | -    | Reserved                                                                                                                                       |  |

| 1     | RO   | 0    | Set to 1 to enable DCDC2 (analogue supply).                                                                                                    |  |

| 0     | RW   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                                        |  |

**0x10:** Power supply states whilst WAKING1

## J.6 Power supply states whilst WAKING2: 0x14

-XMOS-

This register controls what state the power control block should be in when in the WAKING2 state. It also defines the minimum time that the system shall stay in this state. When the minimum time is expired, the next state is entered if all enabled power supplies are good.

| Bits  | Perm | Init | Description                                                                                                                                    |  |

|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:21 | RO   | -    | Reserved                                                                                                                                       |  |

| 20:16 | RW   | 16   | Log2 number of cycles to stay in this state:<br>0: 1 clock cycles<br>1: 2 clock cycles<br>2: 4 clock cycles<br><br>31: 2147483648 clock cycles |  |

| 15    | RO   | -    | Reserved                                                                                                                                       |  |

| 14    | RW   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                                   |  |

| 13:10 | RO   | -    | Reserved                                                                                                                                       |  |

| 9     | RW   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                                              |  |

| 8     | RW   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                                              |  |

| 7:6   | RO   | -    | Reserved                                                                                                                                       |  |

| 5     | RW   | 1    | Set to 1 to enable VOUT6 (IO supply).                                                                                                          |  |

| 4     | RW   | 1    | Set to 1 to enable LDO5 (core PLL supply).                                                                                                     |  |

| 3:2   | RO   | -    | Reserved                                                                                                                                       |  |

| 1     | RO   | 1    | Set to 1 to enable DCDC2 (analogue supply).                                                                                                    |  |

| 0     | RW   | 1    | Set to 1 to enable DCDC1 (core supply).                                                                                                        |  |

0x14: Power supply states whilst WAKING2

# J.7 Power supply states whilst AWAKE: 0x18

This register controls what state the power control block should be in when in the AWAKE state.

-XMOS<sup>®</sup>

| Bits  | Perm | Init | Description                                                                                                                                                             |  |

|-------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31:30 | RO   | -    | Reserved                                                                                                                                                                |  |

| 29    | RO   | 0    | 1 if VOUT6 was enabled in the previous state.                                                                                                                           |  |

| 28    | RO   | 0    | 1 if LDO5 was enabled in the previous state.                                                                                                                            |  |

| 27:26 | RO   | -    | Reserved                                                                                                                                                                |  |

| 25    | RO   | 1    | 1 if DCDC2 was enabled in the previous state.                                                                                                                           |  |

| 24    | RO   | 0    | 1 if DCDC1 was enabled in the previous state.                                                                                                                           |  |

| 23:19 | RO   | -    | Reserved                                                                                                                                                                |  |

| 18:16 | RO   |      | Current state of the power sequence state machine<br>0: Reset<br>1: Asleep<br>2: Waking 1<br>3: Waking 2<br>4: Awake Wait<br>5: Awake<br>6: Sleeping 1<br>7: Sleeping 2 |  |

| 15    | RO   | -    | Reserved                                                                                                                                                                |  |

| 14    | RO   | 0    | Set to 1 to disable clock to the xCORE Tile.                                                                                                                            |  |

| 13:10 | RO   | -    | Reserved                                                                                                                                                                |  |

| 9     | RO   | 0    | Sets modulation used by DCDC2:<br>0: PWM modulation (max 475 mA)<br>1: PFM modulation (max 50 mA)                                                                       |  |

| 8     | RO   | 0    | Sets modulation used by DCDC1:<br>0: PWM modulation (max 700 mA)<br>1: PFM modulation (max 50 mA)                                                                       |  |

| 7:6   | RO   | -    | Reserved                                                                                                                                                                |  |

| 5     | RO   | 0    | Set to 1 to enable VOUT6 (IO supply).                                                                                                                                   |  |

| 4     | RO   | 0    | Set to 1 to enable LDO5 (core PLL supply).                                                                                                                              |  |

| 3:2   | RO   | -    | Reserved                                                                                                                                                                |  |

| 1     | RO   | 0    | Set to 1 to enable DCDC2 (analogue supply).                                                                                                                             |  |

| 0     | RO   | 0    | Set to 1 to enable DCDC1 (core supply).                                                                                                                                 |  |

0x24: Power sequence status

# J.11 DCDC control: 0x2C

This register controls the two DC-DC converters.

-XMOS<sup>®</sup>

- ▶ TDO to pin 13 of the xSYS header

- RST\_N to pin 15 of the xSYS header

- If MODE2 is configured high, connect MODE2 to pin 3 of the xSYS header. Do not connect to VDDIO.

- If MODE3 is configured high, connect MODE3 to pin 3 of the xSYS header. Do not connect to VDDIO.

The RST\_N net should be open-drain, active-low, and have a pull-up to VDDIO.

#### M.3 Full xSYS header

For a full xSYS header you will need to connect the pins as discussed in Section M.2, and then connect a 2-wire xCONNECT Link to the xSYS header. The links can be found in the Signal description table (Section 4): they are labelled XLA, XLB, etc in the function column. The 2-wire link comprises two inputs and outputs, labelled  ${}^{1}_{out}$ ,  ${}^{0}_{out}$ ,  ${}^{0}_{out}$ ,  ${}^{0}_{iu}$ , and  ${}^{1}_{in}$ . For example, if you choose to use XLB of tile 0 for xSCOPE I/O, you need to connect up XLB ${}^{1}_{out}$ , XLB ${}^{0}_{out}$ , XLB ${}^{1}_{in}$  as follows:

- XLB<sup>1</sup><sub>out</sub> (X0D16) to pin 6 of the xSYS header with a 33R series resistor close to the device.

- XLB<sup>0</sup><sub>out</sub> (X0D17) to pin 10 of the xSYS header with a 33R series resistor close to the device.

- ▶ XLB<sup>0</sup><sub>in</sub> (X0D18) to pin 14 of the xSYS header.

- ▶ XLB<sup>1</sup><sub>in</sub> (X0D19) to pin 18 of the xSYS header.

-XM()S