# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1507-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1.0 DEVICE OVERVIEW

The block diagram of these devices are shown in Figure 1-1, the available peripherals are shown in Table 1-1, and the pinout descriptions are shown in Table 1-2.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                                               | PIC12(L)F1501 | PIC16(L)F1503 | PIC16(L)F1507 | PIC16(L)F1508 | PIC16(L)F1509 |   |

|--------------------------------------------------------------------------|---------------|---------------|---------------|---------------|---------------|---|

| Analog-to-Digital Converter (A                                           | -             | •             | •             | •             | •             | • |

| Complementary Wave Genera                                                |               | •             | •             | •             | •             | • |

| Digital-to-Analog Converter (I                                           | DAC)          | •             | •             |               | •             | • |

| Enhanced Universal<br>Synchronous/Asynchronous  <br>Transmitter (EUSART) | Receiver/     |               |               |               | •             | • |

| Fixed Voltage Reference (FV                                              | R)            | •             | •             | •             | •             | • |

| Numerically Controlled Oscill                                            | ator (NCO)    | •             | •             | •             | •             | • |

| Temperature Indicator                                                    |               | •             | ٠             | •             | ٠             | • |

| Comparators                                                              |               |               |               |               |               |   |

|                                                                          | C1            | •             | ٠             |               | •             | • |

|                                                                          | C2            |               | •             |               | •             | • |

| Configurable Logic Cell (CLC                                             | -             |               |               |               |               |   |

|                                                                          | CLC1          | •             | •             | •             | •             | • |

|                                                                          | CLC2          | •             | •             | •             | •             | • |

|                                                                          | CLC3          |               |               |               | •             | • |

|                                                                          | CLC4          |               |               |               | •             | • |

| Master Synchronous Serial P                                              | orts          |               |               | 1             |               |   |

|                                                                          | MSSP1         |               | •             |               | •             | • |

| PWM Modules                                                              | n             |               |               | 1             |               |   |

|                                                                          | PWM1          | •             | •             | •             | •             | • |

|                                                                          | PWM2          | •             | •             | •             | •             | • |

|                                                                          | PWM3<br>PWM4  | •             | •             | •             | •             | • |

|                                                                          | •             | •             | •             | •             | •             |   |

| Timers                                                                   | 1             |               |               | 1             |               |   |

|                                                                          | Timer0        | •             | •             | •             | •             | • |

|                                                                          | Timer1        | •             | •             | •             | •             | • |

|                                                                          | Timer2        | •             | •             | •             | •             | • |

### 3.3.6 CORE FUNCTION REGISTERS SUMMARY

The Core Function registers listed in Table 3-4 can be addressed from any Bank.

| Addr            | Name      | Bit 7                                                    | Bit 6                                       | Bit 5         | Bit 4        | Bit 3       | Bit 2         | Bit 1  | Bit 0 | Value on<br>POR, BOR | Value on all other Resets |

|-----------------|-----------|----------------------------------------------------------|---------------------------------------------|---------------|--------------|-------------|---------------|--------|-------|----------------------|---------------------------|

| Bank            | Bank 0-31 |                                                          |                                             |               |              |             |               |        |       |                      |                           |

| x00h or<br>x80h | INDF0     |                                                          | this location                               |               | nts of FSR0H | /FSR0L to a | ddress data i | memory |       | xxxx xxxx            | uuuu uuuu                 |

| x01h or<br>x81h | INDF1     |                                                          | this location                               |               | nts of FSR1H | /FSR1L to a | ddress data i | memory |       | XXXX XXXX            | uuuu uuuu                 |

| x02h or<br>x82h | PCL       | Program C                                                | ounter (PC)                                 | Least Signifi | cant Byte    |             |               |        |       | 0000 0000            | 0000 0000                 |

| x03h or<br>x83h | STATUS    | -                                                        | —                                           |               | TO           | PD          | Z             | DC     | С     | 1 1000               | q quuu                    |

| x04h or<br>x84h | FSR0L     | Indirect Da                                              | ta Memory A                                 | ddress 0 Lo   | w Pointer    |             |               |        |       | 0000 0000            | uuuu uuuu                 |

| x05h or<br>x85h | FSR0H     | Indirect Da                                              | Indirect Data Memory Address 0 High Pointer |               |              |             |               |        |       |                      | 0000 0000                 |

| x06h or<br>x86h | FSR1L     | Indirect Da                                              | Indirect Data Memory Address 1 Low Pointer  |               |              |             |               |        |       | 0000 0000            | uuuu uuuu                 |

| x07h or<br>x87h | FSR1H     | Indirect Da                                              | ta Memory A                                 | ddress 1 Hig  | gh Pointer   |             |               |        |       | 0000 0000            | 0000 0000                 |

| x08h or<br>x88h | BSR       | _                                                        | BSR<4:0>                                    |               |              |             |               |        |       | 0 0000               | 0 0000                    |

| x09h or<br>x89h | WREG      | Working Register                                         |                                             |               |              |             |               |        |       | 0000 0000            | uuuu uuuu                 |

| x0Ahor<br>x8Ah  | PCLATH    | Write Buffer for the upper 7 bits of the Program Counter |                                             |               |              |             |               |        |       | -000 0000            | -000 0000                 |

| x0Bhor<br>x8Bh  | INTCON    | GIE                                                      | PEIE                                        | TMR0IE        | INTE         | IOCIE       | TMR0IF        | INTF   | IOCIF | 0000 0000            | 0000 0000                 |

#### TABLE 3-4: CORE FUNCTION REGISTERS SUMMARY

Legend: x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations are unimplemented, read as '0'.

| TABLE 3-5: | SPECIAL FUNCTION REGISTER SUMMARY ( | (CONTINUED) |  |

|------------|-------------------------------------|-------------|--|

|            |                                     |             |  |

| TABLE              | ABLE 3-5: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |            |               |        |        |           |        |        |         |                      |                                 |

|--------------------|---------------------------------------------------------|------------|---------------|--------|--------|-----------|--------|--------|---------|----------------------|---------------------------------|

| Address            | Name                                                    | Bit 7      | Bit 6         | Bit 5  | Bit 4  | Bit 3     | Bit 2  | Bit 1  | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 4             |                                                         |            |               |        |        |           |        |        |         |                      |                                 |

| 20Ch               | WPUA                                                    | _          | _             | WPUA5  | WPUA4  | WPUA3     | WPUA2  | WPUA1  | WPUA0   | 11 1111              | 11 1111                         |

| 20Dh               | WPUB                                                    | WPUB7      | WPUB6         | WPUB5  | WPUB4  | _         | _      | _      | _       | 1111                 | 1111                            |

| 20Eh<br>to<br>21Fh | _                                                       | Unimplemen | ted           |        |        |           |        |        |         | _                    | _                               |

| Bank 5             |                                                         |            |               |        |        |           |        |        |         |                      |                                 |

| 28Ch               |                                                         |            |               |        |        |           |        |        |         |                      |                                 |

| to<br>29Fh         | _                                                       | Unimplemen | ted           |        |        |           |        |        |         | —                    | —                               |

| Bank 6             |                                                         |            |               |        |        |           |        |        |         |                      |                                 |

| 30Ch<br>to<br>31Fh | _                                                       | Unimplemen | ted           |        |        |           |        |        |         | -                    | -                               |

| Bank 7             |                                                         | •          |               |        |        |           |        |        |         |                      |                                 |

| 38Ch<br>to<br>390h | _                                                       | Unimplemen | ted           |        |        |           |        |        |         | _                    | _                               |

| 391h               | IOCAP                                                   | _          | —             | IOCAP5 | IOCAP4 | IOCAP3    | IOCAP2 | IOCAP1 | IOCAP0  | 00 0000              | 00 0000                         |

| 392h               | IOCAN                                                   | _          | _             | IOCAN5 | IOCAN4 | IOCAN3    | IOCAN2 | IOCAN1 | IOCAN0  | 00 0000              | 00 0000                         |

| 393h               | IOCAF                                                   | _          | _             | IOCAF5 | IOCAF4 | IOCAF3    | IOCAF2 | IOCAF1 | IOCAF0  | 00 0000              | 00 0000                         |

| 394h               | IOCBP                                                   | IOCBP7     | IOCBP6        | IOCBP5 | IOCBP4 | _         | _      | —      | _       | 0000                 | 0000                            |

| 395h               | IOCBN                                                   | IOCBN7     | IOCBN6        | IOCBN5 | IOCBN4 |           | —      | —      | _       | 0000                 | 0000                            |

| 396h               | IOCBF                                                   | IOCBF7     | IOCBF6        | IOCBF5 | IOCBF4 | -         | —      | —      | —       | 0000                 | 0000                            |

| 397h<br>to<br>39Fh | _                                                       | Unimplemen | Unimplemented |        |        |           |        |        |         |                      | —                               |

| Bank 8             |                                                         | _          |               |        |        |           |        |        |         |                      |                                 |

| 40Ch<br>to<br>41Fh | _                                                       | Unimplemen | ted           |        |        |           |        |        |         | -                    | _                               |

| Bank 9             |                                                         |            |               |        |        |           |        |        |         |                      |                                 |

| 48Ch<br>to<br>497h | _                                                       | Unimplemen | Unimplemented |        |        |           |        |        |         |                      | _                               |

| 498h               | NCO1ACCL                                                |            |               |        | NCO1/  | ACC<7:0>  |        |        |         | 0000 0000            | 0000 0000                       |

| 499h               | NCO1ACCH                                                |            |               |        | NCO1A  | CC<15:8>  |        |        |         | 0000 0000            | 0000 0000                       |

| 49Ah               | NCO1ACCU                                                |            |               |        | NCO1A  | CC<19:16> |        |        |         | 0000 0000            | 0000 0000                       |

| 49Bh               | NCO1INCL                                                |            |               |        | NCO1   | INC<7:0>  |        |        |         | 0000 0001            | 0000 0001                       |

| 49Ch               | NCO1INCH                                                |            |               |        | NCO1I  | NC<15:8>  |        |        |         | 0000 0000            | 0000 0000                       |

| 49Dh               | _                                                       | Unimplemen | ted           |        |        |           |        |        |         | _                    | _                               |

| 49Eh               | NCO1CON                                                 | N1EN       | N10E          | N1OUT  | N1POL  | _         | _      | _      | N1PFM   | 00000                | 00000                           |

| 49Fh               | NCO1CLK                                                 |            | N1PWS<2:0>    |        | —      | _         | _      | N1Ck   | (S<1:0> | 000000               | 000000                          |

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'. PIC16F1507 only. Unimplemented, read as '1'. Legend: Note 1: 2:

| TABLE 3-5: SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) |          |            |               |         |         |          |          |           |            |                      |                                 |

|----------------------------------------------------------|----------|------------|---------------|---------|---------|----------|----------|-----------|------------|----------------------|---------------------------------|

| Address                                                  | Name     | Bit 7      | Bit 6         | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1     | Bit 0      | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 1                                                   | 0        |            |               |         |         |          |          |           |            |                      |                                 |

| 50Ch<br>to<br>51Fh                                       |          | Unimplemen | ted           |         |         |          |          |           |            | _                    | —                               |

| Bank 1                                                   | 1        | -          |               |         |         |          |          |           |            |                      |                                 |

| 58Ch<br>to<br>59Fh                                       | _        | Unimplemen | ted           |         |         |          |          |           |            | _                    | —                               |

| Bank 1                                                   | 2        | -          |               |         |         |          |          |           |            |                      |                                 |

| 60Ch<br>to<br>610h                                       | _        | Unimplemen | ted           |         |         |          |          |           |            | _                    | _                               |

| 611h                                                     | PWM1DCL  | PWM1D      | CL<7:6>       | _       | —       | _        | _        | —         | _          | 00                   | 00                              |

| 612h                                                     | PWM1DCH  |            |               |         | PWM1    | DCH<7:0> |          |           |            | xxxx xxxx            | uuuu uuuu                       |

| 613h                                                     | PWM1CON0 | PWM1EN     | PWM10E        | PWM1OUT | PWM1POL | _        | _        | —         | _          | 0000                 | 0000                            |

| 614h                                                     | PWM2DCL  | PWM2D      | CL<7:6>       | _       | —       | _        | _        | —         | _          | 00                   | 00                              |

| 615h                                                     | PWM2DCH  |            |               |         | PWM2I   | DCH<7:0> |          |           |            | xxxx xxxx            | uuuu uuuu                       |

| 616h                                                     | PWM2CON0 | PWM2EN     | PWM2OE        | PWM2OUT | PWM2POL | _        | _        | —         | _          | 0000                 | 0000                            |

| 617h                                                     | PWM3DCL  | PWM3D      | CL<7:6>       | _       | —       | _        | _        | —         | _          | 00                   | 00                              |

| 618h                                                     | PWM3DCH  |            |               |         | PWM3I   | DCH<7:0> |          |           |            | xxxx xxxx            | uuuu uuuu                       |

| 619h                                                     | PWM3CON0 | PWM3EN     | PWM3OE        | PWM3OUT | PWM3POL | _        | _        | —         | _          | 0000                 | 0000                            |

| 61Ah                                                     | PWM4DCL  | PWM4D      | CL<7:6>       | _       | —       | _        | _        | —         | _          | 00                   | 00                              |

| 61Bh                                                     | PWM4DCH  |            |               |         | PWM4    | DCH<7:0> |          |           |            | xxxx xxxx            | uuuu uuuu                       |

| 61Ch                                                     | PWM4CON0 | PWM4EN     | PWM4OE        | PWM4OUT | PWM4POL | _        | _        | —         | _          | 0000                 | 0000                            |

| 61Dh<br>to<br>61Fh                                       | _        | Unimplemen | ted           |         |         |          |          |           |            | _                    | _                               |

| Bank 1                                                   | 3        |            |               |         |         |          |          |           |            |                      |                                 |

| 68Ch<br>to<br>690h                                       | _        | Unimplemen | Inimplemented |         |         |          |          |           |            |                      | _                               |

| 691h                                                     | CWG1DBR  | _          |               |         |         | CWG1     | DBR<5:0> |           |            | 00 0000              | 00 0000                         |

| 692h                                                     | CWG1DBF  | _          | _             |         |         | CWG1     | DBF<5:0> |           |            | xx xxxx              | xx xxxx                         |

| 693h                                                     | CWG1CON0 | G1EN       | G10EB         | G10EA   | G1POLB  | G1POLA   | _        | —         | G1CS0      | 0000 00              | 0000 00                         |

| 694h                                                     | CWG1CON1 | G1ASDI     | LB<1:0>       | G1ASD   | LA<1:0> | _        |          | G1IS<2:0> |            | 0000 -000            | 0000 -000                       |

| 695h                                                     | CWG1CON2 | G1ASE      | G1ARSEN       | _       | _       | _        | —        | G1ASDSFLT | G1ASDSCLC2 | 0000                 | 0000                            |

| 696h<br>to<br>69Fh                                       | _        | Unimplemen | ted           |         |         |          |          |           |            | _                    | _                               |

#### TABLE 3-5 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16F1507 only.

2:

Unimplemented, read as '1'.

#### 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

#### 7.2 Interrupt Latency

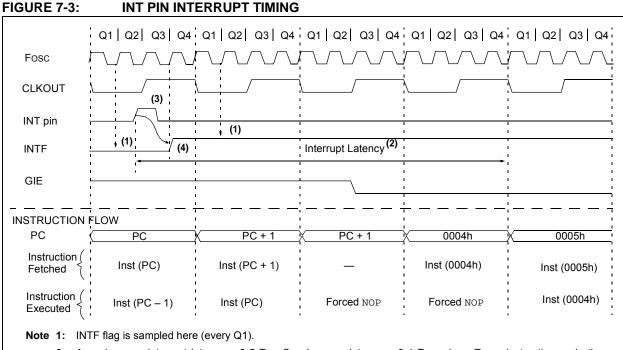

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

2: Asynchronous interrupt latency = 3-5 TCY. Synchronous latency = 3-4 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

3: For minimum width of INT pulse, refer to AC specifications in Section 25.0 "Electrical Specifications".

4: INTF is enabled to be set any time during the Q4-Q1 cycles.

#### 10.4 User ID, Device ID and Configuration Word Access

Instead of accessing program memory, the User ID's, Device ID/Revision ID and Configuration Words can be accessed when CFGS = 1 in the PMCON1 register. This is the region that would be pointed to by PC<15> = 1, but not all addresses are accessible. Different access may exist for reads and writes. Refer to Table 10-2.

When read access is initiated on an address outside the parameters listed in Table 10-2, the PMDATH:PMDATL register pair is cleared, reading back '0's.

| Address     | Function                    | Read Access | Write Access |

|-------------|-----------------------------|-------------|--------------|

| 8000h-8003h | User IDs                    | Yes         | Yes          |

| 8006h       | Device ID/Revision ID       | Yes         | No           |

| 8007h-8008h | Configuration Words 1 and 2 | Yes         | No           |

#### EXAMPLE 10-4: CONFIGURATION WORD AND DEVICE ID ACCESS

\* This code block will read 1 word of program memory at the memory address:

\* PROG\_ADDR\_LO (must be 00h-08h) data will be returned in the variables;

\* PROG\_DATA\_HI, PROG\_DATA\_LO

| BANKSEL | PMADRL       | ; Select correct Bank        |

|---------|--------------|------------------------------|

| MOVLW   | PROG_ADDR_LO | ;                            |

| MOVWF   | PMADRL       | ; Store LSB of address       |

| CLRF    | PMADRH       | ; Clear MSB of address       |

| BSF     | PMCON1,CFGS  | ; Select Configuration Space |

| BCF     | INTCON,GIE   | ; Disable interrupts         |

| BSF     | PMCON1,RD    | ; Initiate read              |

| NOP     |              | ; Executed (See Figure 10-2) |

| NOP     |              | ; Ignored (See Figure 10-2)  |

| BSF     | INTCON,GIE   | ; Restore interrupts         |

| MOVF    | PMDATL,W     | ; Get LSB of word            |

| MOVWF   | PROG_DATA_LO | ; Store in user location     |

| MOVF    | PMDATH,W     | ; Get MSB of word            |

| MOVWF   | PROG_DATA_HI | ; Store in user location     |

#### 11.5 PORTB Registers

#### 11.5.1 DATA REGISTER

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-8). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-7) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

#### 11.5.2 DIRECTION CONTROL

The TRISB register (Register 11-8) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.5.3 ANALOG CONTROL

The ANSELB register (Register 11-10) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

|       | mode after Reset. To use any pins as         |  |  |  |  |  |  |

|       | digital general purpose or peripheral        |  |  |  |  |  |  |

|       | inputs, the corresponding ANSEL bits         |  |  |  |  |  |  |

|       | must be initialized to '0' by user software. |  |  |  |  |  |  |

#### 11.5.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC and comparator inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below in Table 11-5.

#### TABLE 11-5: PORTB OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RB4      | RB4                              |

| RB5      | RB5                              |

| RB6      | RB6                              |

| RB7      | RB7                              |

Note 1: Priority listed from highest to lowest.2: Default pin (see APFCON register).

| R/W-x/u                           | R/W-x/u | R/W-x/u         | R/W-x/u | U-0                                                   | U-0 | U-0 | U-0   |  |  |

|-----------------------------------|---------|-----------------|---------|-------------------------------------------------------|-----|-----|-------|--|--|

| LATB7                             | LATB6   | LATB5           | LATB4   | —                                                     | —   | —   | —     |  |  |

| bit 7                             | ·       | •               |         |                                                       |     | •   | bit 0 |  |  |

|                                   |         |                 |         |                                                       |     |     |       |  |  |

| Legend:                           |         |                 |         |                                                       |     |     |       |  |  |

| R = Readable bit W = Writable bit |         |                 |         | U = Unimplemented bit, read as '0'                    |     |     |       |  |  |

| u = Bit is unch                   | anged   | x = Bit is unkr | nown    | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |  |

#### **REGISTER 11-9: LATB: PORTB DATA LATCH REGISTER**

| bit 7-4 | LATB<7:4>: RB<7:4> Output Latch Value bits <sup>(1)</sup> |

|---------|-----------------------------------------------------------|

|---------|-----------------------------------------------------------|

bit 3-0 Unimplemented: Read as '0'

1' = Bit is set

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

#### REGISTER 11-10: ANSELB: PORTB ANALOG SELECT REGISTER

'0' = Bit is cleared

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|---------|---------|-----|-----|-----|-------|

| —     | _   | ANSB5   | ANSB4   | —   | —   | —   |       |

| bit 7 |     |         |         |     |     |     | bit 0 |

|       |     |         |         |     |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 ANSB<5:4>: Analog Select between Analog or Digital Function on pins RB<5:4>, respectively

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or digital special function.

bit 3-0 Unimplemented: Read as '0'

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

#### 15.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC Interrupt Flag is the ADIF bit in the PIR1 register. The ADC Interrupt Enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

- **Note 1:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

- **2:** The ADC operates during Sleep only when the FRC oscillator is selected.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the GIE and PEIE bits of the INTCON register must be disabled. If the GIE and PEIE bits of the INTCON register are enabled, execution will switch to the Interrupt Service Routine.

#### 15.1.6 RESULT FORMATTING

The 10-bit ADC conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON1 register controls the output format.

Figure 15-3 shows the two output formats.

#### Rev. 10-000054A 7/30/2013 ADRESH ADRESL (ADFM = 0) MSB LSB bit 7 bit 0 bit 7 bit 0 10-bit ADC Result Unimplemented: Read as '0' (ADFM = 1) LSB MSB bit 7 bit 0 bit 7 bit 0 Unimplemented: Read as '0' 10-bit ADC Result

#### FIGURE 15-3: 10-BIT ADC CONVERSION RESULT FORMAT

#### FIGURE 17-4: TIMER1 GATE TOGGLE MODE

| TMR1GE                                                                      |                                                            |

|-----------------------------------------------------------------------------|------------------------------------------------------------|

| T1GPOL                                                                      |                                                            |

| T1GSPM                                                                      |                                                            |

| T1GGO/ Set by software<br>DONE<br>Counting enabled on<br>rising edge of T1C | Cleared by hardware on falling edge of T1GVAL              |

| rising edge of T1G                                                          |                                                            |

|                                                                             |                                                            |

| T1GVAL                                                                      |                                                            |

| Timer1 N N +                                                                | N + 2                                                      |

| TMR1GIF Cleared by software                                                 | Cleared by<br>Set by hardware on<br>falling edge of T1GVAL |

#### 19.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 19-4.

#### EQUATION 19-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + I)]}{\log(2)}$$

bits

**Note:** If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TABLE 19-1: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 19-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 19.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 19.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to for additional details.

#### 19.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

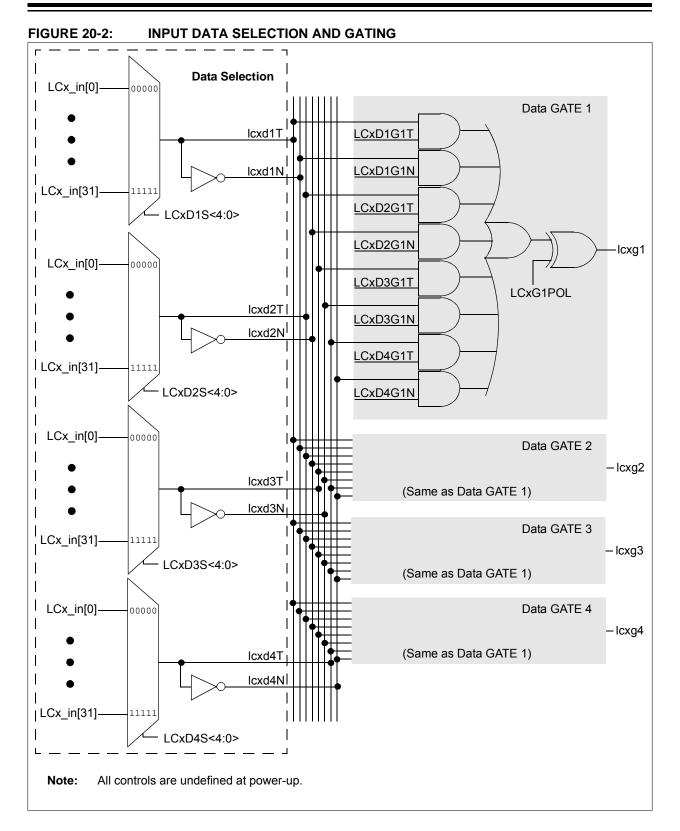

#### 20.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### **Note:** Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 20-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

| TABLE 20-2: | <b>DATA GATING</b> | LOGIC |

|-------------|--------------------|-------|

|-------------|--------------------|-------|

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 20-5)

- Gate 2: CLCxGLS1 (Register 20-6)

- Gate 3: CLCxGLS2 (Register 20-7)

- Gate 4: CLCxGLS3 (Register 20-8)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 20-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 20.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 20-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

#### 20.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

### 24.2 Instruction Descriptions

| ADDFSR           | Add Literal to FSRn                                                                     |

|------------------|-----------------------------------------------------------------------------------------|

| Syntax:          | [label] ADDFSR FSRn, k                                                                  |

| Operands:        | -32 ≤ k ≤ 31<br>n ∈ [ 0, 1]                                                             |

| Operation:       | $FSR(n) + k \rightarrow FSR(n)$                                                         |

| Status Affected: | None                                                                                    |

| Description:     | The signed 6-bit literal 'k' is added to the contents of the FSRnH:FSRnL register pair. |

|                  | FSRn is limited to the range 0000h -                                                    |

FFFFh. Moving beyond these bounds will cause the FSR to wrap-around.

| ANDLW            | AND literal with W                                                                                              |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                        |

| Operands:        | $0 \leq k \leq 255$                                                                                             |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                 |

| Status Affected: | Z                                                                                                               |

| Description:     | The contents of W register are<br>AND'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |

| ADDLW            | Add literal and W                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                            |

| Operands:        | $0 \leq k \leq 255$                                                                                                 |

| Operation:       | $(W) + k \to (W)$                                                                                                   |

| Status Affected: | C, DC, Z                                                                                                            |

| Description:     | The contents of the W register are<br>added to the 8-bit literal 'k' and the<br>result is placed in the W register. |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDWF f,d                                                                                                                                      |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | AND the W register with register 'f'. If<br>'d' is '0', the result is stored in the W<br>register. If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |

| ADDWF            | Add W and f                                                                                                                                                                     |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] ADDWF f,d                                                                                                                                                               |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                 |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                           |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                        |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the result is<br>stored in the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |  |

| ASRF             | Arithmetic Right Shift                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ASRF f {,d}                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |

| Operation:       | (f<7>)→ dest<7><br>(f<7:1>) → dest<6:0>,<br>(f<0>) → C,                                                                                                                                                            |

| Status Affected: | C, Z                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are shifted<br>one bit to the right through the Carry<br>flag. The MSb remains unchanged. If<br>'d' is '0', the result is placed in W. If 'd'<br>is '1', the result is stored back in |

register 'f'.

| ► | register f | -> | С |  |

|---|------------|----|---|--|

| ADDWFC |  |

|--------|--|

| ADDWFC |  |

ADD W and CARRY bit to f

| Syntax:          | [ label ] ADDWFC f {,d}                                                                                                                                                   |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |

| Operation:       | $(W) + (f) + (C) \rightarrow dest$                                                                                                                                        |

| Status Affected: | C, DC, Z                                                                                                                                                                  |

| Description:     | Add W, the Carry flag and data mem-<br>ory location 'f'. If 'd' is '0', the result is<br>placed in W. If 'd' is '1', the result is<br>placed in data memory location 'f'. |

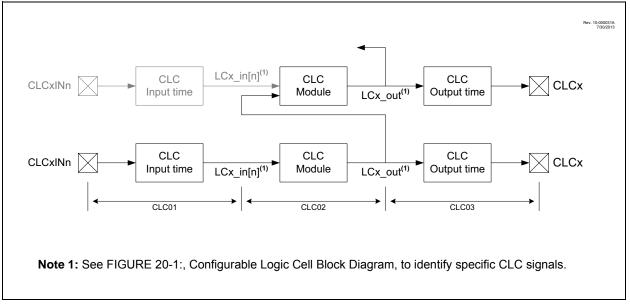

| TABLE 25-12: | CONFIGURATION LOGIC CELL (CLC) CHARACTERISTICS |

|--------------|------------------------------------------------|

|              |                                                |

| Param.<br>No. | Sym.    | Characteristic                              | Min. | Тур†     | Max. | Units    | Conditions               |

|---------------|---------|---------------------------------------------|------|----------|------|----------|--------------------------|

| CLC01*        | TCLCIN  | CLC input time                              | _    | 7        | _    | ns       |                          |

| CLC02*        | TCLC    | CLC module input to output propagation time |      | 24<br>12 |      | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |

| CLC03*        | TCLCOUT | CLC output time Rise Time                   |      | OS18     |      | —        | (Note 1)                 |

|               |         | Fall Time                                   | _    | OS19     | _    |          | (Note 1)                 |

| CLC04*        | FCLCMAX | CLC maximum switching frequency             |      | 45       | _    | MHz      |                          |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1:See Table 25-9 for OS18 and OS19 rise and fall times.

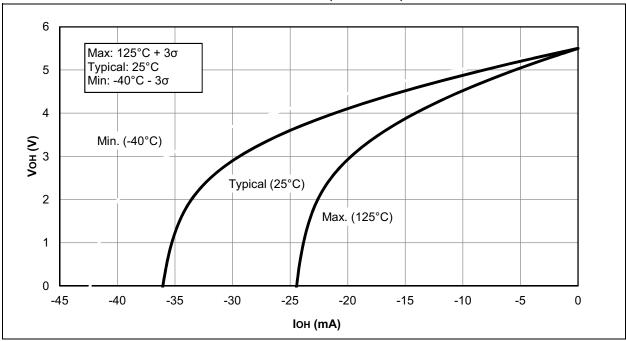

FIGURE 26-31: VOH vs. IOH OVER TEMPERATURE, VDD = 5.5V, PIC16F1507 ONLY

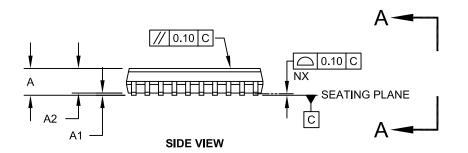

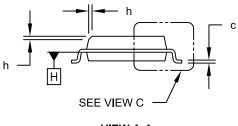

#### 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2

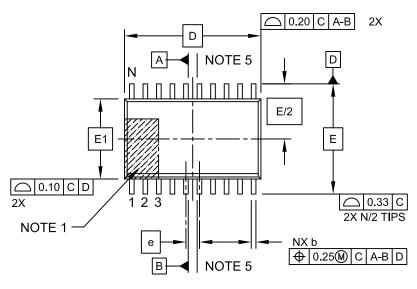

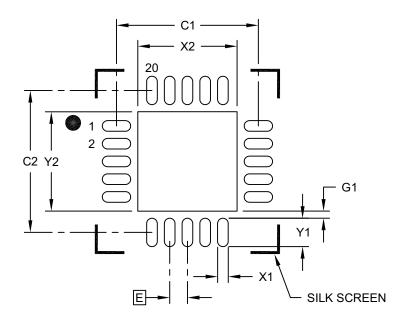

#### 20-Lead Ultra Thin Plastic Quad Flat, No Lead Package (GZ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |          |      |      |  |

|---------------------------------|-------------|----------|------|------|--|

| Dimension Limits                |             | MIN      | NOM  | MAX  |  |

| Contact Pitch E                 |             | 0.50 BSC |      |      |  |

| Optional Center Pad Width       | X2          | 2.80     |      |      |  |

| Optional Center Pad Length      |             |          |      | 2.80 |  |

| Contact Pad Spacing C1          |             |          | 4.00 |      |  |

| Contact Pad Spacing             | C2          |          | 4.00 |      |  |

| Contact Pad Width (X20)         | X1          |          |      | 0.30 |  |

| Contact Pad Length (X20) Y1     |             |          |      | 0.80 |  |

| Contact Pad to Center Pad (X20) | G1          | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2255A