Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                            |

| Supplier Device Package    | 20-SSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1507-e-ss |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 1-2:** PIC16(L)F1507 PINOUT DESCRIPTION (CONTINUED)

| Name                           | Function | Input<br>Type | Output<br>Type | Description                                      |  |  |

|--------------------------------|----------|---------------|----------------|--------------------------------------------------|--|--|

| RC3/AN7/PWM2/CLC2IN0           | RC3      | TTL           | CMOS           | General purpose I/O.                             |  |  |

|                                | AN7      | AN            | _              | A/D Channel input.                               |  |  |

|                                | PWM2     | —             | CMOS           | Pulse Width Module source output.                |  |  |

|                                | CLC2IN0  | ST            | _              | Configurable Logic Cell source input.            |  |  |

| RC4/CLC2IN1/CWG1B              | RC4      | TTL           | CMOS           | General purpose I/O.                             |  |  |

|                                | CLC2IN1  | ST            | —              | Configurable Logic Cell source input.            |  |  |

|                                | CWG1B    | —             | CMOS           | CWG complementary output.                        |  |  |

| RC5/PWM1/CLC1 <sup>(1)</sup> / | RC5      | TTL           | CMOS           | General purpose I/O.                             |  |  |

| CWG1A                          | PWM1     | —             | CMOS           | PWM output.                                      |  |  |

|                                | CLC1     | —             | CMOS           | Configurable Logic Cell source output.           |  |  |

|                                | CWG1A    | —             | CMOS           | CWG primary output.                              |  |  |

| RC6/AN8/NCO1 <sup>(1)</sup>    | RC6      | TTL           | CMOS           | General purpose I/O.                             |  |  |

|                                | AN8      | AN            | —              | A/D Channel input.                               |  |  |

|                                | NCO1     | _             | CMOS           | Numerically Controlled Oscillator source output. |  |  |

| RC7/AN9/CLC1IN1                | RC7      | TTL           | CMOS           | General purpose I/O.                             |  |  |

|                                | AN8      | AN            | _              | A/D Channel input.                               |  |  |

|                                | CLC1IN1  | ST            | —              | Configurable Logic Cell source input.            |  |  |

| Vdd                            | Vdd      | Power         | _              | Positive supply.                                 |  |  |

| Vss                            | Vss      | Power         |                | Ground reference.                                |  |  |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage levels

XTAL = Crystal

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

| TABLE              | 3-5: S   | PECIAL F   | UNCTIO         | N REGIS | TER SUN | MMARY (  | CONTIN   | UED)      |            |                      |                                 |  |  |

|--------------------|----------|------------|----------------|---------|---------|----------|----------|-----------|------------|----------------------|---------------------------------|--|--|

| Address            | Name     | Bit 7      | Bit 6          | Bit 5   | Bit 4   | Bit 3    | Bit 2    | Bit 1     | Bit 0      | Value on<br>POR, BOR | Value on all<br>other<br>Resets |  |  |

| Bank 1             | 0        |            |                |         |         |          |          |           |            |                      |                                 |  |  |

| 50Ch<br>to<br>51Fh |          | Unimplemen | ted            |         |         |          |          |           |            | _                    | —                               |  |  |

| Bank 1             | 1        | -          |                |         |         |          |          |           |            |                      |                                 |  |  |

| 58Ch<br>to<br>59Fh | _        | Unimplemen | nimplemented — |         |         |          |          |           |            |                      |                                 |  |  |

| Bank 1             | 2        | -          |                |         |         |          |          |           |            |                      |                                 |  |  |

| 60Ch<br>to<br>610h | _        | Unimplemen | ted            |         |         |          |          |           |            | _                    | _                               |  |  |

| 611h               | PWM1DCL  | PWM1D      | CL<7:6>        | _       | —       | _        | _        | —         | _          | 00                   | 00                              |  |  |

| 612h               | PWM1DCH  |            |                |         | PWM1    | DCH<7:0> |          |           |            | xxxx xxxx            | uuuu uuuu                       |  |  |

| 613h               | PWM1CON0 | PWM1EN     | PWM10E         | PWM1OUT | PWM1POL | _        | _        | _         | _          | 0000                 | 0000                            |  |  |

| 614h               | PWM2DCL  | PWM2D      | CL<7:6>        | _       | —       | _        | _        | —         | _          | 00                   | 00                              |  |  |

| 615h               | PWM2DCH  |            |                |         | PWM2I   | DCH<7:0> |          |           |            | xxxx xxxx            | uuuu uuuu                       |  |  |

| 616h               | PWM2CON0 | PWM2EN     | PWM2OE         | PWM2OUT | PWM2POL | _        | _        | _         | _          | 0000                 | 0000                            |  |  |

| 617h               | PWM3DCL  | PWM3D      | CL<7:6>        | _       | —       | _        | _        | —         | _          | 00                   | 00                              |  |  |

| 618h               | PWM3DCH  |            |                |         | PWM3I   | DCH<7:0> |          |           |            | xxxx xxxx            | uuuu uuuu                       |  |  |

| 619h               | PWM3CON0 | PWM3EN     | PWM3OE         | PWM3OUT | PWM3POL | _        | _        | _         | _          | 0000                 | 0000                            |  |  |

| 61Ah               | PWM4DCL  | PWM4D      | CL<7:6>        | _       | —       | _        | _        | —         | _          | 00                   | 00                              |  |  |

| 61Bh               | PWM4DCH  |            |                |         | PWM4    | DCH<7:0> |          |           |            | xxxx xxxx            | uuuu uuuu                       |  |  |

| 61Ch               | PWM4CON0 | PWM4EN     | PWM4OE         | PWM4OUT | PWM4POL | _        | _        | —         | _          | 0000                 | 0000                            |  |  |

| 61Dh<br>to<br>61Fh | _        | Unimplemen | ted            |         |         |          |          |           |            | _                    | _                               |  |  |

| Bank 1             | 3        |            |                |         |         |          |          |           |            |                      |                                 |  |  |

| 68Ch<br>to<br>690h | _        | Unimplemen | ted            |         |         |          |          |           |            | —                    | _                               |  |  |

| 691h               | CWG1DBR  | _          |                |         |         | CWG1     | DBR<5:0> |           |            | 00 0000              | 00 0000                         |  |  |

| 692h               | CWG1DBF  | _          | _              |         |         | CWG1     | DBF<5:0> |           |            | xx xxxx              | xx xxxx                         |  |  |

| 693h               | CWG1CON0 | G1EN       | G10EB          | G10EA   | G1POLB  | G1POLA   | _        | —         | G1CS0      | 0000 00              | 0000 00                         |  |  |

| 694h               | CWG1CON1 | G1ASDI     | LB<1:0>        | G1ASD   | LA<1:0> | _        |          | G1IS<2:0> |            | 0000 -000            | 0000 -000                       |  |  |

| 695h               | CWG1CON2 | G1ASE      | G1ARSEN        | _       | _       | _        | —        | G1ASDSFLT | G1ASDSCLC2 | 0000                 | 0000                            |  |  |

| 696h<br>to<br>69Fh | _        | Unimplemen | ted            |         |         |          |          |           |            | _                    | _                               |  |  |

#### TABLE 3-5 SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

Legend:

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16F1507 only.

2:

Unimplemented, read as '1'.

### 5.2 Clock Source Types

Clock sources can be classified as external, internal or peripheral.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The peripheral clock source is a nominal 600 kHz internal RC oscillator, FRC. The FRC is traditionally used with the ADC module, but is sometimes available to other peripherals. See **Section 5.2.2.4** "**Peripheral Clock Sources**".

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

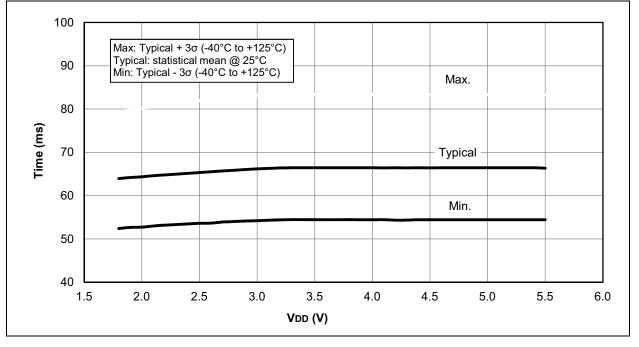

#### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through the Fosc bits in the Configuration Words:

- ECH High power, 4-20 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

#### FIGURE 5-2: EXTERNAL CLOCK (EC) MODE OPERATION

| U-1              | R/W-0/0            | R/W-0/0                                     | R/W/HC-0/0            | R/W/HC-x/q <sup>(2)</sup>             | R/W-0/0           | R/S/HC-0/0           | R/S/HC-0/0       |

|------------------|--------------------|---------------------------------------------|-----------------------|---------------------------------------|-------------------|----------------------|------------------|

| (1)              | CFGS               | LWLO                                        | FREE                  | WRERR                                 | WREN              | WR                   | RD               |

| bit 7            |                    |                                             |                       |                                       |                   |                      | bit (            |

| Legend:          |                    |                                             |                       |                                       |                   |                      |                  |

| R = Readable     | bit                | W = Writable b                              | it                    | U = Unimplemer                        | nted bit, read as | s 'O'                |                  |

| S = Bit can on   | ly be set          | x = Bit is unkno                            | own                   | -n/n = Value at F                     | POR and BOR/      | /alue at all other I | Resets           |

| '1' = Bit is set |                    | '0' = Bit is clea                           | red                   | HC = Bit is clear                     | ed by hardware    | 9                    |                  |

| bit 7            | Unimplemen         | ted: Read as '1'                            |                       |                                       |                   |                      |                  |

| bit 6            | CFGS: Config       | guration Select bit                         |                       |                                       |                   |                      |                  |

|                  |                    | Configuration, Use<br>Flash program me      |                       | ID Registers                          |                   |                      |                  |

| bit 5            | LWLO: Load         | Write Latches On                            | ly bit <sup>(3)</sup> |                                       |                   |                      |                  |

|                  |                    | addressed progra                            |                       |                                       |                   |                      |                  |

|                  |                    | ressed program m<br>nitiated on the nex     |                       | n is loaded/update                    | ed and a write of | all program memo     | ory write latche |

| bit 4            | FREE: Progra       | am Flash Erase E                            | nable bit             |                                       |                   |                      |                  |

|                  |                    | s an erase operati<br>s a write operatior   |                       | •                                     | rdware cleared    | upon completion)     |                  |

| bit 3            |                    | gram/Erase Error                            | •                     |                                       |                   |                      |                  |

|                  |                    | n indicates an imp                          |                       |                                       | e attempt or te   | rmination (bit is s  | et automaticall  |

|                  |                    | et attempt (write '<br>gram or erase ope    |                       |                                       |                   |                      |                  |

| bit 2            |                    | ram/Erase Enable                            | •                     | , , , , , , , , , , , , , , , , , , , |                   |                      |                  |

|                  | 0                  | rogram/erase cyc                            |                       |                                       |                   |                      |                  |

|                  | 0 = Inhibits       | programming/eras                            | ing of program F      | lash                                  |                   |                      |                  |

| bit 1            | WR: Write Co       |                                             |                       |                                       |                   |                      |                  |

|                  |                    | a program Flash p<br>ration is self-timed   |                       |                                       | o onco onorativ   | on is complete       |                  |

|                  | •                  | bit can only be se                          |                       | •                                     | e once operatio   | on is complete.      |                  |

|                  |                    | /erase operation f                          | ` '                   |                                       | ive.              |                      |                  |

| bit 0            | RD: Read Co        | ontrol bit                                  |                       |                                       |                   |                      |                  |

|                  |                    | a program Flash r                           | ead. Read takes       | s one cycle. RD is                    | cleared in hard   | lware. The RD bit    | can only be se   |

|                  | · ·                | ared) in software.<br>It initiate a prograr | n Flash read          |                                       |                   |                      |                  |

| Note 1: U        | nimplemented bit   |                                             |                       |                                       |                   |                      |                  |

|                  | •                  | automatically set I                         | by hardware whe       | en a program men                      | nory write or era | ase operation is st  | arted (WR = 1    |

|                  | he LWLO bit is igi | -                                           | -                     |                                       |                   | •                    | •                |

### REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

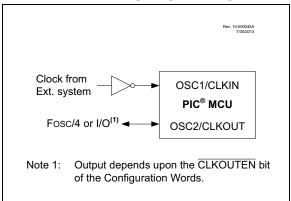

## 11.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- · TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- · ANSELx (analog select)

- · WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

## TABLE 11-1:PORT AVAILABILITY PER<br/>DEVICE

| Device        | PORTA | PORTB | PORTC |

|---------------|-------|-------|-------|

| PIC16(L)F1507 | ٠     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

### FIGURE 11-1: GE

#### GENERIC I/O PORT OPERATION

#### REGISTER 11-15: ANSELC: PORTC ANALOG SELECT REGISTER

| R/W-1/1 | R/W-1/1 | U-0 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|---------|---------|-----|-----|---------|---------|---------|---------|

| ANSC7   | ANSC6   | —   | —   | ANSC3   | ANSC2   | ANSC1   | ANSC0   |

| bit 7   |         |     |     |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-6 | <ul> <li>ANSC&lt;7:6&gt;: Analog Select between Analog or Digital Function on pins RC&lt;7:6&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                        |

| bit 3-0 | <ul> <li>ANSC&lt;3:0&gt;: Analog Select between Analog or Digital Function on pins RC&lt;3:0&gt;, respectively</li> <li>1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.</li> <li>0 = Digital I/O. Pin is assigned to port or digital special function.</li> </ul> |

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELC | ANSC7  | ANSC6  |        | _      | ANSC3  | ANSC2  | ANSC1  | ANSC0  | 107                 |

| LATC   | LATC7  | LATC6  | LATC5  | LATC4  | LATC3  | LATC2  | LATC1  | LATC0  | 106                 |

| PORTC  | RC7    | RC6    | RC5    | RC4    | RC3    | RC2    | RC1    | RC0    | 106                 |

| TRISC  | TRISC7 | TRISC6 | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 106                 |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

### 12.6 Register Definitions: Interrupt-on-Change Control

#### REGISTER 12-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0               | U-0                                     | R/W-0/0            | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |  |

|-------------------|-----------------------------------------|--------------------|---------|-------------------------------------------------------|---------|---------|---------|--|--|

| _                 | _                                       | IOCAP5             | IOCAP4  | IOCAP3                                                | IOCAP2  | IOCAP1  | IOCAP0  |  |  |

| bit 7             |                                         |                    |         |                                                       |         |         | bit 0   |  |  |

|                   |                                         |                    |         |                                                       |         |         |         |  |  |

| Legend:           |                                         |                    |         |                                                       |         |         |         |  |  |

| R = Readable bit  |                                         | W = Writable bi    | t       | U = Unimplemented bit, read as '0'                    |         |         |         |  |  |

| u = Bit is unchan | u = Bit is unchanged x = Bit is unknown |                    |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |  |

| '1' = Bit is set  |                                         | '0' = Bit is clear | ed      |                                                       |         |         |         |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 12-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

#### REGISTER 12-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| _     | _   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

| R/W-0/0                     | R/W-0/  | 0 R/W-0/0         | R/W-0/0         | U-0                         | U-0             | U-0                | U-0          |

|-----------------------------|---------|-------------------|-----------------|-----------------------------|-----------------|--------------------|--------------|

| TRIGSEL<3:0> <sup>(1)</sup> |         |                   |                 |                             |                 | _                  | _            |

| bit 7                       |         |                   |                 |                             |                 |                    | bit          |

| Legend:                     |         |                   |                 |                             |                 |                    |              |

| R = Readable                | hit     | W = Writable      | hit             | U = Unimplei                | mented bit, rea | d as '0'           |              |

|                             |         | x = Bit is unkr   |                 |                             |                 | DR/Value at all o  | thar Dooota  |

| u = Bit is uncl             | •       |                   |                 | -n/n = value                | al POR and BC   | JR/ value at all C | liner Resels |

| '1' = Bit is set            |         | '0' = Bit is cle  | ared            |                             |                 |                    |              |

|                             |         |                   |                 |                             | •               |                    |              |

| bit 7-4                     | TRIGSEL | -<3:0>: Auto-Conv | ersion Trigger  | Selection bits <sup>(</sup> | 1)              |                    |              |

|                             | 0000 =  | No auto-conversio | n trigger selec | ted                         |                 |                    |              |

|                             | 0001 =  | Reserved          |                 |                             |                 |                    |              |

|                             |         | Reserved          | (0)             |                             |                 |                    |              |

|                             |         | Timer0 - T0_overf |                 |                             |                 |                    |              |

|                             |         | Timer1 – T1_overf |                 |                             |                 |                    |              |

|                             | 0101 =  | Timer2 – T2_matc  | h               |                             |                 |                    |              |

|                             | 0110 =  | Reserved          |                 |                             |                 |                    |              |

|                             | 0111 =  | Reserved          |                 |                             |                 |                    |              |

|                             | 1000 =  | CLC1 – LC1_out    |                 |                             |                 |                    |              |

|                             | 1001 =  | CLC2 – LC2_out    |                 |                             |                 |                    |              |

|                             | 1010 =  | Reserved          |                 |                             |                 |                    |              |

|                             | 1011 =  | Reserved          |                 |                             |                 |                    |              |

|                             | 1100 =  | Reserved          |                 |                             |                 |                    |              |

|                             | 1101 =  | Reserved          |                 |                             |                 |                    |              |

|                             | 1110 =  | Reserved          |                 |                             |                 |                    |              |

|                             | 1111 =  | Reserved          |                 |                             |                 |                    |              |

| bit 3-0                     |         | mented: Read as ' |                 |                             |                 |                    |              |

### REGISTER 15-3: ADCON2: ADC CONTROL REGISTER 2

**Note 1:** This is a rising edge sensitive input for all sources.

**2:** Signal also sets its corresponding interrupt flag.

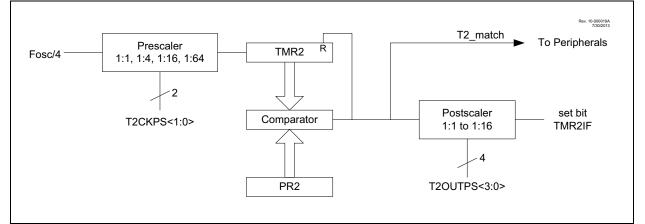

### 18.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4, 1:16, and 1:64)

- Software programmable postscaler (1:1 to 1:16)

- · Interrupt on TMR2 match with PR2

See Figure 18-1 for a block diagram of Timer2.

|                                                        |                                     | Rev 10-00020A<br>7/90/2013 |

|--------------------------------------------------------|-------------------------------------|----------------------------|

| Fosc/4                                                 |                                     |                            |

| Prescale                                               | 1:4                                 |                            |

|                                                        | 0.00                                |                            |

| PR2 \                                                  | 0x03                                |                            |

| TMR2 0x00 0x01 0x02                                    | 0x03                                | 0x00 0x01 0x02             |

| T2_match                                               | Pulse Width <sup>(1)</sup><br>◀   ► |                            |

| <b>Note 1:</b> The Pulse Width of T2_match is equal to | the scaled inpu                     | t of TMR2.                 |

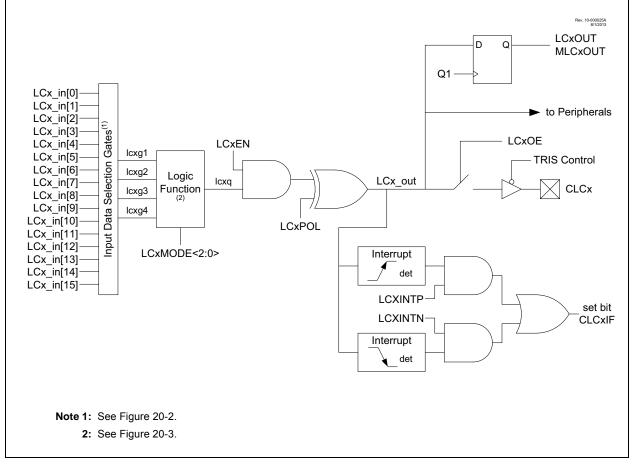

### 20.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) provides programmable logic that operates outside the speed limitations of software execution. The logic cell takes up to 16 input signals, and through the use of configurable gates, reduces the 16 inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

Refer to Figure 20-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

#### 20.1.2 DATA GATING

Outputs from the input multiplexers are directed to the desired logic function input through the data gating stage. Each data gate can direct any combination of the four selected inputs.

#### **Note:** Data gating is undefined at power-up.

The gate stage is more than just signal direction. The gate can be configured to direct each input signal as inverted or non-inverted data. Directed signals are ANDed together in each gate. The output of each gate can be inverted before going on to the logic function stage.

The gating is in essence a 1-to-4 input AND/NAND/OR/NOR gate. When every input is inverted and the output is inverted, the gate is an OR of all enabled data inputs. When the inputs and output are not inverted, the gate is an AND or all enabled inputs.

Table 20-2 summarizes the basic logic that can be obtained in gate 1 by using the gate logic select bits. The table shows the logic of four input variables, but each gate can be configured to use less than four. If no inputs are selected, the output will be zero or one, depending on the gate output polarity bit.

| TABLE 20-2: | <b>DATA GATING</b> | LOGIC |

|-------------|--------------------|-------|

|-------------|--------------------|-------|

| CLCxGLS0 | LCxG1POL | Gate Logic |

|----------|----------|------------|

| 0x55     | 1        | AND        |

| 0x55     | 0        | NAND       |

| 0xAA     | 1        | NOR        |

| 0xAA     | 0        | OR         |

| 0x00     | 0        | Logic 0    |

| 0x00     | 1        | Logic 1    |

It is possible (but not recommended) to select both the true and negated values of an input. When this is done, the gate output is zero, regardless of the other inputs, but may emit logic glitches (transient-induced pulses). If the output of the channel must be zero or one, the recommended method is to set all gate bits to zero and use the gate polarity bit to set the desired level.

Data gating is configured with the logic gate select registers as follows:

- Gate 1: CLCxGLS0 (Register 20-5)

- Gate 2: CLCxGLS1 (Register 20-6)

- Gate 3: CLCxGLS2 (Register 20-7)

- Gate 4: CLCxGLS3 (Register 20-8)

Register number suffixes are different than the gate numbers because other variations of this module have multiple gate selections in the same register. Data gating is indicated in the right side of Figure 20-2. Only one gate is shown in detail. The remaining three gates are configured identically with the exception that the data enables correspond to the enables for that gate.

#### 20.1.3 LOGIC FUNCTION

There are eight available logic functions including:

- AND-OR

- OR-XOR

- AND

- S-R Latch

- D Flip-Flop with Set and Reset

- D Flip-Flop with Reset

- J-K Flip-Flop with Reset

- · Transparent Latch with Set and Reset

Logic functions are shown in Figure 20-3. Each logic function has four inputs and one output. The four inputs are the four data gate outputs of the previous stage. The output is fed to the inversion stage and from there to other peripherals, an output pin, and back to the CLCx itself.

### 20.1.4 OUTPUT POLARITY

The last stage in the configurable logic cell is the output polarity. Setting the LCxPOL bit of the CLCxCON register inverts the output signal from the logic stage. Changing the polarity while the interrupts are enabled will cause an interrupt for the resulting output transition.

### 20.6 Register Definitions: CLC Control

#### REGISTER 20-1: CLCxCON: CONFIGURABLE LOGIC CELL CONTROL REGISTER

| R/W-0/0          | R/W-0/0                                   | R-0/0                                                                          | R/W-0/0          | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0     |  |

|------------------|-------------------------------------------|--------------------------------------------------------------------------------|------------------|-----------------|------------------|------------------|-------------|--|

| LCxEN            | LCxOE LCxOUT LCxINTP LCxINTN LCxMODE<2:0> |                                                                                |                  |                 |                  |                  | >           |  |

| bit 7            |                                           |                                                                                |                  |                 |                  |                  | bit 0       |  |

|                  |                                           |                                                                                |                  |                 |                  |                  |             |  |

| Legend:          |                                           |                                                                                |                  |                 |                  |                  |             |  |

| R = Readable     | bit                                       | W = Writable                                                                   | bit              | U = Unimpler    | mented bit, read | 1 as '0'         |             |  |

| u = Bit is unch  | anged                                     | x = Bit is unkr                                                                | nown             | -n/n = Value a  | at POR and BO    | R/Value at all o | ther Resets |  |

| '1' = Bit is set |                                           | '0' = Bit is cle                                                               | ared             |                 |                  |                  |             |  |

| bit 7            | LCxEN: Cont                               | figurable Logic                                                                | Cell Enable bi   | it              |                  |                  |             |  |

|                  | 1 = Configura                             | able logic cell i<br>able logic cell i                                         | s enabled and    | mixing input s  |                  |                  |             |  |

| bit 6            | LCxOE: Cont                               | figurable Logic                                                                | Cell Output E    | nable bit       |                  |                  |             |  |

|                  |                                           | able logic cell p                                                              |                  |                 |                  |                  |             |  |

|                  | -                                         | able logic cell p                                                              |                  |                 |                  |                  |             |  |

| bit 5            |                                           | nfigurable Logi                                                                |                  | •               |                  |                  |             |  |

|                  | •                                         | •                                                                              |                  | · ·             | d from lcx_out w |                  |             |  |

| bit 4            |                                           | • •                                                                            |                  | • •             | Interrupt Enable | e bit            |             |  |

|                  |                                           | will be set wher<br>will not be set                                            | n a rising edge  | e occurs on Icx | _out             |                  |             |  |

| bit 3            | LCxINTN: Co                               | onfigurable Log                                                                | ic Cell Negativ  | ve Edge Going   | Interrupt Enabl  | le bit           |             |  |

|                  |                                           | will be set wher                                                               | n a falling edge | e occurs on Ic> | c_out            |                  |             |  |

|                  |                                           | will not be set                                                                |                  |                 |                  |                  |             |  |

| bit 2-0          |                                           | 2:0>: Configura                                                                |                  |                 | ode bits         |                  |             |  |

|                  |                                           | 1-input transpo                                                                |                  | h S and R       |                  |                  |             |  |

|                  |                                           | 110 = Cell is J-K flip-flop with R<br>101 = Cell is 2-input D flip-flop with R |                  |                 |                  |                  |             |  |

|                  |                                           | 1-input D flip-f                                                               |                  | R               |                  |                  |             |  |

|                  | 011 = Cell is                             | • •                                                                            |                  |                 |                  |                  |             |  |

|                  | 010 = Cell is                             | •                                                                              |                  |                 |                  |                  |             |  |

|                  | 001 = Cell is<br>000 = Cell is            |                                                                                |                  |                 |                  |                  |             |  |

|                  |                                           | AND-UK                                                                         |                  |                 |                  |                  |             |  |

| R/W-x/u                   | R/W-x/u       | R/W-x/u                           | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|---------------------------|---------------|-----------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxG3D4T                  | LCxG3D4N      | LCxG3D3T                          | LCxG3D3N        | LCxG3D2T       | LCxG3D2N         | LCxG3D1T         | LCxG3D1N    |

| bit 7                     |               |                                   | •               |                |                  |                  | bit         |

| • • • •                   |               |                                   |                 |                |                  |                  |             |

| Legend:<br>R = Readable I | ait           | W = Writable                      | hit             | II – Unimplor  | nented bit, read | L ac. 'O'        |             |

|                           |               |                                   |                 | •              |                  |                  | thar Depata |

| u = Bit is uncha          | angeo         | x = Bit is unkr                   |                 | -n/n = value a | at POR and BO    | R/value at all c | iner Resets |

| '1' = Bit is set          |               | '0' = Bit is cle                  | ared            |                |                  |                  |             |

| bit 7                     | LCxG3D4T:     | Gate 3 Data 4 1                   | Frue (non-invei | rted) bit      |                  |                  |             |

|                           |               | gated into lcxo                   |                 | ,              |                  |                  |             |

|                           | 0 = Icxd4T is | not gated into                    | lcxg3           |                |                  |                  |             |

| bit 6                     | LCxG3D4N:     | Gate 3 Data 4                     | Negated (inver  | rted) bit      |                  |                  |             |

|                           | 1 = Icxd4N is | gated into Icx                    | g3              |                |                  |                  |             |

|                           | 0 = Icxd4N is | not gated into                    | lcxg3           |                |                  |                  |             |

| bit 5                     | LCxG3D3T: G   | Gate 3 Data 3 1                   | Frue (non-invei | rted) bit      |                  |                  |             |

|                           |               | gated into lcxg                   |                 |                |                  |                  |             |

|                           | 0 = Icxd3T is | not gated into                    | lcxg3           |                |                  |                  |             |

| bit 4                     |               | Gate 3 Data 3                     | •               | rted) bit      |                  |                  |             |

|                           |               | gated into Icx                    |                 |                |                  |                  |             |

|                           |               | not gated into                    | •               |                |                  |                  |             |

| bit 3                     |               | Gate 3 Data 2 1                   |                 | rted) bit      |                  |                  |             |

|                           |               | gated into lcxg                   |                 |                |                  |                  |             |

| 1.11.0                    |               | not gated into                    | •               |                |                  |                  |             |

| bit 2                     |               | Gate 3 Data 2                     | •               | rted) bit      |                  |                  |             |

|                           |               | gated into lcxg<br>not gated into |                 |                |                  |                  |             |

| bit 1                     |               | Gate 3 Data 1 1                   | •               | rtad) bit      |                  |                  |             |

|                           |               | gated into lcxc                   |                 | neu) bii       |                  |                  |             |

|                           |               | not gated into                    |                 |                |                  |                  |             |

| bit 0                     |               | Gate 3 Data 1                     | •               | rted) hit      |                  |                  |             |

| Situ                      |               | gated into lcx                    | •               |                |                  |                  |             |

|                           | 0 = lcxd1N is |                                   |                 |                |                  |                  |             |

#### REGISTER 20-7: CLCxGLS2: GATE 3 LOGIC SELECT REGISTER

#### REGISTER 21-3: NCOxACCL: NCOx ACCUMULATOR REGISTER – LOW BYTE

| R/W-0/0      | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|--------------|---------|---------|---------|---------|---------|---------|---------|

| NCOxACC<7:0> |         |         |         |         |         |         |         |

| bit 7        |         |         |         |         |         |         |         |

|              |         |         |         |         |         |         |         |

### Legend:

| _ogona.              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 NCOxACC<7:0>: NCOx Accumulator, Low Byte

#### REGISTER 21-4: NCOxACCH: NCOx ACCUMULATOR REGISTER – HIGH BYTE

| R/W-0/0       | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|---------------|---------|---------|---------|---------|---------|---------|---------|--|

| NCOxACC<15:8> |         |         |         |         |         |         |         |  |

| bit 7         |         |         |         |         |         |         | bit 0   |  |

|               |         |         |         |         |         |         |         |  |

| Legend:       |         |         |         |         |         |         |         |  |

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-0 NCOxACC<15:8>: NCOx Accumulator, High Byte

#### REGISTER 21-5: NCOxACCU: NCOx ACCUMULATOR REGISTER – UPPER BYTE

| U-0         | U-0 | U-0 | U-0 | R/W-0/0        | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|-------------|-----|-----|-----|----------------|---------|---------|---------|--|

| —           | —   | —   | —   | NCOxACC<19:16> |         |         |         |  |

| bit 7 bit 0 |     |     |     |                |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCOxACC<19:16>: NCOx Accumulator, Upper Byte

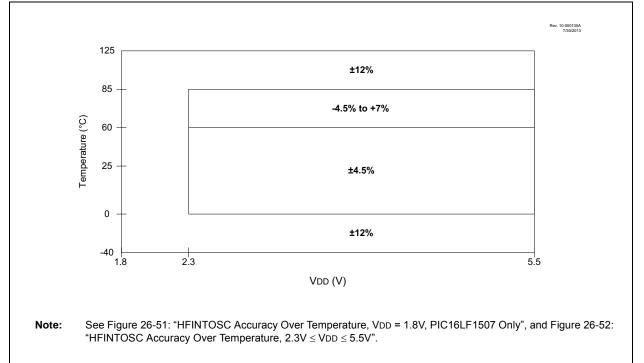

#### TABLE 25-8: OSCILLATOR PARAMETERS

| Standard Operating Conditions (unless otherwise stated) |           |                                                          |                    |      |      |      |       |                                        |

|---------------------------------------------------------|-----------|----------------------------------------------------------|--------------------|------|------|------|-------|----------------------------------------|

| Param.<br>No.                                           | Sym.      | Characteristic                                           | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                             |

| OS08                                                    | HFosc     | Internal Calibrated HFINTOSC<br>Frequency <sup>(1)</sup> | ±2%                |      | 16.0 |      | MHz   | VDD = 3.0V, TA = 25°C,<br>(Note 2)     |

| OS09                                                    | LFosc     | Internal LFINTOSC Frequency                              | —                  | _    | 31   | _    | kHz   | (Note 3)                               |

| OS10*                                                   | TIOSC ST  | HFINTOSC<br>Wake-up from Sleep Start-up Time             | -                  | _    | 5    | 15   | μS    |                                        |

| OS10A*                                                  | TLFOSC ST | LFINTOSC<br>Wake-up from Sleep Start-up Time             | —                  |      | 0.5  | _    | ms    | $-40^\circ C \le T A \le +125^\circ C$ |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

2: See Figure 25-6: "HFINTOSC Frequency Accuracy over Device VDD and Temperature", Figure 26-51: "HFINTOSC Accuracy Over Temperature, VDD = 1.8V, PIC16LF1507 Only", and Figure 26-52: "HFINTOSC Accuracy Over Temperature, 2.3V ≤ VDD ≤ 5.5V".

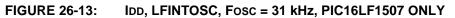

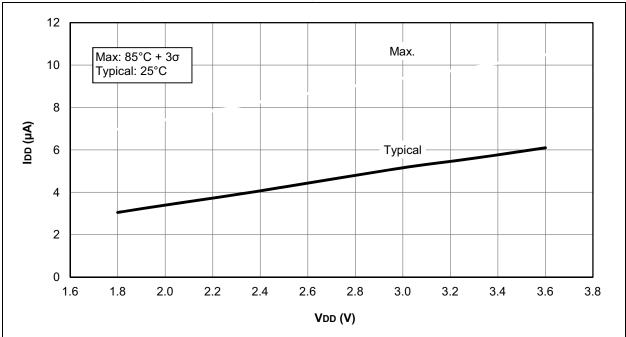

3: See Figure 26-49: "LFINTOSC Frequency over VDD and Temperature, PIC16LF1507 Only", and Figure 26-50: "LFINTOSC Frequency over VDD and Temperature, PIC16F1507".

#### FIGURE 25-6: HFINTOSC FREQUENCY ACCURACY OVER VDD AND TEMPERATURE

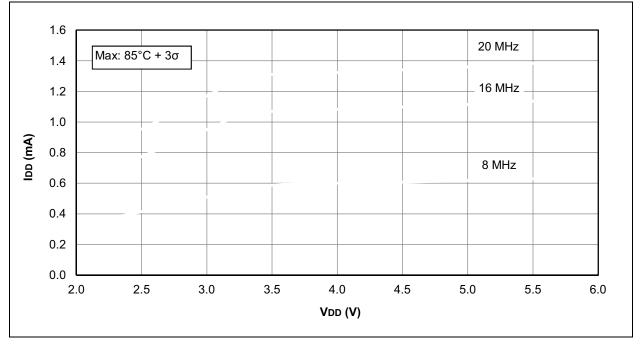

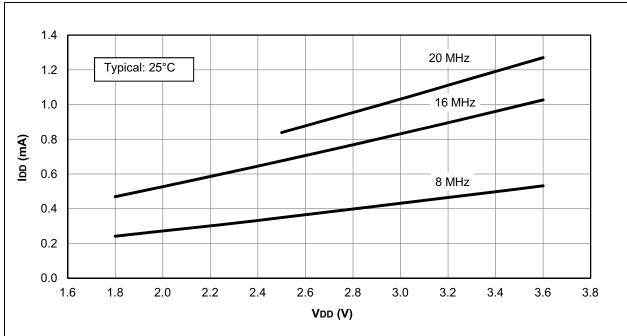

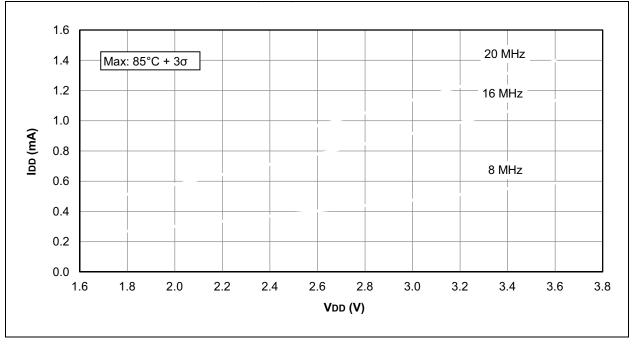

FIGURE 26-10: IDD MAXIMUM, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16LF1507 ONLY

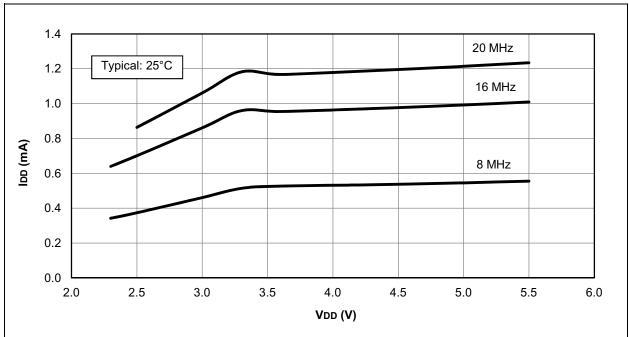

FIGURE 26-11: IDD TYPICAL, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16F1507 ONLY

FIGURE 26-12: IDD MAXIMUM, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16F1507 ONLY