Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 17                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 12x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 20-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1507-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Peripheral Features (Continued):**

- Two Configurable Logic Cell (CLC) modules:

- 16 selectable input source signals

- Four inputs per module

- Software control of combinational/sequential logic/state/clock functions

- Numerically Controlled Oscillator (NCO):

- 20-bit accumulator

- 16-bit increment

- True linear frequency control

- High-speed clock input

- Selectable Output modes

- Fixed Duty Cycle (FDC) mode

- Pulse Frequency (PF) mode

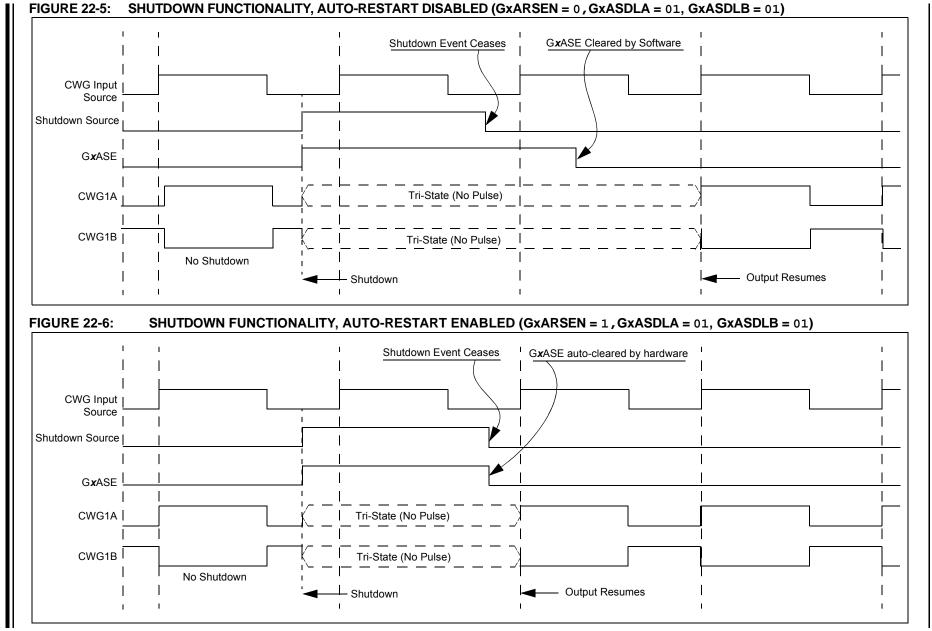

- · Complementary Waveform Generator (CWG):

- Eight selectable signal sources

- Selectable falling and rising edge dead-band \_ control

- Polarity control \_

- Four auto-shutdown sources

- Multiple input sources: PWM, CLC, NCO

| PIC12(L)F1501/PIC16(L)F150X FAMILY TYPES |

|------------------------------------------|

|------------------------------------------|

| Device        | Data Sheet Index | Program Memory<br>Flash (words) | Data SRAM<br>(bytes) | ا/O،s <sup>(2)</sup> | 10-bit ADC (ch) | Comparators | DAC | Timers<br>(8/16-bit) | MWA | EUSART | MSSP (I <sup>2</sup> C/SPI) | CWG | СГС | NCO | Debug <sup>(1)</sup> | XLP |

|---------------|------------------|---------------------------------|----------------------|----------------------|-----------------|-------------|-----|----------------------|-----|--------|-----------------------------|-----|-----|-----|----------------------|-----|

| PIC12(L)F1501 | (1)              | 1024                            | 64                   | 6                    | 4               | 1           | 1   | 2/1                  | 4   |        |                             | 1   | 2   | 1   | Н                    | —   |

| PIC16(L)F1503 | (2)              | 2048                            | 128                  | 12                   | 8               | 2           | 1   | 2/1                  | 4   | _      | 1                           | 1   | 2   | 1   | Н                    |     |

| PIC16(L)F1507 | (3)              | 2048                            | 128                  | 18                   | 12              | _           |     | 2/1                  | 4   | -      | -                           | 1   | 2   | 1   | Н                    | —   |

| PIC16(L)F1508 | (4)              | 4096                            | 256                  | 18                   | 12              | 2           | 1   | 2/1                  | 4   | 1      | 1                           | 1   | 4   | 1   | I/H                  | Y   |

| PIC16(L)F1509 | (4)              | 8192                            | 512                  | 18                   | 12              | 2           | 1   | 2/1                  | 4   | 1      | 1                           | 1   | 4   | 1   | I/H                  | Y   |

Note 1: Debugging Methods: (I) - Integrated on Chip; (H) - using Debug Header; (E) - using Emulation Header. One pin is input-only. 2:

Data Sheet Index: (Unshaded devices are described in this document.)

- 1: DS40001615 PIC12(L)F1501 Data Sheet, 8-Pin Flash, 8-bit Microcontrollers.

- 2: DS40001607

PIC16(L)F1503 Data Sheet, 14-Pin Flash, 8-bit Microcontrollers. PIC16(L)F1507 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers.

3: DS40001586

4: DS40001609 PIC16(L)F1508/9 Data Sheet, 20-Pin Flash, 8-bit Microcontrollers.

Note: For other small form-factor package availability and marking information, please visit http://www.microchip.com/packaging or contact your local sales office.

| Name                             | Function | Input<br>Type | Output<br>Type | Description                                           |

|----------------------------------|----------|---------------|----------------|-------------------------------------------------------|

| RA0/AN0/ICSPDAT                  | RA0      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | AN0      | AN            | _              | A/D Channel input.                                    |

|                                  | ICSPDAT  | ST            | CMOS           | ICSP™ Data I/O.                                       |

| RA1/AN1/VREF+/ICSPCLK            | RA1      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | AN1      | AN            |                | A/D Channel input.                                    |

|                                  | VREF+    | AN            |                | A/D Positive Voltage Reference input.                 |

|                                  | ICSPCLK  | ST            |                | Serial Programming Clock.                             |

| RA2/AN2/T0CKI/INT/PWM3/          | RA2      | ST            | CMOS           | General purpose I/O.                                  |

| CLC1 <sup>(1)</sup> /CWG1FLT     | AN2      | AN            |                | A/D Channel input.                                    |

|                                  | TOCKI    | ST            |                | Timer0 clock input.                                   |

|                                  | INT      | ST            |                | External interrupt.                                   |

|                                  | PWM3     |               | CMOS           | Pulse Width Module source output.                     |

|                                  | CLC1     | —             | CMOS           | Configurable Logic Cell source output.                |

|                                  | CWG1FLT  | ST            | —              | Complementary Waveform Generator Fault input.         |

| RA3/CLC1IN0/VPP/MCLR             | RA3      | TTL           |                | General purpose input.                                |

|                                  | CLC1IN0  | ST            |                | Configurable Logic Cell source input.                 |

|                                  | Vpp      | HV            |                | Programming voltage.                                  |

|                                  | MCLR     | ST            |                | Master Clear with internal pull-up.                   |

| RA4/AN3/CLKOUT/T1G               | RA4      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | AN3      | AN            |                | A/D Channel input.                                    |

|                                  | CLKOUT   | _             | CMOS           | Fosc/4 output.                                        |

|                                  | T1G      | ST            |                | Timer1 Gate input.                                    |

| RA5/CLKIN/T1CKI/NCO1CLK          | RA5      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | CLKIN    | CMOS          |                | External clock input (EC mode).                       |

|                                  | T1CKI    | ST            | —              | Timer1 clock input.                                   |

|                                  | NCO1CLK  | ST            |                | Numerically Controlled Oscillator Clock source input. |

| RB4/AN10                         | RB4      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | AN10     | AN            | —              | A/D Channel input.                                    |

| RB5/AN11                         | RB5      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | AN11     | AN            |                | A/D Channel input.                                    |

| RB6                              | RB6      | TTL           | CMOS           | General purpose I/O.                                  |

| RB7                              | RB7      | TTL           | CMOS           | General purpose I/O.                                  |

| RC0/AN4/CLC2                     | RC0      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | AN4      | AN            |                | A/D Channel input.                                    |

|                                  | CLC2     |               | CMOS           | Configurable Logic Cell source output.                |

| RC1/AN5/PWM4/NCO1 <sup>(1)</sup> | RC1      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | AN5      | AN            | —              | A/D Channel input.                                    |

|                                  | PWM4     | —             | CMOS           | Pulse Width Module source output.                     |

|                                  | NCO1     | —             | CMOS           | Numerically Controlled Oscillator is source output.   |

| RC2/AN6                          | RC2      | TTL           | CMOS           | General purpose I/O.                                  |

|                                  | AN6      | AN            | _              | A/D Channel input.                                    |

TABLE 1-2. PIC16(L)F1507 PINOUT DESCRIPTION

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$  HV = High Voltage XTAL = Crystal levels

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

| Address            | Name       | Bit 7         | Bit 6                    | Bit 5          | Bit 4          | Bit 3                   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

|--------------------|------------|---------------|--------------------------|----------------|----------------|-------------------------|---------|---------|---------|----------------------|---------------------------------|

| Bank 0             |            |               |                          |                |                |                         |         |         | •       | •                    |                                 |

| 00Ch               | PORTA      | _             | —                        | RA5            | RA4            | RA3                     | RA2     | RA1     | RA0     | xx xxxx              | xx xxxx                         |

| 00Dh               | PORTB      | RB7           | RB6                      | RB5            | RB4            | _                       | _       | _       | _       | xxxx                 | xxxx                            |

| 00Eh               | PORTC      | RC7           | RC6                      | RC5            | RC4            | RC3                     | RC2     | RC1     | RC0     | xxxx xxxx            | xxxx xxxx                       |

| 010h               | _          | Unimplemen    | ted                      |                |                |                         |         |         |         | _                    | _                               |

| 011h               | PIR1       | TMR1GIF       | ADIF                     | _              | _              | _                       | _       | TMR2IF  | TMR1IF  | 0000                 | 0000                            |

| 012h               | PIR2       | —             | _                        | —              |                |                         | NCO1IF  |         | _       | 0                    | 0                               |

| 013h               | PIR3       | —             | _                        | —              |                |                         | _       | CLC2IF  | CLC1IF  | 00                   | 00                              |

| 014h               |            | Unimplement   | ted                      |                |                |                         |         |         |         | —                    | —                               |

| 015h               | TMR0       | Holding Regi  | ster for the 8-          | bit Timer0 Co  | ount           |                         |         |         |         | xxxx xxxx            | uuuu uuuu                       |

| 016h               | TMR1L      | Holding Regi  | ster for the Le          | east Significa | nt Byte of the | e 16-bit TMR            | 1 Count |         |         | xxxx xxxx            | uuuu uuuu                       |

| 017h               | TMR1H      | Holding Regi  | ster for the M           | ost Significar | nt Byte of the | 16-bit TMR1             | Count   |         |         | xxxx xxxx            | uuuu uuuu                       |

| 018h               | T1CON      | TMR1C         | S<1:0>                   | T1CKP          | S<1:0>         |                         | T1SYNC  |         | TMR10N  | 0000 -0-0            | uuuu -u-u                       |

| 019h               | T1GCON     | TMR1GE        | T1GPOL                   | T1GTM          | T1GSPM         | T <u>1GGO</u> /<br>DONE | T1GVAL  |         | T1GSS0  | 0000 0x-0            | uuuu ux-u                       |

| 01Ah               | TMR2       | Timer2 Modu   | imer2 Module Register    |                |                |                         |         |         |         | 0000 0000            | 0000 0000                       |

| 01Bh               | PR2        | Timer2 Perio  | d Register               |                |                |                         |         |         |         | 1111 1111            | 1111 1111                       |

| 01Ch               | T2CON      | —             |                          | T2OUTF         | PS<3:0>        |                         | TMR2ON  | T2CK    | PS<1:0> | -000 0000            | -000 0000                       |

| 01Dh<br>to<br>01Fh | _          | Unimplemen    | Unimplemented            |                |                |                         |         |         |         | _                    | _                               |

| Bank 1             |            |               |                          |                |                |                         |         |         |         |                      |                                 |

| 08Ch               | TRISA      | —             | _                        | TRISA5         | TRISA4         | (2)                     | TRISA2  | TRISA1  | TRISA0  | 11 1111              | 11 1111                         |

| 08Dh               | TRISB      | TRISB7        | TRISB6                   | TRISB5         | TRISB4         | —                       | —       | —       | —       | 1111                 | 1111                            |

| 08Eh               | TRISC      | TRISC7        | TRISC6                   | TRISC5         | TRISC4         | TRISC3                  | TRISC2  | TRISC1  | TRISC0  | 1111 1111            | 1111 1111                       |

| 08Fh               |            | Unimplement   | ted                      |                |                |                         |         |         |         |                      | _                               |

| 090h               | _          | Unimplement   | ted                      | 1              |                |                         | 1       | -       | r       | —                    | —                               |

| 091h               | PIE1       | TMR1GIE       | ADIE                     | —              | —              | —                       | —       | TMR2IE  | TMR1IE  | 0000                 | 0000                            |

| 092h               | PIE2       | —             | —                        | —              | —              | —                       | NCO1IE  | —       | —       | 0                    | 0                               |

| 093h               | PIE3       | —             | —                        | —              | —              | —                       | —       | CLC2IE  | CLC1IE  | 00                   | 00                              |

| 094h               | _          | Unimplement   | ted                      | 1              | -              | -                       | 1       |         |         | _                    | —                               |

| 095h               | OPTION_REG | WPUEN         | INTEDG                   | TMR0CS         | TMR0SE         | PSA                     |         | PS<2:0> |         | 1111 1111            | 1111 1111                       |

| 096h               | PCON       | STKOVF        | STKUNF                   | —              | RWDT           | RMCLR                   | RI      | POR     | BOR     | 00-1 11qq            | qq-q qquu                       |

| 097h               | WDTCON     | —             | —                        |                |                | WDTPS<4:0               | >       |         | SWDTEN  | 01 0110              | 01 0110                         |

| 098h               | _          | Unimplemented |                          |                |                |                         |         |         | _       | —                    |                                 |

| 099h               | OSCCON     | —             |                          | IRCF           | <3:0>          |                         | —       | SCS     | S<1:0>  | -011 1-00            | -011 1-00                       |

| 09Ah               | OSCSTAT    | —             | —                        | —              | HFIOFR         | —                       | —       | LFIOFR  | HFIOFS  | 000                  | ddd                             |

| 09Bh               | ADRESL     | ADC Result I  | C Result Register Low xx |                |                |                         |         |         |         | xxxx xxxx            | uuuu uuuu                       |

| 09Ch               | ADRESH     | ADC Result I  | It Register High         |                |                |                         |         |         |         | xxxx xxxx            | uuuu uuuu                       |

| 09Dh               | ADCON0     | _             |                          |                | CHS<4:0>       |                         |         | GO/DONE | ADON    | -000 0000            | -000 0000                       |

| 09Eh               | ADCON1     | ADFM          |                          | ADCS<2:0>      |                | _                       | —       | ADPR    | EF<1:0> | 000000               | 000000                          |

|                    |            |               | TRIGSE                   |                |                |                         |         |         |         |                      |                                 |

#### SPECIAL FUNCTION REGISTER SUMMARY **TABLE 3-5**:

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16F1507 only.

2:

Unimplemented, read as '1'.

## 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

## 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

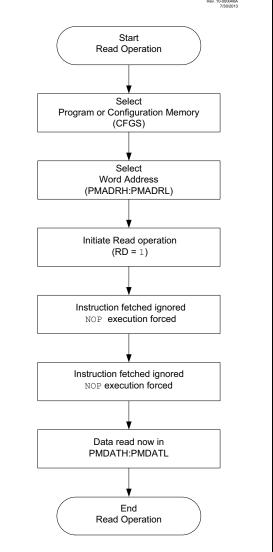

## 10.2.1 READING THE FLASH PROGRAM MEMORY

To read a program memory location, the user must:

- 1. Write the desired address to the PMADRH:PMADRL register pair.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Then, set control bit RD of the PMCON1 register.

Once the read control bit is set, the program memory Flash controller will use the second instruction cycle to read the data. This causes the second instruction immediately following the "BSF PMCON1, RD" instruction to be ignored. The data is available in the very next cycle, in the PMDATH:PMDATL register pair; therefore, it can be read as two bytes in the following instructions.

PMDATH:PMDATL register pair will hold this value until another read or until it is written to by the user.

| Note: | The two instructions following a program    |

|-------|---------------------------------------------|

|       | memory read are required to be NOPs.        |

|       | This prevents the user from executing a     |

|       | 2-cycle instruction on the next instruction |

|       | after the RD bit is set.                    |

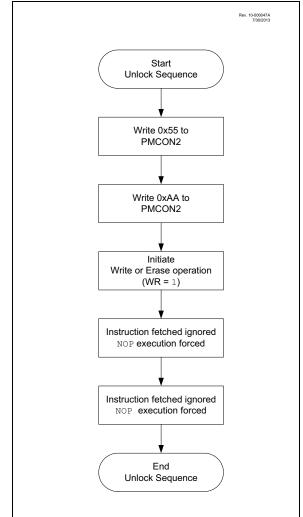

### 10.2.2 FLASH MEMORY UNLOCK SEQUENCE

The unlock sequence is a mechanism that protects the Flash program memory from unintended self-write programming or erasing. The sequence must be executed and completed without interruption to successfully complete any of the following operations:

- Row Erase

- · Load program memory write latches

- Write of program memory write latches to program memory

- Write of program memory write latches to User IDs

The unlock sequence consists of the following steps:

- 1. Write 55h to PMCON2

- 2. Write AAh to PMCON2

- 3. Set the WR bit in PMCON1

- 4. NOP instruction

- 5. NOP instruction

Once the WR bit is set, the processor will always force two NOP instructions. When an Erase Row or Program Row operation is being performed, the processor will stall internal operations (typical 2 ms), until the operation is complete and then resume with the next instruction. When the operation is loading the program memory write latches, the processor will always force the two NOP instructions and continue uninterrupted with the next instruction.

Since the unlock sequence must not be interrupted, global interrupts should be disabled prior to the unlock sequence and re-enabled after the unlock sequence is completed.

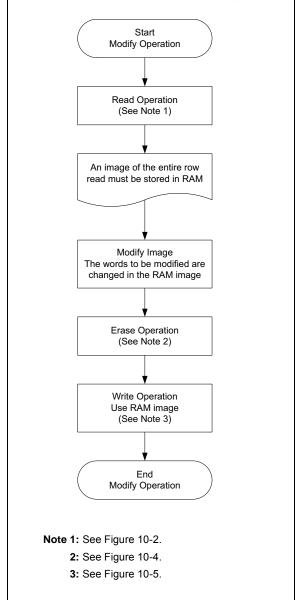

## FIGURE 10-3: FLASH PROGRAM

## MEMORY UNLOCK SEQUENCE FLOWCHART

## 10.3 Modifying Flash Program Memory

When modifying existing data in a program memory row, and data within that row must be preserved, it must first be read and saved in a RAM image. Program memory is modified using the following steps:

- 1. Load the starting address of the row to be modified.

- 2. Read the existing data from the row into a RAM image.

- 3. Modify the RAM image to contain the new data to be written into program memory.

- 4. Load the starting address of the row to be rewritten.

- 5. Erase the program memory row.

- 6. Load the write latches with data from the RAM image.

- 7. Initiate a programming operation.

## FIGURE 10-7: FLASH PROGRAM MEMORY MODIFY FLOWCHART

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELA | _      | _      | _      | ANSA4  | —      | ANSA2  | ANSA1  | ANSA0  | 99                  |

| INTCON | GIE    | PEIE   | TMR0IE | INTE   | IOCIE  | TMR0IF | INTF   | IOCIF  | 64                  |

| IOCAF  | _      | _      | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 110                 |

| IOCAN  | —      | _      | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 110                 |

| IOCAP  | —      | _      | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 110                 |

| IOCBF  | IOCBF7 | IOCBF6 | IOCBF5 | IOCBF4 | _      | _      | _      | _      | 111                 |

| IOCBN  | IOCBN7 | IOCBN6 | IOCBN5 | IOCBN4 | —      | —      | _      | —      | 111                 |

| IOCBP  | IOCBP7 | IOCBP6 | IOCBP5 | IOCBP4 | _      | _      | _      | _      | 111                 |

| TRISA  | _      | _      | TRISA5 | TRISA4 | —(1)   | TRISA2 | TRISA1 | TRISA0 | 98                  |

| TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | _      | _      | _      | _      | 102                 |

### TABLE 12-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

Note 1: Unimplemented, read as '1'.

#### 16.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A software programmable prescaler is available for exclusive use with Timer0. The prescaler is enabled by clearing the PSA bit of the OPTION\_REG register.

| Note: | The Watchdog Timer (WDT) uses its own |

|-------|---------------------------------------|

|       | independent prescaler.                |

There are eight prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION\_REG register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be disabled by setting the PSA bit of the OPTION\_REG register.

The prescaler is not readable or writable. All instructions writing to the TMR0 register will clear the prescaler.

## 16.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The TMR0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The TMR0IF bit can only be cleared in software. The Timer0 interrupt enable is the TMR0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the    |

|-------|-----------------------------------------|

|       | processor from Sleep since the timer is |

|       | frozen during Sleep.                    |

## 16.1.5 8-BIT COUNTER MODE SYNCHRONIZATION

When in 8-Bit Counter mode, the incrementing edge on the T0CKI pin must be synchronized to the instruction clock. Synchronization can be accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the instruction clock. The high and low periods of the external clocking source must meet the timing requirements as shown in **Section 25.0 "Electrical Specifications"**.

## 16.1.6 OPERATION DURING SLEEP

Timer0 cannot operate while the processor is in Sleep mode. The contents of the TMR0 register will remain unchanged while the processor is in Sleep mode.

## 17.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

## 17.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 17.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 17.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

## 17.5 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

### 17.5.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register. When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 17-3 for timing details.

### TABLE 17-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| 1          | 0      | 0   | Counts           |

| 1          | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 17.5.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 17-4. Source selection is controlled by the T1GSS<1:0> bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

### TABLE 17-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 0     | Timer1 Gate pin (T1G)                                                 |

| 1     | Overflow of Timer0 (T0_overflow)<br>(TMR0 increments from FFh to 00h) |

**Note 1:** Optionally synchronized comparator output.

### 19.1.5 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 19-4.

## EQUATION 19-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + I)]}{\log(2)}$$

bits

**Note:** If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TABLE 19-1: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

|-------------|---------------------------------------------------------|

|-------------|---------------------------------------------------------|

| PWM Frequency             | 0.31 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 19-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 0.31 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 64       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

## 19.1.6 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

### 19.1.7 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency (Fosc). Any changes in the system clock frequency will result in changes to the PWM frequency. Refer to for additional details.

### 19.1.8 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWM registers to their Reset states.

DS40001586D-page 183

Status

© 2011-2015 Microchip Technology Inc

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                    |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |  |  |  |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                     |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                                              |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |

| IORLW            | Inclusive OR literal with W                                                                                        |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                           |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the 8-bit literal 'k'. The<br>result is placed in the W register. |  |  |  |  |

| INCF             | Increment f                                                                                                                                                               |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                 |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                         |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |  |  |

| TABLE 25-3: | POWER-DOWN CURRENTS (IPD) <sup>(1,2)</sup> |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| PIC16LF1   | Operating Conditions: (unless otherwise stated)<br>Low-Power Sleep Mode |                                  |       |       |        |       |            |                                                                 |  |

|------------|-------------------------------------------------------------------------|----------------------------------|-------|-------|--------|-------|------------|-----------------------------------------------------------------|--|

| PIC16F1507 |                                                                         | Low-Power Sleep Mode, VREGPM = 1 |       |       |        |       |            |                                                                 |  |

| Param.     |                                                                         |                                  |       | Max.  | Max.   |       | Conditions |                                                                 |  |

| No.        | Device Characteristics                                                  | Min.                             | Тур†  | +85°C | +125°C | Units | Vdd        | Note                                                            |  |

| D022       | Base IPD                                                                | —                                | 0.020 | 1.0   | 8.0    | μA    | 1.8        | WDT, BOR, FVR and SOSC                                          |  |

|            |                                                                         | -                                | 0.025 | 2.0   | 9.0    | μA    | 3.0        | disabled, all Peripherals inactive                              |  |

| D022       | Base IPD                                                                | _                                | 0.25  | 3.0   | 10     | μA    | 2.3        | WDT, BOR, FVR and SOSC                                          |  |

|            |                                                                         | —                                | 0.30  | 4.0   | 12     | μA    | 3.0        | disabled, all Peripherals inactive,                             |  |

|            |                                                                         | —                                | 0.40  | 6.0   | 15     | μA    | 5.0        | Low-Power Sleep mode                                            |  |

| D022A      | Base IPD                                                                | _                                | 9.8   | 16    | 18     | μA    | 2.3        | WDT, BOR, FVR and SOSC                                          |  |

|            |                                                                         | _                                | 10.3  | 18    | 20     | μA    | 3.0        | disabled, all Peripherals inactive,<br>Normal-Power Sleep mode, |  |

|            |                                                                         | —                                | 11.5  | 21    | 26     | μA    | 5.0        | VREGPM = 0                                                      |  |

| D023       |                                                                         | _                                | 0.26  | 2.0   | 9.0    | μA    | 1.8        | WDT Current                                                     |  |

|            |                                                                         | —                                | 0.44  | 3.0   | 10     | μA    | 3.0        | ]                                                               |  |

| D023       |                                                                         | —                                | 0.43  | 6.0   | 15     | μA    | 2.3        | WDT Current                                                     |  |

|            |                                                                         | _                                | 0.53  | 7.0   | 20     | μA    | 3.0        |                                                                 |  |

|            |                                                                         | —                                | 0.64  | 8.0   | 22     | μA    | 5.0        |                                                                 |  |

| D023A      |                                                                         | —                                | 15    | 28    | 30     | μA    | 1.8        | FVR Current                                                     |  |

|            |                                                                         | -                                | 18    | 30    | 33     | μA    | 3.0        |                                                                 |  |

| D023A      |                                                                         | —                                | 18    | 33    | 35     | μA    | 2.3        | FVR Current                                                     |  |

|            |                                                                         | _                                | 19    | 35    | 37     | μA    | 3.0        |                                                                 |  |

|            |                                                                         | —                                | 20    | 37    | 39     | μA    | 5.0        |                                                                 |  |

| D024       |                                                                         | —                                | 6.0   | 17    | 20     | μA    | 3.0        | BOR Current                                                     |  |

| D024       |                                                                         |                                  | 7.0   | 17    | 30     | μA    | 3.0        | BOR Current                                                     |  |

|            |                                                                         |                                  | 8.0   | 20    | 40     | μA    | 5.0        |                                                                 |  |

| D24A       |                                                                         | —                                | 0.1   | 4.0   | 10     | μA    | 3.0        | LPBOR Current                                                   |  |

| D24A       |                                                                         |                                  | 0.35  | 5.0   | 14     | μA    | 3.0        | LPBOR Current                                                   |  |

|            |                                                                         | —                                | 0.45  | 8.0   | 17     | μA    | 5.0        |                                                                 |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral △ current can be determined by subtracting the base IPD current from this limit. Max. values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to Vss.

**3:** ADC clock source is FRC.

## 25.4 AC Characteristics

Timing Parameter Symbology has been created with one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Т      |                                       |     |                |

|--------|---------------------------------------|-----|----------------|

| F      | Frequency                             | Т   | Time           |

| Lowerc | case letters (pp) and their meanings: |     |                |

| рр     |                                       |     |                |

| сс     | CCP1                                  | OSC | CLKIN          |

| ck     | CLKOUT                                | rd  | RD             |

| cs     | CS                                    | rw  | RD or WR       |

| di     | SDIx                                  | sc  | SCKx           |

| do     | SDO                                   | SS  | SS             |

| dt     | Data in                               | t0  | TOCKI          |

| io     | I/O PORT                              | t1  | T1CKI          |

| mc     | MCLR                                  | wr  | WR             |

| Upperc | case letters and their meanings:      |     |                |

| S      |                                       |     |                |

| F      | Fall                                  | Р   | Period         |

| Н      | High                                  | R   | Rise           |

| I      | Invalid (High-impedance)              | V   | Valid          |

| L      | Low                                   | Z   | High-impedance |

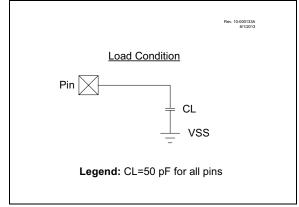

## FIGURE 25-4: LOAD CONDITIONS

## TABLE 25-14: ADC CONVERSION REQUIREMENTS

| Param.<br>No. | Sym. | Characteristic                                                     | Min. | Тур†                      | Max. | Units | Conditions                                   |

|---------------|------|--------------------------------------------------------------------|------|---------------------------|------|-------|----------------------------------------------|

| AD130*        | TAD  | ADC Clock Period (TADC)                                            | 1.0  | —                         | 6.0  | μS    | Fosc-based                                   |

|               |      | ADC Internal FRC Oscillator Period (TFRC)                          | 1.0  | 2.0                       | 6.0  | μS    | ADCS<2:0> = x11 (ADC FRC mode)               |

| AD131         | TCNV | Conversion Time<br>(not including Acquisition Time) <sup>(1)</sup> | —    | 11                        | —    | Tad   | Set GO/DONE bit to conversion complete       |

| AD132*        | TACQ | Acquisition Time                                                   | _    | 5.0                       | _    | μS    |                                              |

| AD133*        | THCD | Holding Capacitor Disconnect Time                                  | _    | 1/2 TAD<br>1/2 TAD + 1TCY | _    |       | Fosc-based<br>ADCS<2:0> = x11 (ADC FRC mode) |

These parameters are characterized but not tested.

t Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The ADRES register may be read on the following TCY cycle.

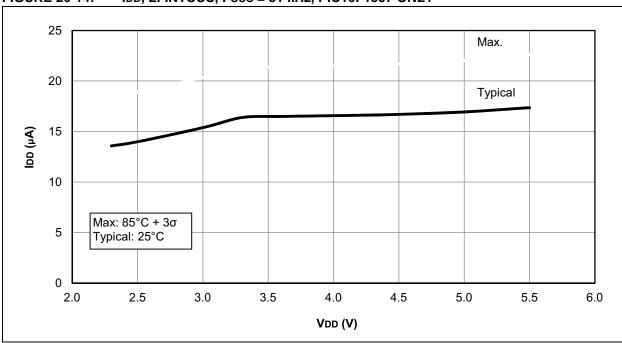

FIGURE 26-6: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16LF1507 ONLY

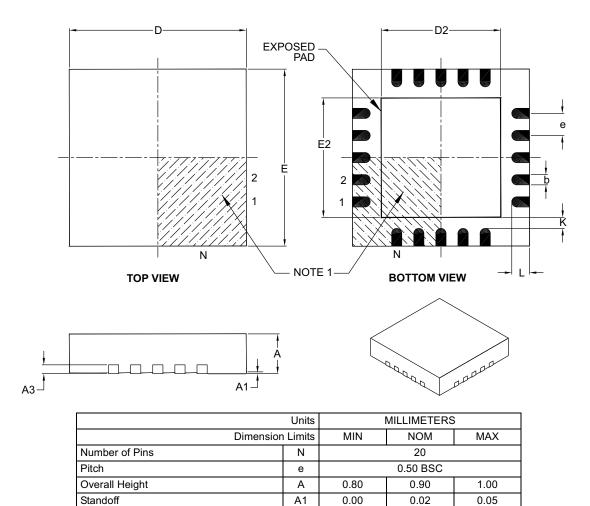

## 20-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

A3

Е

E2

D

D2

b

L

Κ

2.60

2.60

0.18

0.30

0.20

0.20 REF

4.00 BSC

2.70

4.00 BSC

2.70

0.25

0.40

| Notes: |  |

|--------|--|

|--------|--|

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

**Contact Thickness**

Exposed Pad Width

Exposed Pad Length

Contact-to-Exposed Pad

Overall Width

**Overall Length**

Contact Width

Contact Length

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-126B

2.80

2.80

0.30

0.50