# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 17                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                              |

| Data Converters            | A/D 12x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 20-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1507-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

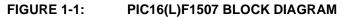

The block diagram of these devices are shown in Figure 1-1, the available peripherals are shown in Table 1-1, and the pinout descriptions are shown in Table 1-2.

TABLE 1-1: DEVICE PERIPHERAL SUMMARY

| Peripheral                                                               |              | PIC12(L)F1501 | PIC16(L)F1503 | PIC16(L)F1507 | PIC16(L)F1508 | PIC16(L)F1509 |

|--------------------------------------------------------------------------|--------------|---------------|---------------|---------------|---------------|---------------|

| Analog-to-Digital Converter (A                                           | -            | •             | •             | •             | •             | •             |

| Complementary Wave Genera                                                |              | •             | •             | •             | •             | •             |

| Digital-to-Analog Converter (I                                           | DAC)         | •             | •             |               | •             | •             |

| Enhanced Universal<br>Synchronous/Asynchronous  <br>Transmitter (EUSART) | Receiver/    |               |               |               | •             | •             |

| Fixed Voltage Reference (FV                                              | R)           | •             | •             | •             | •             | •             |

| Numerically Controlled Oscill                                            | ator (NCO)   | •             | •             | •             | •             | •             |

| Temperature Indicator                                                    | •            | ٠             | •             | ٠             | •             |               |

| Comparators                                                              |              |               |               |               |               |               |

|                                                                          | C1           | •             | ٠             |               | •             | •             |

|                                                                          | C2           |               | •             |               | •             | •             |

| Configurable Logic Cell (CLC                                             | -            |               |               |               |               |               |

|                                                                          | CLC1         | •             | •             | •             | •             | •             |

|                                                                          | CLC2         | •             | •             | •             | •             | •             |

|                                                                          | CLC3         |               |               |               | •             | •             |

|                                                                          | CLC4         |               |               |               | •             | •             |

| Master Synchronous Serial P                                              | orts         |               |               | 1             |               |               |

|                                                                          | MSSP1        |               | •             |               | •             | •             |

| PWM Modules                                                              | n            |               |               | 1             |               |               |

|                                                                          | PWM1         | •             | •             | •             | •             | •             |

|                                                                          | PWM2         | •             | •             | •             | •             | •             |

|                                                                          | PWM3<br>PWM4 | •             | •             | •             | •             | •             |

|                                                                          | •            | •             | •             | •             | •             |               |

| Timers                                                                   | I            |               |               | 1             |               |               |

|                                                                          | Timer0       | •             | •             | •             | •             | •             |

|                                                                          | Timer1       | •             | •             | •             | •             | •             |

|                                                                          | Timer2       | •             | •             | •             | •             | •             |

#### **TABLE 1-2:** PIC16(L)F1507 PINOUT DESCRIPTION (CONTINUED)

| Name                           | Function | Input<br>Type | Output<br>Type | Description                                      |

|--------------------------------|----------|---------------|----------------|--------------------------------------------------|

| RC3/AN7/PWM2/CLC2IN0           | RC3      | TTL           | CMOS           | General purpose I/O.                             |

|                                | AN7      | AN            | —              | A/D Channel input.                               |

|                                | PWM2     | —             | CMOS           | Pulse Width Module source output.                |

|                                | CLC2IN0  | ST            | _              | Configurable Logic Cell source input.            |

| RC4/CLC2IN1/CWG1B              | RC4      | TTL           | CMOS           | General purpose I/O.                             |

|                                | CLC2IN1  | ST            | —              | Configurable Logic Cell source input.            |

|                                | CWG1B    | —             | CMOS           | CWG complementary output.                        |

| RC5/PWM1/CLC1 <sup>(1)</sup> / | RC5      | TTL           | CMOS           | General purpose I/O.                             |

| CWG1A                          | PWM1     | —             | CMOS           | PWM output.                                      |

|                                | CLC1     | —             | CMOS           | Configurable Logic Cell source output.           |

|                                | CWG1A    | —             | CMOS           | CWG primary output.                              |

| RC6/AN8/NCO1 <sup>(1)</sup>    | RC6      | TTL           | CMOS           | General purpose I/O.                             |

|                                | AN8      | AN            | —              | A/D Channel input.                               |

|                                | NCO1     | _             | CMOS           | Numerically Controlled Oscillator source output. |

| RC7/AN9/CLC1IN1                | RC7      | TTL           | CMOS           | General purpose I/O.                             |

|                                | AN8      | AN            | _              | A/D Channel input.                               |

|                                | CLC1IN1  | ST            | _              | Configurable Logic Cell source input.            |

| Vdd                            | Vdd      | Power         | _              | Positive supply.                                 |

| Vss                            | Vss      | Power         |                | Ground reference.                                |

TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels  $I^2C^{TM}$  = Schmitt Trigger input with  $I^2C$ HV = High Voltage levels

XTAL = Crystal

Note 1: Alternate pin function selected with the APFCON (Register 11-1) register.

#### TABLE 6-5: SUMMARY OF REGISTERS ASSOCIATED WITH RESETS

| Name   | Bit 7  | Bit 6  | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|--------|--------|--------|------------|-------|-------|-------|-------|--------|---------------------|

| BORCON | SBOREN | BORFS  |            |       |       | _     | _     | BORRDY | 53                  |

| PCON   | STKOVF | STKUNF | _          | RWDT  | RMCLR | RI    | POR   | BOR    | 57                  |

| STATUS | _      |        | _          | TO    | PD    | Z     | DC    | С      | 17                  |

| WDTCON |        | —      | WDTPS<4:0> |       |       |       |       | SWDTEN | 77                  |

**Legend:** — = unimplemented bit, reads as '0'. Shaded cells are not used by Resets.

#### TABLE 6-6: SUMMARY OF CONFIGURATION WORD WITH RESETS

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

| CONFIG1 | 13:8 |         |         |          |          | CLKOUTEN | BOREI    | N<1:0>  | _       | 20                  |

| CONFIGI | 7:0  | CP      | MCLRE   | PWRTE    | WD       | TE<1:0>  | _        | FOSC    | <1:0>   | 38                  |

|         | 13:8 | _       | _       | LVP      | DEBUG    | LPBOR    | BORV     | STVREN  | _       | 20                  |

| CONFIG2 | 7:0  |         | _       |          | _        |          | _        | WRT     | <1:0>   | 39                  |

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by Resets.

# 8.0 POWER-DOWN MODE (SLEEP)

The Power-down mode is entered by executing a **SLEEP** instruction.

Upon entering Sleep mode, the following conditions exist:

- 1. WDT will be cleared but keeps running, if enabled for operation during Sleep.

- 2. PD bit of the STATUS register is cleared.

- 3.  $\overline{\text{TO}}$  bit of the STATUS register is set.

- 4. CPU clock is disabled.

- 5. 31 kHz LFINTOSC is unaffected and peripherals that operate from it may continue operation in Sleep.

- 6. Timer1 and peripherals that operate from Timer1 continue operation in Sleep when the Timer1 clock source selected is:

- LFINTOSC

- T1CKI

- 7. ADC is unaffected, if the dedicated FRC oscillator is selected.

- 8. I/O ports maintain the status they had before SLEEP was executed (driving high, low or highimpedance).

- 9. Resets other than WDT are not affected by Sleep mode.

Refer to individual chapters for more details on peripheral operation during Sleep.

To minimize current consumption, the following conditions should be considered:

- · I/O pins should not be floating

- External circuitry sinking current from I/O pins

- Internal circuitry sourcing current from I/O pins

- Current draw from pins with internal weak pull-ups

- Modules using 31 kHz LFINTOSC

- CWG, NCO and CLC modules using HFINTOSC

I/O pins that are high-impedance inputs should be pulled to VDD or Vss externally to avoid switching currents caused by floating inputs.

Examples of internal circuitry that might be sourcing current include the FVR module. See **Section 13.0 "Fixed Voltage Reference (FVR)"** for more information on this module.

#### 8.1 Wake-up from Sleep

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin, if enabled

- 2. BOR Reset, if enabled

- 3. POR Reset

- 4. Watchdog Timer, if enabled

- 5. Any external interrupt

- 6. Interrupts by peripherals capable of running during Sleep (see individual peripheral for more information)

The first three events will cause a device Reset. The last three events are considered a continuation of program execution. To determine whether a device Reset or wake-up event occurred, refer to Section 6.12 "Determining the Cause of a Reset".

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be enabled. Wake-up will occur regardless of the state of the GIE bit. If the GIE bit is disabled, the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is enabled, the device executes the instruction after the SLEEP instruction, the device will then call the Interrupt Service Routine. In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

### 8.1.1 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP.

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared.

- If the interrupt occurs **during or after** the execution of a SLEEP instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

| TABLE 9-3: | SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER |

|------------|-----------------------------------------------------|

| IADLE 3-3. | SUMMART OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER |

| Name   | Bit 7  | Bit 6          | Bit 5     | Bit 4 | Bit 3 | Bit 2  | Bit 1    | Bit 0 | Register<br>on Page |

|--------|--------|----------------|-----------|-------|-------|--------|----------|-------|---------------------|

| OSCCON | —      |                | IRCF<3:0> |       |       |        | SCS<1:0> |       | 49                  |

| PCON   | STKOVF | STKUNF         | —         | RWDT  | RMCLR | RI     | POR      | BOR   | 57                  |

| STATUS | —      | —              | _         | TO    | PD    | Z      | DC       | С     | 17                  |

| WDTCON | _      | — WDTPS<4:0> S |           |       |       | SWDTEN | 77       |       |                     |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Watchdog Timer.

#### TABLE 9-4: SUMMARY OF CONFIGURATION WORD WITH WATCHDOG TIMER

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1 | Bit 8/0 | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|---------|---------|---------------------|

|         | 13:8 | _       | —       |          | —        | CLKOUTEN | BORE     | N<1:0>  | —       | 20                  |

| CONFIG1 | 7:0  | CP      | MCLRE   | PWRTE    | WDT      | E<1:0>   | _        | FOSC    | <1:0>   | 38                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by Watchdog Timer.

# 11.6 Register Definitions: PORTB

### REGISTER 11-7: PORTB: PORTB REGISTER

| R/W-x/x                                 | R/W-x/x | R/W-x/x      | R/W-x/x | U-0                                                   | U-0 | U-0 | U-0   |  |

|-----------------------------------------|---------|--------------|---------|-------------------------------------------------------|-----|-----|-------|--|

| RB7                                     | RB6     | RB5          | RB4     |                                                       | —   | —   | —     |  |

| bit 7                                   |         |              |         |                                                       |     |     | bit 0 |  |

|                                         |         |              |         |                                                       |     |     |       |  |

| Legend:                                 |         |              |         |                                                       |     |     |       |  |

| R = Readable I                          | bit     | W = Writable | bit     | U = Unimplemented bit, read as '0'                    |     |     |       |  |

| u = Bit is unchanged x = Bit is unknown |         |              | nown    | -n/n = Value at POR and BOR/Value at all other Resets |     |     |       |  |

| '1' = Bit is set '0' = Bit is cleared   |         |              | ared    |                                                       |     |     |       |  |

| bit 7-4 | RB<7:4>: PORTB I/O Value bits <sup>(1)</sup> |

|---------|----------------------------------------------|

|         | 1 = Port pin is <u>&gt;</u> Vін              |

|         | 0 = Port pin is <u>&lt;</u> VIL              |

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

#### REGISTER 11-8: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | RB<7:4>: PORTB Tri-State Control bits             |

|---------|---------------------------------------------------|

|         | 1 = PORTB pin configured as an input (tri-stated) |

|         | 0 = PORTB pin configured as an output             |

|         |                                                   |

bit 3-0 Unimplemented: Read as '0'

### 12.6 Register Definitions: Interrupt-on-Change Control

#### REGISTER 12-1: IOCAP: INTERRUPT-ON-CHANGE PORTA POSITIVE EDGE REGISTER

| U-0                                                                                           | U-0 | R/W-0/0            | R/W-0/0 | R/W-0/0       | R/W-0/0            | R/W-0/0 | R/W-0/0 |

|-----------------------------------------------------------------------------------------------|-----|--------------------|---------|---------------|--------------------|---------|---------|

| _                                                                                             | _   | IOCAP5             | IOCAP4  | IOCAP3        | IOCAP2             | IOCAP1  | IOCAP0  |

| bit 7                                                                                         |     |                    |         |               |                    |         |         |

|                                                                                               |     |                    |         |               |                    |         |         |

| Legend:                                                                                       |     |                    |         |               |                    |         |         |

| R = Readable bit                                                                              |     | W = Writable bi    | t       | U = Unimpleme | ented bit, read as | '0'     |         |

| u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets |     |                    |         |               |                    |         | Resets  |

| '1' = Bit is set                                                                              |     | '0' = Bit is clear | ed      |               |                    |         |         |

bit 7-6 Unimplemented: Read as '0'

bit 5-0

bit 5-0

bit 5-0

IOCAP<5:0>: Interrupt-on-Change PORTA Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-2: IOCAN: INTERRUPT-ON-CHANGE PORTA NEGATIVE EDGE REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | _   | IOCAN5  | IOCAN4  | IOCAN3  | IOCAN2  | IOCAN1  | IOCAN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

IOCAN<5:0>: Interrupt-on-Change PORTA Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCAFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin.

### REGISTER 12-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

| U-0   | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 |

|-------|-----|------------|------------|------------|------------|------------|------------|

| —     | _   | IOCAF5     | IOCAF4     | IOCAF3     | IOCAF2     | IOCAF1     | IOCAF0     |

| bit 7 |     |            |            |            |            |            | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS - Bit is set in hardware                           |

bit 7-6 Unimplemented: Read as '0'

IOCAF<5:0>: Interrupt-on-Change PORTA Flag bits

1 = An enabled change was detected on the associated pin.

Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

0 = No change was detected, or the user cleared the detected change.

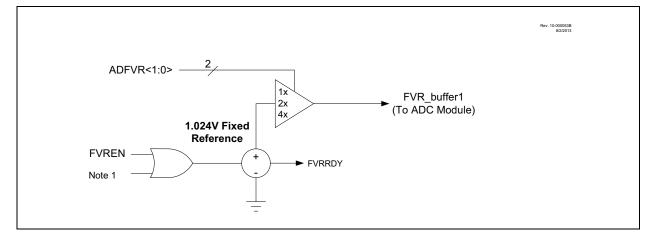

# 13.0 FIXED VOLTAGE REFERENCE (FVR)

The Fixed Voltage Reference (FVR) is a stable voltage reference, independent of VDD, with a nominal output level (VFVR) of 1.024V. The output of the FVR can be configured to supply a reference voltage to the following:

ADC input channel

The FVR can be enabled by setting the FVREN bit of the FVRCON register.

### 13.1 Independent Gain Amplifier

The output of the FVR supplied to the peripherals, (listed above), is routed through a programmable gain amplifier. Each amplifier can be programmed for a gain of 1x, 2x or 4x, to produce the three possible voltage levels.

The ADFVR<1:0> bits of the FVRCON register are used to enable and configure the gain amplifier settings for the reference supplied to the ADC module. Reference **Section 15.0 "Analog-to-Digital Converter (ADC) Module**" for additional information.

To minimize current consumption when the FVR is disabled, the FVR buffers should be turned off by clearing the Buffer Gain Selection bits.

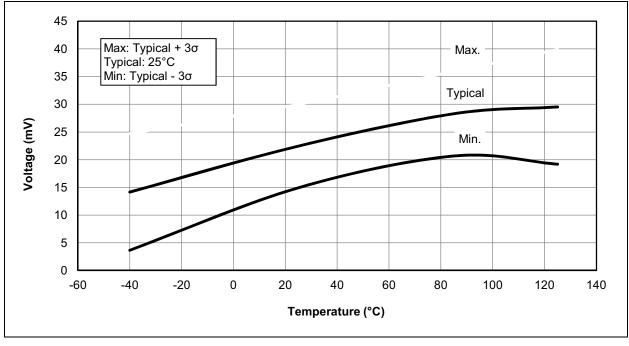

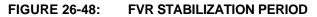

# 13.2 FVR Stabilization Period

When the Fixed Voltage Reference module is enabled, it requires time for the reference and amplifier circuits to stabilize. Once the circuits stabilize and are ready for use, the FVRRDY bit of the FVRCON register will be set. See the FVR Stabilization Period characterization graph, Figure 26-48.

#### TABLE 13-1: PERIPHERALS REQUIRING THE FIXED VOLTAGE REFERENCE (FVR)

| Peripheral | Conditions                                                  | Description                                                        |

|------------|-------------------------------------------------------------|--------------------------------------------------------------------|

| HFINTOSC   | FOSC<2:0> = 010 and<br>IRCF<3:0> = 000x                     | INTOSC is active and device is not in Sleep.                       |

|            | BOREN<1:0> = 11                                             | BOR always enabled.                                                |

| BOR        | BOREN<1:0> = 10 and BORFS = 1                               | BOR disabled in Sleep mode, BOR Fast Start enabled.                |

|            | BOREN<1:0> = 01 and BORFS = 1                               | BOR under software control, BOR Fast Start enabled.                |

| LDO        | All PIC16F1507 devices, when<br>VREGPM = 1 and not in Sleep | The device runs off of the Low-Power Regulator when in Sleep mode. |

# 13.3 Register Definitions: FVR Control

#### REGISTER 13-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0            | ) R-q/q                                   | R/W-0/0                                                    | R/W-0/0                            | U-0                                | U-0                                                | R/W-0/0                 | R/W-0/0              |

|--------------------|-------------------------------------------|------------------------------------------------------------|------------------------------------|------------------------------------|----------------------------------------------------|-------------------------|----------------------|

| FVREN <sup>(</sup> | <sup>1)</sup> FVRRDY <sup>(2)</sup>       | TSEN <sup>(3)</sup>                                        | TSRNG <sup>(3)</sup>               | _                                  | —                                                  | ADFVR                   | <1:0> <sup>(1)</sup> |

| bit 7              |                                           |                                                            |                                    |                                    |                                                    |                         | bit 0                |

|                    |                                           |                                                            |                                    |                                    |                                                    |                         |                      |

| Legend:            |                                           |                                                            |                                    |                                    |                                                    |                         |                      |

| R = Reada          | ıble bit                                  | W = Writable                                               | bit                                | U = Unimpler                       | mented bit, read                                   | as '0'                  |                      |

| u = Bit is u       | nchanged                                  | x = Bit is unki                                            | nown                               | -n/n = Value a                     | at POR and BO                                      | R/Value at all o        | ther Resets          |

| '1' = Bit is s     | set                                       | '0' = Bit is cle                                           | ared                               | q = Value de                       | pends on conditi                                   | on                      |                      |

| bit 7              | 1 = Fixed Vo                              | d Voltage Refe<br>Itage Referenc<br>Itage Referenc         | e is enabled                       | bit <sup>(1)</sup>                 |                                                    |                         |                      |

| bit 6              | 1 = Fixed Vo                              | ed Voltage Re<br>Itage Referenc<br>Itage Referenc          | e output is rea                    | ady for use                        | enabled                                            |                         |                      |

| bit 5              | 1 = Tempera                               | erature Indicato<br>ture Indicator is<br>ture Indicator is | s enabled                          | )                                  |                                                    |                         |                      |

| bit 4              | 1 = VOUT = V                              | perature Indica<br>′DD - 4V⊤ (High<br>′DD - 2V⊤ (Low       | Range)                             | lection bit <sup>(3)</sup>         |                                                    |                         |                      |

| bit 3-2            | Unimplemen                                | ted: Read as '                                             | 0'                                 |                                    |                                                    |                         |                      |

| bit 1-0            | 11 = ADC FV<br>10 = ADC FV<br>01 = ADC FV | R Buffer Gain                                              | is 4x, with out<br>is 2x, with out | put voltage = 4<br>put voltage = 2 | x Vfvr (4.096V<br>x Vfvr (2.048V<br>x Vfvr (1.024V | nominal) <sup>(4)</sup> |                      |

|                    | To minimize curren                        | •                                                          |                                    | R is disabled, tl                  | ne FVR buffers s                                   | should be turne         | ed off by clear-     |

- 2: FVRRDY is always '1' for the PIC16F1507 devices.

- 3: See Section 14.0 "Temperature Indicator Module" for additional information.

- 4: Fixed Voltage Reference output cannot exceed VDD.

#### TABLE 13-2: SUMMARY OF REGISTERS ASSOCIATED WITH THE FIXED VOLTAGE REFERENCE

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG | -     |       | ADFV  | R<1:0> | 114                 |

Legend: Shaded cells are unused by the Fixed Voltage Reference module.

### 16.2 Register Definitions: Option Register

| R/W-1/1         | R/W-1/1                   | R/W-1/1                               | R/W-1/1         | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |

|-----------------|---------------------------|---------------------------------------|-----------------|----------------|------------------|------------------|--------------|--|--|

| WPUEN           | INTEDG                    | TMR0CS                                | TMR0SE          | PSA            |                  | PS<2:0>          |              |  |  |

| bit 7           | ·                         |                                       |                 |                |                  |                  | bit (        |  |  |

|                 |                           |                                       |                 |                |                  |                  |              |  |  |

| Legend:         |                           |                                       |                 |                |                  |                  |              |  |  |

| R = Readabl     | le bit                    | W = Writable                          | bit             |                | mented bit, read |                  |              |  |  |

| u = Bit is und  | changed                   | x = Bit is unk                        | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is se | et                        | '0' = Bit is cle                      | ared            |                |                  |                  |              |  |  |

|                 |                           |                                       |                 |                |                  |                  |              |  |  |

| bit 7           |                           | ak Pull-Up Ena                        |                 |                |                  |                  |              |  |  |

|                 |                           | pull-ups are dis<br>Il-ups are enab   | · · ·           | •              | ,                |                  |              |  |  |

| bit 6           | •                         | errupt Edge Se                        | •               |                | values           |                  |              |  |  |

|                 |                           | on rising edge                        |                 |                |                  |                  |              |  |  |

|                 |                           | on falling edge                       |                 |                |                  |                  |              |  |  |

| bit 5           | TMR0CS: Tir               | mer0 Clock Sou                        | urce Select bit |                |                  |                  |              |  |  |

|                 |                           | n on T0CKI pin                        |                 |                |                  |                  |              |  |  |

|                 |                           | nstruction cycle                      |                 | 4)             |                  |                  |              |  |  |

| bit 4           |                           | TMR0SE: Timer0 Source Edge Select bit |                 |                |                  |                  |              |  |  |

|                 |                           | nt on high-to-lov<br>nt on low-to-hig |                 |                |                  |                  |              |  |  |

| bit 3           |                           | ler Assignment                        |                 | TOCKI pili     |                  |                  |              |  |  |

| DIL D           |                           | r is not assigne                      |                 | 0 module       |                  |                  |              |  |  |

|                 |                           | r is assigned to                      |                 |                |                  |                  |              |  |  |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pre | escaler Rate Se                       | elect bits      |                |                  |                  |              |  |  |

|                 | Bit                       | Value Timer0                          | Rate            |                |                  |                  |              |  |  |

|                 | (                         | 000 1:2                               |                 |                |                  |                  |              |  |  |

|                 |                           | 001 1:4                               |                 |                |                  |                  |              |  |  |

|                 |                           | 010 1:8<br>011 1:1                    |                 |                |                  |                  |              |  |  |

|                 |                           | 100 1:3                               |                 |                |                  |                  |              |  |  |

|                 | 1                         | 101 1:6                               | 4               |                |                  |                  |              |  |  |

### REGISTER 16-1: OPTION\_REG: OPTION REGISTER

#### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

1:128

1:256

110

111

| Name       | Bit 7       | Bit 6          | Bit 5        | Bit 4   | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |  |

|------------|-------------|----------------|--------------|---------|-------|--------|---------|--------|---------------------|--|

| ADCON2     |             | TRIGS          | EL<3:0>      |         | _     | _      | _       | -      | 125                 |  |

| INTCON     | GIE         | PEIE           | TMR0IE       | INTE    | IOCIE | TMR0IF | INTF    | IOCIF  | 64                  |  |

| OPTION_REG | WPUEN       | INTEDG         | TMR0CS       | TMR0SE  | PSA   |        | PS<2:0> |        | 133                 |  |

| TMR0       | Holding Reg | gister for the | 8-bit Timer0 | ) Count |       |        |         |        |                     |  |

| TRISA      | _           | _              | TRISA5       | TRISA4  | _(1)  | TRISA2 | TRISA1  | TRISA0 | 98                  |  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module. \* Page provides register information.

Note 1: Unimplemented, read as '1'.

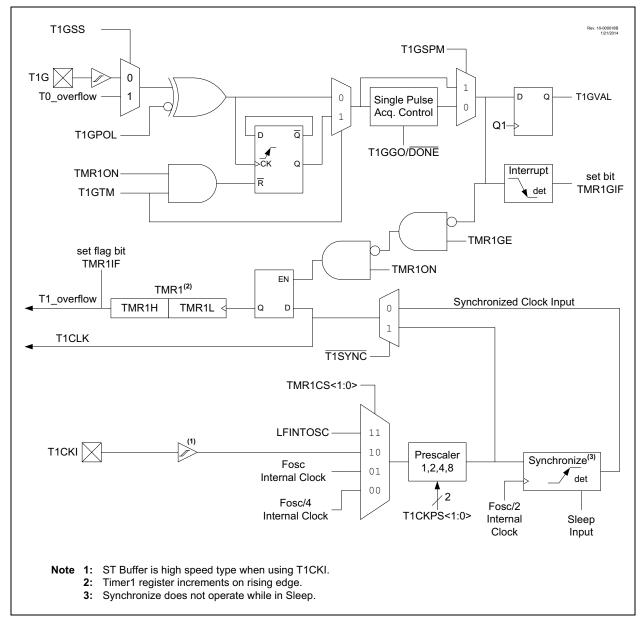

# 17.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- · 2-bit prescaler

- · Optionally synchronized comparator out

- Multiple Timer1 gate (count enable) sources

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- ADC Auto-Conversion Trigger(s)

- · Selectable Gate Source Polarity

- · Gate Toggle mode

- · Gate Single-Pulse mode

- Gate Value Status

- · Gate Event Interrupt

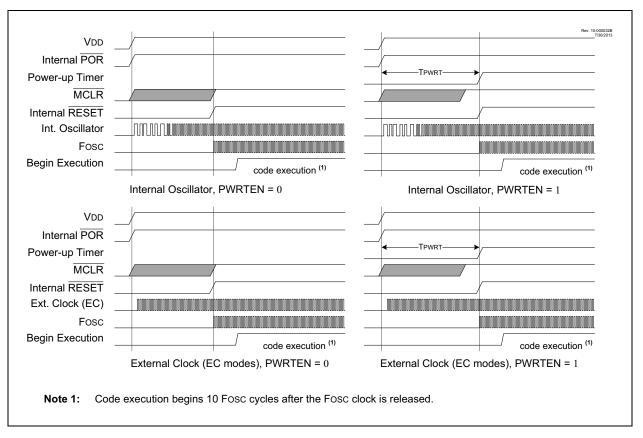

Figure 17-1 is a block diagram of the Timer1 module.

### FIGURE 17-1: TIMER1 BLOCK DIAGRAM

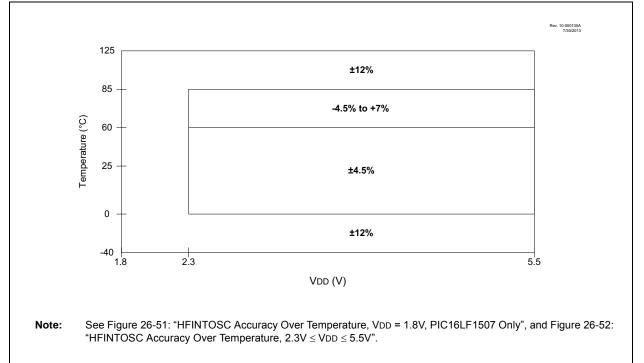

#### TABLE 25-8: OSCILLATOR PARAMETERS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                          |                    |      |      |      |       |                                           |  |  |  |

|---------------|---------------------------------------------------------|----------------------------------------------------------|--------------------|------|------|------|-------|-------------------------------------------|--|--|--|

| Param.<br>No. | Sym.                                                    | Characteristic                                           | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                |  |  |  |

| OS08          | HFosc                                                   | Internal Calibrated HFINTOSC<br>Frequency <sup>(1)</sup> | ±2%                |      | 16.0 |      | MHz   | VDD = 3.0V, TA = 25°C,<br>(Note 2)        |  |  |  |

| OS09          | LFosc                                                   | Internal LFINTOSC Frequency                              | —                  | _    | 31   | _    | kHz   | (Note 3)                                  |  |  |  |

| OS10*         | TIOSC ST                                                | HFINTOSC<br>Wake-up from Sleep Start-up Time             | -                  | _    | 5    | 15   | μS    |                                           |  |  |  |

| OS10A*        | TLFOSC ST                                               | LFINTOSC<br>Wake-up from Sleep Start-up Time             | —                  |      | 0.5  |      | ms    | $-40^{\circ}C \leq TA \leq +125^{\circ}C$ |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

2: See Figure 25-6: "HFINTOSC Frequency Accuracy over Device VDD and Temperature", Figure 26-51: "HFINTOSC Accuracy Over Temperature, VDD = 1.8V, PIC16LF1507 Only", and Figure 26-52: "HFINTOSC Accuracy Over Temperature, 2.3V ≤ VDD ≤ 5.5V".

3: See Figure 26-49: "LFINTOSC Frequency over VDD and Temperature, PIC16LF1507 Only", and Figure 26-50: "LFINTOSC Frequency over VDD and Temperature, PIC16F1507".

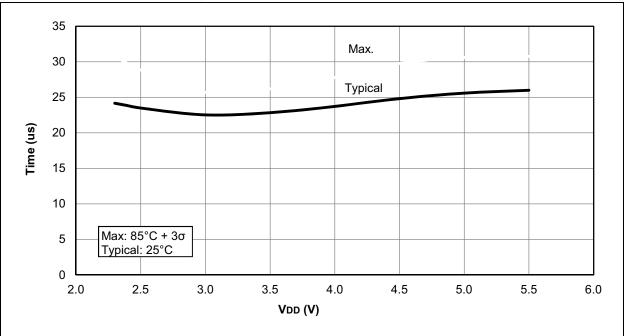

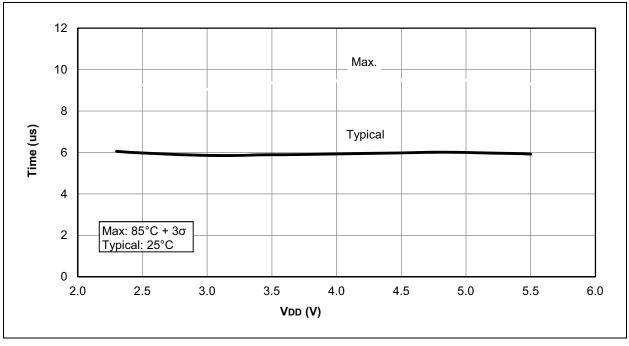

#### FIGURE 25-6: HFINTOSC FREQUENCY ACCURACY OVER VDD AND TEMPERATURE

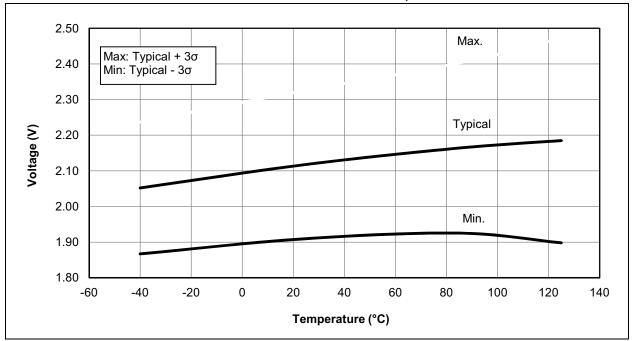

# 26.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "MAXIMUM", "Max.", "MINIMUM" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

FIGURE 26-55: SLEEP MODE, WAKE PERIOD WITH HFINTOSC SOURCE, VREGPM = 0, PIC16F1507 ONLY

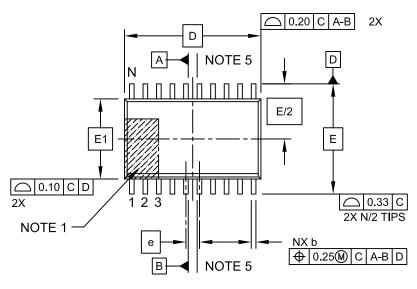

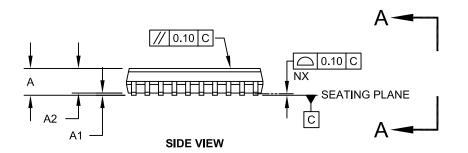

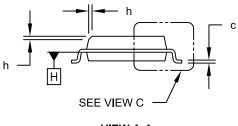

# 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2