#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

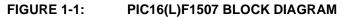

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

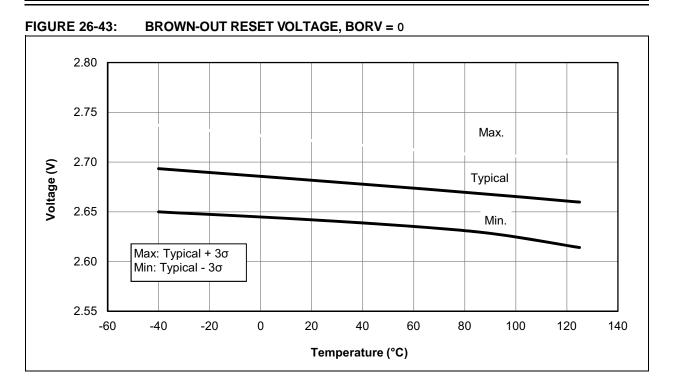

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f1507t-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

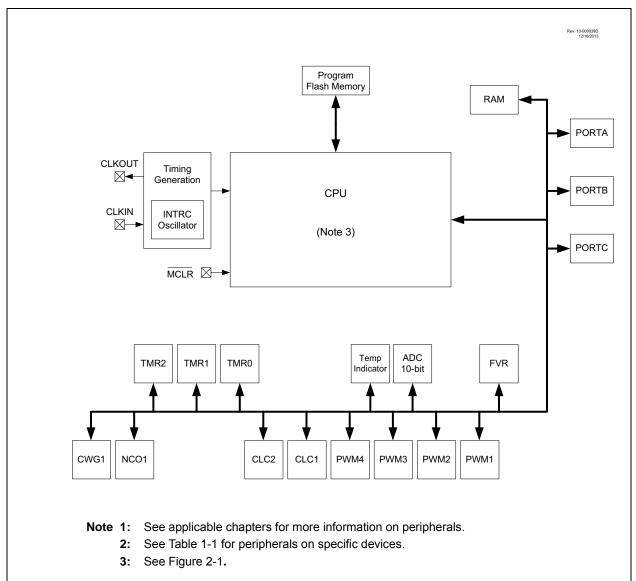

## 3.4 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

#### 3.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

#### 3.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 3.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

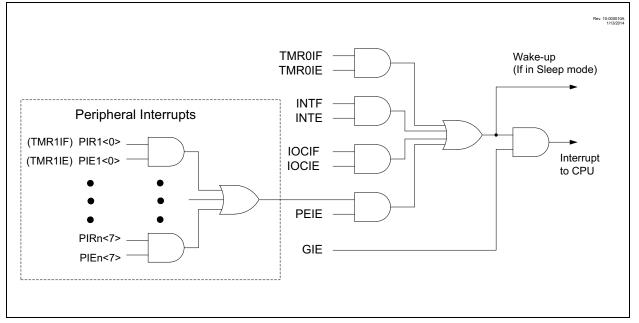

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 7-1.

| U-1              | R/W-0/0            | R/W-0/0                                     | R/W/HC-0/0            | R/W/HC-x/q <sup>(2)</sup>             | R/W-0/0           | R/S/HC-0/0           | R/S/HC-0/0       |

|------------------|--------------------|---------------------------------------------|-----------------------|---------------------------------------|-------------------|----------------------|------------------|

| (1)              | CFGS               | LWLO                                        | FREE                  | WRERR                                 | WREN              | WR                   | RD               |

| bit 7            |                    |                                             |                       |                                       |                   |                      | bit (            |

| Legend:          |                    |                                             |                       |                                       |                   |                      |                  |

| R = Readable     | bit                | W = Writable b                              | it                    | U = Unimplemer                        | nted bit, read as | s 'O'                |                  |

| S = Bit can on   | ly be set          | x = Bit is unkno                            | own                   | -n/n = Value at F                     | POR and BOR/      | /alue at all other I | Resets           |

| '1' = Bit is set |                    | '0' = Bit is clea                           | red                   | HC = Bit is clear                     | ed by hardware    | 9                    |                  |

| bit 7            | Unimplemen         | ted: Read as '1'                            |                       |                                       |                   |                      |                  |

| bit 6            | CFGS: Config       | guration Select bit                         |                       |                                       |                   |                      |                  |

|                  |                    | Configuration, Use<br>Flash program me      |                       | ID Registers                          |                   |                      |                  |

| bit 5            | LWLO: Load         | Write Latches On                            | ly bit <sup>(3)</sup> |                                       |                   |                      |                  |

|                  |                    | addressed progra                            |                       |                                       |                   |                      |                  |

|                  |                    | ressed program m<br>nitiated on the nex     |                       | n is loaded/update                    | ed and a write of | all program memo     | ory write latche |

| bit 4            | FREE: Progra       | am Flash Erase E                            | nable bit             |                                       |                   |                      |                  |

|                  |                    | s an erase operati<br>s a write operatior   |                       | •                                     | rdware cleared    | upon completion)     |                  |

| bit 3            |                    | gram/Erase Error                            | •                     |                                       |                   |                      |                  |

|                  |                    | n indicates an imp                          |                       |                                       | e attempt or te   | rmination (bit is s  | et automaticall  |

|                  |                    | et attempt (write '<br>gram or erase ope    |                       |                                       |                   |                      |                  |

| bit 2            |                    | ram/Erase Enable                            | •                     | , , , , , , , , , , , , , , , , , , , |                   |                      |                  |

|                  | 0                  | rogram/erase cyc                            |                       |                                       |                   |                      |                  |

|                  | 0 = Inhibits       | programming/eras                            | ing of program F      | lash                                  |                   |                      |                  |

| bit 1            | WR: Write Co       |                                             |                       |                                       |                   |                      |                  |

|                  |                    | a program Flash p<br>ration is self-timed   |                       |                                       | o onco onorativ   | on is complete       |                  |

|                  | •                  | bit can only be se                          |                       | •                                     | e once operatio   | on is complete.      |                  |

|                  |                    | /erase operation f                          | ` '                   |                                       | ive.              |                      |                  |

| bit 0            | RD: Read Co        | ontrol bit                                  |                       |                                       |                   |                      |                  |

|                  |                    | a program Flash r                           | ead. Read takes       | s one cycle. RD is                    | cleared in hard   | lware. The RD bit    | can only be se   |

|                  | ```                | ared) in software.<br>It initiate a prograr | n Flash read          |                                       |                   |                      |                  |

| Note 1: U        | nimplemented bit   |                                             |                       |                                       |                   |                      |                  |

|                  | •                  | automatically set I                         | by hardware whe       | en a program men                      | nory write or era | ase operation is st  | arted (WR = 1    |

|                  | he LWLO bit is igi | -                                           | -                     |                                       |                   | •                    | •                |

## REGISTER 10-5: PMCON1: PROGRAM MEMORY CONTROL 1 REGISTER

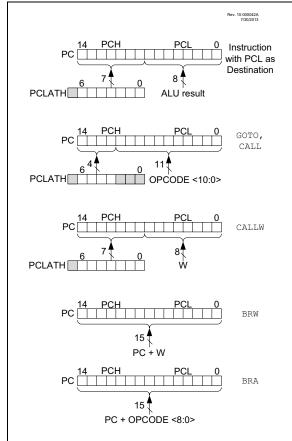

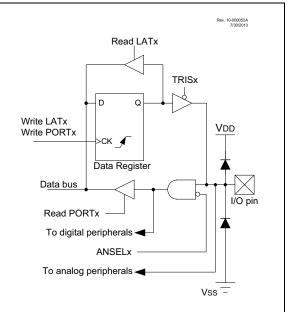

# 11.0 I/O PORTS

Each port has three standard registers for its operation. These registers are:

- · TRISx registers (data direction)

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

Some ports may have one or more of the following additional registers. These registers are:

- · ANSELx (analog select)

- · WPUx (weak pull-up)

In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output. However, the pin can still be read.

# TABLE 11-1:PORT AVAILABILITY PER<br/>DEVICE

| Device        | PORTA | PORTB | PORTC |

|---------------|-------|-------|-------|

| PIC16(L)F1507 | ٠     | •     | •     |

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled. Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 11-1.

## FIGURE 11-1: GE

#### GENERIC I/O PORT OPERATION

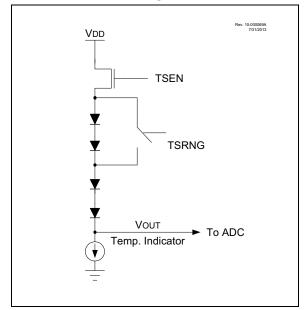

## 14.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

## 14.1 Circuit Operation

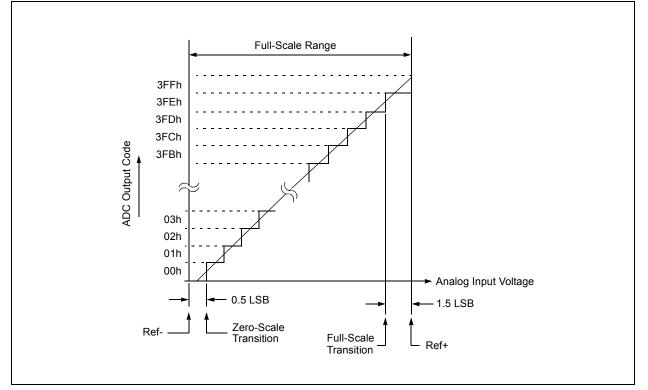

Figure 14-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 14-1 describes the output characteristics of the temperature indicator.

## EQUATION 14-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See Section **13.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

# FIGURE 14-1: TEMPERATURE CIRCUIT DIAGRAM

## 14.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 14-1 shows the recommended minimum VDD vs. range setting.

#### TABLE 14-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

## 14.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 15.0 "Analog-to-Digital Converter (ADC) Module**" for detailed information.

## 14.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

| ADC Clock              | Period (TAD) |            | Device Frequency (Fosc) |            |            |            |  |  |  |  |  |

|------------------------|--------------|------------|-------------------------|------------|------------|------------|--|--|--|--|--|

| ADC<br>Clock<br>Source | ADCS<2:0     | 20 MHz     | 16 MHz                  | 8 MHz      | 4 MHz      | 1 MHz      |  |  |  |  |  |

| Fosc/2                 | 000          | 100 ns     | 125 ns                  | 250 ns     | 500 ns     | 2.0 μs     |  |  |  |  |  |

| Fosc/4                 | 100          | 200 ns     | 250 ns                  | 500 ns     | 1.0 μs     | 4.0 μs     |  |  |  |  |  |

| Fosc/8                 | 001          | 400 ns     | 500 ns                  | 1.0 μs     | 2.0 μs     | 8.0 μs     |  |  |  |  |  |

| Fosc/16                | 101          | 800 ns     | 1.0 μs                  | 2.0 μs     | 4.0 μs     | 16.0 μs    |  |  |  |  |  |

| Fosc/32                | 010          | 1.6 μs     | 2.0 μs                  | 4.0 μs     | 8.0 μs     | 32.0 μs    |  |  |  |  |  |

| Fosc/64                | 110          | 3.2 μs     | 4.0 μs                  | 8.0 μs     | 16.0 μs    | 64.0 μs    |  |  |  |  |  |

| FRC                    | x11          | 1.0-6.0 μs | 1.0-6.0 μs              | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs |  |  |  |  |  |

#### TABLE 15-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range, (see TAD parameter). The TAD period when using the FOSC-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

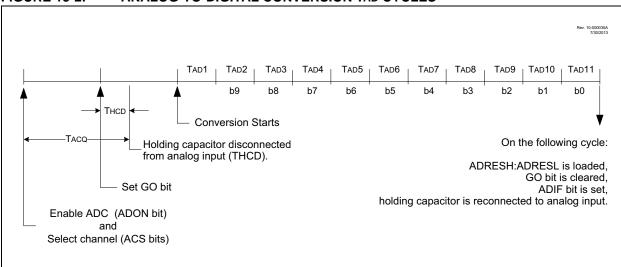

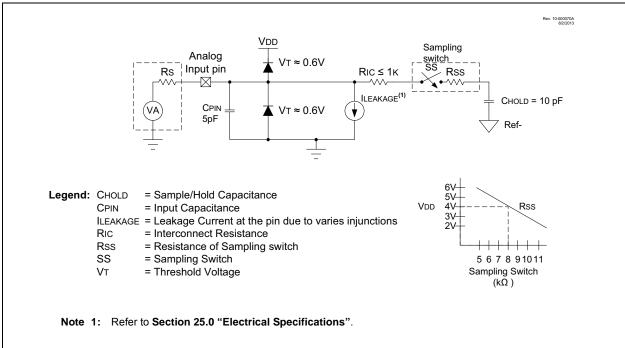

#### FIGURE 15-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

### **REGISTER 15-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

#### **REGISTER 15-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u    | R/W-x/u R/W-x/u |   | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|------------|-----------------|---|---------|---------|---------|---------|---------|

| ADRES<1:0> |                 | — | —       | —       | —       | —       | —       |

| bit 7      |                 |   |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **ADRES<1:0>**: ADC Result Register bits Lower two bits of 10-bit conversion result

bit 5-0 **Reserved**: Do not use.

| Name   | Bit 7      | Bit 6        | Bit 5     | Bit 4    | Bit 3  | Bit 2  | Bit 1   | Bit 0   | Register<br>on Page |

|--------|------------|--------------|-----------|----------|--------|--------|---------|---------|---------------------|

| ADCON0 | —          |              |           | CHS<4:0> |        |        | GO/DONE | ADON    | 123                 |

| ADCON1 | ADFM       |              | ADCS<2:0> |          | _      | —      | ADPRE   | :F<1:0> | 124                 |

| ADCON2 |            | TRIGSE       | EL<3:0>   |          | -      | —      | —       | _       | 125                 |

| ADRESH | ADC Result | Register Hig | h         |          |        |        |         |         | 126, 127            |

| ADRESL | ADC Result | Register Lov | v         |          |        |        |         |         | 126, 127            |

| ANSELA | —          | _            | _         | ANSA4    | _      | ANSA2  | ANSA1   | ANSA0   | 99                  |

| ANSELB | _          | _            | ANSB5     | ANSB4    | -      | —      | —       | _       | 103                 |

| ANSELC | ANSC7      | ANSC6        | _         | _        | ANSC3  | ANSC2  | ANSC1   | ANSC0   | 107                 |

| INTCON | GIE        | PEIE         | TMR0IE    | INTE     | IOCIE  | TMR0IF | INTF    | IOCIF   | 64                  |

| PIE1   | TMR1GIE    | ADIE         | _         | -        | -      | —      | TMR2IE  | TMR1IE  | 65                  |

| PIR1   | TMR1GIF    | ADIF         | _         | _        | _      | —      | TMR2IF  | TMR1IF  | 68                  |

| TRISA  | _          | _            | TRISA5    | TRISA4   | —(1)   | TRISA2 | TRISA1  | TRISA0  | 98                  |

| TRISB  | TRISB7     | TRISB6       | TRISB5    | TRISB4   | _      | _      | _       |         | 102                 |

| TRISC  | TRISC7     | TRISC6       | TRISC5    | TRISC4   | TRISC3 | TRISC2 | TRISC1  | TRISC0  | 106                 |

| FVRCON | FVREN      | FVRRDY       | TSEN      | TSRNG    | _      | _      | ADFV    | R<1:0>  | 114                 |

#### TABLE 15-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

Legend: x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends on condition. Shaded cells are not used for ADC module.

Note 1: Unimplemented, read as '1'.

## 16.2 Register Definitions: Option Register

| R/W-1/1         | R/W-1/1                   | R/W-1/1                                                                                                                                | R/W-1/1    | R/W-1/1        | R/W-1/1          | R/W-1/1          | R/W-1/1      |  |  |  |  |

|-----------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------------|----------------|------------------|------------------|--------------|--|--|--|--|

| WPUEN           | INTEDG                    | TMR0CS                                                                                                                                 | TMR0SE     | PSA            |                  | PS<2:0>          |              |  |  |  |  |

| bit 7           | ·                         |                                                                                                                                        |            |                |                  |                  | bit (        |  |  |  |  |

|                 |                           |                                                                                                                                        |            |                |                  |                  |              |  |  |  |  |

| Legend:         |                           |                                                                                                                                        |            |                |                  |                  |              |  |  |  |  |

| R = Readabl     | le bit                    | W = Writable                                                                                                                           | bit        |                | mented bit, read |                  |              |  |  |  |  |

| u = Bit is und  | changed                   | x = Bit is unk                                                                                                                         | nown       | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |  |  |

| '1' = Bit is se | et                        | '0' = Bit is cle                                                                                                                       | ared       |                |                  |                  |              |  |  |  |  |

|                 |                           |                                                                                                                                        |            |                |                  |                  |              |  |  |  |  |

| bit 7           |                           | ak Pull-Up Ena                                                                                                                         |            |                |                  |                  |              |  |  |  |  |

|                 |                           | pull-ups are dis<br>Il-ups are enab                                                                                                    | · · ·      | •              | ,                |                  |              |  |  |  |  |

| bit 6           | •                         | •                                                                                                                                      | •          |                | values           |                  |              |  |  |  |  |

|                 |                           | INTEDG: Interrupt Edge Select bit<br>1 = Interrupt on rising edge of INT pin                                                           |            |                |                  |                  |              |  |  |  |  |

|                 |                           | 0 = Interrupt on falling edge of INT pin                                                                                               |            |                |                  |                  |              |  |  |  |  |

| bit 5           | TMR0CS: Tir               | TMR0CS: Timer0 Clock Source Select bit                                                                                                 |            |                |                  |                  |              |  |  |  |  |

|                 |                           | n on T0CKI pin                                                                                                                         |            |                |                  |                  |              |  |  |  |  |

|                 |                           | nstruction cycle                                                                                                                       |            | 4)             |                  |                  |              |  |  |  |  |

| bit 4           |                           | ner0 Source E                                                                                                                          | -          |                |                  |                  |              |  |  |  |  |

|                 |                           | <ul> <li>1 = Increment on high-to-low transition on T0CKI pin</li> <li>0 = Increment on low-to-high transition on T0CKI pin</li> </ul> |            |                |                  |                  |              |  |  |  |  |

| bit 3           |                           | ler Assignment                                                                                                                         |            | TOCKI pili     |                  |                  |              |  |  |  |  |

| DIL D           |                           | r is not assigne                                                                                                                       |            | 0 module       |                  |                  |              |  |  |  |  |

|                 |                           | r is assigned to                                                                                                                       |            |                |                  |                  |              |  |  |  |  |

| bit 2-0         | <b>PS&lt;2:0&gt;:</b> Pre | escaler Rate Se                                                                                                                        | elect bits |                |                  |                  |              |  |  |  |  |

|                 | Bit                       | Value Timer0                                                                                                                           | Rate       |                |                  |                  |              |  |  |  |  |

|                 | (                         | 000 1:2                                                                                                                                |            |                |                  |                  |              |  |  |  |  |

|                 |                           | 001 1:4                                                                                                                                |            |                |                  |                  |              |  |  |  |  |

|                 |                           | 010 1:8<br>011 1:1                                                                                                                     |            |                |                  |                  |              |  |  |  |  |

|                 |                           | 100 1:3                                                                                                                                |            |                |                  |                  |              |  |  |  |  |

|                 | 1                         | 101 1:6                                                                                                                                | 4          |                |                  |                  |              |  |  |  |  |

## REGISTER 16-1: OPTION\_REG: OPTION REGISTER

#### TABLE 16-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

1:128

1:256

110

111

| Name       | Bit 7                                       | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|---------------------------------------------|--------|--------|--------|-------|--------|---------|--------|---------------------|

| ADCON2     | DCON2 TRIGSEL<3:0>                          |        |        |        |       | _      | _       | -      | 125                 |

| INTCON     | GIE                                         | PEIE   | TMR0IE | INTE   | IOCIE | TMR0IF | INTF    | IOCIF  | 64                  |

| OPTION_REG | WPUEN                                       | INTEDG | TMR0CS | TMR0SE | PSA   |        | PS<2:0> |        | 133                 |

| TMR0       | Holding Register for the 8-bit Timer0 Count |        |        |        |       |        |         | 131*   |                     |

| TRISA      | _                                           | _      | TRISA5 | TRISA4 | _(1)  | TRISA2 | TRISA1  | TRISA0 | 98                  |

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module. \* Page provides register information.

Note 1: Unimplemented, read as '1'.

## 19.2 Register Definitions: PWM Control

## REGISTER 19-1: PWMxCON: PWM CONTROL REGISTER

| R/W-0/0          | R/W-0/0       | R-0/0             | R/W-0/0         | U-0            | U-0              | U-0              | U-0          |  |  |

|------------------|---------------|-------------------|-----------------|----------------|------------------|------------------|--------------|--|--|

| PWMxEN           | PWMxOE        | PWMxOUT           | PWMxPOL         | —              | _                | —                |              |  |  |

| bit 7            |               |                   |                 |                |                  |                  | bit C        |  |  |

|                  |               |                   |                 |                |                  |                  |              |  |  |

| Legend:          |               |                   |                 |                |                  |                  |              |  |  |

| R = Readable     | bit           | W = Writable      | bit             | U = Unimpler   | nented bit, read | l as '0'         |              |  |  |

| u = Bit is unch  | anged         | x = Bit is unkr   | nown            | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |  |  |

| '1' = Bit is set |               | '0' = Bit is cle  | ared            |                |                  |                  |              |  |  |

|                  |               |                   |                 |                |                  |                  |              |  |  |

| bit 7            | PWMxEN: P     | WM Module En      | able bit        |                |                  |                  |              |  |  |

|                  | 1 = PWM mo    | odule is enable   | dule is enabled |                |                  |                  |              |  |  |

|                  | 0 = PWM mo    | odule is disable  | d               |                |                  |                  |              |  |  |

| bit 6            | PWMxOE: P     | WM Module Ou      | utput Enable bi | bit            |                  |                  |              |  |  |

|                  | •             | o PWMx pin is e   |                 |                |                  |                  |              |  |  |

|                  | 0 = Output to | PWMx pin is o     | disabled        |                |                  |                  |              |  |  |

| bit 5            | PWMxOUT:      | PWM Module C      | Output Value bi | t              |                  |                  |              |  |  |

| bit 4            | PWMxPOL:      | PWMx Output I     | Polarity Select | bit            |                  |                  |              |  |  |

|                  |               | tput is active-lo |                 |                |                  |                  |              |  |  |

|                  | 0 = PWM ou    | tput is active-h  | igh             |                |                  |                  |              |  |  |

| bit 3-0          | Unimplemen    | ted: Read as '    | 0'              |                |                  |                  |              |  |  |

|                  |               |                   |                 |                |                  |                  |              |  |  |

| R/W-x/u              | R/W-x/u                                         | R/W-x/u                             | R/W-x/u        | R/W-x/u                                               | R/W-x/u  | R/W-x/u  | R/W-x/u  |  |  |  |

|----------------------|-------------------------------------------------|-------------------------------------|----------------|-------------------------------------------------------|----------|----------|----------|--|--|--|

| LCxG2D4T             | LCxG2D4N                                        | LCxG2D3T                            | LCxG2D3N       | LCxG2D2T                                              | LCxG2D2N | LCxG2D1T | LCxG2D1N |  |  |  |

| bit 7                |                                                 |                                     |                |                                                       |          |          | bit 0    |  |  |  |

|                      |                                                 |                                     |                |                                                       |          |          |          |  |  |  |

| Legend:              |                                                 |                                     |                |                                                       |          |          |          |  |  |  |

| R = Readable bit     |                                                 | W = Writable bit                    |                | U = Unimplemented bit, read as '0'                    |          |          |          |  |  |  |

| u = Bit is unchanged |                                                 | x = Bit is unkr                     |                | -n/n = Value at POR and BOR/Value at all other Resets |          |          |          |  |  |  |

| '1' = Bit is set     |                                                 | '0' = Bit is clea                   | ared           |                                                       |          |          |          |  |  |  |

| bit 7                |                                                 | Gate 2 Data 4 1<br>gated into Icxo  | •              | rted) bit                                             |          |          |          |  |  |  |

|                      |                                                 | not gated into                      |                |                                                       |          |          |          |  |  |  |

| bit 6                | LCxG2D4N: Gate 2 Data 4 Negated (inverted) bit  |                                     |                |                                                       |          |          |          |  |  |  |

|                      |                                                 | a gated into lcxo<br>not gated into |                |                                                       |          |          |          |  |  |  |

| bit 5                | LCxG2D3T: Gate 2 Data 3 True (non-inverted) bit |                                     |                |                                                       |          |          |          |  |  |  |

|                      |                                                 | gated into lcxg<br>not gated into   |                |                                                       |          |          |          |  |  |  |

| bit 4                |                                                 | Gate 2 Data 3 I                     | •              | ted) bit                                              |          |          |          |  |  |  |

|                      |                                                 | a gated into lcxo<br>not gated into |                |                                                       |          |          |          |  |  |  |

| bit 3                |                                                 | Gate 2 Data 2 1                     |                | rted) bit                                             |          |          |          |  |  |  |

|                      |                                                 | gated into lcxg<br>not gated into   |                |                                                       |          |          |          |  |  |  |

| bit 2                | LCxG2D2N:                                       | Gate 2 Data 2 I                     | Negated (inver | rted) bit                                             |          |          |          |  |  |  |

|                      |                                                 | gated into lcx                      |                |                                                       |          |          |          |  |  |  |

| bit 1                | LCxG2D1T: (                                     | Gate 2 Data 1 1                     | rue (non-invei | rted) bit                                             |          |          |          |  |  |  |

|                      |                                                 | gated into lcxg<br>not gated into   |                |                                                       |          |          |          |  |  |  |

| bit 0                | LCxG2D1N:                                       | Gate 2 Data 1 I                     | Negated (inver | ted) bit                                              |          |          |          |  |  |  |

|                      |                                                 | gated into lcx                      |                |                                                       |          |          |          |  |  |  |

|                      |                                                 |                                     |                |                                                       |          |          |          |  |  |  |

|                      |                                                 |                                     |                |                                                       |          |          |          |  |  |  |

### REGISTER 20-6: CLCxGLS1: GATE 2 LOGIC SELECT REGISTER

DS40001586D-page 173

Status

© 2011-2015 Microchip Technology Inc.

| Mnemonic,<br>Operands |      |                               |               | 14-Bit Opcode |      |      |      | Status   |       |

|-----------------------|------|-------------------------------|---------------|---------------|------|------|------|----------|-------|

|                       |      | Description                   | Cycles        | MSb           |      |      | LSb  | Affected | Notes |

|                       |      | BYTE-ORIENTED FILE I          | REGISTER OPE  | RATIC         | NS   |      |      |          |       |

| ADDWF                 | f, d | Add W and f                   | 1             | 00            | 0111 | dfff | ffff | C, DC, Z | 2     |

| ADDWFC                | f, d | Add with Carry W and f        | 1             | 11            | 1101 | dfff | ffff | C, DC, Z | 2     |

| ANDWF                 | f, d | AND W with f                  | 1             | 00            | 0101 | dfff | ffff | Z        | 2     |

| ASRF                  | f, d | Arithmetic Right Shift        | 1             | 11            | 0111 | dfff | ffff | C, Z     | 2     |

| LSLF                  | f, d | Logical Left Shift            | 1             | 11            | 0101 | dfff | ffff | C, Z     | 2     |

| LSRF                  | f, d | Logical Right Shift           | 1             | 11            | 0110 | dfff | ffff | C, Z     | 2     |

| CLRF                  | f    | Clear f                       | 1             | 00            | 0001 | lfff | ffff | Z        | 2     |

| CLRW                  | _    | Clear W                       | 1             | 00            | 0001 | 0000 | 00xx | Z        |       |

| COMF                  | f, d | Complement f                  | 1             | 00            | 1001 | dfff | ffff | Z        | 2     |

| DECF                  | f, d | Decrement f                   | 1             | 00            | 0011 | dfff | ffff | Z        | 2     |

| INCF                  | f, d | Increment f                   | 1             | 00            | 1010 | dfff | ffff | Z        | 2     |

| IORWF                 | f, d | Inclusive OR W with f         | 1             | 00            | 0100 | dfff | ffff | Z        | 2     |

| MOVF                  | f, d | Move f                        | 1             | 00            | 1000 | dfff | ffff | Z        | 2     |

| MOVWF                 | f    | Move W to f                   | 1             | 00            | 0000 | 1fff | ffff |          | 2     |

| RLF                   | f, d | Rotate Left f through Carry   | 1             | 00            | 1101 | dfff | ffff | С        | 2     |

| RRF                   | f, d | Rotate Right f through Carry  | 1             | 00            | 1100 | dfff | ffff | С        | 2     |

| SUBWF                 | f, d | Subtract W from f             | 1             | 00            | 0010 | dfff | ffff | C, DC, Z | 2     |

| SUBWFB                | f, d | Subtract with Borrow W from f | 1             | 11            | 1011 | dfff | ffff | C, DC, Z | 2     |

| SWAPF                 | f, d | Swap nibbles in f             | 1             | 00            | 1110 | dfff | ffff |          | 2     |

| XORWF                 | f, d | Exclusive OR W with f         | 1             | 00            | 0110 | dfff | ffff | Z        | 2     |

|                       |      | BYTE ORIENTED                 | SKIP OPERATIO | ONS           |      |      |      |          | •     |

| DECFSZ                | f, d | Decrement f, Skip if 0        | 1(2)          | 00            | 1011 | dfff | ffff |          | 1, 2  |

| INCFSZ                | f, d | Increment f, Skip if 0        | 1(2)          | 00            | 1111 | dfff | ffff |          | 1, 2  |

|                       |      | BIT-ORIENTED FILE R           | EGISTER OPER  |               | NS   |      |      |          |       |

| BCF                   | f, b | Bit Clear f                   | 1             | 01            | 00bb | bfff | ffff |          | 2     |

| BSF                   | f, b | Bit Set f                     | 1             | 01            | 01bb | bfff | ffff |          | 2     |

|                       |      | BIT-ORIENTED S                |               | NS            |      |      |      |          |       |

| BTFSC                 | f, b | Bit Test f, Skip if Clear     | 1 (2)         | 01            | 10bb | bfff | ffff |          | 1, 2  |

| BTFSS                 | f, b | Bit Test f, Skip if Set       | 1 (2)         | 01            | 11bb | bfff | ffff |          | 1, 2  |

|                       |      | -                             | PERATIONS     |               |      |      |      |          |       |

| ADDLW                 | k    | Add literal and W             | 1             | 11            | 1110 | kkkk |      | C, DC, Z |       |

| ANDLW                 | k    | AND literal with W            | 1             | 11            |      | kkkk |      | Z        |       |

| IORLW                 | k    | Inclusive OR literal with W   | 1             | 11            | 1000 |      |      | Z        |       |

| MOVLB                 | k    | Move literal to BSR           | 1             | 00            | 0000 |      | kkkk |          |       |

| MOVLP                 | k    | Move literal to PCLATH        | 1             | 11            |      | 1kkk |      |          |       |

| MOVLW                 | k    | Move literal to W             | 1             | 11            | 0000 |      |      |          |       |

| SUBLW                 | k    | Subtract W from literal       | 1             | 11            |      | kkkk |      | C, DC, Z |       |

| XORLW                 | k    | Exclusive OR literal with W   | 1             | 11            | 1010 | kkkk | kkkk | Z        | 1     |

### TABLE 24-3: ENHANCED MID-RANGE INSTRUCTION SET

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

## 27.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 27.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 27.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

### 27.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

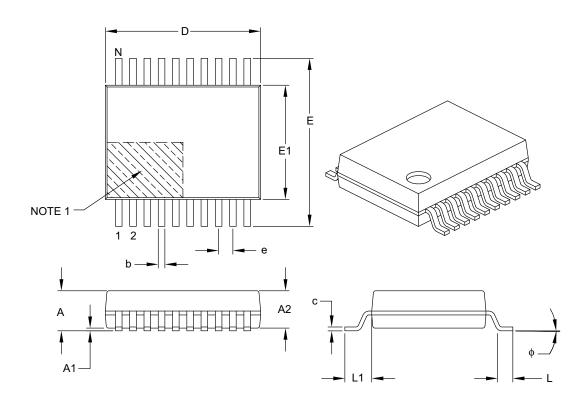

For the most current package drawings, please see the Microchip Packaging Specification located at

#### 20-Lead Plastic Shrink Small Outline (SS) – 5.30 mm Body [SSOP]

http://www.microchip.com/packaging

|                          | Units    |          | MILLIMETERS | 3    |  |  |

|--------------------------|----------|----------|-------------|------|--|--|

| Dimensio                 | n Limits | MIN      | NOM         | MAX  |  |  |

| Number of Pins           | Ν        | 20       |             |      |  |  |

| Pitch                    | е        | 0.65 BSC |             |      |  |  |

| Overall Height           | А        | -        | -           | 2.00 |  |  |

| Molded Package Thickness | A2       | 1.65     | 1.75        | 1.85 |  |  |

| Standoff                 | A1       | 0.05     | -           | -    |  |  |

| Overall Width            | E        | 7.40     | 7.80        | 8.20 |  |  |

| Molded Package Width     | E1       | 5.00     | 5.30        | 5.60 |  |  |

| Overall Length           | D        | 6.90     | 7.20        | 7.50 |  |  |

| Foot Length              | L        | 0.55     | 0.75        | 0.95 |  |  |

| Footprint L1             |          |          | 1.25 REF    |      |  |  |

| Lead Thickness           | с        | 0.09     | -           | 0.25 |  |  |

| Foot Angle               | φ        | 0°       | 4°          | 8°   |  |  |

| Lead Width               | b        | 0.22     | -           | 0.38 |  |  |

#### Notes:

Note:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-072B