Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-UFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-UQFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1507-e-gz |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.3 Data Memory Organization

The data memory is partitioned in 32 memory banks with 128 bytes in a bank. Each bank consists of (Figure 3-2):

- 12 core registers

- 20 Special Function Registers (SFR)

- Up to 80 bytes of General Purpose RAM (GPR)

- 16 bytes of common RAM

The active bank is selected by writing the bank number into the Bank Select Register (BSR). Unimplemented memory will read as '0'. All data memory can be accessed either directly (via instructions that use the file registers) or indirectly via the two File Select Registers (FSR). See **Section 3.6 "Indirect Addressing"** for more information.

Data memory uses a 12-bit address. The upper five bits of the address define the Bank address and the lower seven bits select the registers/RAM in that bank.

#### 3.3.1 CORE REGISTERS

The core registers contain the registers that directly affect the basic operation. The core registers occupy the first 12 addresses of every data memory bank (addresses x00h/x08h through x0Bh/x8Bh). These registers are listed below in Table 3-2. For detailed information, see Table 3-4.

| TABLE 3-2: | CORE REGISTERS |

|------------|----------------|

|            |                |

| Addresses    | BANKx  |

|--------------|--------|

| x00h or x80h | INDF0  |

| x01h or x81h | INDF1  |

| x02h or x82h | PCL    |

| x03h or x83h | STATUS |

| x04h or x84h | FSR0L  |

| x05h or x85h | FSR0H  |

| x06h or x86h | FSR1L  |

| x07h or x87h | FSR1H  |

| x08h or x88h | BSR    |

| x09h or x89h | WREG   |

| 0Ah or x8Ah  | PCLATH |

| x0Bh or x8Bh | INTCON |

# 3.4 PCL and PCLATH

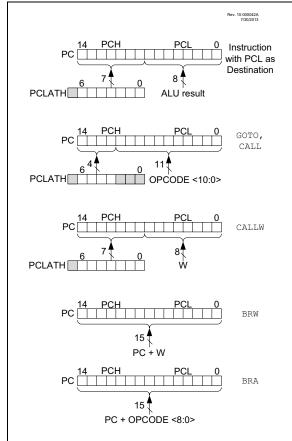

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 3-3 shows the five situations for the loading of the PC.

#### 3.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register and those being written to the PCL register.

#### 3.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

## 3.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 3.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 +, the signed value of the operand of the BRA instruction.

# 7.0 INTERRUPTS

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

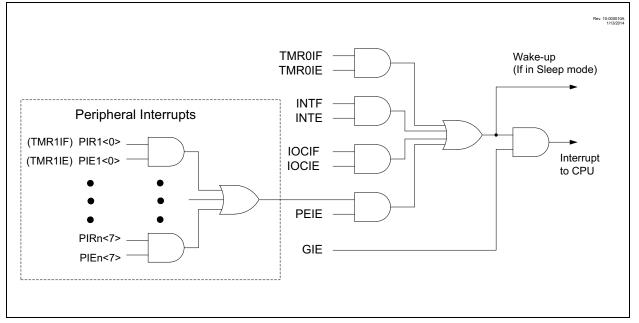

A block diagram of the interrupt logic is shown in Figure 7-1.

# 7.1 Operation

Interrupts are disabled upon any device Reset. They are enabled by setting the following bits:

- GIE bit of the INTCON register

- Interrupt Enable bit(s) for the specific interrupt event(s)

- PEIE bit of the INTCON register (if the Interrupt Enable bit of the interrupt event is contained in the PIE1, PIE2 and PIE3 registers)

The INTCON, PIR1, PIR2 and PIR3 registers record individual interrupts via interrupt flag bits. Interrupt flag bits will be set, regardless of the status of the GIE, PEIE and individual interrupt enable bits.

The following events happen when an interrupt event occurs while the GIE bit is set:

- Current prefetched instruction is flushed

- · GIE bit is cleared

- Current Program Counter (PC) is pushed onto the stack

- Critical registers are automatically saved to the shadow registers (See "Section 7.5 "Automatic Context Saving".")

- · PC is loaded with the interrupt vector 0004h

The firmware within the Interrupt Service Routine (ISR) should determine the source of the interrupt by polling the interrupt flag bits. The interrupt flag bits must be cleared before exiting the ISR to avoid repeated interrupts. Because the GIE bit is cleared, any interrupt that occurs while executing the ISR will be recorded through its interrupt flag, but will not cause the processor to redirect to the interrupt vector.

The RETFIE instruction exits the ISR by popping the previous address from the stack, restoring the saved context from the shadow registers and setting the GIE bit.

For additional information on a specific interrupt's operation, refer to its peripheral chapter.

- Note 1: Individual interrupt flag bits are set, regardless of the state of any other enable bits.

- 2: All interrupts will be ignored while the GIE bit is cleared. Any interrupt occurring while the GIE bit is clear will be serviced when the GIE bit is set again.

# 7.2 Interrupt Latency

Interrupt latency is defined as the time from when the interrupt event occurs to the time code execution at the interrupt vector begins. The latency for synchronous interrupts is three or four instruction cycles. For asynchronous interrupts, the latency is three to five instruction cycles, depending on when the interrupt occurs. See Figure 7-2 and Figure 7-3 for more details.

| Name       | Bit 7   | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1   | Bit 0  | Register<br>on Page |

|------------|---------|--------|--------|--------|-------|--------|---------|--------|---------------------|

| INTCON     | GIE     | PEIE   | TMR0IE | INTE   | IOCIE | TMR0IF | INTF    | IOCIF  | 64                  |

| OPTION_REG | WPUEN   | INTEDG | TMR0CS | TMR0SE | PSA   |        | PS<2:0> |        | 133                 |

| PIE1       | TMR1GIE | ADIE   | _      | _      |       | —      | TMR2IE  | TMR1IE | 65                  |

| PIE2       |         | _      | _      | _      | —     | NCO1IE | _       | _      | 66                  |

| PIE3       |         | _      | _      | _      | —     | —      | CLC2IE  | CLC1IE | 67                  |

| PIR1       | TMR1GIF | ADIF   | _      | _      |       | —      | TMR2IF  | TMR1IF | 68                  |

| PIR2       | _       |        |        |        |       | NCO1IF |         |        | 69                  |

| PIR3       | _       | _      | _      | _      | _     | _      | CLC2IF  | CLC1IF | 70                  |

TABLE 7-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** — = unimplemented location, read as '0'. Shaded cells are not used by interrupts.

# 10.0 FLASH PROGRAM MEMORY CONTROL

The Flash program memory is readable and writable during normal operation over the full VDD range. Program memory is indirectly addressed using Special Function Registers (SFRs). The SFRs used to access program memory are:

- PMCON1

- PMCON2

- PMDATL

- PMDATH

- PMADRL

- PMADRH

When accessing the program memory, the PMDATH:PMDATL register pair forms a 2-byte word that holds the 14-bit data for read/write, and the PMADRH:PMADRL register pair forms a 2-byte word that holds the 15-bit address of the program memory location being read.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

The Flash program memory can be protected in two ways; by code protection (CP bit in Configuration Words) and write protection (WRT<1:0> bits in Configuration Words).

Code protection ( $\overline{CP} = 0$ )<sup>(1)</sup>, disables access, reading and writing, to the Flash program memory via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be reset by a device programmer performing a Bulk Erase to the device, clearing all Flash program memory, Configuration bits and User IDs.

Write protection prohibits self-write and erase to a portion or all of the Flash program memory, as defined by the bits WRT<1:0>. Write protection does not affect a device programmers ability to read, write or erase the device.

**Note 1:** Code protection of the entire Flash program memory array is enabled by clearing the CP bit of Configuration Words.

#### 10.1 PMADRL and PMADRH Registers

The PMADRH:PMADRL register pair can address up to a maximum of 32K words of program memory. When selecting a program address value, the MSB of the address is written to the PMADRH register and the LSB is written to the PMADRL register.

#### 10.1.1 PMCON1 AND PMCON2 REGISTERS

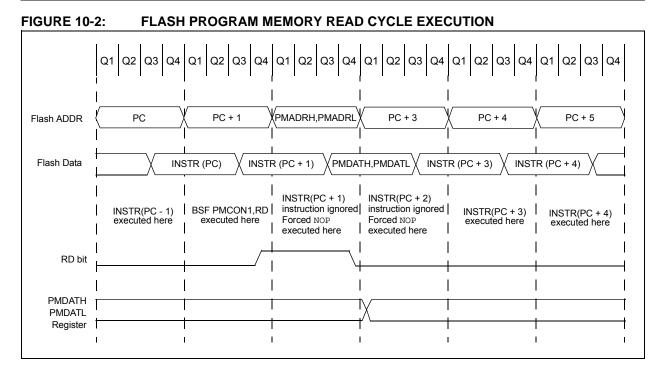

PMCON1 is the control register for Flash program memory accesses.

Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared by hardware at completion of the read or write operation. The inability to clear the WR bit in software prevents the accidental, premature termination of a write operation.

The WREN bit, when set, will allow a write operation to occur. On power-up, the WREN bit is clear. The WRERR bit is set when a write operation is interrupted by a Reset during normal operation. In these situations, following Reset, the user can check the WRERR bit and execute the appropriate error handling routine.

The PMCON2 register is a write-only register. Attempting to read the PMCON2 register will return all '0's.

To enable writes to the program memory, a specific pattern (the unlock sequence), must be written to the PMCON2 register. The required unlock sequence prevents inadvertent writes to the program memory write latches and Flash program memory.

# 10.2 Flash Program Memory Overview

It is important to understand the Flash program memory structure for erase and programming operations. Flash program memory is arranged in rows. A row consists of a fixed number of 14-bit program memory words. A row is the minimum size that can be erased by user software.

After a row has been erased, the user can reprogram all or a portion of this row. Data to be written into the program memory row is written to 14-bit wide data write latches. These write latches are not directly accessible to the user, but may be loaded via sequential writes to the PMDATH:PMDATL register pair.

| Note: | If the user wants to modify only a portion<br>of a previously programmed row, then the<br>contents of the entire row must be read<br>and saved in RAM prior to the erase.<br>Then, new data and retained data can be<br>written into the write latches to reprogram<br>the row of Flash program memory. How-<br>ever, any unprogrammed locations can be<br>written without first erasing the row. In this<br>case, it is not necessary to save and |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | rewrite the other previously programmed locations.                                                                                                                                                                                                                                                                                                                                                                                                 |

See Table 10-1 for Erase Row size and the number of write latches for Flash program memory.

#### TABLE 10-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device        | Row Erase<br>(words) | Write<br>Latches<br>(words) |

|---------------|----------------------|-----------------------------|

| PIC16(L)F1507 | 16                   | 16                          |

#### EXAMPLE 10-1: FLASH PROGRAM MEMORY READ

```

* This code block will read 1 word of program

* memory at the memory address:

PROG_ADDR_HI : PROG_ADDR_LO

data will be returned in the variables;

PROG_DATA_HI, PROG_DATA_LO

BANKSEL PMADRL

; Select Bank for PMCON registers

PROG_ADDR_LO

MOVLW

;

MOVWF

PMADRL

; Store LSB of address

PROG_ADDR_HI

MOVLW

;

MOVWF

PMADRH

; Store MSB of address

BCF

PMCON1,CFGS

; Do not select Configuration Space

BSF

PMCON1,RD

; Initiate read

NOP

; Ignored (Figure 10-2)

NOP

; Ignored (Figure 10-2)

MOVF

PMDATL,W

; Get LSB of word

MOVWF

PROG_DATA_LO

; Store in user location

; Get MSB of word

PMDATH,W

MOVF

MOVWF

PROG_DATA_HI

; Store in user location

```

# 11.6 Register Definitions: PORTB

## REGISTER 11-7: PORTB: PORTB REGISTER

| R/W-x/x                                 | R/W-x/x | R/W-x/x           | R/W-x/x                                            | U-0          | U-0              | U-0          | U-0   |

|-----------------------------------------|---------|-------------------|----------------------------------------------------|--------------|------------------|--------------|-------|

| RB7                                     | RB6     | RB5               | RB4                                                |              | —                | —            | —     |

| bit 7                                   |         |                   |                                                    |              |                  |              | bit 0 |

|                                         |         |                   |                                                    |              |                  |              |       |

| Legend:                                 |         |                   |                                                    |              |                  |              |       |

| R = Readable I                          | bit     | W = Writable      | bit                                                | U = Unimpler | mented bit, read | as '0'       |       |

| u = Bit is unchanged x = Bit is unknown |         | nown              | -n/n = Value at POR and BOR/Value at all other Res |              |                  | other Resets |       |

| '1' = Bit is set                        |         | '0' = Bit is clea | ared                                               |              |                  |              |       |

| bit 7-4 | RB<7:4>: PORTB I/O Value bits <sup>(1)</sup> |

|---------|----------------------------------------------|

|         | 1 = Port pin is <u>&gt;</u> Vін              |

|         | 0 = Port pin is <u>&lt;</u> VIL              |

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

#### REGISTER 11-8: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | RB<7:4>: PORTB Tri-State Control bits             |

|---------|---------------------------------------------------|

|         | 1 = PORTB pin configured as an input (tri-stated) |

|         | 0 = PORTB pin configured as an output             |

|         |                                                   |

bit 3-0 Unimplemented: Read as '0'

# 11.7 PORTC Registers

#### 11.7.1 DATA REGISTER

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 11-13). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., disable the output driver). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 11-12) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

#### 11.7.2 DIRECTION CONTROL

The TRISC register (Register 11-13) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.7.3 ANALOG CONTROL

The ANSELC register (Register 11-15) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 11.7.4 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-8.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the output priority list. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the output priority list.

| Pin Name | Function Priority <sup>(1)</sup>   |

|----------|------------------------------------|

| RC0      | CLC2<br>RC0                        |

| RC1      | NCO1 <sup>(2)</sup><br>PWM4<br>RC1 |

| RC2      | RC2                                |

| RC3      | PWM2<br>RC3                        |

CWG1B

CWG1A

CLC1<sup>(3)</sup>

NCO1<sup>(3)</sup>

PWM1

RC5

RC6

RC7

RC4

RC4

RC5

RC6

RC7

| TABLE 11-8: | PORTC OUTPUT PRIORITY |

|-------------|-----------------------|

|             |                       |

Note 1: Priority listed from highest to lowest.

2: Default pin (see APFCON register).

3: Alternate pin (see APFCON register).

# 15.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- · Port configuration

- · Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- · Interrupt control

- Result formatting

#### 15.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 11.0 "I/O Ports"** for more information.

| Note: | Analog voltages on any pin that is defined |

|-------|--------------------------------------------|

|       | as a digital input may cause the input     |

|       | buffer to conduct excess current.          |

#### 15.1.2 CHANNEL SELECTION

There are 14 channel selections available:

- AN<11:0> pins

- Temperature Indicator

- FVR\_buffer1

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay (TACQ) is required before starting the next conversion. Refer to **Section 15.2.6 "ADC Conversion Procedure"** for more information.

#### 15.1.3 ADC VOLTAGE REFERENCE

The ADC module uses a positive and a negative voltage reference. The positive reference is labeled ref+ and the negative reference is labeled ref-.

The positive voltage reference (ref+) is selected by the ADPREF bits in the ADCON1 register. The positive voltage reference source can be:

- VREF+ pin

- Vdd

The negative voltage reference (ref-) source is:

Vss

#### 15.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- · Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (internal RC oscillator)

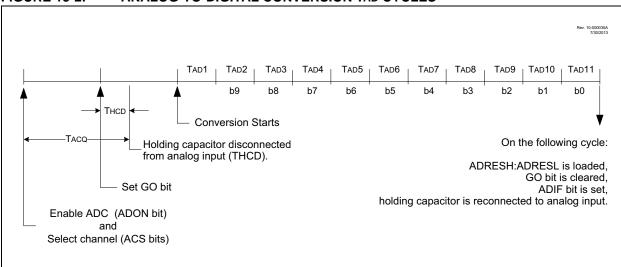

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 11.5 TAD periods as shown in Figure 15-2.

For correct conversion, the appropriate TAD specification must be met. Refer to the ADC conversion requirements in **Section 25.0 "Electrical Specifications"** for more information. Table 15-1 gives examples of appropriate ADC clock selections.

| Note: | Unless using the FRC, any changes in the |  |  |

|-------|------------------------------------------|--|--|

|       | system clock frequency will change the   |  |  |

|       | ADC clock frequency, which may           |  |  |

|       | adversely affect the ADC result.         |  |  |

| ADC Clock Period (TAD) |          |            | Device Frequency (Fosc) |            |            |            |  |

|------------------------|----------|------------|-------------------------|------------|------------|------------|--|

| ADC<br>Clock<br>Source | ADCS<2:0 | 20 MHz     | 16 MHz                  | 8 MHz      | 4 MHz      | 1 MHz      |  |

| Fosc/2                 | 000      | 100 ns     | 125 ns                  | 250 ns     | 500 ns     | 2.0 μs     |  |

| Fosc/4                 | 100      | 200 ns     | 250 ns                  | 500 ns     | 1.0 μs     | 4.0 μs     |  |

| Fosc/8                 | 001      | 400 ns     | 500 ns                  | 1.0 μs     | 2.0 μs     | 8.0 μs     |  |

| Fosc/16                | 101      | 800 ns     | 1.0 μs                  | 2.0 μs     | 4.0 μs     | 16.0 μs    |  |

| Fosc/32                | 010      | 1.6 μs     | 2.0 μs                  | 4.0 μs     | 8.0 μs     | 32.0 μs    |  |

| Fosc/64                | 110      | 3.2 μs     | 4.0 μs                  | 8.0 μs     | 16.0 μs    | 64.0 μs    |  |

| FRC                    | x11      | 1.0-6.0 μs | 1.0-6.0 μs              | 1.0-6.0 μs | 1.0-6.0 μs | 1.0-6.0 μs |  |

#### TABLE 15-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

**Note:** The TAD period when using the FRC clock source can fall within a specified range, (see TAD parameter). The TAD period when using the FOSC-based clock source can be configured for a more precise TAD period. However, the FRC clock source must be used when conversions are to be performed with the device in Sleep mode.

#### FIGURE 15-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

# 17.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 17.4 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer increments asynchronously to the internal phase clocks. If the external clock source is selected then the timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 17.4.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

#### 17.4.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 17.5 Timer1 Gate

Timer1 can be configured to count freely or the count can be enabled and disabled using Timer1 gate circuitry. This is also referred to as Timer1 Gate Enable.

Timer1 gate can also be driven by multiple selectable sources.

#### 17.5.1 TIMER1 GATE ENABLE

The Timer1 Gate Enable mode is enabled by setting the TMR1GE bit of the T1GCON register. The polarity of the Timer1 Gate Enable mode is configured using the T1GPOL bit of the T1GCON register. When Timer1 Gate Enable mode is enabled, Timer1 will increment on the rising edge of the Timer1 clock source. When Timer1 Gate Enable mode is disabled, no incrementing will occur and Timer1 will hold the current count. See Figure 17-3 for timing details.

#### TABLE 17-3: TIMER1 GATE ENABLE SELECTIONS

| T1CLK      | T1GPOL | T1G | Timer1 Operation |

|------------|--------|-----|------------------|

| 1          | 0      | 0   | Counts           |

| 1          | 0      | 1   | Holds Count      |

| $\uparrow$ | 1      | 0   | Holds Count      |

| $\uparrow$ | 1      | 1   | Counts           |

#### 17.5.2 TIMER1 GATE SOURCE SELECTION

Timer1 gate source selections are shown in Table 17-4. Source selection is controlled by the T1GSS<1:0> bits of the T1GCON register. The polarity for each available source is also selectable. Polarity selection is controlled by the T1GPOL bit of the T1GCON register.

#### TABLE 17-4: TIMER1 GATE SOURCES

| T1GSS | Timer1 Gate Source                                                    |

|-------|-----------------------------------------------------------------------|

| 0     | Timer1 Gate pin (T1G)                                                 |

| 1     | Overflow of Timer0 (T0_overflow)<br>(TMR0 increments from FFh to 00h) |

**Note 1:** Optionally synchronized comparator output.

# 19.0 PULSE-WIDTH MODULATION (PWM) MODULE

The PWM module generates a Pulse-Width Modulated signal determined by the duty cycle, period, and resolution that are configured by the following registers:

- PR2

- T2CON

- PWMxDCH

- PWMxDCL

- PWMxCON

Figure 19-1 shows a simplified block diagram of PWM operation.

For a step-by-step procedure on how to set up this module for PWM operation, refer to Section 19.1.9 "Setup for PWM Operation using PWMx Pins".

#### Rev. 10-000022A 8/5/2013 PWMxDCL<7:6> Duty cycle registers **PWMxDCH** PWMx\_out To Peripherals 10-bit Latch (Not visible to user) **PWMxOE** R Q Comparator 0 PWMx 1 Q s TMR2 Module - TRIS Control **PWMxPOL** R TMR2 (1) Comparator T2\_match PR2 Note 1: 8-bit timer is concatenated with two bits generated by Fosc or two bits of the internal prescaler to create 10-bit time-base.

#### FIGURE 19-1: SIMPLIFIED PWM BLOCK DIAGRAM

| R/W-0/0          | R/W-0/0                                                                                                                                                                          | U-0              | U-0   | U-0                                                   | U-0              | R/W-0/0   | R/W-0/0    |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------------------------------------------|------------------|-----------|------------|

| GxASE            | GxARSEN                                                                                                                                                                          |                  | —     | _                                                     | _                | GxASDSFLT | GxASDSCLC2 |

| bit 7            |                                                                                                                                                                                  |                  |       |                                                       |                  |           | bit 0      |

| Legend:          |                                                                                                                                                                                  |                  |       |                                                       |                  |           |            |

| R = Readable     | bit                                                                                                                                                                              | W = Writable     | e bit | U = Unimpler                                          | mented bit, read | d as '0'  |            |

| u = Bit is unch  | nanged                                                                                                                                                                           | x = Bit is unl   | nown  | -n/n = Value at POR and BOR/Value at all other Resets |                  |           |            |

| '1' = Bit is set |                                                                                                                                                                                  | '0' = Bit is cle | eared | q = Value de                                          | pends on condi   | tion      |            |

| bit 6            | <ul> <li>0 = No auto-shutdown event has occurred</li> <li>GxARSEN: Auto-Restart Enable bit</li> <li>1 = Auto-restart is enabled</li> <li>0 = Auto-restart is disabled</li> </ul> |                  |       |                                                       |                  |           |            |

| bit 5-2          | Unimplemented: Read as '0'                                                                                                                                                       |                  |       |                                                       |                  |           |            |

| bit 1            | <b>GxASDSFLT:</b> CWG Auto-shutdown on FLT Enable bit<br>1 = <u>Shutdown when CWG1FLT</u> input is low<br>0 = <u>CWG1FLT</u> input has no effect on shutdown                     |                  |       |                                                       |                  |           |            |

| bit 0            | <b>GxASDSCLC2:</b> CWG Auto-shutdown on CLC2 Enable bit<br>1 = Shutdown when CLC2 output (LC2_out) is high<br>0 = CLC2 output has no effect on shutdown                          |                  |       |                                                       |                  |           |            |

## REGISTER 22-3: CWGxCON2: CWG CONTROL REGISTER 2

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BCF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

| BRA              | Relative Branch                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BRA label<br>[ <i>label</i> ]BRA \$+k                                                                                                                                                                         |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                 |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | Add the signed 9-bit literal 'k' to the PC. Since the PC will have incremented to fetch the next instruction, the new address will be PC + 1 + k. This instruction is a 2-cycle instruction. This branch has a limited range. |

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                         |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSS f,b                                                                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

# BRWRelative Branch with WSyntax:[ label ] BRWOperands:NoneOperation: $(PC) + (W) \rightarrow PC$ Status Affected:None

| otatao / mootoa. | Nelle                                                                                                                                                                                                             |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have incre-<br>mented to fetch the next instruction,<br>the new address will be PC + 1 + (W).<br>This instruction is a 2-cycle instruc-<br>tion. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BSF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

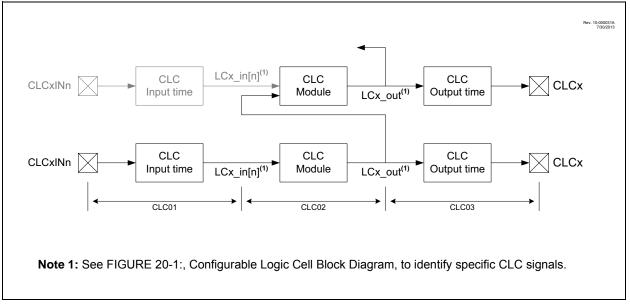

| TABLE 25-12: | CONFIGURATION LOGIC CELL (CLC) CHARACTERISTICS |

|--------------|------------------------------------------------|

|              |                                                |

| Param.<br>No. | Sym.    | Characteristic                              | Min. | Тур†     | Max. | Units    | Conditions               |

|---------------|---------|---------------------------------------------|------|----------|------|----------|--------------------------|

| CLC01*        | TCLCIN  | CLC input time                              | _    | 7        | _    | ns       |                          |

| CLC02*        | TCLC    | CLC module input to output propagation time |      | 24<br>12 |      | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |

| CLC03*        | TCLCOUT | CLC output time Rise Time                   |      | OS18     |      | —        | (Note 1)                 |

|               |         | Fall Time                                   | _    | OS19     | _    |          | (Note 1)                 |

| CLC04*        | FCLCMAX | CLC maximum switching frequency             | _    | 45       | _    | MHz      |                          |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1:See Table 25-9 for OS18 and OS19 rise and fall times.

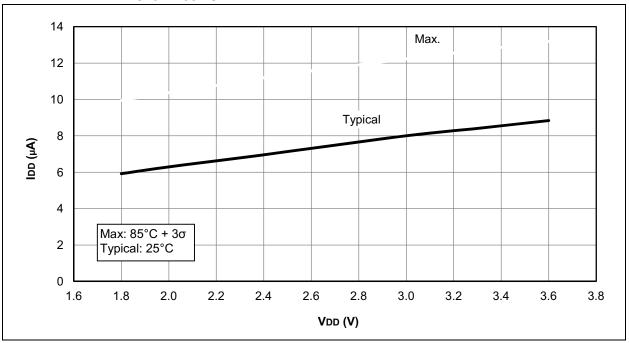

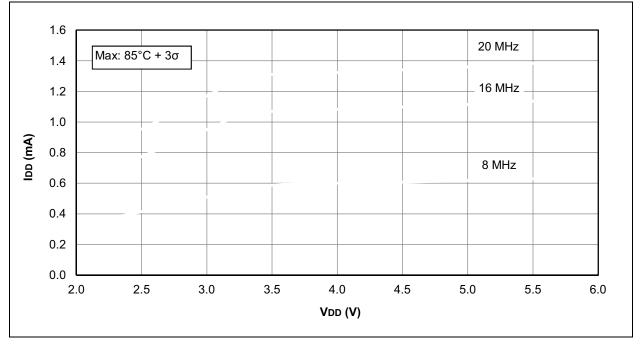

FIGURE 26-1: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 32 kHz, PIC16LF1507 ONLY

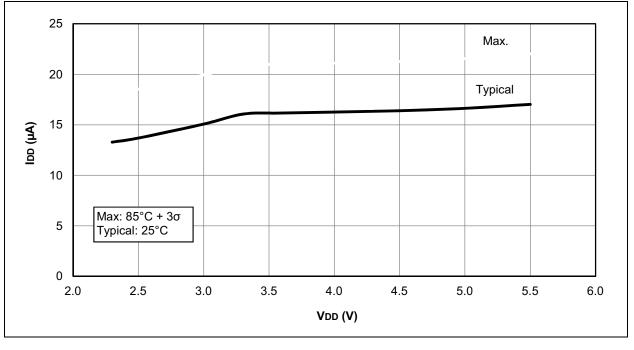

FIGURE 26-2: IDD, EXTERNAL CLOCK (ECL), LOW-POWER MODE, Fosc = 32 kHz, PIC16F1507 ONLY

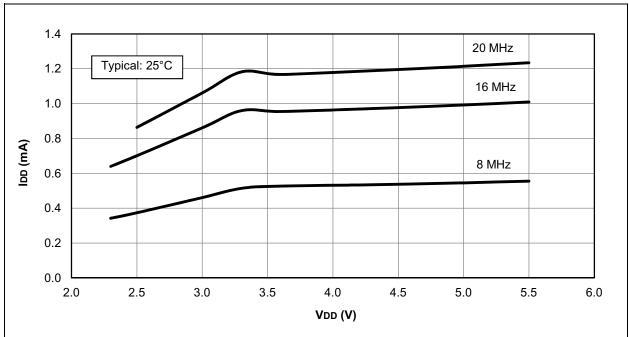

FIGURE 26-11: IDD TYPICAL, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16F1507 ONLY

FIGURE 26-12: IDD MAXIMUM, EXTERNAL CLOCK (ECH), HIGH-POWER MODE, PIC16F1507 ONLY

20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

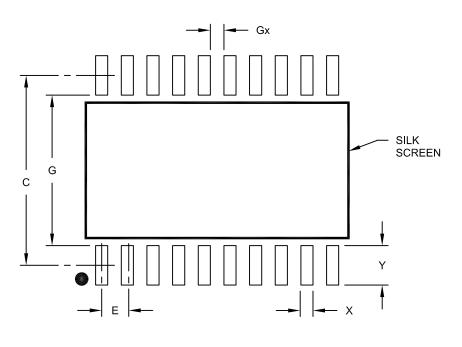

# RECOMMENDED LAND PATTERN

|                          | Units | MILLIMETERS |      |      |  |

|--------------------------|-------|-------------|------|------|--|

| Dimension Limits         |       | MIN         | NOM  | MAX  |  |

| Contact Pitch            | E     | 1.27 BSC    |      |      |  |

| Contact Pad Spacing      | С     |             | 9.40 |      |  |

| Contact Pad Width (X20)  | X     |             |      | 0.60 |  |

| Contact Pad Length (X20) | Y     |             |      | 1.95 |  |

| Distance Between Pads    | Gx    | 0.67        |      |      |  |

| Distance Between Pads    | G     | 7.45        |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2094A