Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1507-e-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED) **TABLE 3-5:**

| Address            | Name     | Bit 7      | Bit 6         | Bit 5       | Bit 4    | Bit 3    | Bit 2        | Bit 1      | Bit 0     | Value on POR, BOR | Value on all<br>other<br>Resets |

|--------------------|----------|------------|---------------|-------------|----------|----------|--------------|------------|-----------|-------------------|---------------------------------|

| Banks 14-29        |          |            |               |             |          |          |              |            |           |                   |                                 |

| x0Ch/<br>x8Ch      | _        | Unimplemen | ted           |             |          |          |              |            |           | —                 | —                               |

| x1Fh/<br>x9Fh      |          |            |               |             |          |          |              |            |           |                   |                                 |

| Bank 3             | 0        |            |               |             |          |          |              |            |           |                   |                                 |

| F0Ch<br>to<br>F0Eh | _        | Unimplemen | Unimplemented |             |          |          |              | _          | _         |                   |                                 |

| F0Fh               | CLCDATA  | —          |               | _           | _        |          |              | MLC2OUT    | MLC1OUT   | 00                | 00                              |

| F10h               | CLC1CON  | LC1EN      | LC10E         | LC10UT      | LC1INTP  | LC1INTN  |              | LC1MODE<2: | :0>       | 0000 0000         | 0000 0000                       |

| F11h               | CLC1POL  | LC1POL     | _             | _           | _        | LC1G4POL | LC1G3POL     | LC1G2POL   | LC1G1POL  | 0 xxxx            | 0 uuuu                          |

| F12h               | CLC1SEL0 | _          | L             | .C1D2S<2:0> | >        | _        | LC1D1S<2:0>  |            |           | -xxx -xxx         | -uuu -uuu                       |

| F13h               | CLC1SEL1 | _          | L             | .C1D4S<2:0> | >        | _        | LC1D3S<2:0>  |            |           | -xxx -xxx         | -uuu -uuu                       |

| F14h               | CLC1GLS0 | LC1G1D4T   | LC1G1D4N      | LC1G1D3T    | LC1G1D3N | LC1G1D2T | LC1G1D2N     | LC1G1D1T   | LC1G1D1N  | XXXX XXXX         | uuuu uuuu                       |

| F15h               | CLC1GLS1 | LC1G2D4T   | LC1G2D4N      | LC1G2D3T    | LC1G2D3N | LC1G2D2T | LC1G2D2N     | LC1G2D1T   | LC1G2D1N  | xxxx xxxx         | uuuu uuuu                       |

| F16h               | CLC1GLS2 | LC1G3D4T   | LC1G3D4N      | LC1G3D3T    | LC1G3D3N | LC1G3D2T | LC1G3D2N     | LC1G3D1T   | LC1G3D1N  | xxxx xxxx         | uuuu uuuu                       |

| F17h               | CLC1GLS3 | LC1G4D4T   | LC1G4D4N      | LC1G4D3T    | LC1G4D3N | LC1G4D2T | LC1G4D2N     | LC1G4D1T   | LC1G4D1N  | XXXX XXXX         | uuuu uuuu                       |

| F18h               | CLC2CON  | LC2EN      | LC2OE         | LC2OUT      | LC2INTP  | LC2INTN  | LC2MODE<2:0> |            | 0000 0000 | 0000 0000         |                                 |

| F19h               | CLC2POL  | LC2POL     |               | _           | _        | LC2G4POL | LC2G3POL     | LC2G2POL   | LC2G1POL  | 0 xxxx            | 0 uuuu                          |

| F1Ah               | CLC2SEL0 | —          | L             | .C2D2S<2:0> | >        |          | LC2D1S<2:0>  |            | -xxx -xxx | -uuu -uuu         |                                 |

| F1Bh               | CLC2SEL1 | _          | L             | .C2D4S<2:0> | >        | _        |              | LC2D3S<2:0 | >         | -xxx -xxx         | -uuu -uuu                       |

| F1Ch               | CLC2GLS0 | LC2G1D4T   | LC2G1D4N      | LC2G1D3T    | LC2G1D3N | LC2G1D2T | LC2G1D2N     | LC2G1D1T   | LC2G1D1N  | XXXX XXXX         | uuuu uuuu                       |

| F1Dh               | CLC2GLS1 | LC2G2D4T   | LC2G2D4N      | LC2G2D3T    | LC2G2D3N | LC2G2D2T | LC2G2D2N     | LC2G2D1T   | LC2G2D1N  | XXXX XXXX         | uuuu uuuu                       |

| F1Eh               | CLC2GLS2 | LC2G3D4T   | LC2G3D4N      | LC2G3D3T    | LC2G3D3N | LC2G3D2T | LC2G3D2N     | LC2G3D1T   | LC2G3D1N  | XXXX XXXX         | uuuu uuuu                       |

| F1Fh               | CLC2GLS3 | LC2G4D4T   | LC2G4D4N      | LC2G4D3T    | LC2G4D3N | LC2G4D2T | LC2G4D2N     | LC2G4D1T   | LC2G4D1N  | XXXX XXXX         | uuuu uuuu                       |

| F20h<br>to<br>F6Fh | _        | Unimplemen | Jnimplemented |             |          |          |              | _          | _         |                   |                                 |

Legend:

x = unknown, u = unchanged, q = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

Note

1:

PIC16F1507 only.

2:

Unimplemented, read as '1'.

| IADLL     |                 |               |                                                    |           |             |             |           | 020)      |           |                      |                                 |

|-----------|-----------------|---------------|----------------------------------------------------|-----------|-------------|-------------|-----------|-----------|-----------|----------------------|---------------------------------|

| Address   | Name            | Bit 7         | Bit 6                                              | Bit 5     | Bit 4       | Bit 3       | Bit 2     | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 3    | 1               |               |                                                    |           |             |             |           |           |           |                      |                                 |

| F8Ch      | —               | Unimplemen    | ted                                                |           |             |             |           |           |           | _                    | —                               |

| —<br>FE3h |                 |               |                                                    |           |             |             |           |           |           |                      |                                 |

| FE4h      | STATUS_<br>SHAD | _             | —                                                  | -         | _           | —           | Z_SHAD    | DC_SHAD   | C_SHAD    | xxx                  | uuu                             |

| FE5h      | WREG_<br>SHAD   | Working Reg   | Working Register Shadow                            |           |             |             | XXXX XXXX | uuuu uuuu |           |                      |                                 |

| FE6h      | BSR_<br>SHAD    | —             | _                                                  | -         | Bank Select | Register Sh | adow      |           |           | x xxxx               | u uuuu                          |

| FE7h      | PCLATH_<br>SHAD | _             | Program Counter Latch High Register Shadow         |           |             |             |           | -xxx xxxx | uuuu uuuu |                      |                                 |

| FE8h      | FSR0L_<br>SHAD  | Indirect Data | Indirect Data Memory Address 0 Low Pointer Shadow  |           |             |             |           |           | XXXX XXXX | uuuu uuuu            |                                 |

| FE9h      | FSR0H_<br>SHAD  | Indirect Data | Indirect Data Memory Address 0 High Pointer Shadow |           |             |             |           |           | xxxx xxxx | uuuu uuuu            |                                 |

| FEAh      | FSR1L_<br>SHAD  | Indirect Data | Indirect Data Memory Address 1 Low Pointer Shadow  |           |             |             |           | XXXX XXXX | uuuu uuuu |                      |                                 |

| FEBh      | FSR1H_<br>SHAD  | Indirect Data | Indirect Data Memory Address 1 High Pointer Shadow |           |             |             |           | XXXX XXXX | uuuu uuuu |                      |                                 |

| FECh      | —               | Unimplemen    | Unimplemented                                      |           |             |             |           | _         | _         |                      |                                 |

| FEDh      | STKPTR          | _             |                                                    | _         | Current Sta | ck Pointer  |           |           |           | 1 1111               | 1 1111                          |

| FEEh      | TOSL            | Top-of-Stack  | Top-of-Stack Low byte                              |           |             |             |           |           |           | XXXX XXXX            | uuuu uuuu                       |

| FEFh      | TOSH            | _             | Top-of-Stack                                       | High byte |             |             |           |           |           | -xxx xxxx            | -uuu uuuu                       |

**TABLE 3-5:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

PIC16F1507 only.

Unimplemented, read as '1'. Legend: : Note 1:

2:

| U-0                                | U-0                          | U-0                  | U-0        | U-0            | R/W-0/0          | U-0               | U-0         |

|------------------------------------|------------------------------|----------------------|------------|----------------|------------------|-------------------|-------------|

| _                                  | —                            | _                    | _          | —              | NCO1IF           | —                 | _           |

| bit 7                              |                              |                      |            |                |                  |                   | bit 0       |

|                                    |                              |                      |            |                |                  |                   |             |

| Legend:                            |                              |                      |            |                |                  |                   |             |

| R = Read                           | lable bit                    | W = Writable         | bit        | U = Unimpler   | mented bit, read | as '0'            |             |

| u = Bit is                         | unchanged                    | x = Bit is unkr      | nown       | -n/n = Value a | at POR and BOF   | R/Value at all of | ther Resets |

| '1' = Bit is                       | s set                        | '0' = Bit is clea    | ared       |                |                  |                   |             |

| bit 7-3                            | Unimplem                     | ented: Read as '     | כ,         |                |                  |                   |             |

| bit 2                              | -                            | Jumerically Contro   |            | or Flag bit    |                  |                   |             |

|                                    |                              | pt is pending        |            | in the grant   |                  |                   |             |

|                                    | 0 = Interrupt is not pending |                      |            |                |                  |                   |             |

| bit 1-0 Unimplemented: Read as '0' |                              |                      |            |                |                  |                   |             |

|                                    |                              |                      |            |                |                  |                   |             |

| Note:                              | Interrupt flag bits          | s are set when an    | interrupt  |                |                  |                   |             |

|                                    | condition occurs             | s, regardless of the | e state of |                |                  |                   |             |

|                                    | its correspondin             | ig enable bit or th  | e Global   |                |                  |                   |             |

|                                    | Interrupt Enable             | e bit, GIE of the    | INTCON     |                |                  |                   |             |

|                                    |                              | ~                    |            |                |                  |                   |             |

register. User software should ensure the appropriate interrupt flag bits are clear prior

to enabling an interrupt.

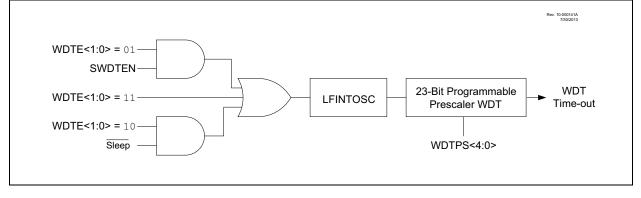

# 9.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- Independent clock source

- Multiple operating modes

- WDT is always on

- WDT is off when in Sleep

- WDT is controlled by software

- WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple Reset conditions

- Operation during Sleep

| R/W-x/u                                 | R/W-x/u | R/W-x/u | R/W-x/u                                               | U-0 | U-0 | U-0 | U-0   |

|-----------------------------------------|---------|---------|-------------------------------------------------------|-----|-----|-----|-------|

| LATB7                                   | LATB6   | LATB5   | LATB4                                                 | —   | —   | —   | —     |

| bit 7                                   | ·       | •       |                                                       |     |     | •   | bit 0 |

|                                         |         |         |                                                       |     |     |     |       |

| Legend:                                 |         |         |                                                       |     |     |     |       |

| R = Readable bit W = Writable bit       |         |         | U = Unimplemented bit, read as '0'                    |     |     |     |       |

| u = Bit is unchanged x = Bit is unknown |         |         | -n/n = Value at POR and BOR/Value at all other Resets |     |     |     |       |

#### **REGISTER 11-9: LATB: PORTB DATA LATCH REGISTER**

| bit 7-4 | LATB<7:4>: RB<7:4> Output Latch Value bits <sup>(1)</sup> |

|---------|-----------------------------------------------------------|

|---------|-----------------------------------------------------------|

bit 3-0 Unimplemented: Read as '0'

1' = Bit is set

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

#### REGISTER 11-10: ANSELB: PORTB ANALOG SELECT REGISTER

'0' = Bit is cleared

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|---------|---------|-----|-----|-----|-------|

| —     | _   | ANSB5   | ANSB4   | —   | —   | —   |       |

| bit 7 |     |         |         |     |     |     | bit 0 |

|       |     |         |         |     |     |     |       |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 Unimplemented: Read as '0'

bit 5-4 ANSB<5:4>: Analog Select between Analog or Digital Function on pins RB<5:4>, respectively

- 1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>. Digital input buffer disabled.

- 0 = Digital I/O. Pin is assigned to port or digital special function.

bit 3-0 Unimplemented: Read as '0'

**Note 1:** When setting a pin to an analog input, the corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

## 11.7 PORTC Registers

#### 11.7.1 DATA REGISTER

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 11-13). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., disable the output driver). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 11-12) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

#### 11.7.2 DIRECTION CONTROL

The TRISC register (Register 11-13) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.7.3 ANALOG CONTROL

The ANSELC register (Register 11-15) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 11.7.4 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-8.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the output priority list. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the output priority list.

| Pin Name | Function Priority <sup>(1)</sup>   |

|----------|------------------------------------|

| RC0      | CLC2<br>RC0                        |

| RC1      | NCO1 <sup>(2)</sup><br>PWM4<br>RC1 |

| RC2      | RC2                                |

| RC3      | PWM2<br>RC3                        |

CWG1B

CWG1A

CLC1<sup>(3)</sup>

NCO1<sup>(3)</sup>

PWM1

RC5

RC6

RC7

RC4

RC4

RC5

RC6

RC7

| TABLE 11-8: | PORTC OUTPUT PRIORITY |

|-------------|-----------------------|

|             |                       |

Note 1: Priority listed from highest to lowest.

2: Default pin (see APFCON register).

3: Alternate pin (see APFCON register).

# 12.0 INTERRUPT-ON-CHANGE

The PORTA and PORTB pins can be configured to operate as Interrupt-on-Change (IOC) pins. An interrupt can be generated by detecting a signal that has either a rising edge or a falling edge. Any individual port pin, or combination of port pins, can be configured to generate an interrupt. The interrupt-on-change module has the following features:

- Interrupt-on-Change enable (Master Switch)

- · Individual pin configuration

- Rising and falling edge detection

- Individual pin interrupt flags

Figure 12-1 is a block diagram of the IOC module.

#### 12.1 Enabling the Module

To allow individual port pins to generate an interrupt, the IOCIE bit of the INTCON register must be set. If the IOCIE bit is disabled, the edge detection on the pin will still occur, but an interrupt will not be generated.

#### 12.2 Individual Pin Configuration

For each port pin, a rising edge detector and a falling edge detector are present. To enable a pin to detect a rising edge, the associated bit of the IOCxP register is set. To enable a pin to detect a falling edge, the associated bit of the IOCxN register is set.

A pin can be configured to detect rising and falling edges simultaneously by setting both associated bits of the IOCxP and IOCxN registers, respectively.

#### 12.3 Interrupt Flags

The IOCAFx and IOCBFx bits located in the IOCAF and IOCBF registers, respectively, are status flags that correspond to the interrupt-on-change pins of the associated port. If an expected edge is detected on an appropriately enabled pin, then the status flag for that pin will be set, and an interrupt will be generated if the IOCIE bit is set. The IOCIF bit of the INTCON register reflects the status of all IOCAFx and IOCBFx bits.

### 12.4 Clearing Interrupt Flags

The individual status flags, (IOCAFx and IOCBFx bits), can be cleared by resetting them to zero. If another edge is detected during this clearing operation, the associated status flag will be set at the end of the sequence, regardless of the value actually being written.

In order to ensure that no detected edge is lost while clearing flags, only AND operations masking out known changed bits should be performed. The following sequence is an example of what should be performed.

#### EXAMPLE 12-1: CLEARING INTERRUPT FLAGS (PORTA EXAMPLE)

MOVLW 0xff XORWF IOCAF, W ANDWF IOCAF, F

## 12.5 Operation in Sleep

The interrupt-on-change interrupt sequence will wake the device from Sleep mode, if the IOCIE bit is set.

If an edge is detected while in Sleep mode, the IOCxF register will be updated prior to the first instruction executed out of Sleep.

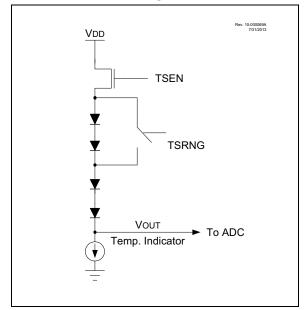

## 14.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The circuit's range of operating temperature falls between -40°C and +85°C. The output is a voltage that is proportional to the device temperature. The output of the temperature indicator is internally connected to the device ADC.

The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately. Reference Application Note AN1333, *"Use and Calibration of the Internal Temperature Indicator"* (DS01333) for more details regarding the calibration process.

## 14.1 Circuit Operation

Figure 14-1 shows a simplified block diagram of the temperature circuit. The proportional voltage output is achieved by measuring the forward voltage drop across multiple silicon junctions.

Equation 14-1 describes the output characteristics of the temperature indicator.

## EQUATION 14-1: VOUT RANGES

High Range: VOUT = VDD - 4VT

Low Range: VOUT = VDD - 2VT

The temperature sense circuit is integrated with the Fixed Voltage Reference (FVR) module. See Section **13.0 "Fixed Voltage Reference (FVR)"** for more information.

The circuit is enabled by setting the TSEN bit of the FVRCON register. When disabled, the circuit draws no current.

The circuit operates in either high or low range. The high range, selected by setting the TSRNG bit of the FVRCON register, provides a wider output voltage. This provides more resolution over the temperature range, but may be less consistent from part to part. This range requires a higher bias voltage to operate and thus, a higher VDD is needed.

The low range is selected by clearing the TSRNG bit of the FVRCON register. The low range generates a lower voltage drop and thus, a lower bias voltage is needed to operate the circuit. The low range is provided for low voltage operation.

# FIGURE 14-1: TEMPERATURE CIRCUIT DIAGRAM

# 14.2 Minimum Operating VDD

When the temperature circuit is operated in low range, the device may be operated at any operating voltage that is within specifications.

When the temperature circuit is operated in high range, the device operating voltage, VDD, must be high enough to ensure that the temperature circuit is correctly biased.

Table 14-1 shows the recommended minimum VDD vs. range setting.

#### TABLE 14-1: RECOMMENDED VDD VS. RANGE

| Min. VDD, TSRNG = 1 | Min. VDD, TSRNG = 0 |

|---------------------|---------------------|

| 3.6V                | 1.8V                |

# 14.3 Temperature Output

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to **Section 15.0 "Analog-to-Digital Converter (ADC) Module**" for detailed information.

# 14.4 ADC Acquisition Time

To ensure accurate temperature measurements, the user must wait at least 200  $\mu$ s after the ADC input multiplexer is connected to the temperature indicator output before the conversion is performed. In addition, the user must wait 200  $\mu$ s between sequential conversions of the temperature indicator output.

| R/W-0/0          | U-0          | U-0                                                 | U-0            | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|--------------|-----------------------------------------------------|----------------|----------------|------------------|------------------|--------------|

| LCxPOL           | —            | —                                                   | _              | LCxG4POL       | LCxG3POL         | LCxG2POL         | LCxG1POL     |

| bit 7            |              |                                                     |                |                |                  |                  | bit 0        |

|                  |              |                                                     |                |                |                  |                  |              |

| Legend:          |              |                                                     |                |                |                  |                  |              |

| R = Readable     | bit          | W = Writable                                        | bit            | U = Unimpler   | mented bit, read | l as '0'         |              |

| u = Bit is unch  | nanged       | x = Bit is unkn                                     | iown           | -n/n = Value a | at POR and BO    | R/Value at all c | other Resets |

| '1' = Bit is set |              | '0' = Bit is clea                                   | ared           |                |                  |                  |              |

|                  |              |                                                     |                |                |                  |                  |              |

| bit 7            | LCxPOL: LCO  | OUT Polarity C                                      | ontrol bit     |                |                  |                  |              |

|                  | •            | ut of the logic o                                   |                |                |                  |                  |              |

|                  |              | ut of the logic c                                   |                | rted           |                  |                  |              |

| bit 6-4          | Unimplemen   | Unimplemented: Read as '0'                          |                |                |                  |                  |              |

| bit 3            |              | LCxG4POL: Gate 4 Output Polarity Control bit        |                |                |                  |                  |              |

|                  |              | ut of gate 4 is in                                  |                | applied to the | logic cell       |                  |              |

| hit 0            | -            | ut of gate 4 is r                                   |                | al hit         |                  |                  |              |

| bit 2            |              | Gate 3 Output I<br>ut of gate 3 is ii               | •              |                |                  |                  |              |

|                  | •            | ut of gate 3 is in                                  |                | applied to the | logic cell       |                  |              |

| bit 1            |              | <b>LCxG2POL:</b> Gate 2 Output Polarity Control bit |                |                |                  |                  |              |

|                  | 1 = The outp | ut of gate 2 is i                                   | nverted when   | applied to the | logic cell       |                  |              |

|                  | 0 = The outp | ut of gate 2 is r                                   | not inverted   |                |                  |                  |              |

| bit 0            | LCxG1POL:    | Gate 1 Output I                                     | Polarity Contr | ol bit         |                  |                  |              |

|                  |              | ut of gate 1 is i                                   |                | applied to the | logic cell       |                  |              |

|                  | 0 = The outp | ut of gate 1 is r                                   | not inverted   |                |                  |                  |              |

#### REGISTER 20-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese '1' = Bit is set '0' = Bit is cleared bit 7 LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit 1 = lcxd4T is gated into lcxg1 0 = lcxd3T is gated into lcxg1 0 = lcxd3T is not gated into lcxg1 0 = lcxd3T is gated into lcxg1 0 = lcxd3T is gated into lcxg1 0 = lcxd3T is not gated into lcxg1 0 = lcxd2T is not gated into lcxg1 0 = lcx                                                                                                             | R/W-x/u          | R/W-x/u       | R/W-x/u          | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------|----------------|----------------|------------------|------------------|-------------|--|--|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reservers         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is not gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T is not g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LCxG1D4T         | LCxG1D4N      | LCxG1D3T         | LCxG1D3N       | LCxG1D2T       | LCxG1D2N         | LCxG1D1T         | LCxG1D1N    |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Rese         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd4N is gated into lcxg1       0 = lcxd4N is gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3N is not gated into lcxg1         0 = lcxd3N is not gated into lcxg1       0 = lcxd3N is not gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T is not g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7            |               |                  |                |                |                  |                  | bit         |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Rese         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd4N is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:          |               |                  |                |                |                  |                  |             |  |  |

| '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is not gated into lcxg1       0 = lcxd4N is gated into lcxg1         0 = lcxd4N is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd4N is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd4N is not gated into lcxg1       0 = lcxd3T is gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3N is gated into lcxg1       0 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1       0 = lcxd3N is not gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is og tated into lcxg1       0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                | bit           | W = Writable     | bit            | U = Unimpler   | mented bit, read | as '0'           |             |  |  |

| bit 7 LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit<br>1 = lcxd4T is gated into lcxg1<br>0 = lcxd4T is not gated into lcxg1<br>bit 6 LCxG1D4N: Gate 1 Data 4 Negated (inverted) bit<br>1 = lcxd4N is gated into lcxg1<br>0 = lcxd4N is not gated into lcxg1<br>bit 5 LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit<br>1 = lcxd3T is gated into lcxg1<br>0 = lcxd3T is not gated into lcxg1<br>0 = lcxd3T is not gated into lcxg1<br>bit 4 LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit<br>1 = lcxd3N is gated into lcxg1<br>0 = lcxd3N is gated into lcxg1<br>0 = lcxd3N is not gated into lcxg1<br>bit 3 LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit<br>1 = lcxd2T is not gated into lcxg1<br>0 = lcxd2T is not gated into lcxg1<br>bit 2 LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit<br>1 = lcxd2N: Gate 1 Data 2 Negated (inverted) bit<br>1 = lcxd2N is not gated into lcxg1<br>0 = lcxd2T is gated into lcxg1<br>0 = lcxd2T is not gated into lcxg1<br>0 = lcxd2N is not gated into lcxg1<br>0 = lcxd1T is gated into lcxg1<br>0 = lcxd1T is gated into lcxg1<br>0 = lcxd1T is not gated into lcxg1<br>0 = lcxd1 | u = Bit is uncha | anged         | x = Bit is unkr  | nown           | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |  |

| 1 = lcxd4T is gated into lcxg1         0 = lcxd4T is not gated into lcxg1         bit 6       LCxG1D4N: Gate 1 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg1         0 = lcxd4N is not gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd2T is gated into lcxg1         0 = lcxd2N is not gated into lcxg1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | '1' = Bit is set | -             | '0' = Bit is cle | ared           |                |                  |                  |             |  |  |

| 1 = lcxd4T is gated into lcxg1         0 = lcxd4T is not gated into lcxg1         bit 6       LCxG1D4N: Gate 1 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg1         0 = lcxd4N is not gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1         0 = lcxd3T is not gated into lcxg1         bit 4       LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd2T is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd1T is gated into lcxg1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | L:1 7            |               |                  | <b>F</b>       |                |                  |                  |             |  |  |

| 0 = lcxd4T is not gated into lcxg1         bit 6       LCxG1D4N: Gate 1 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg1         0 = lcxd4N is not gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1         0 = lcxd3T is ont gated into lcxg1         0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is not gated into lcxg1         0 = lcxd3N is not gated into lcxg1         0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2N is gated into lcxg1         0 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DIT /            |               |                  |                | rted) bit      |                  |                  |             |  |  |

| bit 6       LCxG1D4N: Gate 1 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg1         0 = lcxd4N is not gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1         0 = lcxd3T is not gated into lcxg1         bit 4       LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit         1 = lcxd3T is not gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is not gated into lcxg1         0 = lcxd3N is not gated into lcxg1         bit 3       LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd1T is gated into lcxg1         0 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |               |                  |                |                |                  |                  |             |  |  |

| 1 = lcxd4N is gated into lcxg1         0 = lcxd4N is not gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1         0 = lcxd3T is not gated into lcxg1         bit 4       LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is not gated into lcxg1         0 = lcxd2T Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | bit 6            |               | •                | •              | rted) bit      |                  |                  |             |  |  |

| 0 = lcxd4N is not gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1         0 = lcxd3T is not gated into lcxg1         bit 4       LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is not gated into lcxg1         0 = lcxd3N is not gated into lcxg1         0 = lcxd2T: Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd1T: Gate 1 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg1         0 = lcxd1T is not                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                  |               |                  | •              |                |                  |                  |             |  |  |

| 1 = lcxd3T is gated into lcxg1         0 = lcxd3T is not gated into lcxg1         bit 4       LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg1         0 = lcxd3N is not gated into lcxg1         0 = lcxd3N is not gated into lcxg1         bit 3       LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1         bit 2       LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         bit 1       LCxG1D1T: Gate 1 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                  |               |                  |                |                |                  |                  |             |  |  |

| 0 = lcxd3T is not gated into lcxg1         bit 4       LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg1         0 = lcxd3N is not gated into lcxg1         bit 3       LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1         bit 2       LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | bit 5            | LCxG1D3T:     | Gate 1 Data 3 1  | Frue (non-inve | rted) bit      |                  |                  |             |  |  |

| bit 4       LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit         1 = lcxd3N is gated into lcxg1         0 = lcxd3N is not gated into lcxg1         bit 3       LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd1T is gated into lcxg1         0 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         0 = lcxd1T is not gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |               |                  |                |                |                  |                  |             |  |  |

| 1 = lcxd3N is gated into lcxg1         0 = lcxd3N is not gated into lcxg1         bit 3       LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         bit 2       LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         bit 1       LCxG1D1T: Gate 1 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 = Icxd3T       |               | •                | •              |                |                  |                  |             |  |  |

| 0 = lcxd3N is not gated into lcxg1         bit 3       LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         bit 2       LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         bit 1       LCxG1D1T: Gate 1 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 4            |               |                  | •              | rted) bit      |                  |                  |             |  |  |

| bit 3       LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit         1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         bit 2       LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         0 = lcxd2N is not gated into lcxg1         bit 1       LCxG1D1T: Gate 1 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |               |                  |                |                |                  |                  |             |  |  |

| 1 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1         bit 2       LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         bit 1       LCxG1D1T: Gate 1 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | hit 2            |               | •                | •              | rtad) bit      |                  |                  |             |  |  |

| 0 = lcxd2T is not gated into lcxg1         bit 2       LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         bit 1       LCxG1D1T: Gate 1 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DIL 3            |               |                  |                | neu) bii       |                  |                  |             |  |  |

| bit 2       LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit         1 = lcxd2N is gated into lcxg1         0 = lcxd2N is not gated into lcxg1         bit 1       LCxG1D1T: Gate 1 Data 1 True (non-inverted) bit         1 = lcxd1T is gated into lcxg1         0 = lcxd1T is not gated into lcxg1         bit 0       LCxG1D1N: Gate 1 Data 1 Negated (inverted) bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                  |               |                  |                |                |                  |                  |             |  |  |