Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 20-QFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1507-i-ml |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 3-3: PIC16(L)F1507 MEMORY MAP (CONTINUED)

|              | BANK 24                               |              | BANK 25                               |              | BANK 26                               |              | BANK 27                               |              | BANK 28                               |              | BANK 29                               |              | BANK 30                               |              | BANK 31                               |

|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|--------------|---------------------------------------|

| C00h         | Core Registers<br>(Table 3-2)         | C80h         | Core Registers<br>(Table 3-2)         | D00h         | Core Registers<br>(Table 3-2)         | D80h         | Core Registers<br>(Table 3-2)         | E00h         | Core Registers<br>(Table 3-2)         | E80h         | Core Registers<br>(Table 3-2)         | F00h         | Core Registers<br>(Table 3-2)         | F80h         | Core Registers<br>(Table 3-2)         |

| C0Bh         |                                       | C8Bh         |                                       | D0Bh         |                                       | D8Bh         |                                       | E0Bh         |                                       | E8Bh         |                                       | F0Bh         |                                       | F8Bh         |                                       |

| C0Ch         | —                                     | C8Ch         | —                                     | D0Ch         | —                                     | D8Ch         | —                                     | E0Ch         | —                                     | E8Ch         | —                                     | F0Ch         |                                       | F8Ch         |                                       |

| C0Dh         | —                                     | C8Dh         | —                                     | D0Dh         | —                                     | D8Dh         | —                                     | E0Dh         | —                                     | E8Dh         | _                                     | F0Dh         |                                       | F8Dh         |                                       |

| C0Eh         | —                                     | C8Eh         | _                                     | D0Eh         | —                                     | D8Eh         | —                                     | E0Eh         | _                                     | E8Eh         |                                       | F0Eh         |                                       | F8Eh         |                                       |

| C0Fh         | —                                     | C8Fh         | -                                     | D0Fh         | —                                     | D8Fh         | —                                     | E0Fh         | -                                     | E8Fh         | _                                     | F0Fh         |                                       | F8Fh         |                                       |

| C10h         | —                                     | C90h         | _                                     | D10h         | —                                     | D90h         | —                                     | E10h         | —                                     | E90h         | _                                     | F10h         |                                       | F90h         |                                       |

| C11h         | —                                     | C91h         | _                                     | D11h         | —                                     | D91h         | —                                     | E11h         | _                                     | E91h         |                                       | F11h         |                                       | F91h         |                                       |

| C12h         | —                                     | C92h         | _                                     | D12h         | —                                     | D92h         | —                                     | E12h         | _                                     | E92h         |                                       | F12h         |                                       | F92h         |                                       |

| C13h         | —                                     | C93h         | _                                     | D13h         | —                                     | D93h         | —                                     | E13h         | _                                     | E93h         |                                       | F13h         |                                       | F93h         |                                       |

| C14h         | —                                     | C94h         | —                                     | D14h         | —                                     | D94h         | —                                     | E14h         | —                                     | E94h         | —                                     | F14h         |                                       | F94h         |                                       |

| C15h         | —                                     | C95h         | —                                     | D15h         | —                                     | D95h         | —                                     | E15h         | —                                     | E95h         | —                                     | F15h         |                                       | F95h         |                                       |

| C16h         | —                                     | C96h         | —                                     | D16h         | —                                     | D96h         | —                                     | E16h         | —                                     | E96h         | _                                     | F16h         |                                       | F96h         |                                       |

| C17h         | _                                     | C97h         | —                                     | D17h         | _                                     | D97h         | _                                     | E17h         | —                                     | E97h         | _                                     | F17h         | See Table 3-3 for                     | F97h         | See Table 3-3 for                     |

| C18h         | _                                     | C98h         | —                                     | D18h         | _                                     | D98h         | _                                     | E18h         | —                                     | E98h         | _                                     | F18h         | register mapping                      | F98h         | register mapping                      |

| C19h         | _                                     | C99h         | —                                     | D19h         | _                                     | D99h         | _                                     | E19h         | —                                     | E99h         | _                                     | F19h         | details                               | F99h         | details                               |

| C1Ah         | _                                     | C9Ah         | _                                     | D1Ah         | _                                     | D9Ah         | _                                     | E1Ah         | —                                     | E9Ah         | _                                     | F1Ah         |                                       | F9Ah         |                                       |

| C1Bh         | _                                     | C9Bh         | —                                     | D1Bh         | _                                     | D9Bh         | _                                     | E1Bh         | —                                     | E9Bh         | —                                     | F1Bh         |                                       | F9Bh         |                                       |

| C1Ch         | _                                     | C9Ch         | —                                     | D1Ch         | _                                     | D9Ch         | _                                     | E1Ch         | —                                     | E9Ch         | —                                     | F1Ch         |                                       | F9Ch         |                                       |

| C1Dh         | _                                     | C9Dh         | —                                     | D1Dh         | _                                     | D9Dh         | _                                     | E1Dh         | —                                     | E9Dh         | _                                     | F1Dh         |                                       | F9Dh         |                                       |

| C1Eh         | _                                     | C9Eh         | —                                     | D1Eh         | —                                     | D9Eh         | _                                     | E1Eh         | —                                     | E9Eh         | _                                     | F1Eh         |                                       | F9Eh         |                                       |

| C1Fh         | _                                     | C9Fh         | —                                     | D1Fh         | —                                     | D9Fh         | _                                     | E1Fh         | —                                     | E9Fh         | _                                     | F1Fh         |                                       | F9Fh         |                                       |

| C20h         |                                       | CA0h         |                                       | D20h         |                                       | DA0h         |                                       | E20h         |                                       | EA0h         |                                       | F20h         |                                       | FA0h         |                                       |

|              | Unimplemented<br>Read as '0'          |              |                                       |              |                                       |

| C6Fh         |                                       | CEFh         |                                       | D6Fh         |                                       | DEFh         |                                       | E6Fh         |                                       | EEFh         |                                       | F6Fh         |                                       | FEFh         |                                       |

| C70h<br>CFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | CF0h<br>CFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | D70h<br>D7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | DF0h<br>DFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | E70h<br>E7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | EF0h<br>EFFh | Common RAM<br>(Accesses<br>70h – 7Fh) | F70h<br>F7Fh | Common RAM<br>(Accesses<br>70h – 7Fh) | FF0h<br>FFFh | Common RAM<br>(Accesses<br>70h – 7Fh) |

Legend: = Unimplemented data memory locations, read as '0'.

## 5.2 Clock Source Types

Clock sources can be classified as external, internal or peripheral.

External clock sources rely on external circuitry for the clock source to function. Examples are: oscillator modules (ECH, ECM, ECL modes).

Internal clock sources are contained within the oscillator module. The internal oscillator block has two internal oscillators that are used to generate the internal system clock sources: the 16 MHz High-Frequency Internal Oscillator (HFINTOSC) and the 31 kHz Low-Frequency Internal Oscillator (LFINTOSC).

The peripheral clock source is a nominal 600 kHz internal RC oscillator, FRC. The FRC is traditionally used with the ADC module, but is sometimes available to other peripherals. See **Section 5.2.2.4** "**Peripheral Clock Sources**".

The system clock can be selected between external or internal clock sources via the System Clock Select (SCS) bits in the OSCCON register. See **Section 5.3 "Clock Switching"** for additional information.

#### 5.2.1 EXTERNAL CLOCK SOURCES

An external clock source can be used as the device system clock by performing one of the following actions:

- Program the FOSC<1:0> bits in the Configuration Words to select an external clock source that will be used as the default system clock upon a device Reset.

- Write the SCS<1:0> bits in the OSCCON register to switch the system clock source to:

- Secondary oscillator during run-time, or

- An external clock source determined by the value of the FOSC bits.

See **Section 5.3 "Clock Switching**" for more information.

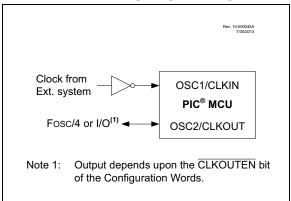

#### 5.2.1.1 EC Mode

The External Clock (EC) mode allows an externally generated logic level signal to be the system clock source. When operating in this mode, an external clock source is connected to the OSC1 input. OSC2/CLKOUT is available for general purpose I/O or CLKOUT. Figure 5-2 shows the pin connections for EC mode.

EC mode has three power modes to select from through the Fosc bits in the Configuration Words:

- ECH High power, 4-20 MHz

- ECM Medium power, 0.5-4 MHz

- ECL Low power, 0-0.5 MHz

#### FIGURE 5-2: EXTERNAL CLOCK (EC) MODE OPERATION

## 5.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the System Clock Select (SCS) bits of the OSCCON register. The following clock sources can be selected using the SCS bits:

- Default system oscillator determined by FOSC bits in Configuration Words

- Internal Oscillator Block (INTOSC)

#### 5.3.1 SYSTEM CLOCK SELECT (SCS) BITS

The System Clock Select (SCS) bits of the OSCCON register selects the system clock source that is used for the CPU and peripherals.

- When the SCS bits of the OSCCON register = 00, the system clock source is determined by value of the FOSC<1:0> bits in the Configuration Words.

- When the SCS bits of the OSCCON register = 01, the system clock source is the secondary oscillator.

- When the SCS bits of the OSCCON register = 1x, the system clock source is chosen by the internal oscillator frequency selected by the IRCF<3:0>

#### TABLE 5-2: OSCILLATOR SWITCHING DELAYS

bits of the OSCCON register. After a Reset, the SCS bits of the OSCCON register are always cleared.

When switching between clock sources, a delay is required to allow the new clock to stabilize. These oscillator delays are shown in Table 5-2.

## 5.3.2 CLOCK SWITCHING BEFORE SLEEP

When clock switching from an old clock to a new clock is requested just prior to entering Sleep mode, it is necessary to confirm that the switch is complete before the SLEEP instruction is executed. Failure to do so may result in an incomplete switch and consequential loss of the system clock altogether. Clock switching is confirmed by monitoring the clock status bits in the OSCSTAT register. Switch confirmation can be accomplished by sensing that the ready bit for the new clock is set or the ready bit for the old clock is cleared. For example, when switching between the internal oscillator with the PLL and the internal oscillator without the PLL, monitor the PLLR bit. When PLLR is set, the switch to 32 MHz operation is complete. Conversely, when PPLR is cleared, the switch from 32 MHz operation to the selected internal clock is complete.

| Switch From      | Switch To     | Oscillator Delay             |

|------------------|---------------|------------------------------|

|                  | LFINTOSC      | 1 cycle of each clock source |

| Any clock source | HFINTOSC      | 2 μs (approx.)               |

|                  | ECH, ECM, ECL | 2 cycles                     |

### 6.1 Power-On Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.1.1 POWER-UP TIMER (PWRT)

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

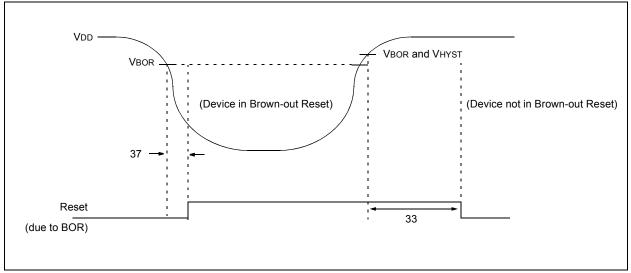

### 6.2 Brown-Out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- BOR is always on

- · BOR is off when in Sleep

- BOR is controlled by software

- · BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below Vpor for a duration greater than parameter TBORDC, the device will reset. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |  |  |  |

|------------|--------|-------------|----------|---------------------------------------------------------------------|--|--|--|

| 11         | Х      | Х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |

| 1.0        |        | Awake       | Active   | Waits for BOR ready                                                 |  |  |  |

| 10         | Х      | Sleep       | Disabled | (BORRDY = 1)                                                        |  |  |  |

| 01         | 1      | х           | Active   | Waits for BOR ready <sup>(1)</sup><br>(BORRDY = 1)                  |  |  |  |

|            | 0      | Х           | Disabled | Begins immediately                                                  |  |  |  |

| 00         | Х      | Х           | Disabled | (BORRDY = x)                                                        |  |  |  |

TABLE 6-1:BOR OPERATING MODES

Note 1: In these specific cases, "release of POR" and "wake-up from Sleep," there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold. BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device start-up is not delayed by the BOR ready condition or the VDD level.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

## 11.6 Register Definitions: PORTB

### REGISTER 11-7: PORTB: PORTB REGISTER

| R/W-x/x                             | R/W-x/x | R/W-x/x           | R/W-x/x        | U-0           | U-0              | U-0          | U-0   |

|-------------------------------------|---------|-------------------|----------------|---------------|------------------|--------------|-------|

| RB7                                 | RB6     | RB5               | RB4            |               | —                | —            | —     |

| bit 7                               |         |                   |                |               |                  |              | bit 0 |

|                                     |         |                   |                |               |                  |              |       |

| Legend:                             |         |                   |                |               |                  |              |       |

| R = Readable I                      | bit     | W = Writable      | bit            | U = Unimpler  | mented bit, read | as '0'       |       |

| u = Bit is unchanged x = Bit is unk |         | nown              | -n/n = Value a | at POR and BO | R/Value at all c | other Resets |       |

| '1' = Bit is set                    |         | '0' = Bit is clea | ared           |               |                  |              |       |

| bit 7-4 | RB<7:4>: PORTB I/O Value bits <sup>(1)</sup> |

|---------|----------------------------------------------|

|         | 1 = Port pin is <u>&gt;</u> Vін              |

|         | 0 = Port pin is <u>&lt;</u> VIL              |

bit 3-0 Unimplemented: Read as '0'

**Note 1:** Writes to PORTB are actually written to corresponding LATB register. Reads from PORTB register is return of actual I/O pin values.

### REGISTER 11-8: TRISB: PORTB TRI-STATE REGISTER

| R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| TRISB7  | TRISB6  | TRISB5  | TRISB4  | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | RB<7:4>: PORTB Tri-State Control bits             |

|---------|---------------------------------------------------|

|         | 1 = PORTB pin configured as an input (tri-stated) |

|         | 0 = PORTB pin configured as an output             |

|         |                                                   |

bit 3-0 Unimplemented: Read as '0'

## 11.7 PORTC Registers

### 11.7.1 DATA REGISTER

PORTC is a 8-bit wide, bidirectional port. The corresponding data direction register is TRISC (Register 11-13). Setting a TRISC bit (= 1) will make the corresponding PORTC pin an input (i.e., disable the output driver). Clearing a TRISC bit (= 0) will make the corresponding PORTC pin an output (i.e., enable the output driver and put the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTC register (Register 11-12) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATC).

### 11.7.2 DIRECTION CONTROL

The TRISC register (Register 11-13) controls the PORTC pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISC register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

### 11.7.3 ANALOG CONTROL

The ANSELC register (Register 11-15) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELC bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELC bits has no effect on digital output functions. A pin with TRIS clear and ANSELC set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELC bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 11.7.4 PORTC FUNCTIONS AND OUTPUT PRIORITIES

Each PORTC pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-8.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input and some digital input functions are not included in the output priority list. These input functions can remain active when the pin is configured as an output. Certain digital input functions override other port functions and are included in the output priority list.

| Pin Name | Function Priority <sup>(1)</sup>   |

|----------|------------------------------------|

| RC0      | CLC2<br>RC0                        |

| RC1      | NCO1 <sup>(2)</sup><br>PWM4<br>RC1 |

| RC2      | RC2                                |

| RC3      | PWM2<br>RC3                        |

CWG1B

CWG1A

CLC1<sup>(3)</sup>

NCO1<sup>(3)</sup>

PWM1

RC5

RC6

RC7

RC4

RC4

RC5

RC6

RC7

| TABLE 11-8: | PORTC OUTPUT PRIORITY |

|-------------|-----------------------|

|             |                       |

Note 1: Priority listed from highest to lowest.

2: Default pin (see APFCON register).

3: Alternate pin (see APFCON register).

#### REGISTER 12-4: IOCBP: INTERRUPT-ON-CHANGE PORTB POSITIVE EDGE REGISTER

| R/W-0/0                               | R/W-0/0 | R/W-0/0          | R/W-0/0 | U-0                                | U-0           | U-0                 | U-0    |  |

|---------------------------------------|---------|------------------|---------|------------------------------------|---------------|---------------------|--------|--|

| IOCBP7                                | IOCBP6  | IOCBP5           | IOCBP4  | _                                  | —             | —                   | _      |  |

| bit 7                                 |         |                  |         |                                    |               |                     | bit 0  |  |

|                                       |         |                  |         |                                    |               |                     |        |  |

| Legend:                               |         |                  |         |                                    |               |                     |        |  |

| R = Readable bi                       | t       | W = Writable bi  | it      | U = Unimplemented bit, read as '0' |               |                     |        |  |

| u = Bit is unchanged x = Bit i        |         | x = Bit is unkno | own     | -n/n = Value at                    | POR and BOR/V | alue at all other l | Resets |  |

| '1' = Bit is set '0' = Bit is cleared |         |                  |         |                                    |               |                     |        |  |

IOCBP<7:4>: Interrupt-on-Change PORTB Positive Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a positive going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 3-0 Unimplemented: Read as '0'

bit 7-4

#### REGISTER 12-5: IOCBN: INTERRUPT-ON-CHANGE PORTB NEGATIVE EDGE REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| IOCBN7  | IOCBN6  | IOCBN5  | IOCBN4  | —   | _   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4

IOCBN<7:4>: Interrupt-on-Change PORTB Negative Edge Enable bits

1 = Interrupt-on-Change enabled on the pin for a negative going edge. IOCBFx bit and IOCIF flag will be set upon detecting an edge.

0 = Interrupt-on-Change disabled for the associated pin.

bit 3-0

Unimplemented: Read as '0'

#### REGISTER 12-6: IOCBF: INTERRUPT-ON-CHANGE PORTB FLAG REGISTER

| R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0   |

|------------|------------|------------|------------|-----|-----|-----|-------|

| IOCBF7     | IOCBF6     | IOCBF5     | IOCBF4     | _   | _   | _   | —     |

| bit 7      |            |            |            |     |     |     | bit 0 |

| table bit U = Unimplemented bit, read as '0'                  |

|---------------------------------------------------------------|

| unknown -n/n = Value at POR and BOR/Value at all other Resets |

| is cleared HS - Bit is set in hardware                        |

| is                                                            |

| bit 7-4 | <ul> <li>IOCBF&lt;7:4&gt;: Interrupt-on-Change PORTB Flag bits</li> <li>1 = An enabled change was detected on the associated pin.<br/>Set when IOCBPx = 1 and a rising edge was detected on RBx, or when IOCBNx = 1 and a falling edge was detected on RBx.</li> <li>0 = No change was detected, or the user cleared the detected change.</li> </ul> |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3-0 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                           |

## 15.2 ADC Operation

#### 15.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

| Note: | The GO/DONE bit should not be set in the |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | same instruction that turns on the ADC.  |  |  |  |  |  |

|       | Refer to Section 15.2.6 "ADC Conver-     |  |  |  |  |  |

|       | sion Procedure".                         |  |  |  |  |  |

#### 15.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF Interrupt Flag bit

- Update the ADRESH and ADRESL registers with new conversion result

#### 15.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH and ADRESL registers will be updated with the partially complete Analog-to-Digital conversion sample. Incomplete bits will match the last bit converted.

| Note: | A device Reset forces all registers to their |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|

|       | Reset state. Thus, the ADC module is         |  |  |  |  |  |

|       | turned off and any pending conversion is     |  |  |  |  |  |

|       | terminated.                                  |  |  |  |  |  |

#### 15.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. Performing the ADC conversion during Sleep can reduce system noise. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

### 15.2.5 AUTO-CONVERSION TRIGGER

The auto-conversion trigger allows periodic ADC measurements without software intervention. When a rising edge of the selected source occurs, the GO/DONE bit is set by hardware.

The auto-conversion trigger source is selected with the TRIGSEL<3:0> bits of the ADCON2 register.

Using the auto-conversion trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

See Table 15-2 for auto-conversion sources.

#### TABLE 15-2: AUTO-CONVERSION SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| Timer0            | T0_overflow |

| Timer1            | T1_overflow |

| Timer2            | T2_match    |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

## 17.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer and increments on every instruction cycle. When used with an external clock source, the module can be used as either a timer or counter and increments on every selected edge of the external source.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 17-1 displays the Timer1 enable selections.

TABLE 17-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

## 17.2 Clock Source Selection

The TMR1CS<1:0> bits of the T1CON register are used to select the clock source for Timer1. Table 17-2 displays the clock source selections.

#### 17.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected, the TMR1H:TMR1L register pair will increment on multiples of Fosc as determined by the Timer1 prescaler.

When the Fosc internal clock source is selected, the Timer1 register value will increment by four counts every instruction clock cycle. Due to this condition, a 2 LSB error in resolution will occur when reading the Timer1 value. To utilize the full resolution of Timer1, an asynchronous input signal must be used to gate the Timer1 clock input.

The following asynchronous sources may be used:

- Asynchronous event on the T1G pin to Timer1

gate

- C1 or C2 comparator input to Timer1 gate

#### 17.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When enabled to count, Timer1 is incremented on the rising edge of the external clock input T1CKI. The external clock source can be synchronized to the microcontroller system clock or it can run asynchronously.

Note: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the following conditions:

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

### TABLE 17-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | Clock Source                   |

|-------------|--------------------------------|

| 11          | LFINTOSC                       |

| 10          | External Clocking on T1CKI Pin |

| 01          | System Clock (Fosc)            |

| 00          | Instruction Clock (Fosc/4)     |

© 2011-2015 Microchip Technology Inc.

| R/W-0/u          | R/W-0/u                                                                                                                                                  | R/W-0/u                                                       | R/W-0/u      | R/W/HC-0/u                         | R-x/x           | U-0              | R/W-0/u      |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|--------------|------------------------------------|-----------------|------------------|--------------|--|--|--|

| TMR1GE           | T1GPOL                                                                                                                                                   | T1GTM                                                         | T1GSPM       | T1GGO/<br>DONE                     | T1GVAL          | _                | T1GSS        |  |  |  |

| bit 7            |                                                                                                                                                          | •                                                             |              | •                                  |                 |                  | bit          |  |  |  |

|                  |                                                                                                                                                          |                                                               |              |                                    |                 |                  |              |  |  |  |

| Legend:          |                                                                                                                                                          |                                                               |              |                                    |                 |                  |              |  |  |  |

| R = Readable     | bit                                                                                                                                                      | W = Writable                                                  | bit          | U = Unimplemented bit, read as '0' |                 |                  |              |  |  |  |

| u = Bit is uncl  | nanged                                                                                                                                                   | x = Bit is unk                                                | nown         | -n/n = Value a                     | at POR and BO   | R/Value at all o | other Resets |  |  |  |

| '1' = Bit is set |                                                                                                                                                          | '0' = Bit is cle                                              | ared         | HC = Bit is cle                    | eared by hardw  | vare             |              |  |  |  |

| hit 7            |                                                                                                                                                          | mart Cata Eng                                                 | bla bit      |                                    |                 |                  |              |  |  |  |

| bit 7            | If TMR10P.                                                                                                                                               | mer1 Gate Ena<br>= 0 <sup>.</sup>                             |              |                                    |                 |                  |              |  |  |  |

|                  | This bit is ign                                                                                                                                          |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | If TMR10N =                                                                                                                                              | <u>If TMR10N = 1</u> :                                        |              |                                    |                 |                  |              |  |  |  |

|                  |                                                                                                                                                          | 1 = Timer1 counting is controlled by the Timer1 gate function |              |                                    |                 |                  |              |  |  |  |

| bit 6            | <ul> <li>0 = Timer1 counts regardless of Timer1 gate function</li> <li>T1GPOL: Timer1 Gate Polarity bit</li> </ul>                                       |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | 1 = Timer1 gate is active-high (Timer1 counts when gate is high)                                                                                         |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | 0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                                                                           |                                                               |              |                                    |                 |                  |              |  |  |  |

| bit 5            | T1GTM: Timer1 Gate Toggle Mode bit                                                                                                                       |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | 1 = Timer1 Gate Toggle mode is enabled                                                                                                                   |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | <ul> <li>0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared</li> <li>Timer1 gate flip-flop toggles on every rising edge.</li> </ul> |                                                               |              |                                    |                 |                  |              |  |  |  |

| bit 4            | -                                                                                                                                                        |                                                               | -            |                                    |                 |                  |              |  |  |  |

|                  | <b>T1GSPM:</b> Timer1 Gate Single-Pulse Mode bit<br>1 = Timer1 gate Single-Pulse mode is enabled and is controlling Timer1 gate                          |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | 0 = Timer1 gate Single-Pulse mode is disabled                                                                                                            |                                                               |              |                                    |                 |                  |              |  |  |  |

| bit 3            | T1GGO/DONE: Timer1 Gate Single-Pulse Acquisition Status bit                                                                                              |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | 1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge                                                                                   |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | 0 = Timer1 gate single-pulse acquisition has completed or has not been started                                                                           |                                                               |              |                                    |                 |                  |              |  |  |  |

| bit 2            | <b>T1GVAL:</b> Timer1 Gate Value Status bit<br>Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L.                     |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  |                                                                                                                                                          | y Timer1 Gate                                                 | •            |                                    | e provided to 1 | MR1H: I MR1L     |              |  |  |  |

| bit 1            | Unimplemer                                                                                                                                               | nted: Read as '                                               | 0'           |                                    |                 |                  |              |  |  |  |

| bit 0            | T1GSS: Time                                                                                                                                              | er1 Gate Sourc                                                | e Select bit |                                    |                 |                  |              |  |  |  |

|                  |                                                                                                                                                          |                                                               |              |                                    |                 |                  |              |  |  |  |

|                  | 0 = Timer1                                                                                                                                               | gate pin (T1G)                                                |              |                                    |                 |                  |              |  |  |  |

## REGISTER 17-2: T1GCON: TIMER1 GATE CONTROL REGISTER

## 19.1.9 SETUP FOR PWM OPERATION USING PWMx PINS

The following steps should be taken when configuring the module for PWM operation using the PWMx pins:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Clear the PWMxCON register.

- 3. Load the PR2 register with the PWM period value.

- 4. Clear the PWMxDCH register and bits <7:6> of the PWMxDCL register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register. See note below.

- Configure the T2CKPS bits of the T2CON register with the Timer2 prescale value.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output pin and wait until Timer2 overflows, TMR2IF bit of the PIR1 register is set. See note below.

- 7. Enable the PWMx pin output driver(s) by clearing the associated TRIS bit(s) and setting the PWMxOE bit of the PWMxCON register.

- 8. Configure the PWM module by loading the PWMxCON register with the appropriate values.

- Note 1: In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then move Step 8 to replace Step 4.

- 2: For operation with other peripherals only, disable PWMx pin outputs.

| U-0            | R/W-x/u                                                                          | R/W-x/u                                                                          | R/W-x/u      | U-0                        | R/W-x/u                    | R/W-x/u           | R/W-x/u    |  |

|----------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------|----------------------------|----------------------------|-------------------|------------|--|

| _              | — LCxD4S<2:0> <sup>(1)</sup>                                                     |                                                                                  | —            | l                          | _CxD3S<2:0> <sup>(1)</sup> |                   |            |  |

| bit 7          |                                                                                  |                                                                                  |              |                            |                            |                   | bit 0      |  |

|                |                                                                                  |                                                                                  |              |                            |                            |                   |            |  |

| Legend:        |                                                                                  |                                                                                  |              |                            |                            |                   |            |  |

| R = Readal     | ole bit                                                                          | W = Writable t                                                                   | bit          | U = Unimple                | mented bit, read           | d as '0'          |            |  |

| u = Bit is ur  | nchanged                                                                         | x = Bit is unkn                                                                  | own          | -n/n = Value               | at POR and BC              | R/Value at all ot | her Resets |  |

| '1' = Bit is s | et                                                                               | '0' = Bit is clea                                                                | red          |                            |                            |                   |            |  |

|                |                                                                                  |                                                                                  |              |                            |                            |                   |            |  |

| bit 7          | Unimpleme                                                                        | ented: Read as '0                                                                | ,            |                            |                            |                   |            |  |

| bit 6-4        | LCxD4S<2                                                                         | :0>: Input Data 4                                                                | Selection Co | ontrol bits <sup>(1)</sup> |                            |                   |            |  |

|                | 111 = LCx                                                                        | _in[3] is selected f                                                             | or lcxd4     |                            |                            |                   |            |  |

|                | 110 = LCx                                                                        | in[2] is selected t                                                              | or lcxd4     |                            |                            |                   |            |  |

|                | -                                                                                | _in[1] is selected f                                                             |              |                            |                            |                   |            |  |

|                |                                                                                  | _in[0] is selected                                                               |              |                            |                            |                   |            |  |

|                |                                                                                  | _in[15] is selected                                                              |              |                            |                            |                   |            |  |

|                | -                                                                                | _in[14] is selected                                                              |              |                            |                            |                   |            |  |

|                |                                                                                  | _in[13] is selected<br>in[12] is selected                                        |              |                            |                            |                   |            |  |

| bit 3          | -                                                                                | nted: Read as '0                                                                 |              |                            |                            |                   |            |  |

| bit 2-0        | -                                                                                |                                                                                  |              | ntral hita(1)              |                            |                   |            |  |

| DIL 2-0        |                                                                                  | :0>: Input Data 3                                                                |              |                            |                            |                   |            |  |

|                | -                                                                                | _in[15] is selected                                                              |              |                            |                            |                   |            |  |

|                |                                                                                  | 110 = LCx_in[14] is selected for lcxd3<br>101 = LCx_in[13] is selected for lcxd3 |              |                            |                            |                   |            |  |

|                |                                                                                  | _in[13] is selected<br>_in[12] is selected                                       |              |                            |                            |                   |            |  |

|                |                                                                                  |                                                                                  |              |                            |                            |                   |            |  |

|                | 011 = LCx_in[11] is selected for lcxd3<br>010 = LCx in[10] is selected for lcxd3 |                                                                                  |              |                            |                            |                   |            |  |

|                | -                                                                                | _in[9] is selected i                                                             |              |                            |                            |                   |            |  |

|                |                                                                                  | in[8] is selected i                                                              |              |                            |                            |                   |            |  |

## REGISTER 20-4: CLCxSEL1: MULTIPLEXER DATA 3 AND 4 SELECT REGISTER

**Note 1:** See Table 20-1 for signal names associated with inputs.

| bit 7 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Rese '1' = Bit is set '0' = Bit is cleared bit 7 LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit 1 = lcxd4T is gated into lcxg1 0 = lcxd3T is gated into lcxg1 0 = lcxd3T is not gated into lcxg1 0 = lcxd3T is gated into lcxg1 0 = lcxd3T is gated into lcxg1 0 = lcxd3T is not gated into lcxg1 0 = lcxd2T is not gated into lcxg1 0 = lcx                                                                                                             | R/W-x/u          | R/W-x/u       | R/W-x/u          | R/W-x/u        | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|------------------|----------------|----------------|------------------|------------------|-------------|--|--|

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Reservers         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is not gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T is not g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | LCxG1D4T         | LCxG1D4N      | LCxG1D3T         | LCxG1D3N       | LCxG1D2T       | LCxG1D2N         | LCxG1D1T         | LCxG1D1N    |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Rese         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd4N is gated into lcxg1       0 = lcxd4N is gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3N is not gated into lcxg1         0 = lcxd3N is not gated into lcxg1       0 = lcxd3N is not gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T is not g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 7            |               |                  |                |                |                  |                  | bit         |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         u = Bit is unchanged       x = Bit is unknown       -n/n = Value at POR and BOR/Value at all other Rese         '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd4N is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3T is not gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is not gated into lcxg1       0 = lcxd2T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Legend:          |               |                  |                |                |                  |                  |             |  |  |

| '1' = Bit is set       '0' = Bit is cleared         bit 7       LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit         1 = lcxd4T is gated into lcxg1       0 = lcxd4T is not gated into lcxg1         0 = lcxd4T is not gated into lcxg1       0 = lcxd4N is gated into lcxg1         0 = lcxd4N is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd4N is gated into lcxg1       0 = lcxd4N is not gated into lcxg1         0 = lcxd4N is not gated into lcxg1       0 = lcxd3T is gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is gated into lcxg1         0 = lcxd3T is gated into lcxg1       0 = lcxd3T is not gated into lcxg1         0 = lcxd3N is gated into lcxg1       0 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1       0 = lcxd3N is not gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is og tated into lcxg1       0 = lcxd2T is not gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is gated into lcxg1       0 = lcxd2T is gated into lcxg1         0 = lcxd2T is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                | bit           | W = Writable     | bit            | U = Unimpler   | mented bit, read | as '0'           |             |  |  |

| bit 7 LCxG1D4T: Gate 1 Data 4 True (non-inverted) bit<br>1 = lcxd4T is gated into lcxg1<br>0 = lcxd4T is not gated into lcxg1<br>bit 6 LCxG1D4N: Gate 1 Data 4 Negated (inverted) bit<br>1 = lcxd4N is gated into lcxg1<br>0 = lcxd4N is not gated into lcxg1<br>bit 5 LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit<br>1 = lcxd3T is gated into lcxg1<br>0 = lcxd3T is not gated into lcxg1<br>0 = lcxd3T is not gated into lcxg1<br>bit 4 LCxG1D3N: Gate 1 Data 3 Negated (inverted) bit<br>1 = lcxd3N is gated into lcxg1<br>0 = lcxd3N is gated into lcxg1<br>0 = lcxd3N is not gated into lcxg1<br>bit 3 LCxG1D2T: Gate 1 Data 2 True (non-inverted) bit<br>1 = lcxd2T is not gated into lcxg1<br>0 = lcxd2T is not gated into lcxg1<br>bit 2 LCxG1D2N: Gate 1 Data 2 Negated (inverted) bit<br>1 = lcxd2N: Gate 1 Data 2 Negated (inverted) bit<br>1 = lcxd2N is not gated into lcxg1<br>0 = lcxd2T is gated into lcxg1<br>0 = lcxd2T is not gated into lcxg1<br>0 = lcxd2N is not gated into lcxg1<br>0 = lcxd1T is gated into lcxg1<br>0 = lcxd1T is gated into lcxg1<br>0 = lcxd1T is not gated into lcxg1<br>0 = lcxd1 | u = Bit is uncha | anged         | x = Bit is unkr  | nown           | -n/n = Value a | at POR and BO    | R/Value at all c | ther Resets |  |  |

| 1 = lcxd4T is gated into lcxg1         0 = lcxd4T is not gated into lcxg1         bit 6       LCxG1D4N: Gate 1 Data 4 Negated (inverted) bit         1 = lcxd4N is gated into lcxg1         0 = lcxd4N is not gated into lcxg1         bit 5       LCxG1D3T: Gate 1 Data 3 True (non-inverted) bit         1 = lcxd3T is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd3N is gated into lcxg1         0 = lcxd2T is gated into lcxg1         0 = lcxd2N is not gated into lcxg1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | '1' = Bit is set | -             | '0' = Bit is cle | ared           |                |                  |                  |             |  |  |