Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2010                       |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 17                                                                         |

| Program Memory Size        | 3.5КВ (2К х 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 20-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf1507-i-so |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE OF CONTENTS

| 1.0   | Device Overview                                | 7   |  |  |  |  |

|-------|------------------------------------------------|-----|--|--|--|--|

| 2.0   | Enhanced Mid-Range CPU                         | 11  |  |  |  |  |

| 3.0   | Memory Organization                            | 13  |  |  |  |  |

| 4.0   | Device Configuration                           | 37  |  |  |  |  |

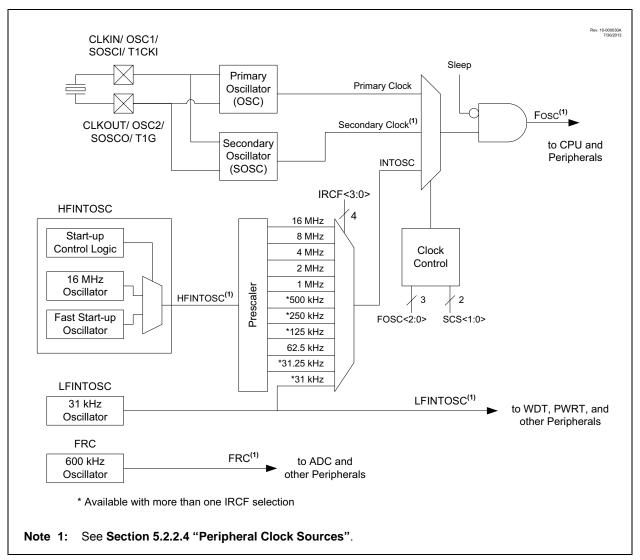

| 5.0   | Oscillator Module                              |     |  |  |  |  |

| 6.0   | Resets                                         | 51  |  |  |  |  |

| 7.0   | Interrupts                                     | 59  |  |  |  |  |

| 8.0   | Power-Down Mode (Sleep)                        | 72  |  |  |  |  |

| 9.0   | Watchdog Timer (WDT)                           | 75  |  |  |  |  |

| 10.0  | Flash Program Memory Control                   | 79  |  |  |  |  |

| 11.0  | I/O Ports                                      | 95  |  |  |  |  |

| 12.0  | Interrupt-On-Change                            | 108 |  |  |  |  |

| 13.0  | Fixed Voltage Reference (FVR)                  | 113 |  |  |  |  |

| 14.0  | Temperature Indicator Module                   | 115 |  |  |  |  |

| 15.0  | Analog-to-Digital Converter (ADC) Module       | 117 |  |  |  |  |

| 16.0  | Timer0 Module                                  | 131 |  |  |  |  |

| 17.0  | Timer1 Module with Gate Control                | 134 |  |  |  |  |

| 18.0  | Timer2 Module                                  | 145 |  |  |  |  |

| 19.0  | Pulse-Width Modulation (PWM) Module            | 148 |  |  |  |  |

| 20.0  | Configurable Logic Cell (CLC)                  | 154 |  |  |  |  |

| 21.0  | Numerically Controlled Oscillator (NCO) Module | 170 |  |  |  |  |

| 22.0  | Complementary Waveform Generator (CWG) Module  | 177 |  |  |  |  |

| 23.0  | In-Circuit Serial Programming™ (ICSP™)         | 189 |  |  |  |  |

| 24.0  | Instruction Set Summary                        | 191 |  |  |  |  |

| 25.0  | Electrical Specifications                      | 205 |  |  |  |  |

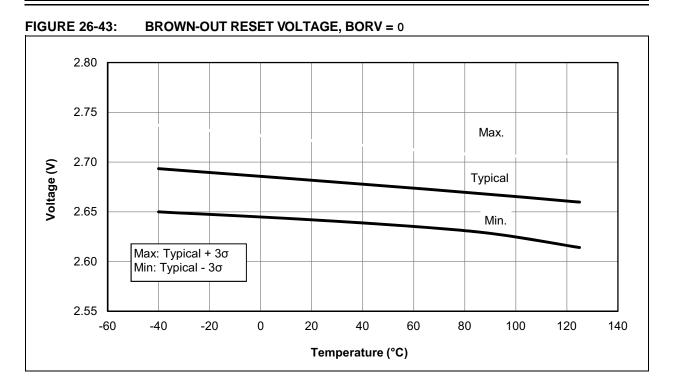

| 26.0  | DC and AC Characteristics Graphs and Charts    | 227 |  |  |  |  |

| 27.0  | Development Support                            | 257 |  |  |  |  |

| 28.0  | Packaging Information                          | 261 |  |  |  |  |

|       | ndix A: Data Sheet Revision History            |     |  |  |  |  |

| The M | Aicrochip Website                              | 275 |  |  |  |  |

| Custo | ustomer Change Notification Service            |     |  |  |  |  |

| Custo | omer Support                                   | 275 |  |  |  |  |

| Produ | oduct Identification System                    |     |  |  |  |  |

| IADLL     |                 |                                                    |                                                    |           |             |             |        | 020)      |           |                      |                                 |

|-----------|-----------------|----------------------------------------------------|----------------------------------------------------|-----------|-------------|-------------|--------|-----------|-----------|----------------------|---------------------------------|

| Address   | Name            | Bit 7                                              | Bit 6                                              | Bit 5     | Bit 4       | Bit 3       | Bit 2  | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on all<br>other<br>Resets |

| Bank 3    | Bank 31         |                                                    |                                                    |           |             |             |        |           |           |                      |                                 |

| F8Ch      | —               | Unimplemen                                         | ted                                                |           |             |             |        |           |           | _                    | —                               |

| —<br>FE3h |                 |                                                    |                                                    |           |             |             |        |           |           |                      |                                 |

| FE4h      | STATUS_<br>SHAD | _                                                  | —                                                  | -         | _           | —           | Z_SHAD | DC_SHAD   | C_SHAD    | xxx                  | uuu                             |

| FE5h      | WREG_<br>SHAD   | Working Reg                                        | gister Shadow                                      |           |             |             |        |           |           | XXXX XXXX            | uuuu uuuu                       |

| FE6h      | BSR_<br>SHAD    | _                                                  | _                                                  | -         | Bank Select | Register Sh | adow   |           |           | x xxxx               | u uuuu                          |

| FE7h      | PCLATH_<br>SHAD | _                                                  | Program Counter Latch High Register Shadow         |           |             |             |        |           | -xxx xxxx | uuuu uuuu            |                                 |

| FE8h      | FSR0L_<br>SHAD  | Indirect Data                                      | Indirect Data Memory Address 0 Low Pointer Shadow  |           |             |             |        |           |           | XXXX XXXX            | uuuu uuuu                       |

| FE9h      | FSR0H_<br>SHAD  | Indirect Data                                      | Indirect Data Memory Address 0 High Pointer Shadow |           |             |             |        |           | xxxx xxxx | uuuu uuuu            |                                 |

| FEAh      | FSR1L_<br>SHAD  | Indirect Data                                      | Indirect Data Memory Address 1 Low Pointer Shadow  |           |             |             |        |           | XXXX XXXX | uuuu uuuu            |                                 |

| FEBh      | FSR1H_<br>SHAD  | Indirect Data Memory Address 1 High Pointer Shadow |                                                    |           |             |             |        | XXXX XXXX | uuuu uuuu |                      |                                 |

| FECh      | —               | Unimplemen                                         | Unimplemented                                      |           |             |             |        |           | _         | _                    |                                 |

| FEDh      | STKPTR          | _                                                  |                                                    | _         | Current Sta | ck Pointer  |        |           |           | 1 1111               | 1 1111                          |

| FEEh      | TOSL            | Top-of-Stack                                       | Top-of-Stack Low byte                              |           |             |             |        |           |           | XXXX XXXX            | uuuu uuuu                       |

| FEFh      | TOSH            | _                                                  | Top-of-Stack                                       | High byte |             |             |        |           |           | -xxx xxxx            | -uuu uuuu                       |

**TABLE 3-5:** SPECIAL FUNCTION REGISTER SUMMARY (CONTINUED)

x = unknown, u = unchanged, g = value depends on condition, - = unimplemented, r = reserved. Shaded locations are unimplemented, read as '0'.

PIC16F1507 only.

Unimplemented, read as '1'. Legend: : Note 1:

2:

## 4.3 Code Protection

Code protection allows the device to be protected from unauthorized access. Internal access to the program memory is unaffected by any code protection setting.

### 4.3.1 PROGRAM MEMORY PROTECTION

The entire program memory space is protected from external reads and writes by the  $\overline{CP}$  bit in Configuration Words. When  $\overline{CP} = 0$ , external reads and writes of program memory are inhibited and a read will return all '0's. The CPU can continue to read program memory, regardless of the protection bit settings. Writing the program memory is dependent upon the write protection setting. See **Section 4.4 "Write Protection"** for more information.

## 4.4 Write Protection

Write protection allows the device to be protected from unintended self-writes. Applications, such as bootloader software, can be protected while allowing other regions of the program memory to be modified.

The WRT<1:0> bits in Configuration Words define the size of the program memory block that is protected.

## 4.5 User ID

Four memory locations (8000h-8003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are readable and writable during normal execution. See **Section 10.4 "User ID, Device ID and Configuration Word Access"** for more information on accessing these memory locations. For more information on checksum calculation, see the "*PIC12(L)F1501/PIC16(L)F150X Memory Programming Specification*" (DS41573).

| R/W-0/0                                                                                                | 0 R/W-0/0                                      | U-0                                            | U-0             | U-0            | U-0              | R/W-0/0          | R/W-0/0     |

|--------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| TMR1GI                                                                                                 | E ADIE                                         | —                                              | _               | _              | —                | TMR2IE           | TMR1IE      |

| bit 7                                                                                                  |                                                |                                                |                 |                |                  |                  | bit 0       |

|                                                                                                        |                                                |                                                |                 |                |                  |                  |             |

| Legend:                                                                                                |                                                |                                                |                 |                |                  |                  |             |

| R = Reada                                                                                              | able bit                                       | W = Writable                                   | bit             | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is u                                                                                           | nchanged                                       | x = Bit is unkn                                | iown            | -n/n = Value   | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is :                                                                                         | set                                            | '0' = Bit is clea                              | ared            |                |                  |                  |             |

|                                                                                                        |                                                |                                                |                 |                |                  |                  |             |

| bit 7                                                                                                  | TMR1GIE: Ti                                    | mer1 Gate Inte                                 | rrupt Enable I  | oit            |                  |                  |             |

|                                                                                                        |                                                | the Timer1 gate                                |                 |                |                  |                  |             |

|                                                                                                        | 0 = Disables                                   | the Timer1 gate                                | e acquisition i | nterrupt       |                  |                  |             |

| bit 6                                                                                                  | -                                              | g-to-Digital Con                               | . ,             | Interrupt Enab | le bit           |                  |             |

|                                                                                                        |                                                | the ADC interru                                |                 |                |                  |                  |             |

|                                                                                                        |                                                | the ADC interru                                | •               |                |                  |                  |             |

| bit 5-2                                                                                                | •                                              | ited: Read as '                                |                 |                |                  |                  |             |

| bit 1                                                                                                  |                                                | TMR2IE: TMR2 to PR2 Match Interrupt Enable bit |                 |                |                  |                  |             |

|                                                                                                        | 1 = Enables the Timer2 to PR2 match interrupt  |                                                |                 |                |                  |                  |             |

| <b>h</b> :+ 0                                                                                          | 0 = Disables the Timer2 to PR2 match interrupt |                                                |                 |                |                  |                  |             |

| bit 0 <b>TMR1IE:</b> Timer1 Overflow Interrupt Enable bit<br>1 = Enables the Timer1 overflow interrupt |                                                |                                                |                 |                |                  |                  |             |

| 0 = Disables the Timer1 overflow interrupt                                                             |                                                |                                                |                 |                |                  |                  |             |

|                                                                                                        |                                                |                                                |                 |                |                  |                  |             |

| Note:                                                                                                  |                                                |                                                | must be         |                |                  |                  |             |

| Note:                                                                                                  | Bit PEIE of the IN set to enable any           | 0                                              |                 |                |                  |                  |             |

|                                                                                                        | set to chable any                              |                                                | up (.           |                |                  |                  |             |

### REGISTER 7-2: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

# 10.2.4 WRITING TO FLASH PROGRAM MEMORY

Program memory is programmed using the following steps:

- 1. Load the address in PMADRH:PMADRL of the row to be programmed.

- 2. Load each write latch with data.

- 3. Initiate a programming operation.

- 4. Repeat steps 1 through 3 until all data is written.

Before writing to program memory, the word(s) to be written must be erased or previously unwritten. Program memory can only be erased one row at a time. No automatic erase occurs upon the initiation of the write.

Program memory can be written one or more words at a time. The maximum number of words written at one time is equal to the number of write latches. See Figure 10-5 (row writes to program memory with 16 write latches) for more details.

The write latches are aligned to the Flash row address boundary defined by the upper 10-bits of PMADRH:PMADRL, (PMADRH<6:0>:PMADRL<7:5>) with the lower five bits of PMADRL, (PMADRL<7:0>) determining the write latch being loaded. Write operations do not cross these boundaries. At the completion of a program memory write operation, the data in the write latches is reset to contain 0x3FFF. The following steps should be completed to load the write latches and program a row of program memory. These steps are divided into two parts. First, each write latch is loaded with data from the PMDATH:PMDATL using the unlock sequence with LWLO = 1. When the last word to be loaded into the write latch is ready, the LWLO bit is cleared and the unlock sequence executed. This initiates the programming operation, writing all the latches into Flash program memory.

| Note: | The special unlock sequence is required<br>to load a write latch with data or initiate a<br>Flash programming operation. If the |

|-------|---------------------------------------------------------------------------------------------------------------------------------|

|       | unlock sequence is interrupted, writing to the latches or program memory will not be initiated.                                 |

- 1. Set the WREN bit of the PMCON1 register.

- 2. Clear the CFGS bit of the PMCON1 register.

- 3. Set the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '1', the write sequence will only load the write latches and will not initiate the write to Flash program memory.

- 4. Load the PMADRH:PMADRL register pair with the address of the location to be written.

- 5. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The write latch is now loaded.

- 7. Increment the PMADRH:PMADRL register pair to point to the next location.

- 8. Repeat steps 5 through 7 until all but the last write latch has been loaded.

- Clear the LWLO bit of the PMCON1 register. When the LWLO bit of the PMCON1 register is '0', the write sequence will initiate the write to Flash program memory.

- 10. Load the PMDATH:PMDATL register pair with the program memory data to be written.

- Execute the unlock sequence (Section 10.2.2 "Flash Memory Unlock Sequence"). The entire program memory latch content is now written to Flash program memory.

- Note: The program memory write latches are reset to the blank state (0x3FFF) at the completion of every write or erase operation. As a result, it is not necessary to load all the program memory write latches. Unloaded latches will remain in the blank state.

An example of the complete write sequence is shown in Example 10-3. The initial address is loaded into the PMADRH:PMADRL register pair; the data is loaded using indirect addressing.

### 11.5 PORTB Registers

#### 11.5.1 DATA REGISTER

PORTB is a 4-bit wide, bidirectional port. The corresponding data direction register is TRISB (Register 11-8). Setting a TRISB bit (= 1) will make the corresponding PORTB pin an input (i.e., disable the output driver). Clearing a TRISB bit (= 0) will make the corresponding PORTB pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 11-1 shows how to initialize an I/O port.

Reading the PORTB register (Register 11-7) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATB).

### 11.5.2 DIRECTION CONTROL

The TRISB register (Register 11-8) controls the PORTB pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISB register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

#### 11.5.3 ANALOG CONTROL

The ANSELB register (Register 11-10) is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSELB bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSELB bits has no effect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

| Note: | The ANSELB bits default to the Analog        |

|-------|----------------------------------------------|

|       | mode after Reset. To use any pins as         |

|       | digital general purpose or peripheral        |

|       | inputs, the corresponding ANSEL bits         |

|       | must be initialized to '0' by user software. |

#### 11.5.4 PORTB FUNCTIONS AND OUTPUT PRIORITIES

Each PORTB pin is multiplexed with other functions. The pins, their combined functions and their output priorities are shown in Table 11-5.

When multiple outputs are enabled, the actual pin control goes to the peripheral with the highest priority.

Analog input functions, such as ADC and comparator inputs, are not shown in the priority lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx registers. Digital output functions may control the pin when it is in Analog mode with the priority shown below in Table 11-5.

### TABLE 11-5: PORTB OUTPUT PRIORITY

| Pin Name | Function Priority <sup>(1)</sup> |

|----------|----------------------------------|

| RB4      | RB4                              |

| RB5      | RB5                              |

| RB6      | RB6                              |

| RB7      | RB7                              |

Note 1: Priority listed from highest to lowest.2: Default pin (see APFCON register).

| Name   | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Register<br>on page |

|--------|-------|--------|-------|-------|-------|-------|-------|--------|---------------------|

| FVRCON | FVREN | FVRRDY | TSEN  | TSRNG |       |       | ADFVF | २<1:0> | 114                 |

Legend: Shaded cells are unused by the temperature indicator module.

### **REGISTER 15-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u          | R/W-x/u | R/W-x/u           | R/W-x/u | R/W-x/u        | R/W-x/u          | R/W-x/u        | R/W-x/u      |

|------------------|---------|-------------------|---------|----------------|------------------|----------------|--------------|

|                  |         |                   | ADRE    | S<9:2>         |                  |                |              |

| bit 7            |         |                   |         |                |                  |                | bit 0        |

|                  |         |                   |         |                |                  |                |              |

| Legend:          |         |                   |         |                |                  |                |              |

| R = Readable     | bit     | W = Writable I    | bit     | U = Unimpler   | nented bit, read | d as '0'       |              |

| u = Bit is unch  | anged   | x = Bit is unkn   | iown    | -n/n = Value a | at POR and BC    | R/Value at all | other Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                |              |

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

#### **REGISTER 15-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | 6<1:0>  | —       | —       | —       | —       | —       | —       |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-6 **ADRES<1:0>**: ADC Result Register bits Lower two bits of 10-bit conversion result

bit 5-0 **Reserved**: Do not use.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                               |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                 |

| Description:     | The contents of register 'f' are decre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', then a<br>NOP is executed instead, making it a<br>2-cycle instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                    |  |  |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                 |  |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                    |  |  |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<6:3> $\rightarrow$ PC<14:11>                                                                                                                         |  |  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                    |  |  |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch. The<br>11-bit immediate value is loaded into<br>PC bits <10:0>. The upper bits of PC<br>are loaded from PCLATH<4:3>. GOTO<br>is a 2-cycle instruction. |  |  |  |  |  |  |  |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                                                                               |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                      |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'.<br>If the result is '1', the next instruction is<br>executed. If the result is '0', a NOP is<br>executed instead, making it a 2-cycle<br>instruction. |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                  |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                     |  |  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                            |  |  |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                 |  |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                            |  |  |  |  |  |  |  |

| Description:     | The contents of the W register are OR'ed with the 8-bit literal 'k'. The result is placed in the W register. |  |  |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] INCF f,d                                                                                                                                                          |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                               |  |  |  |  |  |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                       |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of register 'f' are incre-<br>mented. If 'd' is '0', the result is placed<br>in the W register. If 'd' is '1', the result<br>is placed back in register 'f'. |  |  |  |  |  |

| IORWF            | Inclusive OR W with f                                                                                                                                                      |  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                 |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                         |  |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                   |  |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                          |  |  |  |  |  |  |

| Description:     | Inclusive OR the W register with regis-<br>ter 'f'. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |  |  |  |  |  |  |

# 25.0 ELECTRICAL SPECIFICATIONS

# 25.1 Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias40°C to +125°C<br>Storage temperature65°C to +150°C |  |

|-----------------------------------------------------------------------------------|--|

|                                                                                   |  |

| Voltage on pins with respect to Vss                                               |  |

| on Vod pin                                                                        |  |

| PIC16F15070.3V to +6.5V                                                           |  |

| PIC16LF15070.3V to +4.0V                                                          |  |

| on MCLR pin0.3V to +9.0V                                                          |  |

| on all other pins0.3V to (VDD + 0.3V)                                             |  |

| Maximum current                                                                   |  |

| on Vss pin <sup>(1)</sup>                                                         |  |

| $-40^\circ C \leq T_A \leq +85^\circ C$                                           |  |

| +85°C $\leq$ Ta $\leq$ +125°C $\ldots$ 85 mA                                      |  |

| on VDD pin <sup>(1)</sup>                                                         |  |

| $-40^\circ C \leq T_A \leq +85^\circ C$                                           |  |

| +85°C $\leq$ Ta $\leq$ +125°C $\ldots$ 85 mA                                      |  |

| Sunk by any standard I/O pin 50 mA                                                |  |

| Sourced by any standard I/O pin 50 mA                                             |  |

| Clamp current, Ικ (VPIN < 0 or VPIN > VDD)                                        |  |

| Total power dissipation <sup>(2)</sup>                                            |  |

**Note 1:** Maximum current rating requires even load distribution across I/O pins. Maximum current rating may be limited by the device package power dissipation characterizations, see Table 25-6 to calculate device specifications.

2: Power dissipation is calculated as follows: PDIS = VDD x {IDD  $-\sum$  IOH} +  $\sum$  {(VDD - VOH) x IOH} +  $\sum$ (VOI x IOL).

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

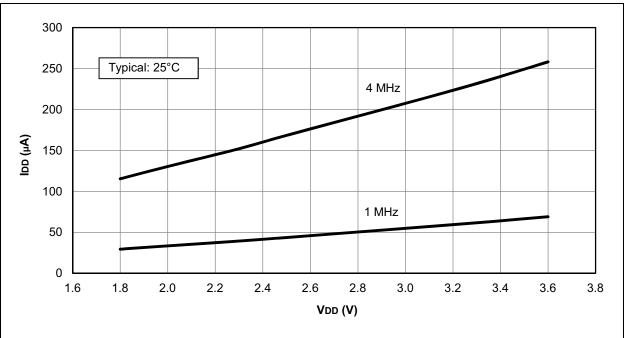

# TABLE 25-2: SUPPLY CURRENT (IDD)<sup>(1,2)</sup>

| PIC16LF | 1507            | Stand    | Standard Operating Conditions (unless otherwise stated) |      |                                           |     |                                            |  |  |  |

|---------|-----------------|----------|---------------------------------------------------------|------|-------------------------------------------|-----|--------------------------------------------|--|--|--|

| PIC16F1 | 507             |          |                                                         |      |                                           |     |                                            |  |  |  |

| Param.  | Device          | Min.     | Тур†                                                    | Max. | Units                                     |     | Conditions                                 |  |  |  |

| No.     | Characteristics |          | <i>.</i>                                                |      |                                           | Vdd | Note                                       |  |  |  |

| D013    |                 |          | 30                                                      | 65   | μA                                        | 1.8 | Fosc = 1 MHz,                              |  |  |  |

|         |                 | —        | 55                                                      | 100  | μA                                        | 3.0 | External Clock (ECM),<br>Medium-Power mode |  |  |  |

| D013    |                 |          | 65                                                      | 110  | μA                                        | 2.3 | Fosc = 1 MHz,                              |  |  |  |

|         |                 |          | 85                                                      | 140  | μA                                        | 3.0 | External Clock (ECM),<br>Medium-Power mode |  |  |  |

|         |                 |          | 115                                                     | 190  | μA                                        | 5.0 | Medium-Power mode                          |  |  |  |

| D014    |                 |          | 115                                                     | 190  | μA                                        | 1.8 | Fosc = 4 MHz,                              |  |  |  |

|         |                 | _        | 210                                                     | 310  | μA                                        | 3.0 | External Clock (ECM),<br>Medium-Power mode |  |  |  |

| D014    |                 | —        | 180                                                     | 270  | μA                                        | 2.3 | Fosc = 4 MHz,                              |  |  |  |

|         |                 | _        | 240                                                     | 365  | μA                                        | 3.0 | External Clock (ECM),                      |  |  |  |

|         |                 |          | 295                                                     | 460  | μA                                        | 5.0 | Medium-Power mode                          |  |  |  |

| D015    |                 | —        | 3.2                                                     | 12   | μA                                        | 1.8 | Fosc = 31 kHz,                             |  |  |  |

|         |                 | — 5.4 20 | μA                                                      | 3.0  | LFINTOSC,<br>-40°C $\leq$ TA $\leq$ +85°C |     |                                            |  |  |  |

| D015    |                 | —        | 13                                                      | 28   | μA                                        | 2.3 | Fosc = 31 kHz,                             |  |  |  |

|         |                 |          | 15                                                      | 30   | μA                                        | 3.0 |                                            |  |  |  |

|         |                 |          | 17                                                      | 36   | μA                                        | 5.0 | $-40^{\circ}C \le TA \le +85^{\circ}C$     |  |  |  |

| D016    |                 | —        | 215                                                     | 360  | μA                                        | 1.8 | Fosc = 500 kHz,                            |  |  |  |

|         |                 | —        | 275                                                     | 480  | μA                                        | 3.0 | HFINTOSC                                   |  |  |  |

| D016    |                 |          | 270                                                     | 450  | μA                                        | 2.3 | Fosc = 500 kHz,                            |  |  |  |

|         |                 | _        | 300                                                     | 500  | μA                                        | 3.0 | HFINTOSC                                   |  |  |  |

|         |                 | _        | 350                                                     | 620  | μA                                        | 5.0 |                                            |  |  |  |

| D017*   |                 |          | 410                                                     | 660  | μA                                        | 1.8 | Fosc = 8 MHz,                              |  |  |  |

|         |                 |          | 630                                                     | 970  | μA                                        | 3.0 | HFINTOSC                                   |  |  |  |

| D017*   |                 | _        | 530                                                     | 750  | μA                                        | 2.3 | Fosc = 8 MHz,                              |  |  |  |

|         |                 | _        | 660                                                     | 1100 | μA                                        | 3.0 | HFINTOSC                                   |  |  |  |

|         |                 | _        | 730                                                     | 1200 | μA                                        | 5.0 |                                            |  |  |  |

| D018    |                 | _        | 600                                                     | 940  | μA                                        | 1.8 | Fosc = 16 MHz,                             |  |  |  |

|         |                 |          | 970                                                     | 1400 | μA                                        | 3.0 | HFINTOSC                                   |  |  |  |

| D018    |                 | —        | 780                                                     | 1200 | μA                                        | 2.3 | Fosc = 16 MHz,                             |  |  |  |

|         |                 | —        | 1000                                                    | 1550 | μA                                        | 3.0 | HFINTOSC                                   |  |  |  |

|         |                 |          | 1090                                                    | 1700 | μA                                        | 5.0 |                                            |  |  |  |

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance t only and are not tested.

Note 1: The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to Vss; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

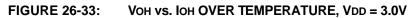

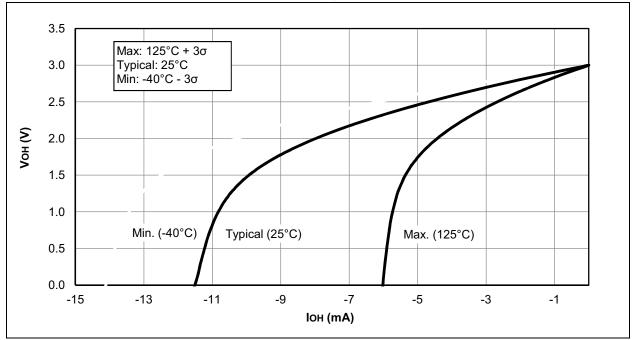

#### TABLE 25-4: I/O PORTS

| Standard O | perating Condit | ions (unless oth | erwise stated) |

|------------|-----------------|------------------|----------------|

| Param.<br>No. | Sym. | Characteristic                       | Min.            | Тур†     | Max.     | Units | Conditions                                                                 |

|---------------|------|--------------------------------------|-----------------|----------|----------|-------|----------------------------------------------------------------------------|

|               | VIL  | Input Low Voltage                    | · · ·           |          |          |       | ·                                                                          |

|               |      | I/O PORT:                            |                 |          |          |       |                                                                            |

| D030          |      | with TTL buffer                      | —               | _        | 0.8      | V     | $4.5V \le V\text{DD} \le 5.5V$                                             |

| D030A         |      |                                      | —               | _        | 0.15 VDD | V     | $1.8V \le V\text{DD} \le 4.5V$                                             |

| D032          |      | MCLR                                 | —               | _        | 0.2 Vdd  | V     |                                                                            |

|               | Vih  | Input High Voltage                   |                 |          |          |       |                                                                            |

|               |      | I/O PORT:                            |                 |          |          |       |                                                                            |

| D040          |      | with TTL buffer                      | 2.0             |          | _        | V     | $4.5V \le V\text{DD} \le 5.5V$                                             |

| D040A         |      |                                      | 0.25 VDD +      |          |          | V     | $1.8V \leq V\text{DD} \leq 4.5V$                                           |

| D0.40         |      | MOLE                                 | 0.8             |          |          |       |                                                                            |

| D042          |      | MCLR                                 | 0.8 VDD         |          | —        | V     |                                                                            |

|               | lı∟  | Input Leakage Current <sup>(1)</sup> |                 |          | 1        |       |                                                                            |

| D060          |      | I/O Ports                            | —               | ± 5      | ± 125    | nA    | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance, 85°C                 |

|               |      |                                      | —               | ± 5      | ± 1000   | nA    | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance, 125°C                |

| D061          |      | MCLR <sup>(2)</sup>                  |                 | ± 50     | ± 200    | nA    | Vss $\leq$ VPIN $\leq$ VDD,                                                |

| DUUT          |      | MOLK                                 | _               | ± 50     | ± 200    | 114   | Pin at high-impedance, 85°C                                                |

|               | IPUR | Weak Pull-up Current                 |                 |          |          |       |                                                                            |

| D070*         |      |                                      | 25              | 100      | 200      | μΑ    | VDD = 3.3V, VPIN = VSS                                                     |

|               |      |                                      | 25              | 140      | 300      | μA    | VDD = 5.0V, VPIN = VSS                                                     |

|               | Vol  | Output Low Voltage                   |                 |          | •        |       |                                                                            |

| D080          |      | I/O Ports                            | _               | _        | 0.6      | V     | IOL = 8 mA, VDD = 5V<br>IOL = 6 mA, VDD = 3.3V<br>IOL = 1.8 mA, VDD = 1.8V |

|               | Voн  | Output High Voltage                  |                 |          |          |       |                                                                            |

| D090          |      | I/O Ports                            | Vdd - 0.7       | _        | _        | V     | ІОН = 3.5 mA, VDD = 5V<br>ІОН = 3 mA, VDD = 3.3V<br>ІОН = 1 mA, VDD = 1.8V |

|               |      | Capacitive Loading Specifi           | cations on Outr | out Dinc |          |       | 10n - 1 IIIA, VUU - 1.0V                                                   |

| D101A*        | CIO  | All I/O pins                         |                 |          | 50       | pF    |                                                                            |

| DIVIA         | 00   |                                      | _               |          | 50       | μг    |                                                                            |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Negative current is defined as current sourced by the pin.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

### TABLE 25-8: OSCILLATOR PARAMETERS

| Standar       | Standard Operating Conditions (unless otherwise stated) |                                                          |                    |      |      |      |       |                                           |

|---------------|---------------------------------------------------------|----------------------------------------------------------|--------------------|------|------|------|-------|-------------------------------------------|

| Param.<br>No. | Sym.                                                    | Characteristic                                           | Freq.<br>Tolerance | Min. | Тур† | Max. | Units | Conditions                                |

| OS08          | HFosc                                                   | Internal Calibrated HFINTOSC<br>Frequency <sup>(1)</sup> | ±2%                |      | 16.0 |      | MHz   | VDD = 3.0V, TA = 25°C,<br>(Note 2)        |

| OS09          | LFosc                                                   | Internal LFINTOSC Frequency                              | —                  | _    | 31   | _    | kHz   | (Note 3)                                  |

| OS10*         | TIOSC ST                                                | HFINTOSC<br>Wake-up from Sleep Start-up Time             | -                  | _    | 5    | 15   | μS    |                                           |

| OS10A*        | TLFOSC ST                                               | LFINTOSC<br>Wake-up from Sleep Start-up Time             | —                  |      | 0.5  |      | ms    | $-40^{\circ}C \leq TA \leq +125^{\circ}C$ |

These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

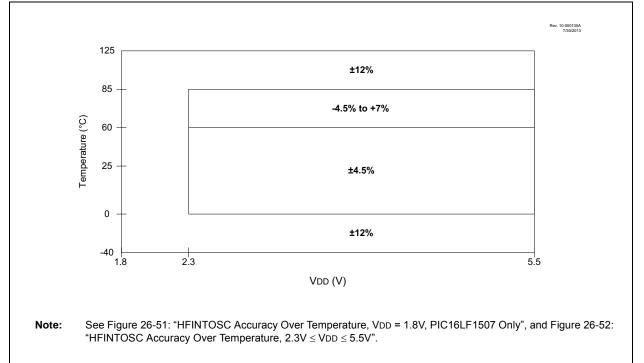

2: See Figure 25-6: "HFINTOSC Frequency Accuracy over Device VDD and Temperature", Figure 26-51: "HFINTOSC Accuracy Over Temperature, VDD = 1.8V, PIC16LF1507 Only", and Figure 26-52: "HFINTOSC Accuracy Over Temperature, 2.3V ≤ VDD ≤ 5.5V".

3: See Figure 26-49: "LFINTOSC Frequency over VDD and Temperature, PIC16LF1507 Only", and Figure 26-50: "LFINTOSC Frequency over VDD and Temperature, PIC16F1507".

#### FIGURE 25-6: HFINTOSC FREQUENCY ACCURACY OVER VDD AND TEMPERATURE

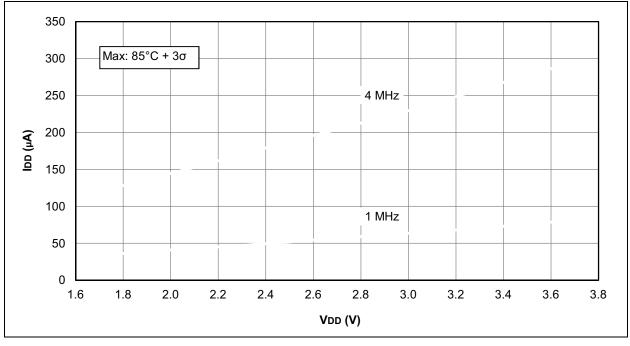

FIGURE 26-6: IDD MAXIMUM, EXTERNAL CLOCK (ECM), MEDIUM POWER MODE, PIC16LF1507 ONLY

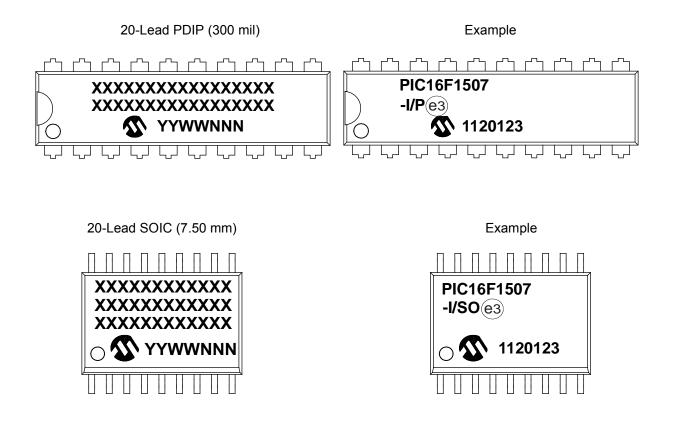

# 28.0 PACKAGING INFORMATION

## 28.1 Package Marking Information

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator ((e3))<br>can be found on the outer packaging for this package. |

|--------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | be carried                               | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>s for customer-specific information.                                                                                                                                                                                                           |

\* Standard PICmicro<sup>®</sup> device marking consists of Microchip part number, year code, week code and traceability code. For PICmicro device marking beyond this, certain price adders apply. Please check with your Microchip Sales Office. For QTP devices, any special marking adders are included in QTP price.

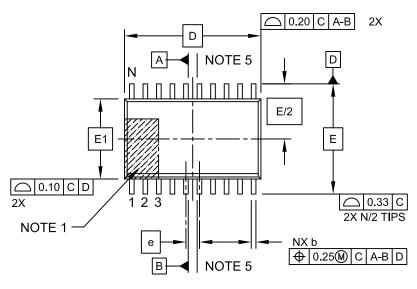

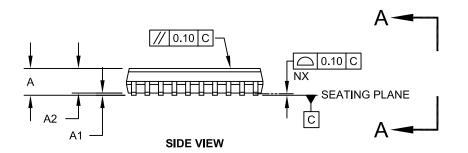

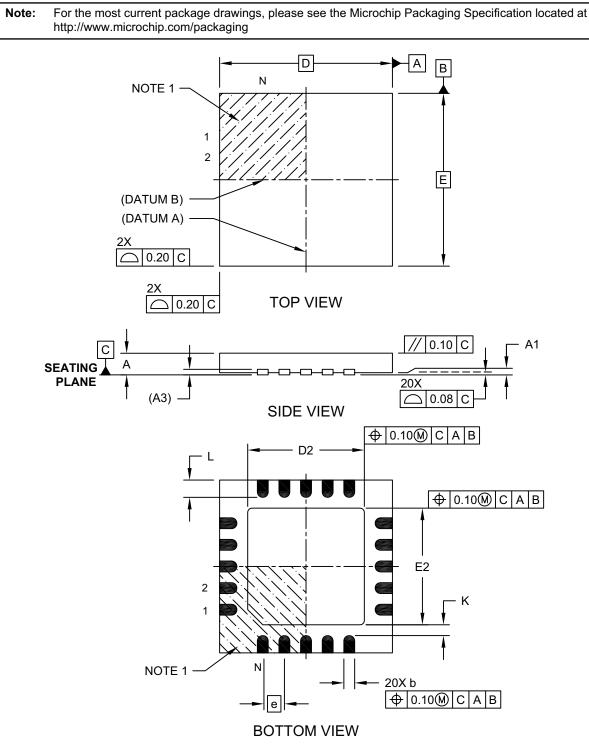

## 20-Lead Plastic Small Outline (SO) - Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-094C Sheet 1 of 2

Microchip Technology Drawing C04-255A Sheet 1 of 2