# E·XFL

Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | AVR                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 16MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 23                                                                     |

| Program Memory Size        | 8KB (4K x 16)                                                          |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 32-VQFN (5x5)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega8-16mc |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending interrupts, as shown in the following example.

Assembly Code Example

| <b>sei</b> ; set global interrupt enable                     |

|--------------------------------------------------------------|

| <b>sleep</b> ; enter sleep, waiting for interrupt            |

| ; note: will enter sleep before any pending                  |

| ; interrupt(s)                                               |

| C Code Example                                               |

| _SEI(); /* set global interrupt enable */                    |

| _SLEEP(); /* enter sleep, waiting for interrupt */           |

| /* note: will enter sleep before any pending interrupt(s) */ |

## **Interrupt Response Time**

The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. After four clock cycles, the Program Vector address for the actual interrupt handling routine is executed. During this 4-clock cycle period, the Program Counter is pushed onto the Stack. The Vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by four clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes four clock cycles. During these four clock cycles, the Program Counter (2 bytes) is popped back from the Stack, the Stack Pointer is incremented by 2, and the I-bit in SREG is set.

| /hen the SM20 bits are written to 000, the SLEEP instruction makes the MCU enter<br>lle mode, stopping the CPU but allowing SPI, USART, Analog Comparator, ADC, Two-<br>ire Serial Interface, Timer/Counters, Watchdog, and the interrupt system to continue<br>perating. This sleep mode basically halts clk <sub>CPU</sub> and clk <sub>FLASH</sub> , while allowing the other<br>ocks to run.                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| lle mode enables the MCU to wake up from external triggered interrupts as well as ternal ones like the Timer Overflow and USART Transmit Complete interrupts. If ake-up from the Analog Comparator interrupt is not required, the Analog Comparator an be powered down by setting the ACD bit in the Analog Comparator Control and Stans Register – ACSR. This will reduce power consumption in Idle mode. If the ADC is nabled, a conversion starts automatically when this mode is entered.                                                                                                                                                                                                       |

| /hen the SM20 bits are written to 001, the SLEEP instruction makes the MCU enter DC Noise Reduction mode, stopping the CPU but allowing the ADC, the external terrupts, the Two-wire Serial Interface address watch, Timer/Counter2 and the /atchdog to continue operating (if enabled). This sleep mode basically halts $clk_{I/O}$ , $k_{CPU}$ , and $clk_{FLASH}$ , while allowing the other clocks to run.                                                                                                                                                                                                                                                                                      |

| his improves the noise environment for the ADC, enabling higher resolution measure-<br>ents. If the ADC is enabled, a conversion starts automatically when this mode is<br>intered. Apart form the ADC Conversion Complete interrupt, only an External Reset, a<br>/atchdog Reset, a Brown-out Reset, a Two-wire Serial Interface address match inter-<br>ipt, a Timer/Counter2 interrupt, an SPM/EEPROM ready interrupt, or an external level<br>terrupt on INT0 or INT1, can wake up the MCU from ADC Noise Reduction mode.                                                                                                                                                                       |

| /hen the SM20 bits are written to 010, the SLEEP instruction makes the MCU enter<br>ower-down mode. In this mode, the External Oscillator is stopped, while the external<br>terrupts, the Two-wire Serial Interface address watch, and the Watchdog continue<br>perating (if enabled). Only an External Reset, a Watchdog Reset, a Brown-out Reset, a<br>wo-wire Serial Interface address match interrupt, or an external level interrupt on INTO<br>r INT1, can wake up the MCU. This sleep mode basically halts all generated clocks,<br>lowing operation of asynchronous modules only.                                                                                                           |

| ote that if a level triggered interrupt is used for wake-up from Power-down mode, the<br>nanged level must be held for some time to wake up the MCU. Refer to "External Inter-<br>upts" on page 64 for details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| /hen waking up from Power-down mode, there is a delay from the wake-up condition<br>ccurs until the wake-up becomes effective. This allows the clock to restart and become<br>able after having been stopped. The wake-up period is defined by the same CKSEL<br>uses that define the Reset Time-out period, as described in "Clock Sources" on page<br>4.                                                                                                                                                                                                                                                                                                                                          |

| /hen the SM20 bits are written to 011, the SLEEP instruction makes the MCU enter<br>ower-save mode. This mode is identical to Power-down, with one exception:<br>If Timer/Counter2 is clocked asynchronously, i.e. the AS2 bit in ASSR is set,<br>Timer/Counter2 will run during sleep. The device can wake up from either Timer<br>Overflow or Output Compare event from Timer/Counter2 if the corresponding<br>Timer/Counter2 interrupt enable bits are set in TIMSK, and the global interrupt<br>enable bit in SREG is set.<br>the asynchronous timer is NOT clocked asynchronously, Power-down mode is recom-<br>nended instead of Power-save mode because the contents of the registers in the |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# I/O Ports

# Introduction

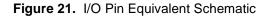

All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions. The same applies when changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input). Each output buffer has symmetrical drive characteristics with both high sink and source capability. The pin driver is strong enough to drive LED displays directly. All port pins have individually selectable pull-up resistors with a supply-voltage invariant resistance. All I/O pins have protection diodes to both  $V_{CC}$  and Ground as indicated in Figure 21. Refer to "Electrical Characteristics" on page 237 for a complete list of parameters.

All registers and bit references in this section are written in general form. A lower case "x" represents the numbering letter for the port, and a lower case "n" represents the bit number. However, when using the register or bit defines in a program, the precise form must be used (i.e., PORTB3 for bit 3 in Port B, here documented generally as PORTxn). The physical I/O Registers and bit locations are listed in "Register Description for I/O Ports" on page 63.

Three I/O memory address locations are allocated for each port, one each for the Data Register – PORTx, Data Direction Register – DDRx, and the Port Input Pins – PINx. The Port Input Pins I/O location is read only, while the Data Register and the Data Direction Register are read/write. In addition, the Pull-up Disable – PUD bit in SFIOR disables the pull-up function for all pins in all ports when set.

Using the I/O port as General Digital I/O is described in "Ports as General Digital I/O" on page 50. Most port pins are multiplexed with alternate functions for the peripheral features on the device. How each alternate function interferes with the port pin is described in "Alternate Port Functions" on page 54. Refer to the individual module sections for a full description of the alternate functions.

Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O.

# Timer/Counter Timing Diagrams

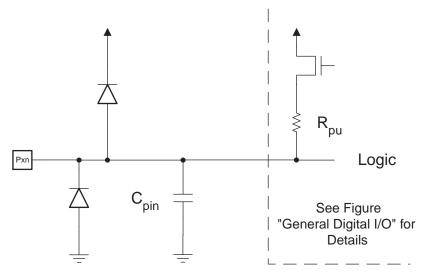

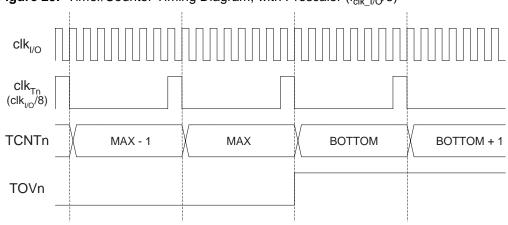

The Timer/Counter is a synchronous design and the timer clock  $(clk_{T0})$  is therefore shown as a clock enable signal in the following figures. The figures include information on when Interrupt Flags are set. Figure 28 contains timing data for basic Timer/Counter operation. The figure shows the count sequence close to the MAX value.

Figure 28. Timer/Counter Timing Diagram, No Prescaling

Figure 29 shows the same timing data, but with the prescaler enabled.

Figure 29. Timer/Counter Timing Diagram, with Prescaler ( $f_{clk \ I/O}/8$ )

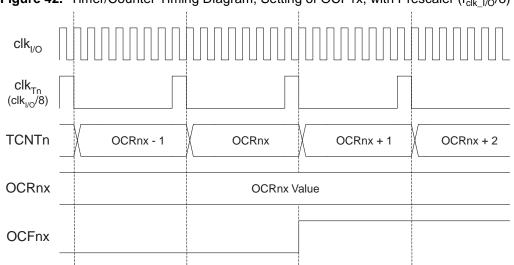

Figure 42. Timer/Counter Timing Diagram, Setting of OCF1x, with Prescaler (f<sub>clk I/O</sub>/8)

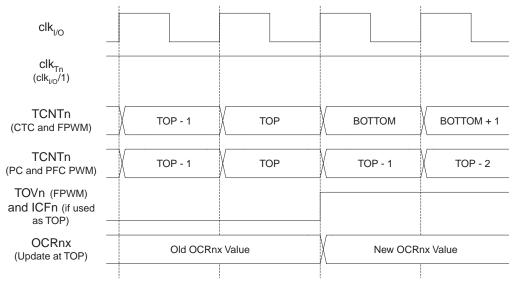

Figure 43 shows the count sequence close to TOP in various modes. When using phase and frequency correct PWM mode the OCR1x Register is updated at BOTTOM. The timing diagrams will be the same, but TOP should be replaced by BOTTOM, TOP-1 by BOTTOM+1 and so on. The same renaming applies for modes that set the TOV1 Flag at BOTTOM.

Figure 43. Timer/Counter Timing Diagram, no Prescaling

Figure 44 shows the same timing data, but with the prescaler enabled.

Table 37 shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to the fast PWM mode.

Table 37. Compare Output Mode, Fast PWM<sup>(1)</sup>

| COM1A1/<br>COM1B1 | COM1A0/<br>COM1B0 | Description                                                                                                                                                        |

|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | 0                 | Normal port operation, OC1A/OC1B disconnected.                                                                                                                     |

| 0                 | 1                 | WGM13:0 = 15: Toggle OC1A on Compare Match, OC1B disconnected (normal port operation). For all other WGM1 settings, normal port operation, OC1A/OC1B disconnected. |

| 1                 | 0                 | Clear OC1A/OC1B on Compare Match, set OC1A/OC1B at TOP                                                                                                             |

| 1                 | 1                 | Set OC1A/OC1B on Compare Match, clear OC1A/OC1B at TOP                                                                                                             |

A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. In this case the Compare Match is ignored, but the set or clear is done at TOP. See "Fast PWM Mode" on page 87. for more details.

Table 38 shows the COM1x1:0 bit functionality when the WGM13:0 bits are set to the phase correct or the phase and frequency correct, PWM mode.

**Table 38.** Compare Output Mode, Phase Correct and Phase and Frequency Correct

PWM<sup>(1)</sup>

| COM1A1/<br>COM1B1 | COM1A0/<br>COM1B0 | Description                                                                                                                                                             |

|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                 | 0                 | Normal port operation, OC1A/OC1B disconnected.                                                                                                                          |

| 0                 | 1                 | WGM13:0 = 9 or 14: Toggle OC1A on Compare Match, OC1B disconnected (normal port operation). For all other WGM1 settings, normal port operation, OC1A/OC1B disconnected. |

| 1                 | 0                 | Clear OC1A/OC1B on Compare Match when up-counting. Set OC1A/OC1B on Compare Match when downcounting.                                                                    |

| 1                 | 1                 | Set OC1A/OC1B on Compare Match when up-counting. Clear OC1A/OC1B on Compare Match when downcounting.                                                                    |

Note: 1. A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. See "Phase Correct PWM Mode" on page 89. for more details.

### • Bit 3 – FOC1A: Force Output Compare for channel A

### • Bit 2 – FOC1B: Force Output Compare for channel B

The FOC1A/FOC1B bits are only active when the WGM13:0 bits specifies a non-PWM mode. However, for ensuring compatibility with future devices, these bits must be set to zero when TCCR1A is written when operating in a PWM mode. When writing a logical one to the FOC1A/FOC1B bit, an immediate Compare Match is forced on the waveform generation unit. The OC1A/OC1B output is changed according to its COM1x1:0 bits setting. Note that the FOC1A/FOC1B bits are implemented as strobes. Therefore it is the value present in the COM1x1:0 bits that determine the effect of the forced compare.

A FOC1A/FOC1B strobe will not generate any interrupt nor will it clear the timer in Clear Timer on Compare Match (CTC) mode using OCR1A as TOP.

The FOC1A/FOC1B bits are always read as zero.

# • Bit 1:0 – WGM11:0: Waveform Generation Mode

Combined with the WGM13:2 bits found in the TCCR1B Register, these bits control the counting sequence of the counter, the source for maximum (TOP) counter value, and

what type of waveform generation to be used, see Table 39. Modes of operation supported by the Timer/Counter unit are: Normal mode (counter), Clear Timer on Compare Match (CTC) mode, and three types of Pulse Width Modulation (PWM) modes. (See "Modes of Operation" on page 86.)

Table 39. Waveform Generation Mode Bit Description

| Mode | WGM13 | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of Operation <sup>(1)</sup> | ТОР    | Update of<br>OCR1x | TOV1 Flag<br>Set on |

|------|-------|-----------------|------------------|------------------|------------------------------------------------|--------|--------------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                                         | 0xFFFF | Immediate          | MAX                 |

| 1    | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit                      | 0x00FF | TOP                | BOTTOM              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit                      | 0x01FF | TOP                | BOTTOM              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit                     | 0x03FF | TOP                | BOTTOM              |

| 4    | 0     | 1               | 0                | 0                | СТС                                            | OCR1A  | Immediate          | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                                | 0x00FF | TOP                | ТОР                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                                | 0x01FF | TOP                | ТОР                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                               | 0x03FF | ТОР                | ТОР                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency<br>Correct            | ICR1   | BOTTOM             | BOTTOM              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency<br>Correct            | OCR1A  | BOTTOM             | BOTTOM              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct                             | ICR1   | TOP                | BOTTOM              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct                             | OCR1A  | TOP                | BOTTOM              |

| 12   | 1     | 1               | 0                | 0                | СТС                                            | ICR1   | Immediate          | MAX                 |

| 13   | 1     | 1               | 0                | 1                | (Reserved)                                     | -      | -                  | -                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                                       | ICR1   | TOP                | ТОР                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                                       | OCR1A  | ТОР                | TOP                 |

Note: 1. The CTC1 and PWM11:0 bit definition names are obsolete. Use the WGM12:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

| Registers                      | The Timer/Counter (TCNT2) and Output Compare Register (OCR2) are 8-bit registers.<br>Interrupt request (shorten as Int.Req.) signals are all visible in the Timer Interrupt Flag<br>Register (TIFR). All interrupts are individually masked with the Timer Interrupt Mask<br>Register (TIMSK). TIFR and TIMSK are not shown in the figure since these registers are<br>shared by other timer units.                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                | The Timer/Counter can be clocked internally, via the prescaler, or asynchron<br>clocked from the TOSC1/2 pins, as detailed later in this section. The asynchro<br>operation is controlled by the Asynchronous Status Register (ASSR). The Clock<br>logic block controls which clock source the Timer/Counter uses to increment (or<br>ment) its value. The Timer/Counter is inactive when no clock source is selecte<br>output from the clock select logic is referred to as the timer clock (clk <sub>T2</sub> ). |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                | The double buffered Output Compare Register (OCR2) is compared<br>Timer/Counter value at all times. The result of the compare can be used by<br>form generator to generate a PWM or variable frequency output on the Output<br>Pin (OC2). For details, see "Output Compare Unit" on page 105. The Compa<br>event will also set the Compare Flag (OCF2) which can be used to generate a<br>Compare interrupt request.                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Definitions                    | hitions Many register and bit references in this document are written in general case "n" replaces the Timer/Counter number, in this case 2. However, w register or bit defines in a program, the precise form must be used (i. accessing Timer/Counter2 counter value and so on).                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                | The definitio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ns in Table 41 are also used extensively throughout the document.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                                | Table 41. D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Pefinitions                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                                | BOTTOM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | The counter reaches the BOTTOM when it becomes zero (0x00).                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                                | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The counter reaches its MAXimum when it becomes 0xFF (decimal 255).                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                | ТОР                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR2 Register. The assignment is dependent on the mode of operation.                                                                                                                                               |  |  |  |  |  |

| Timer/Counter Clock<br>Sources | nous clock s<br>When the As<br>from the Tir<br>asynchronou                                                                                                                                                                                                                                                                                                                                                                                                                                                         | counter can be clocked by an internal synchronous or an external asynchro-<br>source. The clock source $clk_{T2}$ is by default equal to the MCU clock, $clk_{I/O}$ .<br>S2 bit in the ASSR Register is written to logic one, the clock source is taken<br>ner/Counter Oscillator connected to TOSC1 and TOSC2. For details on<br>us operation, see "Asynchronous Status Register – ASSR" on page 117. For |  |  |  |  |  |

details on clock sources and prescaler, see "Timer/Counter Prescaler" on page 121.

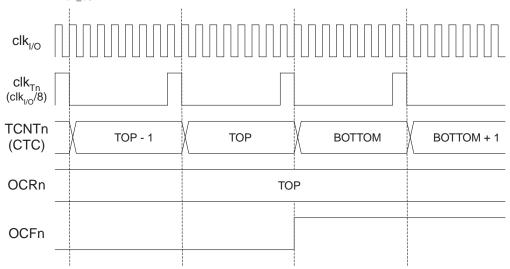

Figure 54. Timer/Counter Timing Diagram, Setting of OCF2, with Prescaler ( $f_{clk_l/O}/8$ )

Figure 55 shows the setting of OCF2 and the clearing of TCNT2 in CTC mode.

Figure 55. Timer/Counter Timing Diagram, Clear Timer on Compare Match Mode, with Prescaler (f\_{clk}  $_{\rm I/O}\!/8)$

| f <sub>osc</sub> = 8.0000 MHz |          |         |        |         | f <sub>osc</sub> = 11.0592 MHz |         |          |         | f <sub>osc</sub> = 14.7456 MHz |         |          |         |  |

|-------------------------------|----------|---------|--------|---------|--------------------------------|---------|----------|---------|--------------------------------|---------|----------|---------|--|

| Baud<br>Rate                  | U2X      | U2X = 0 |        | U2X = 1 |                                | U2X = 0 |          | U2X = 1 |                                | U2X = 0 |          | U2X = 1 |  |

| (bps)                         | UBRR     | Error   | UBRR   | Error   | UBRR                           | Error   | UBRR     | Error   | UBRR                           | Error   | UBRR     | Error   |  |

| 2400                          | 207      | 0.2%    | 416    | -0.1%   | 287                            | 0.0%    | 575      | 0.0%    | 383                            | 0.0%    | 767      | 0.0%    |  |

| 4800                          | 103      | 0.2%    | 207    | 0.2%    | 143                            | 0.0%    | 287      | 0.0%    | 191                            | 0.0%    | 383      | 0.0%    |  |

| 9600                          | 51       | 0.2%    | 103    | 0.2%    | 71                             | 0.0%    | 143      | 0.0%    | 95                             | 0.0%    | 191      | 0.0%    |  |

| 14.4k                         | 34       | -0.8%   | 68     | 0.6%    | 47                             | 0.0%    | 95       | 0.0%    | 63                             | 0.0%    | 127      | 0.0%    |  |

| 19.2k                         | 25       | 0.2%    | 51     | 0.2%    | 35                             | 0.0%    | 71       | 0.0%    | 47                             | 0.0%    | 95       | 0.0%    |  |

| 28.8k                         | 16       | 2.1%    | 34     | -0.8%   | 23                             | 0.0%    | 47       | 0.0%    | 31                             | 0.0%    | 63       | 0.0%    |  |

| 38.4k                         | 12       | 0.2%    | 25     | 0.2%    | 17                             | 0.0%    | 35       | 0.0%    | 23                             | 0.0%    | 47       | 0.0%    |  |

| 57.6k                         | 8        | -3.5%   | 16     | 2.1%    | 11                             | 0.0%    | 23       | 0.0%    | 15                             | 0.0%    | 31       | 0.0%    |  |

| 76.8k                         | 6        | -7.0%   | 12     | 0.2%    | 8                              | 0.0%    | 17       | 0.0%    | 11                             | 0.0%    | 23       | 0.0%    |  |

| 115.2k                        | 3        | 8.5%    | 8      | -3.5%   | 5                              | 0.0%    | 11       | 0.0%    | 7                              | 0.0%    | 15       | 0.0%    |  |

| 230.4k                        | 1        | 8.5%    | 3      | 8.5%    | 2                              | 0.0%    | 5        | 0.0%    | 3                              | 0.0%    | 7        | 0.0%    |  |

| 250k                          | 1        | 0.0%    | 3      | 0.0%    | 2                              | -7.8%   | 5        | -7.8%   | 3                              | -7.8%   | 6        | 5.3%    |  |

| 0.5M                          | 0        | 0.0%    | 1      | 0.0%    | -                              | -       | 2        | -7.8%   | 1                              | -7.8%   | 3        | -7.8%   |  |

| 1M                            | -        | _       | 0      | 0.0%    | -                              | -       | _        | -       | 0                              | -7.8%   | 1        | -7.8%   |  |

| Max <sup>(1)</sup>            | 0.5 Mbps | 5       | 1 Mbps |         | 691.2 kb                       | ps      | 1.3824 N | lbps    | 921.6 kb                       | ps      | 1.8432 N | lbps    |  |

| Table 62. | Examples of | UBRR Settings | for Commonly | Used Oscillator | Frequencies | (Continued) |

|-----------|-------------|---------------|--------------|-----------------|-------------|-------------|

|           |             |               |              |                 |             |             |

1. UBRR = 0, Error = 0.0%

# AMEL

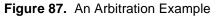

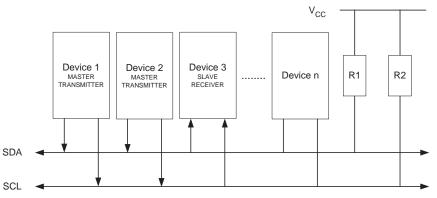

# Multi-master Bus Systems, Arbitration and Synchronization

The TWI protocol allows bus systems with several masters. Special concerns have been taken in order to ensure that transmissions will proceed as normal, even if two or more masters initiate a transmission at the same time. Two problems arise in multi-master systems:

- An algorithm must be implemented allowing only one of the masters to complete the transmission. All other masters should cease transmission when they discover that they have lost the selection process. This selection process is called arbitration. When a contending master discovers that it has lost the arbitration process, it should immediately switch to Slave mode to check whether it is being addressed by the winning master. The fact that multiple masters have started transmission at the same time should not be detectable to the slaves, i.e. the data being transferred on the bus must not be corrupted.

- Different masters may use different SCL frequencies. A scheme must be devised to synchronize the serial clocks from all masters, in order to let the transmission proceed in a lockstep fashion. This will facilitate the arbitration process.

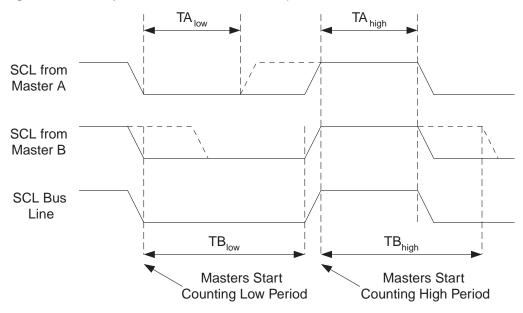

The wired-ANDing of the bus lines is used to solve both these problems. The serial clocks from all masters will be wired-ANDed, yielding a combined clock with a high period equal to the one from the Master with the shortest high period. The low period of the combined clock is equal to the low period of the Master with the longest low period. Note that all masters listen to the SCL line, effectively starting to count their SCL high and low time-out periods when the combined SCL line goes high or low, respectively.

Figure 74. SCL Synchronization Between Multiple Masters

Arbitration is carried out by all masters continuously monitoring the SDA line after outputting data. If the value read from the SDA line does not match the value the Master had output, it has lost the arbitration. Note that a Master can only lose arbitration when it outputs a high SDA value while another Master outputs a low value. The losing Master should immediately go to Slave mode, checking if it is being addressed by the winning Master. The SDA line should be left high, but losing masters are allowed to generate a clock signal until the end of the current data or address packet. Arbitration will continue until only one Master remains, and this may take many bits. If several masters are trying to address the same Slave, arbitration will continue into the data packet.

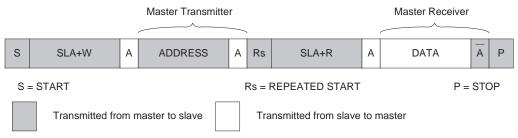

# Combining Several TWI Modes

In some cases, several TWI modes must be combined in order to complete the desired action. Consider for example reading data from a serial EEPROM. Typically, such a transfer involves the following steps:

- 1. The transfer must be initiated.

- 2. The EEPROM must be instructed what location should be read.

- 3. The reading must be performed.

- 4. The transfer must be finished.

Note that data is transmitted both from Master to Slave and vice versa. The Master must instruct the Slave what location it wants to read, requiring the use of the MT mode. Subsequently, data must be read from the Slave, implying the use of the MR mode. Thus, the transfer direction must be changed. The Master must keep control of the bus during all these steps, and the steps should be carried out as an atomical operation. If this principle is violated in a multimaster system, another Master can alter the data pointer in the EEPROM between steps 2 and 3, and the Master will read the wrong data location. Such a change in transfer direction is accomplished by transmitting a REPEATED START between the transmission of the address byte and reception of the data. After a REPEATED START, the Master keeps ownership of the bus. The following figure shows the flow in this transfer.

# Figure 86. Combining Several TWI Modes to Access a Serial EEPROM

# Multi-master Systems and Arbitration

If multiple masters are connected to the same bus, transmissions may be initiated simultaneously by one or more of them. The TWI standard ensures that such situations are handled in such a way that one of the masters will be allowed to proceed with the transfer, and that no data will be lost in the process. An example of an arbitration situation is depicted below, where two masters are trying to transmit data to a Slave Receiver.

Several different scenarios may arise during arbitration, as described below:

# ATmega8(L)

# Analog Comparator Control and Status Register – ACSR

| Bit           | 7   | 6    | 5   | 4   | 3    | 2    | 1     | 0     | _    |

|---------------|-----|------|-----|-----|------|------|-------|-------|------|

|               | ACD | ACBG | ACO | ACI | ACIE | ACIC | ACIS1 | ACIS0 | ACSR |

| Read/Write    | R/W | R/W  | R   | R/W | R/W  | R/W  | R/W   | R/W   | •    |

| Initial Value | 0   | 0    | N/A | 0   | 0    | 0    | 0     | 0     |      |

# • Bit 7 – ACD: Analog Comparator Disable

When this bit is written logic one, the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in Active and Idle mode. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

# • Bit 6 – ACBG: Analog Comparator Bandgap Select

When this bit is set, a fixed bandgap reference voltage replaces the positive input to the Analog Comparator. When this bit is cleared, AIN0 is applied to the positive input of the Analog Comparator. See "Internal Voltage Reference" on page 40.

# • Bit 5 – ACO: Analog Comparator Output

The output of the Analog Comparator is synchronized and then directly connected to ACO. The synchronization introduces a delay of 1 - 2 clock cycles.

# • Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set by hardware when a comparator output event triggers the interrupt mode defined by ACIS1 and ACIS0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set and the I-bit in SREG is set. ACI is cleared by hardware when executing the corresponding interrupt Handling Vector. Alternatively, ACI is cleared by writing a logic one to the flag.

# • Bit 3 – ACIE: Analog Comparator Interrupt Enable

When the ACIE bit is written logic one and the I-bit in the Status Register is set, the Analog Comparator interrupt is activated. When written logic zero, the interrupt is disabled.

# • Bit 2 – ACIC: Analog Comparator Input Capture Enable

When written logic one, this bit enables the Input Capture function in Timer/Counter1 to be triggered by the Analog Comparator. The comparator output is in this case directly connected to the Input Capture front-end logic, making the comparator utilize the noise canceler and edge select features of the Timer/Counter1 Input Capture interrupt. When written logic zero, no connection between the Analog Comparator and the Input Capture function exists. To make the comparator trigger the Timer/Counter1 Input Capture interrupt, the TICIE1 bit in the Timer Interrupt Mask Register (TIMSK) must be set.

# • Bits 1,0 – ACIS1, ACIS0: Analog Comparator Interrupt Mode Select

These bits determine which comparator events that trigger the Analog Comparator interrupt. The different settings are shown in Table 71.

| ACIS1 | ACIS0 | Interrupt Mode                              |  |  |  |

|-------|-------|---------------------------------------------|--|--|--|

| 0     | 0     | Comparator Interrupt on Output Toggle       |  |  |  |

| 0     | 1     | Reserved                                    |  |  |  |

| 1     | 0     | Comparator Interrupt on Falling Output Edge |  |  |  |

| 1     | 1     | Comparator Interrupt on Rising Output Edge  |  |  |  |

Table 71.

ACIS1/ACIS0 Settings

| Table 88. | Fuse L | _ow Byte |

|-----------|--------|----------|

|-----------|--------|----------|

|   | Fuse Low<br>Byte                           | Bit<br>No.                                      | Description                                                                                                                            | Default Value                                                                                                                                                                          |

|---|--------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | BODLEVEL                                   | 7                                               | Brown out detector trigger level                                                                                                       | 1 (unprogrammed)                                                                                                                                                                       |

|   | BODEN                                      | 6                                               | Brown out detector enable                                                                                                              | 1 (unprogrammed, BOD disabled)                                                                                                                                                         |

|   | SUT1                                       | 5                                               | Select start-up time                                                                                                                   | 1 (unprogrammed) <sup>(1)</sup>                                                                                                                                                        |

|   | SUT0                                       | 4                                               | Select start-up time                                                                                                                   | 0 (programmed) <sup>(1)</sup>                                                                                                                                                          |

|   | CKSEL3                                     | 3                                               | Select Clock source                                                                                                                    | 0 (programmed) <sup>(2)</sup>                                                                                                                                                          |

|   | CKSEL2                                     | 2                                               | Select Clock source                                                                                                                    | 0 (programmed) <sup>(2)</sup>                                                                                                                                                          |

|   | CKSEL1                                     | 1                                               | Select Clock source                                                                                                                    | 0 (programmed) <sup>(2)</sup>                                                                                                                                                          |

|   | CKSEL0                                     | 0                                               | Select Clock source                                                                                                                    | 1 (unprogrammed) <sup>(2)</sup>                                                                                                                                                        |

|   | 28<br>2. Th                                | for detail<br>e default                         | S.                                                                                                                                     | m start-up time. SeeTable 10 on page nternal RC Oscillator @ 1MHz. See                                                                                                                 |

|   |                                            |                                                 |                                                                                                                                        | rase. Note that the Fuse Bits are Fuse Bits before programming the                                                                                                                     |

| - | the fuse value<br>not apply to the         | es will ha<br>ne EESA                           | ave no effect until the part leave                                                                                                     | rogramming mode and changes of<br>es Programming mode. This does<br>once it is programmed. The fuses                                                                                   |

| - | code can be r                              | ead in b                                        |                                                                                                                                        | le which identifies the device. This so when the device is locked. The                                                                                                                 |

|   | For the ATme                               | ga8 the                                         | signature bytes are:                                                                                                                   |                                                                                                                                                                                        |

|   | 1. 0x000: 0x                               | 1E (indio                                       | cates manufactured by Atmel).                                                                                                          |                                                                                                                                                                                        |

|   | 2. 0x001: 0x                               | 93 (indic                                       | cates 8KB Flash memory).                                                                                                               |                                                                                                                                                                                        |

|   | 3. 0x002: 0x                               | 07 (indic                                       | cates ATmega8 device).                                                                                                                 |                                                                                                                                                                                        |

| - | These bytes in 0x0002, and 0 is automatica | resides i<br>0x0003 f<br>Ily loade<br>ue has te | in the signature row High byte<br>or 1, 2, 4, and 8 Mhz respective<br>ed into the OSCCAL Register. I<br>o be loaded manually, see "Osc | es for the internal RC Oscillator.<br>of the addresses 0x000, 0x0001,<br>ly. During Reset, the 1 MHz value<br>f other frequencies are used, the<br>illator Calibration Register – OSC- |

# **Data Polling Flash**

When a page is being programmed into the Flash, reading an address location within the page being programmed will give the value 0xFF. At the time the device is ready for a new page, the programmed value will read correctly. This is used to determine when the next page can be written. Note that the entire page is written simultaneously and any address within the page can be used for polling. Data polling of the Flash will not work for the value 0xFF, so when programming this value, the user will have to wait for at least  $t_{WD_{FLASH}}$  before programming the next page. As a chip-erased device contains 0xFF in all locations, programming of addresses that are meant to contain 0xFF, can be skipped. See Table 97 for  $t_{WD_{FLASH}}$  value.

# **Data Polling EEPROM** When a new byte has been written and is being programmed into EEPROM, reading the address location being programmed will give the value 0xFF. At the time the device is ready for a new byte, the programmed value will read correctly. This is used to determine when the next byte can be written. This will not work for the value 0xFF, but the user should have the following in mind: As a chip-erased device contains 0xFF in all locations, programming of addresses that are meant to contain 0xFF, can be skipped. This does not apply if the EEPROM is Re-programmed without chip-erasing the device. In this case, data polling cannot be used for the value 0xFF, and the user will have to wait at least t<sub>WD\_EEPROM</sub> before programming the next byte. See Table 97 for t<sub>WD\_EEPROM</sub> value.

| Symbol                 | Minimum Wait Delay |

|------------------------|--------------------|

| t <sub>WD_FUSE</sub>   | 4.5 ms             |

| t <sub>WD_FLASH</sub>  | 4.5 ms             |

| t <sub>WD_EEPROM</sub> | 9.0 ms             |

| t <sub>WD_ERASE</sub>  | 9.0 ms             |

Table 97. Minimum Wait Delay Before Writing the Next Flash or EEPROM Location

Figure 113. Serial Programming Waveforms

| $T_{A} = -40^{\circ}C$ to 85°C.         | $V_{CC} = 2.7V$ to 5.5V ( | (unless otherwise noted) | (Continued) |

|-----------------------------------------|---------------------------|--------------------------|-------------|

| · A · · · · · · · · · · · · · · · · · · |                           |                          | (000        |

| Symbol            | Parameter                                  | Condition                                        | Min | Тур        | Max | Units |

|-------------------|--------------------------------------------|--------------------------------------------------|-----|------------|-----|-------|

|                   |                                            | Active 4 MHz, V <sub>CC</sub> = 3V<br>(ATmega8L) |     |            | 5   | mA    |

|                   | Power Supply Current                       | Active 8 MHz, V <sub>CC</sub> = 5V<br>(ATmega8)  |     |            | 15  | mA    |

| I <sub>CC</sub>   |                                            | Idle 4 MHz, V <sub>CC</sub> = 3V<br>(ATmega8L)   |     |            | 2   | mA    |

|                   |                                            | Idle 8 MHz, V <sub>CC</sub> = 5V<br>(ATmega8)    |     |            | 7   | mA    |

|                   | Power-down mode <sup>(5)</sup>             | WDT enabled, $V_{CC} = 3V$                       |     |            | 25  | μA    |

|                   |                                            | WDT disabled, $V_{CC} = 3V$                      |     |            | 2   | μA    |

| V <sub>ACIO</sub> | Analog Comparator<br>Input Offset Voltage  | $V_{CC} = 5V$ $V_{in} = V_{CC}/2$                |     |            | 20  | mV    |

| I <sub>ACLK</sub> | Analog Comparator<br>Input Leakage Current | $V_{CC} = 5V$ $V_{in} = V_{CC}/2$                | -50 |            | 50  | nA    |

| t <sub>ACID</sub> | Analog Comparator<br>Propagation Delay     | $V_{CC} = 2.7V$ $V_{CC} = 4.0V$                  |     | 750<br>500 |     | ns    |

Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low

2. "Min" means the lowest value where the pin is guaranteed to be read as high

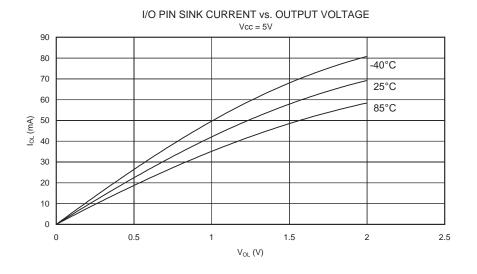

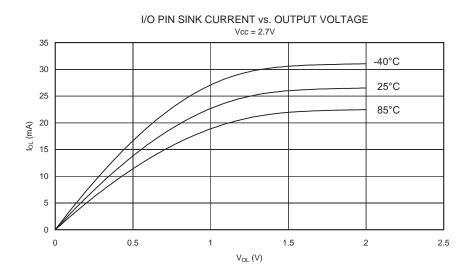

Although each I/O port can sink more than the test conditions (20mA at Vcc = 5V, 10mA at Vcc = 3V) under steady state conditions (non-transient), the following must be observed:

PDIP Package:

1] The sum of all IOL, for all ports, should not exceed 400 mA.

2] The sum of all IOL, for ports C0 - C5 should not exceed 200 mA.

3] The sum of all IOL, for ports B0 - B7, C6, D0 - D7 and XTAL2, should not exceed 100 mA.

TQFP and MLF Package:

1] The sum of all IOL, for all ports, should not exceed 400 mA.

2] The sum of all IOL, for ports C0 - C5, should not exceed 200 mA.

3] The sum of all IOL, for ports C6, D0 - D4, should not exceed 300 mA.

4] The sum of all IOL, for ports B0 - B7, D5 - D7, should not exceed 300 mA.

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

Although each I/O port can source more than the test conditions (20mA at Vcc = 5V, 10mA at Vcc = 3V) under steady state conditions (non-transient), the following must be observed:

PDIP Package:

1] The sum of all IOH, for all ports, should not exceed 400 mA.

2] The sum of all IOH, for port C0 - C5, should not exceed 100 mA.

3] The sum of all IOH, for ports B0 - B7, C6, D0 - D7 and XTAL2, should not exceed 100 mA.

TQFP and MLF Package:

1] The sum of all IOH, for all ports, should not exceed 400 mA.

2] The sum of all IOH, for ports C0 - C5, should not exceed 200 mA.

3] The sum of all IOH, for ports C6, D0 - D4, should not exceed 300 mA.

4] The sum of all IOH, for ports B0 - B7, D5 - D7, should not exceed 300 mA.

If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

5. Minimum  $V_{CC}$  for Power-down is 2.5V.

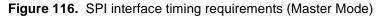

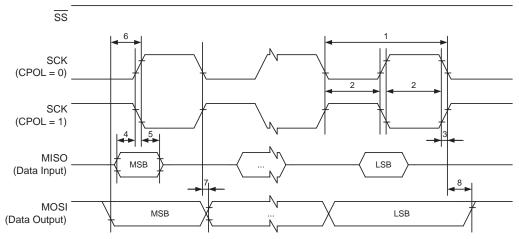

Figure 117. SPI interface timing requirements (Slave Mode)

Figure 149. I/O Pin Sink Current vs. Output Voltage ( $V_{CC} = 5V$ )

Figure 150. I/O Pin Sink Current vs. Output Voltage ( $V_{CC}$  = 2.7V)

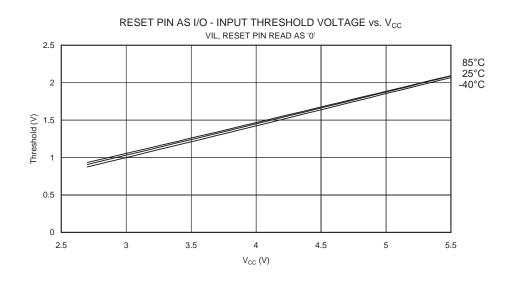

Figure 159. Reset Pin as I/O – Input Threshold Voltage vs.  $V_{CC}$  (V $_{\rm IL}$ , I/O Pin Read as "0")

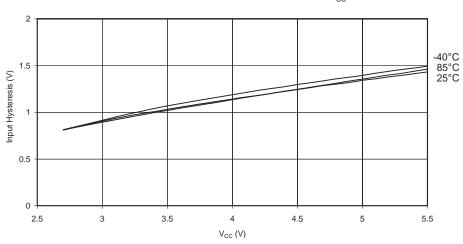

Figure 160. Reset Pin as I/O – Pin Hysteresis vs.  $V_{CC}$

| System Control and Reset                                                                                                                                                                                                                         | 35                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Internal Voltage Reference                                                                                                                                                                                                                       | 40                                                                                |

| Watchdog Timer                                                                                                                                                                                                                                   | 41                                                                                |

| Timed Sequences for Changing the Configuration of the Watchdog Tin                                                                                                                                                                               | ner 43                                                                            |

| Interrupts                                                                                                                                                                                                                                       | 44                                                                                |

| Interrupt Vectors in ATmega8                                                                                                                                                                                                                     | 44                                                                                |

| I/O Ports                                                                                                                                                                                                                                        | 49                                                                                |

| Introduction                                                                                                                                                                                                                                     | 49                                                                                |

| Ports as General Digital I/O                                                                                                                                                                                                                     | 50                                                                                |

| Alternate Port Functions                                                                                                                                                                                                                         | 54                                                                                |

| Register Description for I/O Ports                                                                                                                                                                                                               | 63                                                                                |

| External Interrupts                                                                                                                                                                                                                              | 64                                                                                |

| 8-bit Timer/Counter0                                                                                                                                                                                                                             | 67                                                                                |

| Overview                                                                                                                                                                                                                                         | 67                                                                                |

| Timer/Counter Clock Sources                                                                                                                                                                                                                      | 68                                                                                |

| Counter Unit                                                                                                                                                                                                                                     | 68                                                                                |

| Operation                                                                                                                                                                                                                                        | 68                                                                                |

| Timer/Counter Timing Diagrams                                                                                                                                                                                                                    | 69                                                                                |

| 8-bit Timer/Counter Register Description                                                                                                                                                                                                         |                                                                                   |

|                                                                                                                                                                                                                                                  |                                                                                   |

| Timer/Counter0 and Timer/Counter1 Prescalers                                                                                                                                                                                                     | 72                                                                                |

| Timer/Counter0 and Timer/Counter1 Prescalers                                                                                                                                                                                                     |                                                                                   |

|                                                                                                                                                                                                                                                  |                                                                                   |

| 16-bit Timer/Counter1                                                                                                                                                                                                                            | <b> 74</b><br>74                                                                  |

| <b>16-bit Timer/Counter1</b><br>Overview                                                                                                                                                                                                         | <b> 74</b><br>74<br>77                                                            |

| <b>16-bit Timer/Counter1</b><br>Overview<br>Accessing 16-bit Registers                                                                                                                                                                           | <b> 74</b><br>74<br>77<br>80                                                      |

| <b>16-bit Timer/Counter1</b><br>Overview<br>Accessing 16-bit Registers<br>Timer/Counter Clock Sources                                                                                                                                            | <b>74</b><br>74<br>77<br>80<br>80                                                 |

| <b>16-bit Timer/Counter1</b><br>Overview<br>Accessing 16-bit Registers<br>Timer/Counter Clock Sources.<br>Counter Unit.                                                                                                                          | <b> 74</b><br>74<br>77<br>80<br>80<br>81                                          |

| <b>16-bit Timer/Counter1</b><br>Overview<br>Accessing 16-bit Registers<br>Timer/Counter Clock Sources.<br>Counter Unit.<br>Input Capture Unit.                                                                                                   | <b>74</b><br>74<br>77<br>80<br>80<br>80<br>81<br>81<br>83                         |

| <b>16-bit Timer/Counter1</b><br>Overview<br>Accessing 16-bit Registers<br>Timer/Counter Clock Sources<br>Counter Unit<br>Input Capture Unit<br>Output Compare Units                                                                              | <b>74</b><br>74<br>77<br>80<br>80<br>80<br>81<br>83<br>83<br>85                   |

| <b>16-bit Timer/Counter1</b><br>Overview<br>Accessing 16-bit Registers<br>Timer/Counter Clock Sources<br>Counter Unit<br>Input Capture Unit<br>Output Compare Units<br>Compare Match Output Unit                                                 | <b> 74</b><br>74<br>77<br>80<br>80<br>80<br>81<br>81<br>83<br>85<br>85<br>86      |

| 16-bit Timer/Counter1<br>Overview<br>Accessing 16-bit Registers<br>Timer/Counter Clock Sources.<br>Counter Unit.<br>Input Capture Unit.<br>Output Compare Units<br>Compare Match Output Unit.<br>Modes of Operation                              | <b>74</b><br>74<br>77<br>80<br>80<br>80<br>81<br>83<br>83<br>85<br>85<br>86<br>93 |

| 16-bit Timer/Counter1<br>Overview<br>Accessing 16-bit Registers<br>Timer/Counter Clock Sources<br>Counter Unit<br>Input Capture Unit<br>Output Compare Units<br>Compare Match Output Unit<br>Modes of Operation<br>Timer/Counter Timing Diagrams | <b> 74</b><br>                                                                    |

| <ul> <li>16-bit Timer/Counter1</li></ul>                                                                                                                                                                                                         |                                                                                   |