# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | AVR                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                  |

| Number of I/O              | 23                                                                     |

| Program Memory Size        | 8KB (4K x 16)                                                          |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 512 x 8                                                                |

| RAM Size                   | 1K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                            |

| Data Converters            | A/D 8x10b                                                              |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 32-VFQFN Exposed Pad                                                   |

| Supplier Device Package    | 32-VQFN (5x5)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega8l-8mc |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

When using the SEI instruction to enable interrupts, the instruction following SEI will be executed before any pending interrupts, as shown in the following example.

Assembly Code Example

| <b>sei</b> ; set global interrupt enable                     |

|--------------------------------------------------------------|

| <b>sleep</b> ; enter sleep, waiting for interrupt            |

| ; note: will enter sleep before any pending                  |

| ; interrupt(s)                                               |

| C Code Example                                               |

| _SEI(); /* set global interrupt enable */                    |

| _SLEEP(); /* enter sleep, waiting for interrupt */           |

| /* note: will enter sleep before any pending interrupt(s) */ |

#### **Interrupt Response Time**

The interrupt execution response for all the enabled AVR interrupts is four clock cycles minimum. After four clock cycles, the Program Vector address for the actual interrupt handling routine is executed. During this 4-clock cycle period, the Program Counter is pushed onto the Stack. The Vector is normally a jump to the interrupt routine, and this jump takes three clock cycles. If an interrupt occurs during execution of a multi-cycle instruction, this instruction is completed before the interrupt is served. If an interrupt occurs when the MCU is in sleep mode, the interrupt execution response time is increased by four clock cycles. This increase comes in addition to the start-up time from the selected sleep mode.

A return from an interrupt handling routine takes four clock cycles. During these four clock cycles, the Program Counter (2 bytes) is popped back from the Stack, the Stack Pointer is incremented by 2, and the I-bit in SREG is set.

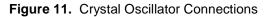

## **Crystal Oscillator**

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an On-chip Oscillator, as shown in Figure 11. Either a quartz crystal or a ceramic resonator may be used. The CKOPT Fuse selects between two different Oscillator amplifier modes. When CKOPT is programmed, the Oscillator output will oscillate a full rail-to-rail swing on the output. This mode is suitable when operating in a very noisy environment or when the output from XTAL2 drives a second clock buffer. This mode has a wide frequency range. When CKOPT is unprogrammed, the Oscillator has a smaller output swing. This reduces power consumption considerably. This mode has a limited frequency range and it cannot be used to drive other clock buffers.

For resonators, the maximum frequency is 8 MHz with CKOPT unprogrammed and 16 MHz with CKOPT programmed. C1 and C2 should always be equal for both crystals and resonators. The optimal value of the capacitors depends on the crystal or resonator in use, the amount of stray capacitance, and the electromagnetic noise of the environment. Some initial guidelines for choosing capacitors for use with crystals are given in Table 4. For ceramic resonators, the capacitor values given by the manufacturer should be used.

The Oscillator can operate in three different modes, each optimized for a specific frequency range. The operating mode is selected by the fuses CKSEL3..1 as shown in Table 4.

| Table 4. | Crystal | Oscillator | Operating | Modes |

|----------|---------|------------|-----------|-------|

|----------|---------|------------|-----------|-------|

| СКОРТ | CKSEL31            | Frequency<br>Range(MHz) | Recommended Range for Capacitors<br>C1 and C2 for Use with Crystals (pF) |

|-------|--------------------|-------------------------|--------------------------------------------------------------------------|

| 1     | 101 <sup>(1)</sup> | 0.4 - 0.9               | -                                                                        |

| 1     | 110                | 0.9 - 3.0               | 12 - 22                                                                  |

| 1     | 111                | 3.0 - 8.0               | 12 - 22                                                                  |

| 0     | 101, 110, 111      | 1.0 ≤                   | 12 - 22                                                                  |

Note: 1. This option should not be used with crystals, only with ceramic resonators.

The CKSEL0 Fuse together with the SUT1..0 Fuses select the start-up times as shown in Table 5.

# Calibrated Internal RC Oscillator

The calibrated internal RC Oscillator provides a fixed 1.0, 2.0, 4.0, or 8.0 MHz clock. All frequencies are nominal values at 5V and 25°C. This clock may be selected as the system clock by programming the CKSEL Fuses as shown in Table 9. If selected, it will operate with no external components. The CKOPT Fuse should always be unprogrammed when using this clock option. During reset, hardware loads the calibration byte into the OSCCAL Register and thereby automatically calibrates the RC Oscillator. At 5V, 25°C and 1.0 MHz Oscillator frequency selected, this calibration gives a frequency within  $\pm$  3% of the nominal frequency. Using run-time calibration methods as described in application notes available at www.atmel.com/avr it is possible to achieve  $\pm$  1% accuracy at any given V<sub>CC</sub> and Temperature. When this Oscillator is used as the chip clock, the Watchdog Oscillator will still be used for the Watchdog Timer and for the Reset Time-out. For more information on the pre-programmed calibration value, see the section "Calibration Byte" on page 221.

| Table 9. | Internal Calibrated RC Oscillator Operating Modes |

|----------|---------------------------------------------------|

|----------|---------------------------------------------------|

| CKSEL30             | Nominal Frequency (MHz) |

|---------------------|-------------------------|

| 0001 <sup>(1)</sup> | 1.0                     |

| 0010                | 2.0                     |

| 0011                | 4.0                     |

| 0100                | 8.0                     |

Note: 1. The device is shipped with this option selected.

When this Oscillator is selected, start-up times are determined by the SUT Fuses as shown in Table 10. PB6 (XTAL1/TOSC1) and PB7(XTAL2/TOSC2) can be used as either general I/O pins or Timer Oscillator pins..

| SUT10             | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | Recommended Usage   |

|-------------------|----------------------------------------------------|------------------------------------------------------------|---------------------|

| 00                | 6 CK                                               | _                                                          | BOD enabled         |

| 01                | 6 CK                                               | 4.1 ms                                                     | Fast rising power   |

| 10 <sup>(1)</sup> | 6 CK                                               | 65 ms                                                      | Slowly rising power |

| 11                |                                                    | Reserved                                                   |                     |

Note: 1. The device is shipped with this option selected.

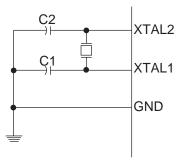

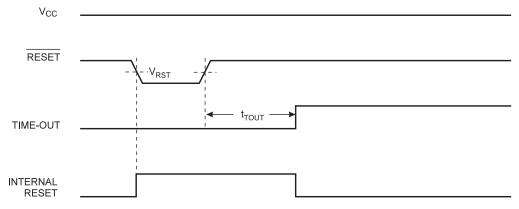

#### **External Reset**

An External Reset is generated by a low level on the RESET pin. Reset pulses longer than the minimum pulse width (see Table 15) will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage –  $V_{RST}$  on its positive edge, the delay counter starts the MCU after the time-out period  $t_{TOUT}$  has expired.

#### **Brown-out Detection**

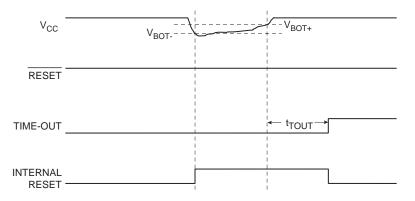

ATmega8 has an On-chip Brown-out Detection (BOD) circuit for monitoring the V<sub>CC</sub> level during operation by comparing it to a fixed trigger level. The trigger level for the BOD can be selected by the fuse BODLEVEL to be 2.7V (BODLEVEL unprogrammed), or 4.0V (BODLEVEL programmed). The trigger level has a hysteresis to ensure spike free Brown-out Detection. The hysteresis on the detection level should be interpreted as  $V_{BOT+} = V_{BOT} + V_{HYST}/2$  and  $V_{BOT-} = V_{BOT} - V_{HYST}/2$ .

The BOD circuit can be enabled/disabled by the fuse BODEN. When the BOD is enabled (BODEN programmed), and  $V_{CC}$  decreases to a value below the trigger level ( $V_{BOT}$  in Figure 18), the Brown-out Reset is immediately activated. When  $V_{CC}$  increases above the trigger level ( $V_{BOT}$  in Figure 18), the delay counter starts the MCU after the time-out period  $t_{TOUT}$  has expired.

The BOD circuit will only detect a drop in  $V_{CC}$  if the voltage stays below the trigger level for longer than  $t_{BOD}$  given in Table 15.

#### Figure 18. Brown-out Reset During Operation

## ATmega8(L)

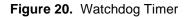

## Watchdog Timer

The Watchdog Timer is clocked from a separate On-chip Oscillator which runs at 1 MHz. This is the typical value at  $V_{CC} = 5V$ . See characterization data for typical values at other  $V_{CC}$  levels. By controlling the Watchdog Timer prescaler, the Watchdog Reset interval can be adjusted as shown in Table 17 on page 42. The WDR – Watchdog Reset – instruction resets the Watchdog Timer. The Watchdog Timer is also reset when it is disabled and when a Chip Reset occurs. Eight different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog Reset, the ATmega8 resets and executes from the Reset Vector. For timing details on the Watchdog Reset, refer to page 39.

To prevent unintentional disabling of the Watchdog, a special turn-off sequence must be followed when the Watchdog is disabled. Refer to the description of the Watchdog Timer Control Register for details.

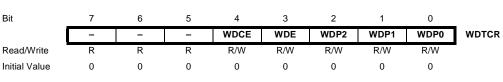

#### Watchdog Timer Control Register – WDTCR

#### • Bits 7..5 - Res: Reserved Bits

These bits are reserved bits in the ATmega8 and will always read as zero.

#### • Bit 4 – WDCE: Watchdog Change Enable

This bit must be set when the WDE bit is written to logic zero. Otherwise, the Watchdog will not be disabled. Once written to one, hardware will clear this bit after four clock cycles. Refer to the description of the WDE bit for a Watchdog disable procedure. In Safety Level 1 and 2, this bit must also be set when changing the prescaler bits. See the Code Examples on page 43.

## I/O Ports

### Introduction

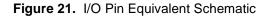

All AVR ports have true Read-Modify-Write functionality when used as general digital I/O ports. This means that the direction of one port pin can be changed without unintentionally changing the direction of any other pin with the SBI and CBI instructions. The same applies when changing drive value (if configured as output) or enabling/disabling of pull-up resistors (if configured as input). Each output buffer has symmetrical drive characteristics with both high sink and source capability. The pin driver is strong enough to drive LED displays directly. All port pins have individually selectable pull-up resistors with a supply-voltage invariant resistance. All I/O pins have protection diodes to both  $V_{CC}$  and Ground as indicated in Figure 21. Refer to "Electrical Characteristics" on page 237 for a complete list of parameters.

All registers and bit references in this section are written in general form. A lower case "x" represents the numbering letter for the port, and a lower case "n" represents the bit number. However, when using the register or bit defines in a program, the precise form must be used (i.e., PORTB3 for bit 3 in Port B, here documented generally as PORTxn). The physical I/O Registers and bit locations are listed in "Register Description for I/O Ports" on page 63.

Three I/O memory address locations are allocated for each port, one each for the Data Register – PORTx, Data Direction Register – DDRx, and the Port Input Pins – PINx. The Port Input Pins I/O location is read only, while the Data Register and the Data Direction Register are read/write. In addition, the Pull-up Disable – PUD bit in SFIOR disables the pull-up function for all pins in all ports when set.

Using the I/O port as General Digital I/O is described in "Ports as General Digital I/O" on page 50. Most port pins are multiplexed with alternate functions for the peripheral features on the device. How each alternate function interferes with the port pin is described in "Alternate Port Functions" on page 54. Refer to the individual module sections for a full description of the alternate functions.

Note that enabling the alternate function of some of the port pins does not affect the use of the other pins in the port as general digital I/O.

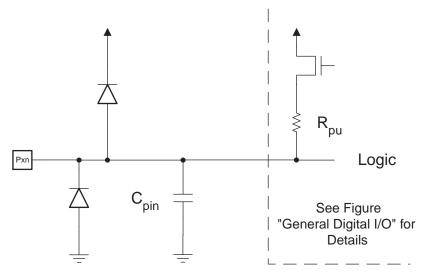

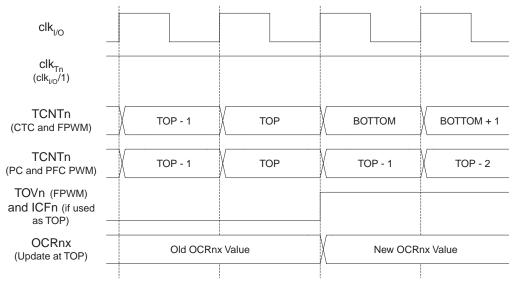

Figure 42. Timer/Counter Timing Diagram, Setting of OCF1x, with Prescaler (f<sub>clk I/O</sub>/8)

Figure 43 shows the count sequence close to TOP in various modes. When using phase and frequency correct PWM mode the OCR1x Register is updated at BOTTOM. The timing diagrams will be the same, but TOP should be replaced by BOTTOM, TOP-1 by BOTTOM+1 and so on. The same renaming applies for modes that set the TOV1 Flag at BOTTOM.

Figure 43. Timer/Counter Timing Diagram, no Prescaling

Figure 44 shows the same timing data, but with the prescaler enabled.

what type of waveform generation to be used, see Table 39. Modes of operation supported by the Timer/Counter unit are: Normal mode (counter), Clear Timer on Compare Match (CTC) mode, and three types of Pulse Width Modulation (PWM) modes. (See "Modes of Operation" on page 86.)

Table 39. Waveform Generation Mode Bit Description

| Mode | WGM13 | WGM12<br>(CTC1) | WGM11<br>(PWM11) | WGM10<br>(PWM10) | Timer/Counter Mode of Operation <sup>(1)</sup> | ТОР    | Update of OCR1x | TOV1 Flag<br>Set on |

|------|-------|-----------------|------------------|------------------|------------------------------------------------|--------|-----------------|---------------------|

| 0    | 0     | 0               | 0                | 0                | Normal                                         | 0xFFFF | Immediate       | MAX                 |

| 1    | 0     | 0               | 0                | 1                | PWM, Phase Correct, 8-bit                      | 0x00FF | TOP             | BOTTOM              |

| 2    | 0     | 0               | 1                | 0                | PWM, Phase Correct, 9-bit                      | 0x01FF | TOP             | BOTTOM              |

| 3    | 0     | 0               | 1                | 1                | PWM, Phase Correct, 10-bit                     | 0x03FF | TOP             | BOTTOM              |

| 4    | 0     | 1               | 0                | 0                | СТС                                            | OCR1A  | Immediate       | MAX                 |

| 5    | 0     | 1               | 0                | 1                | Fast PWM, 8-bit                                | 0x00FF | TOP             | ТОР                 |

| 6    | 0     | 1               | 1                | 0                | Fast PWM, 9-bit                                | 0x01FF | TOP             | ТОР                 |

| 7    | 0     | 1               | 1                | 1                | Fast PWM, 10-bit                               | 0x03FF | ТОР             | ТОР                 |

| 8    | 1     | 0               | 0                | 0                | PWM, Phase and Frequency<br>Correct            | ICR1   | BOTTOM          | BOTTOM              |

| 9    | 1     | 0               | 0                | 1                | PWM, Phase and Frequency<br>Correct            | OCR1A  | BOTTOM          | BOTTOM              |

| 10   | 1     | 0               | 1                | 0                | PWM, Phase Correct                             | ICR1   | TOP             | BOTTOM              |

| 11   | 1     | 0               | 1                | 1                | PWM, Phase Correct                             | OCR1A  | TOP             | BOTTOM              |

| 12   | 1     | 1               | 0                | 0                | СТС                                            | ICR1   | Immediate       | MAX                 |

| 13   | 1     | 1               | 0                | 1                | (Reserved)                                     | -      | -               | -                   |

| 14   | 1     | 1               | 1                | 0                | Fast PWM                                       | ICR1   | TOP             | ТОР                 |

| 15   | 1     | 1               | 1                | 1                | Fast PWM                                       | OCR1A  | ТОР             | TOP                 |

Note: 1. The CTC1 and PWM11:0 bit definition names are obsolete. Use the WGM12:0 definitions. However, the functionality and location of these bits are compatible with previous versions of the timer.

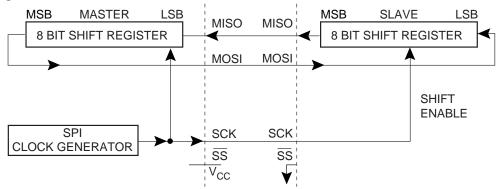

When configured as a Master, the SPI interface has no automatic control of the SS line. This must be handled by user software before communication can start. When this is done, writing a byte to the SPI Data Register starts the SPI clock generator, and the hardware shifts the eight bits into the Slave. After shifting one byte, the SPI clock generator stops, setting the end of Transmission Flag (SPIF). If the SPI interrupt enable bit (SPIE) in the SPCR Register is set, an interrupt is requested. The Master may continue to shift the next byte by writing it into SPDR, or signal the end of packet by pulling high the Slave Select, SS line. The last incoming byte will be kept in the Buffer Register for later use.

When configured as a Slave, the SPI interface will remain sleeping with MISO tri-stated as long as the SS pin is driven high. In this state, software may update the contents of the SPI Data Register, SPDR, but the data will not be shifted out by incoming clock pulses on the SCK pin until the SS pin is driven low. As one byte has been completely shifted, the end of Transmission Flag, SPIF is set. If the SPI interrupt enable bit, SPIE, in the SPCR Register is set, an interrupt is requested. The Slave may continue to place new data to be sent into SPDR before reading the incoming data. The last incoming byte will be kept in the Buffer Register for later use.

Figure 58. SPI Master-Slave Interconnection

The system is single buffered in the transmit direction and double buffered in the receive direction. This means that bytes to be transmitted cannot be written to the SPI Data Register before the entire shift cycle is completed. When receiving data, however, a received character must be read from the SPI Data Register before the next character has been completely shifted in. Otherwise, the first byte is lost.

In SPI Slave mode, the control logic will sample the incoming signal of the SCK pin. To ensure correct sampling of the clock signal, the frequency of the SPI clock should never exceed  $f_{osc}/4$ .

When the SPI is enabled, the data direction of the MOSI, MISO, SCK, and SS pins is overridden according to Table 47. For more details on automatic port overrides, refer to "Alternate Port Functions" on page 54.

Table 47. SPI Pin Overrides<sup>(1)</sup>

| Pin  | Direction, Master SPI | Direction, Slave SPI |

|------|-----------------------|----------------------|

| MOSI | User Defined          | Input                |

| MISO | Input                 | User Defined         |

| SCK  | User Defined          | Input                |

| SS   | User Defined          | Input                |

Note: 1. See "Port B Pins Alternate Functions" on page 56 for a detailed description of how to define the direction of the user defined SPI pins.

- Sp Stop bit, always high.

- IDLE No transfers on the communication line (RxD or TxD). An IDLE line must be high.

The frame format used by the USART is set by the UCSZ2:0, UPM1:0 and USBS bits in UCSRB and UCSRC. The Receiver and Transmitter use the same setting. Note that changing the setting of any of these bits will corrupt all ongoing communication for both the Receiver and Transmitter.

The USART Character SiZe (UCSZ2:0) bits select the number of data bits in the frame. The USART Parity mode (UPM1:0) bits enable and set the type of parity bit. The selection between one or two stop bits is done by the USART Stop Bit Select (USBS) bit. The Receiver ignores the second stop bit. An FE (Frame Error) will therefore only be detected in the cases where the first stop bit is zero.

**Parity Bit Calculation** The parity bit is calculated by doing an exclusive-or of all the data bits. If odd parity is used, the result of the exclusive or is inverted. The relation between the parity bit and data bits is as follows:

$$P_{even} = d_{n-1} \oplus \dots \oplus d_3 \oplus d_2 \oplus d_1 \oplus d_0 \oplus 0$$

$$P_{odd} = d_{n-1} \oplus \dots \oplus d_3 \oplus d_2 \oplus d_1 \oplus d_0 \oplus 1$$

Peven Parity bit using even parity.

- P<sub>odd</sub> Parity bit using odd parity.

- d<sub>n</sub> Data bit n of the character.

If used, the parity bit is located between the last data bit and first stop bit of a serial frame.

#### **USART Initialization** The USART has to be initialized before any communication can take place. The initialization process normally consists of setting the baud rate, setting frame format and enabling the Transmitter or the Receiver depending on the usage. For interrupt driven USART operation, the Global Interrupt Flag should be cleared (and interrupts globally disabled) when doing the initialization.

Before doing a re-initialization with changed baud rate or frame format, be sure that there are no ongoing transmissions during the period the registers are changed. The TXC Flag can be used to check that the Transmitter has completed all transfers, and the RXC Flag can be used to check that there are no unread data in the receive buffer. Note that the TXC Flag must be cleared before each transmission (before UDR is written) if it is used for this purpose.

The following simple USART initialization code examples show one assembly and one C function that are equal in functionality. The examples assume asynchronous operation using polling (no interrupts enabled) and a fixed frame format. The baud rate is given as a function parameter. For the assembly code, the baud rate parameter is assumed to be stored in the r17:r16 Registers. When the function writes to the UCSRC Register, the URSEL bit (MSB) must be set due to the sharing of I/O location by UBRRH and UCSRC.

```

Assembly Code Example<sup>(1)</sup>

```

```

USART_Init:

; Set baud rate

out UBRRH, r17

out UBRRL, r16

; Enable Receiver and Transmitter

ldi r16, (1<<RXEN)|(1<<TXEN)

out UCSRB,r16

; Set frame format: 8data, 2stop bit

ldi r16, (1<<URSEL)|(1<<USBS)|(3<<UCSZ0)

out UCSRC,r16

ret

```

C Code Example<sup>(1)</sup>

```

void USART_Init( unsigned int baud )

{

/* Set baud rate */

UBRRH = (unsigned char)(baud>>8);

UBRRL = (unsigned char)baud;

/* Enable Receiver and Transmitter */

UCSRB = (1<<RXEN)|(1<<TXEN);

/* Set frame format: 8data, 2stop bit */

UCSRC = (1<<URSEL)|(1<<USBS)|(3<UCSZO);

}</pre>

```

Note: 1. The example codes assume that the part specific header file is included.

More advanced initialization routines can be made that include frame format as parameters, disable interrupts and so on. However, many applications use a fixed setting of the Baud and Control Registers, and for these types of applications the initialization code can be placed directly in the main routine, or be combined with initialization code for other I/O modules.

|   |  | E | L          |

|---|--|---|------------|

| _ |  |   | _          |

|   |  |   | <b>7</b> 🖪 |

| Multi-processor<br>Communication Mode | Setting the Multi-processor Communication mode (MPCM) bit in UCSRA enables a fil-<br>tering function of incoming frames received by the USART Receiver. Frames that do not<br>contain address information will be ignored and not put into the receive buffer. This<br>effectively reduces the number of incoming frames that has to be handled by the CPU,<br>in a system with multiple MCUs that communicate via the same serial bus. The Trans-<br>mitter is unaffected by the MPCM setting, but has to be used differently when it is a part<br>of a system utilizing the Multi-processor Communication mode. |  |  |  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                       | If the Receiver is set up to receive frames that contain 5 to 8 data bits, then the first stop bit indicates if the frame contains data or address information. If the Receiver is set up for frames with nine data bits, then the ninth bit (RXB8) is used for identifying address and data frames. When the frame type bit (the first stop or the ninth bit) is one, the frame contains an address. When the frame type bit is zero the frame is a data frame.                                                                                                                                                  |  |  |  |

|                                       | The Multi-processor Communication mode enables several Slave MCUs to receive data from a Master MCU. This is done by first decoding an address frame to find out which MCU has been addressed. If a particular Slave MCU has been addressed, it will receive the following data frames as normal, while the other Slave MCUs will ignore the received frames until another address frame is received.                                                                                                                                                                                                             |  |  |  |

| Using MPCM                            | For an MCU to act as a Master MCU, it can use a 9-bit character frame format (UCSZ = 7). The ninth bit (TXB8) must be set when an address frame (TXB8 = 1) or cleared when a data frame (TXB = 0) is being transmitted. The Slave MCUs must in this case be set to use a 9-bit character frame format.                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       | The following procedure should be used to exchange data in Multi-processor Communi-<br>cation mode:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|                                       | <ol> <li>All Slave MCUs are in Multi-processor Communication mode (MPCM in UCSRA<br/>is set).</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|                                       | <ol> <li>The Master MCU sends an address frame, and all slaves receive and read this frame. In the Slave MCUs, the RXC Flag in UCSRA will be set as normal.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                       | 3. Each Slave MCU reads the UDR Register and determines if it has been selected. If so, it clears the MPCM bit in UCSRA, otherwise it waits for the next address byte and keeps the MPCM setting.                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                       | 4. The addressed MCU will receive all data frames until a new address frame is received. The other Slave MCUs, which still have the MPCM bit set, will ignore the data frames.                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                       | 5. When the last data frame is received by the addressed MCU, the addressed MCU sets the MPCM bit and waits for a new address frame from Master. The process then repeats from 2.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                       | Using any of the 5- to 8-bit character frame formats is possible, but impractical since the Receiver must change between using n and n+1 character frame formats. This makes full-duplex operation difficult since the Transmitter and Receiver uses the same character size setting. If 5- to 8-bit character frames are used, the Transmitter must be set to use two stop bit (USBS = 1) since the first stop bit is used for indicating the frame type.                                                                                                                                                        |  |  |  |

|                                       | Do not use Read-Modify-Write instructions (SBI and CBI) to set or clear the MPCM bit. The MPCM bit shares the same I/O location as the TXC Flag and this might accidentally be cleared when using SBI or CBI instructions.                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

#### • Bit 5:4 – UPM1:0: Parity Mode

These bits enable and set type of Parity Generation and Check. If enabled, the Transmitter will automatically generate and send the parity of the transmitted data bits within each frame. The Receiver will generate a parity value for the incoming data and compare it to the UPM0 setting. If a mismatch is detected, the PE Flag in UCSRA will be set.

#### Table 56. UPM Bits Settings

| UPM1 | UPM0 | Parity Mode          |

|------|------|----------------------|

| 0    | 0    | Disabled             |

| 0    | 1    | Reserved             |

| 1    | 0    | Enabled, Even Parity |

| 1    | 1    | Enabled, Odd Parity  |

#### • Bit 3 – USBS: Stop Bit Select

This bit selects the number of stop bits to be inserted by the trAnsmitter. The Receiver ignores this setting.

#### Table 57. USBS Bit Settings

| USBS | Stop Bit(s) |

|------|-------------|

| 0    | 1-bit       |

| 1    | 2-bit       |

#### • Bit 2:1 – UCSZ1:0: Character Size

The UCSZ1:0 bits combined with the UCSZ2 bit in UCSRB sets the number of data bits (Character Size) in a frame the Receiver and Transmitter use.

#### Table 58. UCSZ Bits Settings

| UCSZ2 | UCSZ1 | UCSZ0 | Character Size |

|-------|-------|-------|----------------|

| 0     | 0     | 0     | 5-bit          |

| 0     | 0     | 1     | 6-bit          |

| 0     | 1     | 0     | 7-bit          |

| 0     | 1     | 1     | 8-bit          |

| 1     | 0     | 0     | Reserved       |

| 1     | 0     | 1     | Reserved       |

| 1     | 1     | 0     | Reserved       |

| 1     | 1     | 1     | 9-bit          |

• Bit 0 – UCPOL: Clock Polarity

## ATmega8(L)

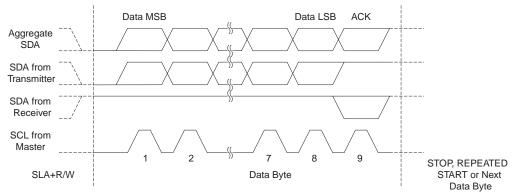

#### **Data Packet Format**

All data packets transmitted on the TWI bus are nine bits long, consisting of one data byte and an acknowledge bit. During a data transfer, the Master generates the clock and the START and STOP conditions, while the Receiver is responsible for acknowledging the reception. An Acknowledge (ACK) is signalled by the Receiver pulling the SDA line low during the ninth SCL cycle. If the Receiver leaves the SDA line high, a NACK is signalled. When the Receiver has received the last byte, or for some reason cannot receive any more bytes, it should inform the Transmitter by sending a NACK after the final byte. The MSB of the data byte is transmitted first.

#### Figure 72. Data Packet Format

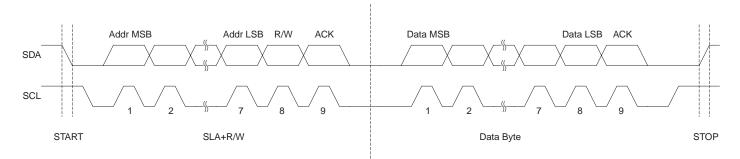

# Combining Address and Data Packets into a Transmission

A transmission basically consists of a START condition, a SLA+R/W, one or more data packets and a STOP condition. An empty message, consisting of a START followed by a STOP condition, is illegal. Note that the Wired-ANDing of the SCL line can be used to implement handshaking between the Master and the Slave. The Slave can extend the SCL low period by pulling the SCL line low. This is useful if the clock speed set up by the Master is too fast for the Slave, or the Slave needs extra time for processing between the data transmissions. The Slave extending the SCL low period will not affect the SCL high period, which is determined by the Master. As a consequence, the Slave can reduce the TWI data transfer speed by prolonging the SCL duty cycle.

Figure 73 shows a typical data transmission. Note that several data bytes can be transmitted between the SLA+R/W and the STOP condition, depending on the software protocol implemented by the application software.

Figure 73. Typical Data Transmission

#### **Slave Transmitter Mode**

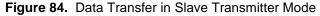

In the Slave Transmitter mode, a number of data bytes are transmitted to a Master Receiver (see Figure 84). All the status codes mentioned in this section assume that the prescaler bits are zero or are masked to zero.

To initiate the Slave Transmitter mode, TWAR and TWCR must be initialized as follows:

| TWAR  | TWA6                       | TWA5 | TWA4 | TWA3 | TWA2 | TWA1 | TWA0 | TWGCE |

|-------|----------------------------|------|------|------|------|------|------|-------|

| value | Device's Own Slave Address |      |      |      |      |      |      |       |

The upper seven bits are the address to which the Two-wire Serial Interface will respond when addressed by a Master. If the LSB is set, the TWI will respond to the general call address (0x00), otherwise it will ignore the general call address.

| TWCR  | TWINT | TWEA | TWSTA | TWSTO | тwwc | TWEN | - | TWIE |

|-------|-------|------|-------|-------|------|------|---|------|

| value | 0     | 1    | 0     | 0     | 0    | 1    | 0 | Х    |

TWEN must be written to one to enable the TWI. The TWEA bit must be written to one to enable the acknowledgement of the device's own slave address or the general call address. TWSTA and TWSTO must be written to zero.

When TWAR and TWCR have been initialized, the TWI waits until it is addressed by its own slave address (or the general call address if enabled) followed by the data direction bit. If the direction bit is "1" (read), the TWI will operate in ST mode, otherwise SR mode is entered. After its own slave address and the write bit have been received, the TWINT Flag is set and a valid status code can be read from TWSR. The status code is used to determine the appropriate software action. The appropriate action to be taken for each status code is detailed in Table 69. The Slave Transmitter mode may also be entered if arbitration is lost while the TWI is in the Master mode (see state 0xB0).

If the TWEA bit is written to zero during a transfer, the TWI will transmit the last byte of the transfer. State 0xC0 or state 0xC8 will be entered, depending on whether the Master Receiver transmits a NACK or ACK after the final byte. The TWI is switched to the not addressed Slave mode, and will ignore the Master if it continues the transfer. Thus the Master Receiver receives all "1" as serial data. State 0xC8 is entered if the Master demands additional data bytes (by transmitting ACK), even though the Slave has transmitted the last byte (TWEA zero and expecting NACK from the Master).

While TWEA is zero, the TWI does not respond to its own slave address. However, the Two-wire Serial Bus is still monitored and address recognition may resume at any time by setting TWEA. This implies that the TWEA bit may be used to temporarily isolate the TWI from the Two-wire Serial Bus.

### Parallel Programming Parameters, Pin Mapping, and Commands

This section describes how to parallel program and verify Flash Program memory, EEPROM Data memory, Memory Lock Bits, and Fuse Bits in the ATmega8. Pulses are assumed to be at least 250 ns unless otherwise noted.

**Signal Names**

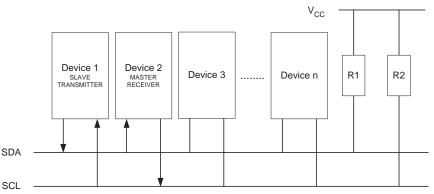

In this section, some pins of the ATmega8 are referenced by signal names describing their functionality during parallel programming, see Figure 104 and Table 89. Pins not described in the following table are referenced by pin names.

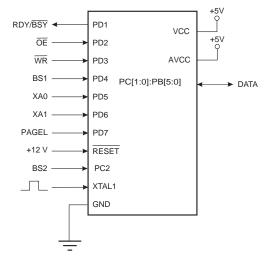

The XA1/XA0 pins determine the action executed when the XTAL1 pin is given a positive pulse. The bit coding is shown in Table 91.

When pulsing WR or OE, the command loaded determines the action executed. The different Commands are shown in Table 92.

#### Figure 104. Parallel Programming

Table 89.Pin Name Mapping

| Signal Name in<br>Programming Mode | Pin Name | I/O | Function                                                          |

|------------------------------------|----------|-----|-------------------------------------------------------------------|

| RDY/BSY                            | PD1      | 0   | 0: Device is busy programming, 1: Device is ready for new command |

| OE                                 | PD2      | I   | Output Enable (Active low)                                        |

| WR                                 | PD3      | I   | Write Pulse (Active low)                                          |

| BS1                                | PD4      | I   | Byte Select 1 ("0" selects Low byte, "1" selects High byte)       |

| XA0                                | PD5      | I   | XTAL Action Bit 0                                                 |

| XA1                                | PD6      | I   | XTAL Action Bit 1                                                 |

Figure 111. Parallel Programming Timing, Reading Sequence (within the same Page) with Timing Requirements<sup>(1)</sup>

Note: 1. The timing requirements shown in Figure 109 (i.e., t<sub>DVXH</sub>, t<sub>XHXL</sub>, and t<sub>XLDX</sub>) also apply to reading operation.

| Symbol               | Parameter                                            | Min  | Тур | Max  | Units |

|----------------------|------------------------------------------------------|------|-----|------|-------|

| V <sub>PP</sub>      | Programming Enable Voltage                           | 11.5 |     | 12.5 | V     |

| I <sub>PP</sub>      | Programming Enable Current                           |      |     | 250  | μA    |

| t <sub>DVXH</sub>    | Data and Control Valid before XTAL1 High             | 67   |     |      | ns    |

| t <sub>XLXH</sub>    | XTAL1 Low to XTAL1 High                              | 200  |     |      | ns    |

| t <sub>XHXL</sub>    | XTAL1 Pulse Width High                               | 150  |     |      | ns    |

| t <sub>XLDX</sub>    | Data and Control Hold after XTAL1 Low                | 67   |     |      | ns    |

| t <sub>XLWL</sub>    | XTAL1 Low to WR Low                                  | 0    |     |      | ns    |

| t <sub>XLPH</sub>    | XTAL1 Low to PAGEL high                              | 0    |     |      | ns    |

| t <sub>PLXH</sub>    | PAGEL low to XTAL1 high                              | 150  |     |      | ns    |

| t <sub>BVPH</sub>    | BS1 Valid before PAGEL High                          | 67   |     |      | ns    |

| t <sub>PHPL</sub>    | PAGEL Pulse Width High                               | 150  |     |      | ns    |

| t <sub>PLBX</sub>    | BS1 Hold after PAGEL Low                             | 67   |     |      | ns    |

| t <sub>WLBX</sub>    | BS2/1 Hold after WR Low                              | 67   |     |      | ns    |

| t <sub>PLWL</sub>    | PAGEL Low to WR Low                                  | 67   |     |      | ns    |

| t <sub>BVWL</sub>    | BS1 Valid to WR Low                                  | 67   |     |      | ns    |

| t <sub>WLWH</sub>    | WR Pulse Width Low                                   | 150  |     |      | ns    |

| t <sub>WLRL</sub>    | WR Low to RDY/BSY Low                                | 0    |     | 1    | μs    |

| t <sub>WLRH</sub>    | WR Low to RDY/BSY High <sup>(1)</sup>                | 3.7  |     | 4.5  | ms    |

| t <sub>WLRH_CE</sub> | WR Low to RDY/BSY High for Chip Erase <sup>(2)</sup> | 7.5  |     | 9    | ms    |

| t <sub>XLOL</sub>    | XTAL1 Low to OE Low                                  | 0    |     |      | ns    |

**Table 95.** Parallel Programming Characteristics,  $V_{CC} = 5V \pm 10\%$

Table 98. Serial Programming Instruction Set

|                              |                   | Instructio        | ]                 |                   |                                                                                                                                                                                                 |  |  |

|------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Instruction                  | Byte 1            | Byte 2            | Byte 3            | Byte4             | Operation                                                                                                                                                                                       |  |  |

| Programming Enable           | 1010 1100         | 0101 0011         | XXXX XXXX         | xxxx xxxx         | Enable Serial Programming after RESET goes low.                                                                                                                                                 |  |  |

| Chip Erase                   | 1010 1100         | 100x xxxx         | xxxx xxxx         | xxxx xxxx         | Chip Erase EEPROM and Flash.                                                                                                                                                                    |  |  |

| Read Program Memory          | 0010 <b>H</b> 000 | 0000 <b>aaaa</b>  | bbbb bbbb         | 0000 0000         | Read <b>H</b> (high or low) data <b>o</b> from<br>Program memory at word address<br><b>a</b> : <b>b</b> .                                                                                       |  |  |

| Load Program Memory<br>Page  | 0100 <b>H</b> 000 | 0000 xxxx         | xxxb bbbb         | iiii iiii         | Write <b>H</b> (high or low) data <b>i</b> to<br>Program memory page at word<br>address <b>b</b> . Data Low byte must be<br>loaded before Data High byte is<br>applied within the same address. |  |  |

| Write Program Memory<br>Page | 0100 1100         | 0000 <b>aaaa</b>  | bbbx xxxx         | xxxx xxxx         | Write Program memory Page at address <b>a</b> : <b>b</b> .                                                                                                                                      |  |  |

| Read EEPROM Memory           | 1010 0000         | 00xx xxx <b>a</b> | bbbb bbbb         | 0000 0000         | Read data <b>o</b> from EEPROM memory at address <b>a</b> : <b>b</b> .                                                                                                                          |  |  |

| Write EEPROM Memory          | 1100 0000         | 00xx xxx <b>a</b> | bbbb bbbb         | 1111 1111         | Write data i to EEPROM memory at address a:b.                                                                                                                                                   |  |  |

| Read Lock Bits               | 0101 1000         | 0000 0000         | xxxx xxxx         | xx <b>oo oooo</b> | Read Lock Bits. "0" = programmed,<br>"1" = unprogrammed. See Table<br>85 on page 219 for details.                                                                                               |  |  |

| Write Lock Bits              | 1010 1100         | 111x xxxx         | xxxx xxxx         | 11 <b>ii iiii</b> | Write Lock Bits. Set bits = "0" to<br>program Lock Bits. See Table 85<br>on page 219 for details.                                                                                               |  |  |

| Read Signature Byte          | 0011 0000         | 00xx xxxx         | xxxx xx <b>bb</b> | 0000 0000         | Read Signature Byte <b>o</b> at address <b>b</b> .                                                                                                                                              |  |  |

| Write Fuse Bits              | 1010 1100         | 1010 0000         | xxxx xxxx         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 88 on<br>page 221 for details.                                                                                                        |  |  |

| Write Fuse High Bits         | 1010 1100         | 1010 1000         | xxxx xxxx         | iiii iiii         | Set bits = "0" to program, "1" to<br>unprogram. See Table 87 on<br>page 220 for details.                                                                                                        |  |  |

| Read Fuse Bits               | 0101 0000         | 0000 0000         | xxxx xxxx         | 0000 0000         | Read Fuse Bits. "0" = programmed,<br>"1" = unprogrammed. See Table<br>88 on page 221 for details.                                                                                               |  |  |

| Read Fuse High Bits          | 0101 1000         | 0000 1000         | XXXX XXXX         | 0000 0000         | Read Fuse high bits. "0" = pro-<br>grammed, "1" = unprogrammed.<br>See Table 87 on page 220 for<br>details.                                                                                     |  |  |

| Read Calibration Byte        | 0011 1000         | 00xx xxxx         | 0000 00 <b>bb</b> | 0000 0000         | Read Calibration Byte                                                                                                                                                                           |  |  |

Note: **a** = address high bits

**b** = address low bits

$\mathbf{H} = 0 - \text{Low byte}, 1 - \text{High byte}$

o = data out

i = data in

x = don't care

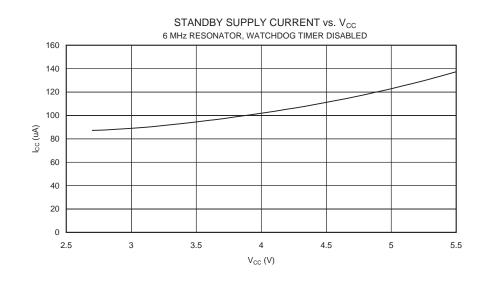

Figure 141. Standby Supply Current vs.  $V_{CC}$  (6 MHz Resonator, Watchdog Timer Disabled)

## Datasheet Change Log for ATmega8

Changes from Rev. 2486K-08/03 to Rev. 2486L-10/03

Changes from Rev. 2486K-08/03 to Rev. 2486L-10/03 This document contains a log on the changes made to the datasheet for ATmega8.

All page numbers refers to this document.

1. Updated "Calibrated Internal RC Oscillator" on page 28.

All page numbers refers to this document.

- 1. Removed "Preliminary" and TBDs from the datasheet.

- 2. Renamed ICP to ICP1 in the datasheet.

- 3. Removed instructions CALL and JMP from the datasheet.

- 4. Updated  $t_{RST}$  in Table 15 on page 36,  $V_{BG}$  in Table 16 on page 40, Table 100 on page 239 and Table 102 on page 241.

- 5. Replaced text "XTAL1 and XTAL2 should be left unconnected (NC)" after Table 9 in "Calibrated Internal RC Oscillator" on page 28. Added text regarding XTAL1/XTAL2 and CKOPT Fuse in "Timer/Counter Oscillator" on page 30.

- 6. Updated Watchdog Timer code examples in "Timed Sequences for Changing the Configuration of the Watchdog Timer" on page 43.

- 7. Removed bit 4, ADHSM, from "Special Function IO Register SFIOR" on page 56.

- 8. Added note 2 to Figure 103 on page 212.

- 9. Updated item 4 in the "Serial Programming Algorithm" on page 233.

- 10. Added t<sub>WD\_FUSE</sub> to Table 97 on page 234 and updated Read Calibration Byte, Byte 3, in Table 98 on page 235.

- 11. Updated Absolute Maximum Ratings\* and DC Characteristics in "Electrical Characteristics" on page 237.

All page numbers refers to this document.

- 1. Updated V<sub>BOT</sub> values in Table 15 on page 36.

- 2. Updated "ADC Characteristics" on page 243.

- 3. Updated "ATmega8 Typical Characteristics" on page 244.

- 4. Updated "Erratas" on page 291.

Changes from Rev. 2486I-12/02 to Rev. 2486J-02/03

Changes from Rev.

2486J-02/03 to Rev.

2486K-08/03

All page numbers refers to this document.

292 ATmega8(L)