Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, LINbus, UART/USART                                            |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 13                                                                              |

| Program Memory Size        | 32KB (32K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 2K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                                     |

| Data Converters            | A/D 6x8/10b                                                                     |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 20-LSSOP (0.173", 4.40mm Width)                                                 |

| Supplier Device Package    | 20-LSSOP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f1076cmsp-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

RL78/I1A 1. OUTLINE

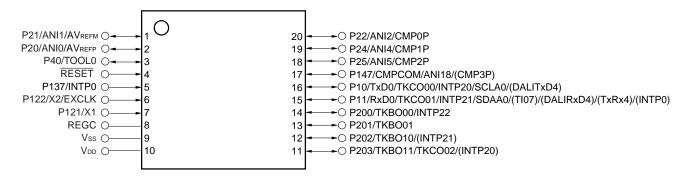

### 1.3 Pin Configuration (Top View)

#### 1.3.1 20-pin products

• 20-pin plastic LSSOP (4.4 x 6.5)

Caution Connect the REGC pin to Vss via a capacitor (0.47 to 1  $\mu$ F).

- Remarks 1. For pin identification, see 1.4 Pin Identification.

- 2. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR1) or the input switch control register (ISC). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR1) and Figure 15-20 Format of Input Switch Control Register (ISC) in the RL78/I1A User's Manual.

- **3.** The shared function CMP3P can be assigned to P147 by setting the CMPSEL0 bit in the comparator input switch control register (CMPSEL).

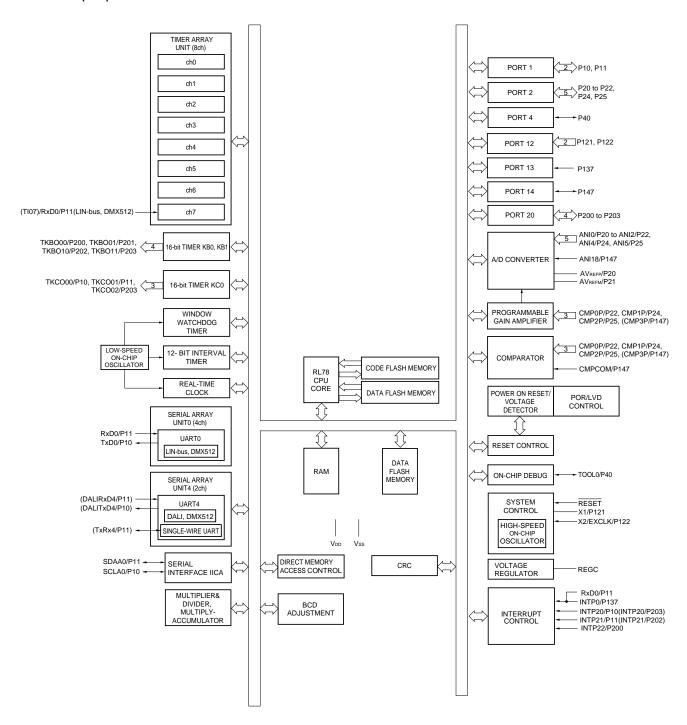

RL78/I1A 1. OUTLINE

### 1.5 Block Diagram

#### 1.5.1 20-pin products

Remarks 1. Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR1) or the input switch control register (ISC). See Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR1) and Figure 15-20 Format of Input Switch Control Register (ISC) in the RL78/I1A User's Manual.

2. The shared function CMP3P can be assigned to P147 by setting the CMPSEL0 bit in the comparator input switch control register (CMPSEL).

RL78/I1A 1. OUTLINE

(3/3)

| Item                          | 20-pin                                                                                 | 30-pin                                                 | 38-pin                 |  |  |

|-------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|--|--|

|                               | R5F1076C                                                                               | R5F107AC, R5F107AE                                     | R5F107DE               |  |  |

| Power-on-reset circuit        | • Power-on-reset: 1. • Power-down-reset: 1.                                            | 51 V (TYP.)<br>50 V (TYP.)                             |                        |  |  |

| Voltage detector              | Rising edge: 2.81 V to 4.06 V (6 stages)     Falling edge: 2.75 V to 3.98 V (6 stages) |                                                        |                        |  |  |

| On-chip debug function        | Provided                                                                               |                                                        |                        |  |  |

| Power supply voltage          | V <sub>DD</sub> = 2.7 to 5.5 V                                                         |                                                        |                        |  |  |

| Operating ambient temperature | $T_A = -40 \text{ to } +105^{\circ}\text{C } (G:$                                      | Industrial applications), $T_A = -40$ to +125°C (M: In | dustrial applications) |  |  |

#### 2. ELECTRICAL SPECIFICATIONS

(G: Industrial applications,  $T_A = -40$  to +105°C)

In this chapter, shows the electrical spesifications of the target products.

Target products (G: Industrial applications):  $T_A = -40 \text{ to} + 105^{\circ}\text{C}$ R5F107xxGxx

- Cautions 1. The RL78/I1A has an on-chip debug function, which is provided for development and evaluation.

Do not use the on-chip debug function in products designated for mass production, because the guaranteed number of rewritable times of the flash memory may be exceeded when this function is used, and product reliability therefore cannot be guaranteed. Renesas Electronics is not liable for problems occurring when the on-chip debug function is used.

- 2. The pins mounted depend on the product. See 2.1 Port Function to 2.2.1 Functions for each product in the RL78/I1A User's Manual.

#### 2.3 DC Characteristics

#### 2.3.1 Pin characteristics

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.7 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Items                  | Symbol       | Conditions                                                             |                                                     | MIN. | TYP. | MAX.                   | Unit |

|------------------------|--------------|------------------------------------------------------------------------|-----------------------------------------------------|------|------|------------------------|------|

| Output current,        | Іон1         | Per pin for P02, P03, P05, P06, P10 to P12,                            | $4.0~V \leq V_{DD} \leq 5.5~V$                      |      |      | -3.0 <sup>Note 2</sup> | mA   |

| high <sup>Note 1</sup> |              | P30, P31, P40, P75 to P77, P120, P147, P200 to P206                    | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$ |      |      | -1.0                   | mA   |

|                        |              | Total of P02, P03, P40, P120                                           | $4.0~V \leq V_{DD} \leq 5.5~V$                      |      |      | -12.0                  | mA   |

|                        |              | (When duty ≤ 70% <sup>Note 3</sup> )                                   | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$ |      |      | -4.0                   | mA   |

|                        |              | Total of P05, P06, P10 to P12, P30, P31,                               | $4.0~V \leq V_{DD} \leq 5.5~V$                      |      |      | -30.0                  | mA   |

|                        |              | P75 to P77, P147, P200 to P206 (When duty $\le 70\%^{\text{Note 3}}$ ) | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$ |      |      | -10.0                  | mA   |

|                        |              | Total of all pins                                                      | $4.0~V \leq V_{DD} \leq 5.5~V$                      |      |      | -30.0                  | mA   |

|                        |              | (When duty ≤ 70% <sup>Note 3</sup> )                                   | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$ |      |      | -14.0                  | mA   |

|                        | <b>І</b> он2 | Per pin for P20 to P22, P24 to P27                                     | $2.7~V \leq V_{DD} \leq 5.5~V$                      |      |      | -0.1 <sup>Note 2</sup> | mA   |

|                        |              | Total of all pins (When duty $\leq 70\%^{\text{Note 3}}$ )             | $2.7~V \leq V_{DD} \leq 5.5~V$                      |      |      | -0.7                   | mA   |

- **Notes 1.** Value of current at which the device operation is guaranteed even if the current flows from the V<sub>DD</sub> pin to an output pin.

- 2. However, do not exceed the total current value.

- **3.** Specification under conditions where the duty factor  $\leq 70\%$ .

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

- Total output current of pins = (IoH × 0.7)/(n × 0.01)

- <Example> Where n = 80% and IoH = -10.0 mA

Total output current of pins =  $(-10.0 \times 0.7)/(80 \times 0.01) \cong -8.7$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

#### Caution P02, P10 to P12 do not output high level in N-ch open-drain mode.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

- Notes 1. Current flowing to the VDD.

- 2. When the high-speed on-chip oscillator and high-speed system clock are stopped.

- 3. Current flowing only to the real-time clock (RTC) (excluding the operating current of the low-speed onchip oscillator and the XT1 oscillator). The supply current of the RL78 microcontrollers is the sum of the values of either IDD1 or IDD2, and IRTC, when the real-time clock operates in operation mode or HALT mode. When the low-speed on-chip oscillator is selected, IFIL should be added. IDD2 subsystem clock operation includes the operational current of the real-time clock.

- **4.** Current flowing only to the 12-bit interval timer (excluding the operating current of the XT1 oscillator and f<sub>IL</sub> operating current). The current of the RL78 microcontrollers is the sum of the values of either I<sub>DD1</sub> or I<sub>DD2</sub>, and I<sub>IT</sub>, when the 12-bit interval timer operates in operation mode or HALT mode.

- **5.** Current flowing only to the watchdog timer (including the operating current of the low-speed on-chip oscillator). The supply current of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and IWDT when the watchdog timer is in operation.

- **6.** Current flowing only to the A/D converter. The supply current of the RL78 microcontrollers is the sum of IDD1 or IDD2 and IADC when the A/D converter operates in an operation mode or the HALT mode.

- 7. Current flowing only to the LVD circuit. The supply current of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3 and ILVD when the LVD circuit is in operation.

- **8.** Current flowing during self-programming operation.

- **9.** Current flowing only to the programmable gain amplifier. The supply current value of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3, and IPGA, when the programmable gain amplifier is operating in operating mode or in HALT mode.

- **10.** Current flowing only to the comparator. The supply current value of the RL78 microcontrollers is the sum of IDD1, IDD2 or IDD3, and ICMP, when the comparator is operating.

- **11.** This is the current required to flow to V<sub>DD</sub> pin of the current circuit that is used as the programmable gain amplifier and the comparator.

- 12. Current flowing only during data flash rewrite.

- 13. See 21.3.3 SNOOZE mode in the RL78/I1A User's Manual for shift time to the SNOOZE mode .

- Remarks 1. fil: Low-speed on-chip oscillator clock frequency

- 2. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- 3. fclk: CPU/peripheral hardware clock frequency

- **4.** Temperature condition of the TYP. value is T<sub>A</sub> = 25°C

- 5. Example of calculating current value when using programmable gain amplifier and comparator.

- Examples 1) TYP. operating current value when three comparator channels, one internal reference voltage generator, and PGA are operating (when AVREFP = VDD = 5.0 V)

```

ICMP × 3 + IVREF + IPGA + IREF

= 41.4 [\mu A] × 3 + 14.8 [\mu A] × 1 + 210 [\mu A] + 3.2 [\mu A]

= 352.2 [\mu A]

```

Examples 2) TYP. operating current value when using two comparator channels, without using internal reference voltage generator (when AVREFP = VDD = 5.0 V)

```

ICMP × 2 + IIREF

= 41.4 [\mu A] × 2 + 3.2 [\mu A]

= 86.0 [\mu A]

```

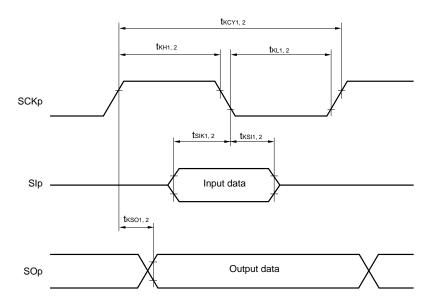

# (2) During communication at same potential (CSI mode) (master mode, SCKp... internal clock output) $(T_A = -40 \text{ to } +105^{\circ}\text{C}^{\text{Note } 5}, 2.7 \text{ V} \leq \text{V}_{\text{DD}} \leq 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                             | Symbol        | Conditions                     | HS (high-s <sub>l</sub> | ,    | LS (low-sp   | Unit |    |

|-------------------------------------------------------|---------------|--------------------------------|-------------------------|------|--------------|------|----|

|                                                       |               |                                | MIN.                    | MAX. | MIN.         | MAX. |    |

| SCKp cycle time                                       | <b>t</b> KCY1 | tkcy1 ≥ 4/fclk                 | 125                     |      | 500          |      | ns |

| SCKp high-/low-level                                  | <b>t</b> кн1, | $4.0~V \leq V_{DD} \leq 5.5~V$ | tkcy1/2 - 12            |      | tkcy1/2 - 50 |      | ns |

| width                                                 | <b>t</b> KL1  | $2.7~V \leq V_{DD} \leq 5.5~V$ | tkcy1/2 - 18            |      | tkcy1/2 - 50 |      | ns |

| SIp setup time (to SCKp↑)                             | tsıĸı         | $4.0~V \leq V_{DD} \leq 5.5~V$ | 44                      |      | 110          |      | ns |

| Note 1                                                |               | $2.7~V \leq V_{DD} \leq 5.5~V$ | 44                      |      | 110          |      | ns |

| SIp hold time (from SCKp↑) Note 2                     | tksı1         |                                | 19                      |      | 19           |      | ns |

| Delay time from SCKp↓ to SOp output <sup>Note 3</sup> | tkso1         | C = 30 pF <sup>Note 4</sup>    |                         | 25   |              | 25   | ns |

- **Notes 1.** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp setup time becomes "to SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 2. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The SIp hold time becomes "from SCKp↓" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 3. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1. The delay time to SOp output becomes "from SCKp↑" when DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

- 4. C is the load capacitance of the SCKp and SOp output lines.

- **5.** Operating conditions of LS (low-speed main) mode is  $T_A = -40$  to +85 °C.

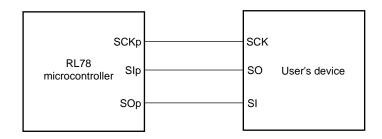

Caution Select the normal input buffer for the SIp pin and the normal output mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg).

Remarks 1. p: CSI number (p = 00), m: Unit number (m = 0), n: Channel number (n = 0), g: PIM and POM number (g = 1)

fmck: Serial array unit operation clock frequency(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number,n: Channel number (mn = 00))

#### CSI mode connection diagram (during communication at same potential)

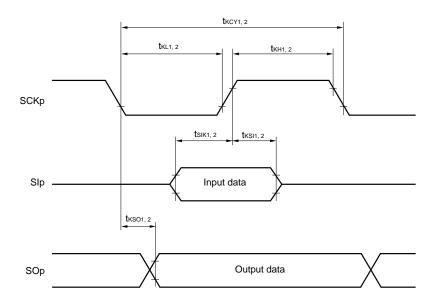

## CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

## CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

**Remarks 1.** p: CSI number (p = 00)

2. m: Unit number, n: Channel number (mn = 00)

(4) When reference voltage (+) = Internal reference voltage (ADREFP1 = 1, ADREFP0 = 0), reference voltage (-) = AVREFM/ANI1 (ADREFM = 1), target pin: ANI0, ANI2, ANI4 to ANI7, ANI16 to ANI19

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.7 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V}, \text{Reference voltage (+)} = V_{BGR}^{Note 3}, \text{Reference voltage (-)} = AV_{REFM} = 0 \text{ V}^{Note 4}, \text{HS (high-speed main) mode)}$

| Parameter                              | Symbol | Conditions       | MIN. | TYP. | MAX.                    | Unit |

|----------------------------------------|--------|------------------|------|------|-------------------------|------|

| Resolution                             | RES    |                  |      | 8    |                         | bit  |

| Conversion time                        | tconv  | 8-bit resolution | 17   |      | 39                      | μS   |

| Zero-scale error <sup>Notes 1, 2</sup> | Ezs    | 8-bit resolution |      |      | ±0.60                   | %FSR |

| Integral linearity error Note 1        | ILE    | 8-bit resolution |      |      | ±2.0                    | LSB  |

| Differential linearity errorNote 1     | DLE    | 8-bit resolution |      |      | ±1.0                    | LSB  |

| Analog input voltage                   | VAIN   |                  | 0    |      | V <sub>BGR</sub> Note 3 | ٧    |

- **Notes 1.** Excludes quantization error ( $\pm 1/2$  LSB).

- 2. This value is indicated as a ratio (%FSR) to the full-scale value.

- 3. See 2.6.2 Temperature sensor/internal reference voltage characteristics.

- **4.** When reference voltage (–) = Vss, the MAX. values are as follows.

Zero-scale error: Add  $\pm 0.35\%$  FSR to the MAX. value when reference voltage (–) = AVREFM.

Integral linearity error: Add  $\pm 0.5$  LSB to the MAX. value when reference voltage (–) = AVREFM.

Differential linearity error: Add  $\pm 0.2$  LSB to the MAX. value when reference voltage (–) = AV<sub>REFM</sub>.

## 2.6.3 Programmable gain amplifier

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.7 \text{ V} \le AV_{REFP} = V_{DD} \le 5.5 \text{ V}, V_{SS} = AV_{REFM} = 0 \text{ V})$

| Parameter                                           | Symbol       |          | Conditions                                          |              | MIN. | TYP. | MAX.                 | Unit                                                |            |              |     |  |      |      |

|-----------------------------------------------------|--------------|----------|-----------------------------------------------------|--------------|------|------|----------------------|-----------------------------------------------------|------------|--------------|-----|--|------|------|

| Input offset voltage                                | VIOPGA       |          |                                                     |              |      | ±5   | ±10                  | mV                                                  |            |              |     |  |      |      |

| Input voltage range                                 | VIPGA        |          |                                                     |              | 0    |      | 0.9V <sub>DD</sub> / | V                                                   |            |              |     |  |      |      |

|                                                     |              |          |                                                     |              |      |      | gain                 |                                                     |            |              |     |  |      |      |

| Gain error <sup>Note 1</sup>                        |              | 4, 8 tim | es                                                  |              |      |      | ±1                   | %                                                   |            |              |     |  |      |      |

|                                                     |              | 16 time  | S                                                   |              |      |      | ±1.5                 | %                                                   |            |              |     |  |      |      |

|                                                     |              | 32 time  | s                                                   |              |      |      | ±2                   | %                                                   |            |              |     |  |      |      |

| Slew rate <sup>Note 1</sup>                         | SRRPGA       | Rising   | $4.0~V \leq V_{DD} \leq 5.5~V$                      | 4, 8 times   | 4    |      |                      | V/μs                                                |            |              |     |  |      |      |

|                                                     |              | edge     | edge                                                | edge         | edge | edge | edge                 | edge                                                |            | 16, 32 times | 1.4 |  |      | V/μs |

|                                                     |              |          |                                                     |              |      |      |                      | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$ | 4, 8 times | 1.8          |     |  | V/μs |      |

|                                                     |              |          |                                                     | 16, 32 times | 0.5  |      |                      | V/μs                                                |            |              |     |  |      |      |

|                                                     | SRFPGA       | Falling  | $4.0~V \leq V_{DD} \leq 5.5~V$                      | 4, 8 times   | 3.2  |      |                      | V/μs                                                |            |              |     |  |      |      |

|                                                     |              | edge     |                                                     | 16, 32 times | 1.4  |      |                      | V/μs                                                |            |              |     |  |      |      |

|                                                     |              |          | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$ | 4, 8 times   | 1.2  |      |                      | V/μs                                                |            |              |     |  |      |      |

|                                                     |              |          |                                                     | 16, 32 times | 0.5  |      |                      | V/μs                                                |            |              |     |  |      |      |

| Operation stabilization wait time <sup>Note 2</sup> | <b>t</b> PGA | 4, 8 tim | es                                                  |              | 5    |      |                      | μS                                                  |            |              |     |  |      |      |

|                                                     |              | 16, 32 t | imes                                                |              | 10   |      |                      | μS                                                  |            |              |     |  |      |      |

**Notes 1.** When  $V_{IPGA} = 0.1V_{DD}/gain$  to  $0.9V_{DD}/gain$ .

2. Time required until a state is entered where the DC and AC specifications of the PGA are satisfied after the PGA operation has been enabled (PGAEN = 1).

Remark These characteristics apply when AVREFM is selected as GND of the PGA by using the CVRVS1 bit.

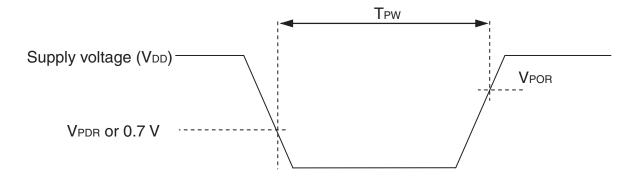

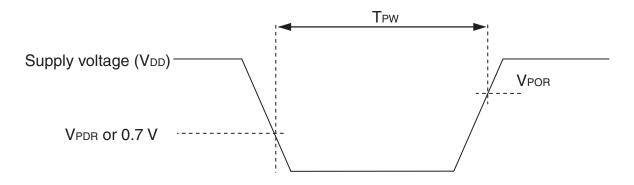

#### 2.6.5 POR circuit characteristics

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, \text{Vss} = 0 \text{ V})$

| Parameter                | Symbol           | Conditions             | MIN. | TYP. | MAX. | Unit |

|--------------------------|------------------|------------------------|------|------|------|------|

| Detection voltage        | V <sub>POR</sub> | Power supply rise time | 1.45 | 1.51 | 1.57 | ٧    |

|                          | V <sub>PDR</sub> | Power supply fall time | 1.44 | 1.50 | 1.56 | V    |

| Minimum pulse width Note | T <sub>PW</sub>  |                        | 300  |      |      | μs   |

**Note** Minimum time required for a POR reset when V<sub>DD</sub> exceeds below V<sub>PDR</sub>. This is also the minimum time required for a POR reset from when V<sub>DD</sub> exceeds below 0.7 V to when V<sub>DD</sub> exceeds V<sub>POR</sub> while STOP mode is entered or the main system clock is stopped through setting bit 0 (HIOSTOP) and bit 7 (MSTOP) in the clock operation status control register (CSC).

#### Absolute Maximum Ratings (T<sub>A</sub> = 25°C) (2/2)

| Parameter            | Symbols          |                     | Conditions                                                                                | Ratings     | Unit |

|----------------------|------------------|---------------------|-------------------------------------------------------------------------------------------|-------------|------|

| Output current, high | Іон1             | Per pin             | P02, P03, P05, P06, P10 to P12,<br>P30, P31, P40, P75 to P77, P120,<br>P147, P200 to P206 | -40         | mA   |

|                      |                  | Total of all pins   | P02, P03, P40, P120                                                                       | -70         | mA   |

|                      |                  | –170 mA             | P05, P06, P10 to P12, P30, P31, P75 to P77, P147, P200 to P206                            | -100        | mA   |

|                      | Iон <sub>2</sub> | Per pin             | P20 to P22, P24 to P27                                                                    | -0.5        | mA   |

|                      |                  | Total of all pins   |                                                                                           | -2          | mA   |

| Output current, low  | lo <sub>L1</sub> | Per pin             | P02, P03, P05, P06, P10 to P12,<br>P30, P31, P40, P75 to P77, P120,<br>P147, P200 to P206 | 40          | mA   |

|                      |                  | Total of all pins   | P02, P03, P40, P120                                                                       | 70          | mA   |

|                      |                  | 170 mA              | P05, P06, P10 to P12, P30, P31, P75 to P77, P147, P200 to P206                            | 100         | mA   |

|                      | lol2             | Per pin             | P20 to P22, P24 to P27                                                                    | 1           | mA   |

|                      |                  | Total of all pins   |                                                                                           | 5           | mA   |

| Operating ambient    | TA               | In normal operation | on mode                                                                                   | -40 to +125 | °C   |

| temperature          |                  | In flash memory p   | programming mode                                                                          | -40 to +105 |      |

| Storage temperature  | Tstg             |                     |                                                                                           | -65 to +150 | °C   |

Caution Product quality may suffer if the absolute maximum rating is exceeded even momentarily for any parameter. That is, the absolute maximum ratings are rated values at which the product is on the verge of suffering physical damage, and therefore the product must be used under conditions that ensure that the absolute maximum ratings are not exceeded.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

$(T_A = -40 \text{ to } +125^{\circ}\text{C}, 2.7 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Items                 | Symbol           | Conditions                                                         |                                                                  | MIN. | TYP. | MAX.                  | Unit |

|-----------------------|------------------|--------------------------------------------------------------------|------------------------------------------------------------------|------|------|-----------------------|------|

| Output current,       | I <sub>OL1</sub> | Per pin for P02, P03, P05, P06,                                    | $4.0~V \leq V_{DD} \leq 5.5~V$                                   |      |      | 8.5 <sup>Note 2</sup> | mA   |

| low <sup>Note 1</sup> |                  | P10 to P12, P30, P31, P40,<br>P75 to P77, P120, P147, P200 to P206 | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$              |      |      | 1.5 <sup>Note 2</sup> | mA   |

|                       |                  | Total of P02, P03, P40, P120                                       | $4.0~V \leq V_{DD} \leq 5.5~V$                                   |      |      | 20.0                  | mA   |

|                       |                  | (When duty ≤ 70% <sup>Note 3</sup> )                               | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$              |      |      | 5.0                   | mA   |

|                       |                  | Total of P05, P06, P10 to P12, P30, P31,                           | $4.0~V \leq V_{DD} \leq 5.5~V$                                   |      |      | 20.0                  | mA   |

|                       |                  | P75 to P77, P147, P200 to P206 (When duty ≤ 70% Note 3)            | 2.7 V ≤ V <sub>DD</sub> < 4.0 V                                  |      |      | 10.0                  | mA   |

|                       |                  | Total of all pins                                                  | $4.0~V \leq V_{DD} \leq 5.5~V$                                   |      |      | 40.0                  | mA   |

|                       |                  | (When duty ≤ 70% <sup>Note 3</sup> )                               | $2.7 \text{ V} \le \text{V}_{DD} \le 4.0 \text{ V}$              |      |      | 15.0                  | mA   |

|                       | lol2             | Per pin for P20 to P22, P24 to P27                                 | $2.7~V \leq V_{DD} \leq 5.5~V$                                   |      |      | 0.4 <sup>Note 2</sup> | mA   |

|                       |                  | Total of all pins (When duty $\leq 70\%^{\text{Note 3}}$ )         | $2.7~\textrm{V} \leq \textrm{V}_\textrm{DD} \leq 5.5~\textrm{V}$ |      |      | 1.6                   | mA   |

- **Notes 1**. Value of current at which the device operation is guaranteed even if the current flows from an output pin to the Vss pin.

- 2. However, do not exceed the total current value.

- **3.** Specification under conditions where the duty factor  $\leq$  70%.

The output current value that has changed to the duty factor > 70% the duty ratio can be calculated with the following expression (when changing the duty factor from 70% to n%).

• Total output current of pins = (IoL × 0.7)/(n × 0.01)

<Example> Where n = 80% and IoL = -10.0 mA

Total output current of pins =  $(-10.0 \times 0.7)/(80 \times 0.01) \approx -8.7$  mA

However, the current that is allowed to flow into one pin does not vary depending on the duty factor. A current higher than the absolute maximum rating must not flow into one pin.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

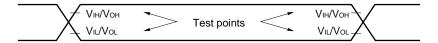

#### 3.5 Peripheral Functions Characteristics

#### **AC Timing Test Points**

## 3.5.1 Serial array unit 0, 4 (UART0, UART1, CSI00, DALI/UART4)

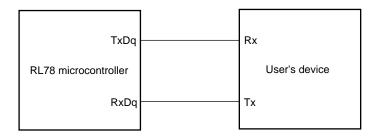

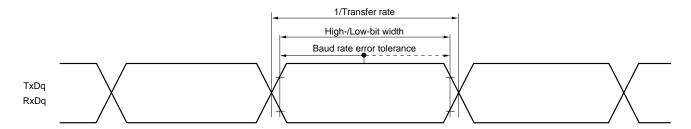

#### (1) During communication at same potential (UART mode)

$(T_A = -40 \text{ to } +125^{\circ}\text{C}, 2.7 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                       | Symbol | Symbol Conditions I |                                                                             | HS (high-speed main)  Mode |        | Unit |

|---------------------------------|--------|---------------------|-----------------------------------------------------------------------------|----------------------------|--------|------|

|                                 |        |                     |                                                                             | MIN.                       | MAX.   |      |

| Transfer rate <sup>Note 1</sup> |        |                     |                                                                             |                            | fмск/6 | bps  |

|                                 |        |                     | Theoretical value of the maximum transfer rate $f_{MCK} = f_{CLK}^{Note 2}$ |                            | 3.3    | Mbps |

- Notes 1. Transfer rate in the SNOOZE mode is 4800 bps only.

- 2. The operating frequencies of the CPU/peripheral hardware clock (fclk) are:

HS (high-speed main) mode: 20 MHz (2.7 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V)

#### **UART** mode connection diagram (during communication at same potential)

#### **UART** mode bit width (during communication at same potential) (reference)

Caution Select the normal input buffer for the RxDq pin and the normal output mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

**Remarks 1.** q: UART number (q = 0, 1), g: PIM and POM number (g = 0, 1)

2. fmck: Serial array unit operation clock frequency(Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number,n: Channel number (mn = 00 to 03))

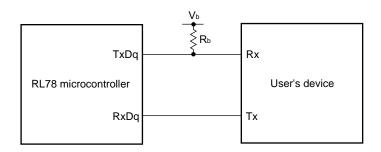

#### **UART** mode connection diagram (during communication at different potential)

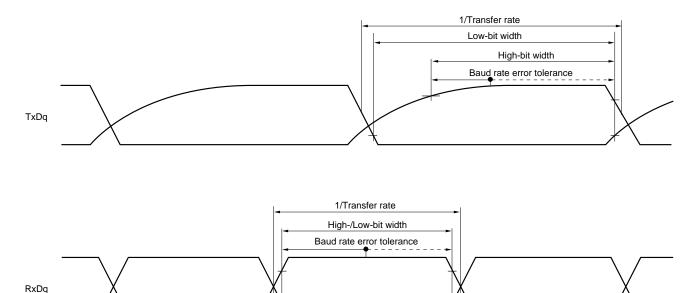

#### UART mode bit width (during communication at different potential) (reference)

Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (VDD tolerance) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg).

**Remarks 1.**  $R_b[\Omega]$ : Communication line (TxDq) pull-up resistance,  $V_b[V]$ : Communication line voltage

**2.** q: UART number (q = 0, 1), g: PIM and POM number (g = 0, 1)

## (5) Communication at different potential (2.5 V, 3 V) (CSI mode) (master mode, SCKp... internal clock output) $(T_A = -40 \text{ to } +125^{\circ}\text{C}, 2.7 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Vss} = 0 \text{ V})$

| Parameter                                             | Symbol            |                                                                                                                                                                | Conditions                                                                                                                                   | HS (high-sp<br>Mod | -    | Unit |

|-------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|------|

|                                                       |                   |                                                                                                                                                                |                                                                                                                                              | MIN.               | MAX. |      |

| SCKp cycle time                                       | tkcy1             | tkcy1 ≥ 4/fclk                                                                                                                                                 | $ \begin{aligned} 4.0 \ V \leq V_{DD} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V, \\ C_b = 30 \ pF, \ R_b = 1.4 \ k\Omega \end{aligned} $ | 600                |      | ns   |

|                                                       |                   |                                                                                                                                                                |                                                                                                                                              | 1000               |      | ns   |

| SCKp high-level width                                 | t <sub>KH1</sub>  | $4.0 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $5.5 \text{ V}, 2.7 \text{ V} \le \text{V}_b \le 4.0 \text{ V},$ $R_b = 1.4 \text{ k}Ω$                                                      | tkcy1/2 - 80       |      | ns   |

|                                                       |                   | $2.7 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $<$ 4.0 V, 2.3 V $\leq$ V <sub>b</sub> $\leq$ 2.7 V, $R_b = 2.7 \text{ k}\Omega$                                                             | tксү1/2 — 170      |      | ns   |

| SCKp low-level width                                  | t <sub>KL1</sub>  | $4.0 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $5.5~V,~2.7~V \leq V_b \leq 4.0~V,$ $R_b = 1.4~k\Omega$                                                                                      | tксү1/2 – 28       |      | ns   |

|                                                       |                   | $2.7 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $\begin{array}{l} <4.0 \text{ V}, \ 2.3 \text{ V} \leq V_b \leq 2.7 \text{ V}, \\ R_b = 2.7 \text{ k}\Omega \end{array}$                     | tксү1/2 – 40       |      | ns   |

| SIp setup time<br>(to SCKp↑) <sup>Note 1</sup>        | tsıĸ1             | $4.0 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $5.5~V,~2.7~V \leq V_b \leq 4.0~V,$ $R_b = 1.4~k\Omega$                                                                                      | 160                |      | ns   |

|                                                       |                   | 2.7 V ≤ V <sub>DD</sub> <<br>C <sub>b</sub> = 30 pF, F                                                                                                         | $<$ 4.0 V, 2.3 V $\leq$ V <sub>b</sub> $\leq$ 2.7 V, $R_b = 2.7 \text{ k}\Omega$                                                             | 250                |      | ns   |

| SIp hold time<br>(from SCKp↑) <sup>Note 1</sup>       | t <sub>KSI1</sub> | $4.0 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $5.5~\text{V},~2.7~\text{V} \leq \text{V}_\text{b} \leq 4.0~\text{V},$ $R_\text{b} = 1.4~\text{k}\Omega$                                     | 40                 |      | ns   |

|                                                       |                   | $ 2.7 \text{ V} \leq \text{V}_{DD} < 4.0 \text{ V}, \ 2.3 \text{ V} \leq \text{V}_b \leq 2.7 \text{ V}, $ $ C_b = 30 \text{ pF}, \ R_b = 2.7 \text{ k}\Omega $ |                                                                                                                                              | 40                 |      | ns   |

| Delay time from SCKp↓ to SOp output <sup>Note 1</sup> | tkso1             | $4.0 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $5.5~V,~2.7~V \leq V_b \leq 4.0~V,$ $R_b = 1.4~k\Omega$                                                                                      |                    | 160  | ns   |

|                                                       |                   | $2.7 \text{ V} \leq \text{V}_{DD} \leq C_b = 30 \text{ pF}, \text{ F}$                                                                                         | $\begin{array}{l} <4.0 \text{ V},  2.3 \text{ V} \leq V_b \leq 2.7 \text{ V}, \\ \\ R_b = 2.7 \text{ k}\Omega \end{array}$                   |                    | 250  | ns   |

| SIp setup time<br>(to SCKp↓) <sup>Note 2</sup>        | tsıĸ1             | $4.0 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $5.5~V,~2.7~V \leq V_b \leq 4.0~V,$ $R_b = 1.4~k\Omega$                                                                                      | 80                 |      | ns   |

|                                                       |                   | 2.7 V ≤ V <sub>DD</sub> <<br>C <sub>b</sub> = 30 pF, F                                                                                                         | $<$ 4.0 V, 2.3 V $\leq$ V <sub>b</sub> $\leq$ 2.7 V, $R_b = 2.7 \text{ k}\Omega$                                                             | 80                 |      | ns   |

| SIp hold time<br>(from SCKp↓) <sup>Note 2</sup>       | tksi1             | $4.0 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $6.5.5~\text{V},~2.7~\text{V} \leq \text{V}_\text{b} \leq 4.0~\text{V},$ $R_\text{b} = 1.4~\text{k}\Omega$                                   | 40                 |      | ns   |

|                                                       |                   | $2.7 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $<$ 4.0 V, 2.3 V $\leq$ V <sub>b</sub> $\leq$ 2.7 V, $<$ R <sub>b</sub> = 2.7 k $\Omega$                                                     | 40                 |      | ns   |

| Delay time from SCKp↑ to SOp output <sup>Note 2</sup> | <b>t</b> KSO1     | $4.0 \text{ V} \le \text{V}_{DD} \le C_b = 30 \text{ pF}, \text{ F}$                                                                                           | $6.5 \text{ V}, 2.7 \text{ V} \leq \text{V}_{\text{b}} \leq 4.0 \text{ V},$ $R_{\text{b}} = 1.4 \text{ k}\Omega$                             |                    | 80   | ns   |

|                                                       |                   | 2.7 V ≤ V <sub>DD</sub> <<br>C <sub>b</sub> = 30 pF, F                                                                                                         | $4.0 \text{ V}, 2.3 \text{ V} \le \text{V}_b \le 2.7 \text{ V},$ $4.0 \text{ R}_b = 2.7 \text{ k}Ω$                                          |                    | 80   | ns   |

Notes 1. When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.

2. When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.

(Caution and Remarks are listed on the next page.)

## 3.6 Analog Characteristics

## 3.6.1 A/D converter characteristics

Classification of A/D converter characteristics

|                                                              |                                                                                       | Reference Voltage                                                                  |                                                                                     |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Input channel                                                | Reference voltage (+) = AV <sub>REFP</sub> Reference voltage (-) = AV <sub>REFM</sub> | Reference voltage (+) = V <sub>DD</sub><br>Reference voltage (-) = V <sub>SS</sub> | Reference voltage (+) = V <sub>BGR</sub> Reference voltage (-) = AV <sub>REFM</sub> |

| ANI0 to ANI2, ANI4 to ANI7                                   | See 3.6.1 (1).                                                                        | See <b>3.6.1 (3)</b> .                                                             | See 3.6.1 (4).                                                                      |

| ANI16 to ANI19                                               | See <b>3.6.1 (2)</b> .                                                                |                                                                                    |                                                                                     |

| Internal reference voltage Temperature sensor output voltage | See 3.6.1 (1).                                                                        |                                                                                    | -                                                                                   |

(2) When reference voltage (+) = AVREFP/ANIO (ADREFP1 = 0, ADREFP0 = 1), reference voltage (-) = AVREFM/ANI1 (ADREFM = 1), target pin: ANI16 to ANI19

(TA = -40 to +125°C, 2.7 V  $\leq$  AVREFP  $\leq$  VDD  $\leq$  5.5 V, Vss = 0 V, Reference voltage (+) = AVREFP, Reference voltage (-) = AVREFM = 0 V)

| Parameter                                      | Symbol                                    | Conditio                                                                          | MIN.                           | TYP.  | MAX. | Unit                                   |      |

|------------------------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------|-------|------|----------------------------------------|------|

| Resolution                                     | RES                                       |                                                                                   |                                | 8     |      | 10                                     | bit  |

| Overall error <sup>Note 1</sup>                | AINL                                      | 10-bit resolution AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>          |                                |       | 1.2  | ±5.0                                   | LSB  |

| Conversion time                                | ersion time tconv 10-bit resolution 3.6 V |                                                                                   | $3.6~V \leq V_{DD} \leq 5.5~V$ | 2.125 |      | 39                                     | μS   |

|                                                |                                           | Target ANI pin : ANI16 to ANI19 $2.7 \text{ V} \le \text{V}_{DD} < 5.5 \text{ V}$ |                                | 3.4   |      | 39                                     | μS   |

| Zero-scale error <sup>Notes 1, 2</sup>         | Ezs                                       | 10-bit resolution AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>          |                                |       |      | ±0.35                                  | %FSR |

| Full-scale error <sup>Notes 1, 2</sup>         | E <sub>FS</sub>                           | 10-bit resolution AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>          |                                |       |      | ±0.35                                  | %FSR |

| Integral linearity error <sup>Note 1</sup>     | ILE                                       | 10-bit resolution AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>          |                                |       |      | ±3.5                                   | LSB  |

| Differential linearity error <sup>Note 1</sup> | DLE                                       | 10-bit resolution AV <sub>REFP</sub> = V <sub>DD</sub> <sup>Note 3</sup>          |                                |       |      | ±2.0                                   | LSB  |

| Analog input voltage                           | Vain                                      | ANI16 to ANI19                                                                    |                                | 0     |      | AV <sub>REFP</sub> and V <sub>DD</sub> | V    |

Notes 1. Excludes quantization error (±1/2 LSB).

- 2. This value is indicated as a ratio (%FSR) to the full-scale value.

- **3.** When  $AV_{REFP} < V_{DD}$ , the MAX. values are as follows.

Overall error: Add  $\pm 4.0$  LSB to the MAX. value when AV<sub>REFP</sub> = V<sub>DD</sub>.

Zero-scale error/Full-scale error: Add  $\pm 0.2\%$  FSR to the MAX. value when AV<sub>REFP</sub> = V<sub>DD</sub>.

Integral linearity error/Differential linearity error: Add ±2.0 LSB to the MAX. value when AVREFP = VDD.

## 3.6.3 Programmable gain amplifier

$(T_A = -40 \text{ to } +125^{\circ}\text{C}, 2.7 \text{ V} \le AV_{REFP} = V_{DD} \le 5.5 \text{ V}, V_{SS} = AV_{REFM} = 0 \text{ V})$

| Parameter                                | Symbol             | Conditions      |                                                            |              | MIN. | TYP.                 | MAX. | Unit |

|------------------------------------------|--------------------|-----------------|------------------------------------------------------------|--------------|------|----------------------|------|------|

| Input offset voltage                     | VIOPGA             |                 |                                                            |              |      | ±5                   | ±10  | mV   |

| Input voltage range                      | VIPGA              |                 |                                                            | 0            |      | 0.9V <sub>DD</sub> / | V    |      |

|                                          |                    |                 |                                                            |              |      |                      | gain |      |

| Gain error <sup>Note 1</sup>             |                    | 4, 8 times      |                                                            |              |      | ±1                   | %    |      |

|                                          |                    | 16 times        |                                                            |              |      |                      | ±1.5 | %    |

|                                          |                    | 32 times        |                                                            |              |      |                      | ±2   | %    |

| Slew rate <sup>Note 1</sup>              | SRRPGA             | Rising edge     | $4.0~\text{V} \leq \text{V}_{\text{DD}} \leq 5.5~\text{V}$ | 4, 8 times   | 4    |                      |      | V/μs |

|                                          |                    |                 |                                                            | 16, 32 times | 1.4  |                      |      | V/μs |

|                                          |                    |                 | 2.7 V ≤ V <sub>DD</sub> < 4.0 V                            | 4, 8 times   | 1.8  |                      |      | V/μs |

|                                          |                    |                 |                                                            | 16, 32 times | 0.5  |                      |      | V/μs |

|                                          | SR <sub>FPGA</sub> | Falling<br>edge | $4.0~\text{V} \leq \text{V}_{\text{DD}} \leq 5.5~\text{V}$ | 4, 8 times   | 3.2  |                      |      | V/μs |

|                                          |                    |                 |                                                            | 16, 32 times | 1.4  |                      |      | V/μs |

|                                          |                    |                 | 2.7 V ≤ V <sub>DD</sub> < 4.0 V                            | 4, 8 times   | 1.2  |                      |      | V/μs |

|                                          |                    |                 |                                                            | 16, 32 times | 0.5  |                      |      | V/μs |

| Operation stabilization wait time Note 2 | <b>t</b> PGA       | 4, 8 times      |                                                            |              | 5    |                      |      | μS   |

|                                          |                    | 16, 32 times    |                                                            |              | 10   |                      |      | μS   |

**Notes 1.** When VIPGA = 0.1VDD/gain to 0.9VDD/gain.

2. Time required until a state is entered where the DC and AC specifications of the PGA are satisfied after the PGA operation has been enabled (PGAEN = 1).

Remark These characteristics apply when AVREFM is selected as GND of the PGA by using the CVRVS1 bit.

#### 3.6.5 POR circuit characteristics

$(T_A = -40 \text{ to } +125^{\circ}\text{C}, \text{Vss} = 0 \text{ V})$

| Parameter                           | Symbol           | Conditions             | MIN. | TYP. | MAX. | Unit |

|-------------------------------------|------------------|------------------------|------|------|------|------|

| Detection voltage                   | V <sub>POR</sub> | Power supply rise time | 1.45 | 1.51 | 1.62 | V    |

|                                     | V <sub>PDR</sub> | Power supply fall time | 1.44 | 1.50 | 1.61 | ٧    |

| Minimum pulse width <sup>Note</sup> | T <sub>PW</sub>  |                        | 300  |      |      | μs   |

**Note** Minimum time required for a POR reset when V<sub>DD</sub> exceeds below V<sub>PDR</sub>. This is also the minimum time required for a POR reset from when V<sub>DD</sub> exceeds below 0.7 V to when V<sub>DD</sub> exceeds V<sub>POR</sub> while STOP mode is entered or the main system clock is stopped through setting bit 0 (HIOSTOP) and bit 7 (MSTOP) in the clock operation status control register (CSC).

#### 3.6.6 LVD circuit characteristics

#### LVD Detection Voltage of Reset Mode and Interrupt Mode

(TA = -40 to +125°C, VPDR  $\leq$  VDD  $\leq$  5.5 V, Vss = 0 V)

|                      | Parameter                                    | Symbol            | Conditions             | MIN. | TYP. | MAX. | Unit |

|----------------------|----------------------------------------------|-------------------|------------------------|------|------|------|------|

| Detection            | ction Supply voltage level V <sub>LVDI</sub> | $V_{\text{LVD0}}$ | Power supply rise time | 3.97 | 4.06 | 4.25 | V    |

| voltage              |                                              |                   | Power supply fall time | 3.89 | 3.98 | 4.15 | V    |

|                      |                                              | V <sub>LVD1</sub> | Power supply rise time | 3.67 | 3.75 | 3.93 | V    |

|                      |                                              |                   | Power supply fall time | 3.59 | 3.67 | 3.83 | V    |

|                      |                                              | V <sub>LVD2</sub> | Power supply rise time | 3.06 | 3.13 | 3.28 | V    |

|                      |                                              |                   | Power supply fall time | 2.99 | 3.06 | 3.20 | V    |

|                      |                                              | V <sub>LVD3</sub> | Power supply rise time | 2.95 | 3.02 | 3.17 | V    |

|                      |                                              |                   | Power supply fall time | 2.89 | 2.96 | 3.09 | V    |

|                      |                                              | V <sub>LVD4</sub> | Power supply rise time | 2.85 | 2.92 | 3.07 | V    |

|                      |                                              |                   | Power supply fall time | 2.79 | 2.86 | 2.99 | V    |

|                      |                                              | V <sub>LVD5</sub> | Power supply rise time | 2.75 | 2.81 | 2.95 | V    |

|                      |                                              |                   | Power supply fall time | 2.70 | 2.75 | 2.88 | V    |

| Minimum pulse width  |                                              | tw                |                        | 300  |      |      | μS   |

| Detection delay time |                                              |                   |                        |      |      | 300  | μs   |