#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                       |

|---------------------------------|------------------------------------------------------------------------------|

| Core Processor                  | ARM926EJ-S                                                                   |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                               |

| Speed                           | 400MHz                                                                       |

| Co-Processors/DSP               | -                                                                            |

| RAM Controllers                 | DDR2, SDRAM, SRAM                                                            |

| Graphics Acceleration           | No                                                                           |

| Display & Interface Controllers | LCD, Touchscreen                                                             |

| Ethernet                        | 10/100Mbps                                                                   |

| SATA                            | -                                                                            |

| USB                             | USB 2.0 (3)                                                                  |

| Voltage - I/O                   | 1.8V, 3.3V                                                                   |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                            |

| Security Features               | -                                                                            |

| Package / Case                  | 217-LFBGA                                                                    |

| Supplier Device Package         | 217-LFBGA (15x15)                                                            |

| Purchase URL                    | https://www.e-xfl.com/product-detail/microchip-technology/at91sam9g35-cu-999 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 10.5.3.3 Enumeration Process

The USB protocol is a master/slave protocol. The host starts the enumeration, sending requests to the device through the control endpoint. The device handles standard requests as defined in the USB Specification.

| Request           | Definition                                            |

|-------------------|-------------------------------------------------------|

| GET_DESCRIPTOR    | Returns the current device configuration value.       |

| SET_ADDRESS       | Sets the device address for all future device access. |

| SET_CONFIGURATION | Sets the device configuration.                        |

| GET_CONFIGURATION | Returns the current device configuration value.       |

| GET_STATUS        | Returns status for the specified recipient.           |

| SET_FEATURE       | Used to set or enable a specific feature.             |

| CLEAR_FEATURE     | Used to clear or disable a specific feature.          |

Table 10-6. Handled Standard Requests

The device also handles some class requests defined in the CDC class.

| Request                | Definition                                                                 |

|------------------------|----------------------------------------------------------------------------|

| SET_LINE_CODING        | Configures DTE rate, stop bits, parity and number of character bits.       |

| GET_LINE_CODING        | Requests current DTE rate, stop bits, parity and number of character bits. |

| SET_CONTROL_LINE_STATE | RS-232 signal used to tell the DCE device the DTE device is now present.   |

Table 10-7. Handled Class Requests

Unhandled requests are STALLed.

#### 10.5.3.4 Communication Endpoints

There are two communication endpoints and endpoint 0 is used for the enumeration process. Endpoint 1 is a 64byte Bulk OUT endpoint and endpoint 2 is a 64-byte Bulk IN endpoint. SAM-BA Boot commands are sent by the host through endpoint 1. If required, the message is split by the host into several data payloads by the host driver. If the command requires a response, the host can send IN transactions to pick up the response.

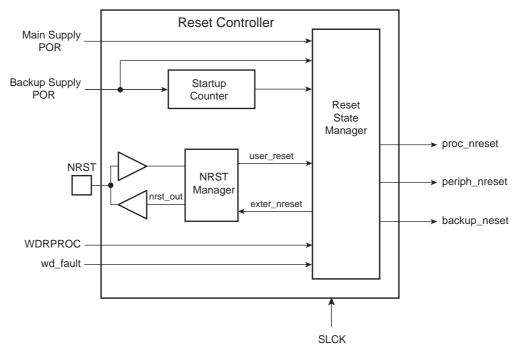

# 13. Reset Controller (RSTC)

# 13.1 Description

The Reset Controller (RSTC), based on power-on reset cells, handles all the resets of the system without any external components. It reports which reset occurred last.

The Reset Controller also drives independently or simultaneously the external reset and the peripheral and processor resets.

# **13.2 Embedded Characteristics**

- Manages All Resets of the System, Including

- External Devices Through the NRST Pin

- Processor Reset

- Peripheral Set Reset

- Backed-up Peripheral Reset

- Based on 2 Embedded Power-on Reset Cells

- Reset Source Status

- Status of the Last Reset

- Either General Reset, Wake-up Reset, Software Reset, User Reset, Watchdog Reset

- External Reset Signal Shaping

# 13.3 Block Diagram

Atmel

# 21.16 Register Write Protection

To prevent any single software error from corrupting PMC behavior, certain registers in the address space can be write-protected by setting the WPEN bit in the PMC Write Protection Mode Register (PMC\_WPMR).

If a write access to a write-protected register is detected, the WPVS bit in the PMC Write Protection Status Register (PMC\_WPSR) is set and the field WPVSRC indicates the register in which the write access has been attempted.

The WPVS bit is automatically cleared after reading the PMC\_WPSR.

The following registers can be write-protected:

- PMC System Clock Enable Register

- PMC System Clock Disable Register

- PMC Clock Generator Main Clock Frequency Register

- PMC Clock Generator PLLA Register

- PMC Master Clock Register

- PMC USB Clock Register

- PMC Programmable Clock Register

- PLL Charge Pump Current Register

# 21.17.2 PMC System Clock Disable Register

| Name:<br>Address: | PMC_SCDR<br>0xFFFFFC04 |    |       |         |       |           |           |

|-------------------|------------------------|----|-------|---------|-------|-----------|-----------|

| Access:           | Write-only             |    |       |         |       |           |           |

| 31                | 30                     | 29 | 28    | 27      | 26    | 25        | 24        |

| —                 | -                      | _  | -     | _       | _     | _         | —         |

| 23                | 22                     | 21 | 20    | 19<br>— | 18    | 17        | 16        |

| 15                | 14                     | 13 | 12    | 11      | 10    | 9<br>PCK1 | 8<br>PCK0 |

| 7                 | 6                      | 5  |       | 3       | 2     | 1         | 0         |

| UDP               | UHP                    | -  | SMDCK | LCDCK   | DDRCK | -         | PCK       |

This register can only be written if the WPEN bit is cleared in the PMC Write Protection Mode Register.

#### • PCK: Processor Clock Disable

0: No effect.

1: Disables the Processor clock. This is used to enter the processor in Idle mode.

#### • DDRCK: DDR Clock Disable

0: No effect.

1: Disables the DDR clock.

#### • LCDCK: MCK2x Clock Disable

0: No effect.

1: Disables the MCK2x clock.

#### • SMDCK: SMD Clock Disable

0: No effect.

1: Disables the soft modem clock.

#### • UHP: USB Host OHCI Clock Disable

0: No effect.

1: Disables the UHP48M and UHP12M OHCI clocks.

## • UDP: USB Device Clock Enable

0: No effect.

1: Disables the USB Device clock.

#### • PCKx: Programmable Clock x Output Disable

- 0: No effect.

- 1: Disables the corresponding Programmable Clock output.

# 21.17.13 PMC SMD Clock Register

| Name:    | PMC_SMD    |    |        |    |    |    |      |  |  |  |

|----------|------------|----|--------|----|----|----|------|--|--|--|

| Address: | 0xFFFFC3C  |    |        |    |    |    |      |  |  |  |

| Access:  | Read/Write |    |        |    |    |    |      |  |  |  |

| 31       | 30         | 29 | 28     | 27 | 26 | 25 | 24   |  |  |  |

| _        | -          | _  | -      | -  | -  | _  | -    |  |  |  |

|          |            |    |        |    |    |    |      |  |  |  |

| 23       | 22         | 21 | 20     | 19 | 18 | 17 | 16   |  |  |  |

| _        | -          | Ι  | -      | -  | -  | Ι  | —    |  |  |  |

|          | -          | -  | -      | -  |    | -  |      |  |  |  |

| 15       | 14         | 13 | 12     | 11 | 10 | 9  | 8    |  |  |  |

| -        | -          | -  | SMDDIV |    |    |    |      |  |  |  |

|          |            |    |        |    |    |    |      |  |  |  |

| 7        | 6          | 5  | 4      | 3  | 2  | 1  | 0    |  |  |  |

| _        | -          | —  | —      | —  | —  | —  | SMDS |  |  |  |

# SMDS: SMD Input Clock Selection

0: SMD clock input is PLLA.

1: SMD clock input is UPLL.

#### • SMDDIV: Divider for SMD Clock

SMD clock is input clock divided by SMD + 1.

## 22.6.38 PIO Additional Interrupt Modes Mask Register

| Name:    | PIO_AIMMR     |               |                |               |               |           |     |

|----------|---------------|---------------|----------------|---------------|---------------|-----------|-----|

| Address: | 0xFFFFF4B8 (P | IOA), 0xFFFFF | 6B8 (PIOB), 0x | FFFFF8B8 (PIC | DC), 0xFFFFFA | B8 (PIOD) |     |

| Access:  | Read-only     |               |                |               |               |           |     |

| 31       | 30            | 29            | 28             | 27            | 26            | 25        | 24  |

| P31      | P30           | P29           | P28            | P27           | P26           | P25       | P24 |

| 23       | 22            | 21            | 20             | 19            | 18            | 17        | 16  |

| P23      | P22           | P21           | P20            | P19           | P18           | P17       | P16 |

| 15       | 14            | 13            | 12             | 11            | 10            | 9         | 8   |

| P15      | P14           | P13           | P12            | P11           | P10           | P9        | P8  |

| 7        | 6             | 5             | 4              | 3             | 2             | 1         | 0   |

| P7       | P6            | P5            | P4             | P3            | P2            | P1        | P0  |

## • P0-P31: IO Line Index

Selects the IO event type triggering an interrupt.

0: The interrupt source is a both-edge detection event.

1: The interrupt source is described by the registers PIO\_ELSR and PIO\_FRLHSR.

Atmel

- If no bank is validated yet, the default DATA0 ZLP is answered and underflow is flagged (ERR\_FL\_ISO is set in UDPHS\_EPTSTAx). Then, no data bank is flushed at microframe end.

- If no data bank has been validated at the time when a response should be made for the second transaction

of NB\_TRANS = 3 transactions microframe, a DATA1 ZLP is answered and underflow is flagged

(ERR\_FL\_ISO is set in UDPHS\_EPTSTAx). If and only if remaining untransmitted banks for that microframe

are available at its end, they are flushed and an error condition is flagged (ERR\_FLUSH is set in

UDPHS\_EPTSTAx).

- If no data bank has been validated at the time when a response should be made for the last programmed transaction of a microframe, a DATA0 ZLP is answered and underflow is flagged (ERR\_FL\_ISO is set in UDPHS\_EPTSTAx). If and only if the remaining untransmitted data bank for that microframe is available at its end, it is flushed and an error condition is flagged (ERR\_FLUSH is set in UDPHS\_EPTSTAx).

- If at the end of a microframe no valid token IN has been recognized, no data bank is flushed and no error condition is reported.

At the end of a microframe in which at least one data bank has been transmitted, if less than NB\_TRANS banks have been validated for that microframe, an error condition is flagged (ERR\_TRANS is set in UDPHS\_EPTSTAx).

Cases of Error (in UDPHS\_EPTSTAx)

- ERR\_FL\_ISO: There was no data to transmit inside a microframe, so a ZLP is answered by default.

- ERR\_FLUSH: At least one packet has been sent inside the microframe, but the number of token IN received is lesser than the number of transactions actually validated (TXRDY\_TRER) and likewise with the NB\_TRANS programmed.

- ERR\_TRANS: At least one packet has been sent inside the microframe, but the number of token IN received is lesser than the number of programmed NB\_TRANS transactions and the packets not requested were not validated.

- ERR\_FL\_ISO + ERR\_FLUSH: At least one packet has been sent inside the microframe, but the data has not been validated in time to answer one of the following token IN.

- ERR\_FL\_ISO + ERR\_TRANS: At least one packet has been sent inside the microframe, but the data has not been validated in time to answer one of the following token IN and the data can be discarded at the microframe end.

- ERR\_FLUSH + ERR\_TRANS: The first token IN has been answered and it was the only one received, a second bank has been validated but not the third, whereas NB\_TRANS was waiting for three transactions.

- ERR\_FL\_ISO + ERR\_FLUSH + ERR\_TRANS: The first token IN has been treated, the data for the second Token IN was not available in time, but the second bank has been validated before the end of the microframe. The third bank has not been validated, but three transactions have been set in NB\_TRANS.

#### 31.6.10.4 Data OUT

#### Bulk OUT or Interrupt OUT

Like data IN, data OUT packets are sent by the host during the data or the status stage of control transfer or during an interrupt/bulk/isochronous OUT transfer. Data buffers are sent packet by packet under the control of the application or under the control of the DMA channel.

# Bulk OUT or Interrupt OUT: Receiving a Packet Under Application Control (Host to Device)

Algorithm Description for Each Packet:

- The application enables an interrupt on RXRDY\_TXKL.

- When an interrupt on RXRDY\_TXKL is received, the application knows that UDPHS\_EPTSTAx register BYTE\_COUNT bytes have been received.

- The application reads the BYTE\_COUNT bytes from the endpoint.

- The application clears RXRDY\_TXKL.

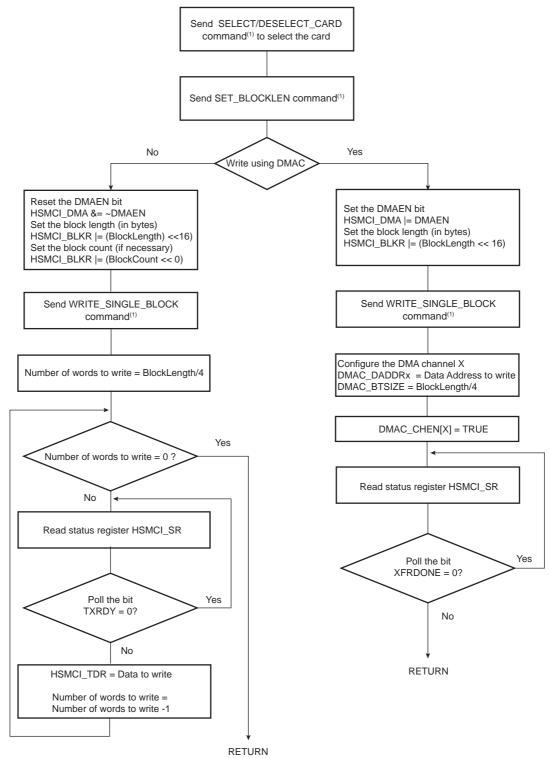

If set, the bit DMAEN in the HSMCI DMA Condiguration Register (HSMCI\_DMA) enables DMA transfer.

The flowchart in Figure 33-9 shows how to write a single block with or without use of DMA facilities. Polling or interrupt method can be used to wait for the end of write according to the contents of the HSMCI Interrupt Mask Register (HSMCI\_IMR).

## 34.8.8 SPI Interrupt Mask Register

| Name:    | SPI_IMR       |               |     |       |       |         |      |

|----------|---------------|---------------|-----|-------|-------|---------|------|

| Address: | 0xF000001C (0 | ), 0xF000401C | (1) |       |       |         |      |

| Access:  | Read-only     |               |     |       |       |         |      |

| 31       | 30            | 29            | 28  | 27    | 26    | 25      | 24   |

| _        | —             | —             | —   | —     | —     | -       | -    |

| 23       | 22            | 21            | 20  | 19    | 18    | 17      | 16   |

| _        | _             | -             | -   | -     | —     | -       | -    |

| 15       | 14            | 13            | 12  | 11    | 10    | 9       | 8    |

| _        | _             | -             | _   | _     | UNDES | TXEMPTY | NSSR |

| 7        | 6             | 5             | 4   | 3     | 2     | 1       | 0    |

| _        | -             | -             | _   | OVRES | MODF  | TDRE    | RDRF |

The following configuration values are valid for all listed bit names of this register:

0: The corresponding interrupt is not enabled.

1: The corresponding interrupt is enabled.

RDRF: Receive Data Register Full Interrupt Mask

- TDRE: SPI Transmit Data Register Empty Interrupt Mask

- MODF: Mode Fault Error Interrupt Mask

- OVRES: Overrun Error Interrupt Mask

- NSSR: NSS Rising Interrupt Mask

- TXEMPTY: Transmission Registers Empty Mask

- UNDES: Underrun Error Interrupt Mask

# 34.8.10 SPI Write Protection Mode Register

| Name:               | SPI_WPMR                       |    |    |      |  |  |  |  |  |

|---------------------|--------------------------------|----|----|------|--|--|--|--|--|

| Address:            | 0xF00000E4 (0), 0xF00040E4 (1) |    |    |      |  |  |  |  |  |

| Access: Read/Write. |                                |    |    |      |  |  |  |  |  |

| 31                  | 30                             | 29 | 28 | 27   |  |  |  |  |  |

|                     |                                |    | WF | PKEY |  |  |  |  |  |

| 23                  | 22                             | 21 | 20 | 19   |  |  |  |  |  |

|                     |                                |    | WF | PKEY |  |  |  |  |  |

| 23 | 22    | 21 | 20 | 19  | 18 | 17 | 16   |  |  |  |  |

|----|-------|----|----|-----|----|----|------|--|--|--|--|

|    | WPKEY |    |    |     |    |    |      |  |  |  |  |

| 15 | 14    | 13 | 12 | 11  | 10 | 9  | 8    |  |  |  |  |

|    |       |    | WP | KEY |    |    |      |  |  |  |  |

| 7  | 6     | 5  | 4  | 3   | 2  | 1  | 0    |  |  |  |  |

| -  | _     | _  | _  | _   | _  | _  | WPEN |  |  |  |  |

#### • WPEN: Write Protection Enable

0: Disables the write protection if WPKEY corresponds to 0x535049 ("SPI" in ASCII)

1: Enables the write protection if WPKEY corresponds to 0x535049 ("SPI" in ASCII)

See Section 34.7.5 "Register Write Protection" for the list of registers that can be write-protected.

#### • WPKEY: Write Protection Key

| Value        | Name   | Description                                                                       |

|--------------|--------|-----------------------------------------------------------------------------------|

| 0.525040     | PASSWD | Writing any other value in this field aborts the write operation of the WPEN bit. |

| 0x535049 PAS | FASSWD | Always reads as 0.                                                                |

25

24

26

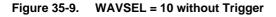

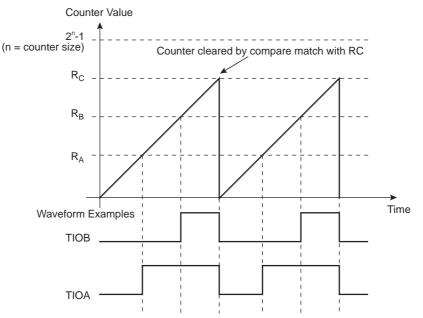

#### 35.6.11.2 WAVSEL = 10

When WAVSEL = 10, the value of TC\_CV is incremented from 0 to the value of RC, then automatically reset on a RC Compare. Once the value of TC\_CV has been reset, it is then incremented and so on. See Figure 35-9.

It is important to note that TC\_CV can be reset at any time by an external event or a software trigger if both are programmed correctly. See Figure 35-10.

In addition, RC Compare can stop the counter clock (CPCSTOP = 1 in TC\_CMR) and/or disable the counter clock (CPCDIS = 1 in TC\_CMR).

## 35.7.11 TC Interrupt Disable Register

Name: TC\_IDRx [x=0..2]

Address: 0xF8008028 (0)[0], 0xF8008068 (0)[1], 0xF80080A8 (0)[2], 0xF800C028 (1)[0], 0xF800C068 (1)[1], 0xF800C0A8 (1)[2]

# Access: Write-only

| 31    | 30    | 29    | 28   | 27   | 26   | 25    | 24    |

|-------|-------|-------|------|------|------|-------|-------|

| -     | -     | —     | —    | —    | -    | -     | -     |

| 23    | 22    | 21    | 20   | 19   | 18   | 17    | 16    |

| -     | -     | -     | -    | -    | -    | -     | -     |

| 15    | 14    | 13    | 12   | 11   | 10   | 9     | 8     |

| -     | -     | -     | -    | —    | -    | -     | -     |

| 7     | 6     | 5     | 4    | 3    | 2    | 1     | 0     |

| ETRGS | LDRBS | LDRAS | CPCS | CPBS | CPAS | LOVRS | COVFS |

#### COVFS: Counter Overflow

0: No effect.

1: Disables the Counter Overflow Interrupt.

#### • LOVRS: Load Overrun

0: No effect.

1: Disables the Load Overrun Interrupt (if TC\_CMRx.WAVE = 0).

#### • CPAS: RA Compare

0: No effect.

1: Disables the RA Compare Interrupt (if TC\_CMRx.WAVE = 1).

#### • CPBS: RB Compare

0: No effect.

1: Disables the RB Compare Interrupt (if TC\_CMRx.WAVE = 1).

#### • CPCS: RC Compare

0: No effect.

1: Disables the RC Compare Interrupt.

# • LDRAS: RA Loading

0: No effect.

1: Disables the RA Load Interrupt (if TC\_CMRx.WAVE = 0).

#### • LDRBS: RB Loading

0: No effect.

1: Disables the RB Load Interrupt (if TC\_CMRx.WAVE = 0).

Atmel

## 36.7.4 PWM Status Register

| Name:<br>Address: | PWM_SR<br>0xF803400C |    |    |         |         |       |         |

|-------------------|----------------------|----|----|---------|---------|-------|---------|

| Access:           | Read-only            |    |    |         |         |       |         |

| 31                | 30                   | 29 | 28 | 27      | 26      | 25    | 24      |

| _                 | _                    | _  | —  | _       | _       | _     | _       |

| 23                | 22                   | 21 | 20 | 19<br>— | 18<br>- | 17    | 16<br>- |

| 15                | 14                   | 13 | 12 | 11      | 10      | 9     | 8       |

| -                 | -                    | —  | -  | -       | -       | -     | -       |

| 7                 | 6                    | 5  | 4  | 3       | 2       | 1     | 0       |

| -                 | -                    | _  | _  | CHID3   | CHID2   | CHID1 | CHID0   |

#### • CHIDx: Channel ID

0 = PWM output for channel x is disabled.

1 = PWM output for channel x is enabled.

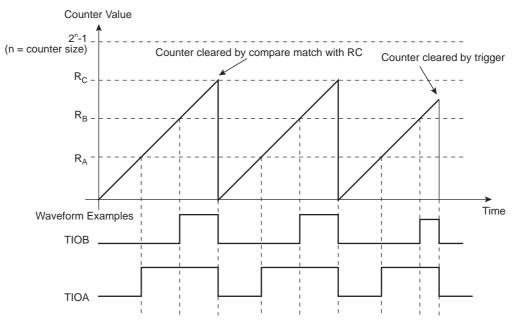

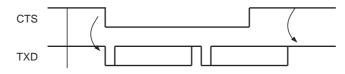

Figure 38-27. Receiver Behavior when Operating with Hardware Handshaking

Figure 38-28 shows how the transmitter operates if hardware handshaking is enabled. The CTS pin disables the transmitter. If a character is being processed, the transmitter is disabled only after the completion of the current character and transmission of the next character happens as soon as the pin CTS falls.

Figure 38-28. Transmitter Behavior when Operating with Hardware Handshaking

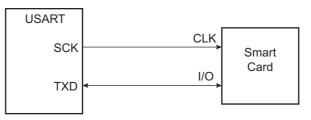

#### 38.6.4 ISO7816 Mode

The USART features an ISO7816-compatible operating mode. This mode permits interfacing with smart cards and Security Access Modules (SAM) communicating through an ISO7816 link. Both T = 0 and T = 1 protocols defined by the ISO7816 specification are supported.

Setting the USART in ISO7816 mode is performed by writing the USART\_MODE field in US\_MR to the value 0x4 for protocol T = 0 and to the value 0x5 for protocol T = 1.

#### 38.6.4.1 ISO7816 Mode Overview

The ISO7816 is a half duplex communication on only one bidirectional line. The baud rate is determined by a division of the clock provided to the remote device (see Section 38-2 "Baud Rate Generator").

The USART connects to a smart card as shown in Figure 38-29. The TXD line becomes bidirectional and the baud rate generator feeds the ISO7816 clock on the SCK pin. As the TXD pin becomes bidirectional, its output remains driven by the output of the transmitter but only when the transmitter is active while its input is directed to the input of the receiver. The USART is considered as the master of the communication as it generates the clock.

#### Figure 38-29. Connection of a Smart Card to the USART

When operating in ISO7816, either in T = 0 or T = 1 modes, the character format is fixed. The configuration is 8 data bits, even parity and 1 or 2 stop bits, regardless of the values programmed in the CHRL, MODE9, PAR and CHMODE fields. MSBF can be used to transmit LSB or MSB first. Parity Bit (PAR) can be used to transmit in normal or inverse mode. Refer to Section 38.7.3 "USART Mode Register" and "PAR: Parity Type".

NACT(slave1)=PUBLISH

NACT(slave2)=SUBSCRIBE

Data transfer from the slave2 to the master and to the slave1: NACT(master)=SUBSCRIBE NACT(slave1)=SUBSCRIBE NACT(slave2)=PUBLISH

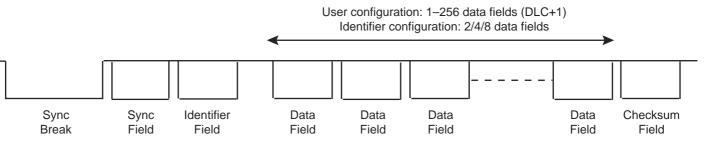

## 38.6.8.11 Response Data Length

The LIN response data length is the number of data fields (bytes) of the response excluding the checksum.

The response data length can either be configured by the user or be defined automatically by bits 4 and 5 of the Identifier (compatibility to LIN Specification 1.1). The user can choose between these two modes by the DLM bit of US\_LINMR:

- DLM = 0: The response data length is configured by the user via the DLC field of US\_LINMR. The response data length is equal to (DLC + 1) bytes. DLC can be programmed from 0 to 255, so the response can contain from 1 data byte up to 256 data bytes.

- DLM = 1: The response data length is defined by the Identifier (IDCHR in US\_LINIR) according to the table below. The DLC field of US\_LINMR is discarded. The response can contain 2 or 4 or 8 data bytes.

| IDCHR[5] | IDCHR[4] | Response Data Length [Bytes] |

|----------|----------|------------------------------|

| 0        | 0        | 2                            |

| 0        | 1        | 2                            |

| 1        | 0        | 4                            |

| 1        | 1        | 8                            |

#### Table 38-14. Response Data Length if DLM = 1

#### Figure 38-43. Response Data Length

#### 38.6.8.12 Checksum

The last field of a frame is the checksum. The checksum contains the inverted 8-bit sum with carry, over all data bytes or all data bytes and the protected identifier. Checksum calculation over the data bytes only is called classic checksum and it is used for communication with LIN 1.3 slaves. Checksum calculation over the data bytes and the protected identifier byte is called enhanced checksum and it is used for communication with LIN 2.0 slaves.

The USART can be configured to:

- Send/Check an Enhanced checksum automatically (CHKDIS = 0 & CHKTYP = 0)

- Send/Check a Classic checksum automatically (CHKDIS = 0 & CHKTYP = 1)

- Not send/check a checksum (CHKDIS = 1)

This configuration is made by the Checksum Type (CHKTYP) and Checksum Disable (CHKDIS) fields of US\_LINMR.

# 38.7.9 USART Interrupt Disable Register (SPI\_MODE)

Name: US\_IDR (SPI\_MODE)

Address: 0xF801C00C (0), 0xF802000C (1), 0xF802400C (2)

Access: Write-only

| 31 | 30 | 29   | 28 | 27   | 26   | 25      | 24    |

|----|----|------|----|------|------|---------|-------|

| _  | _  | -    | -  | _    | -    | _       | -     |

| 23 | 22 | 21   | 20 | 19   | 18   | 17      | 16    |

| -  | -  | -    | -  | NSSE | —    | -       | -     |

|    | -  | -    | -  | -    | -    | -       | -     |

| 15 | 14 | 13   | 12 | 11   | 10   | 9       | 8     |

| _  | -  | _    | —  | _    | UNRE | TXEMPTY | —     |

|    |    |      |    |      |      |         |       |

| 7  | 6  | 5    | 4  | 3    | 2    | 1       | 0     |

| _  | _  | OVRE | —  | _    | —    | TXRDY   | RXRDY |

This configuration is relevant only if USART\_MODE = 0xE or 0xF in the USART Mode Register.

The following configuration values are valid for all listed bit names of this register:

0: No effect

- 1: Disables the corresponding interrupt.

- RXRDY: RXRDY Interrupt Disable

- TXRDY: TXRDY Interrupt Disable

- OVRE: Overrun Error Interrupt Disable

- TXEMPTY: TXEMPTY Interrupt Disable

- UNRE: SPI Underrun Error Interrupt Disable

- NSSE: NSS Line (Driving CTS Pin) Rising or Falling Edge Event Interrupt Disable

# 38.7.19 USART Baud Rate Generator Register

| Name:    | US_BRGR                                        |    |    |    |    |    |    |  |

|----------|------------------------------------------------|----|----|----|----|----|----|--|

| Address: | 0xF801C020 (0), 0xF8020020 (1), 0xF8024020 (2) |    |    |    |    |    |    |  |

| Access:  | Read/Write                                     |    |    |    |    |    |    |  |

| 31       | 30                                             | 29 | 28 | 27 | 26 | 25 | 24 |  |

| -        | -                                              | -  | -  | _  | -  | _  | -  |  |

| 23       | 22                                             | 21 | 20 | 19 | 18 | 17 | 16 |  |

| _        | – – – – FP                                     |    |    |    |    |    |    |  |

| 15       | 14                                             | 13 | 12 | 11 | 10 | 9  | 8  |  |

|          | CD                                             |    |    |    |    |    |    |  |

| 7        | 6                                              | 5  | 4  | 3  | 2  | 1  | 0  |  |

|          |                                                |    | С  | D  |    |    |    |  |

This register can only be written if the WPEN bit is cleared in the USART Write Protection Mode Register.

## • CD: Clock Divider

|            | SYN                                              | C = 0                                    | SYNC = 1                                    |                                                       |  |  |  |

|------------|--------------------------------------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|--|--|--|

| CD         | OVER = 0                                         | OVER = 1                                 | or<br>USART_MODE = SPI<br>(Master or Slave) | USART_MODE = ISO7816                                  |  |  |  |

| 0          | Baud Rate Clock Disabled                         |                                          |                                             |                                                       |  |  |  |

| 1 to 65535 | CD = Selected Clock /<br>(16 $\times$ Baud Rate) | CD = Selected Clock /<br>(8 × Baud Rate) | CD = Selected Clock /<br>Baud Rate          | CD = Selected Clock /<br>(FI_DI_RATIO × Baud<br>Rate) |  |  |  |

# • FP: Fractional Part

0: Fractional divider is disabled.

1–7: Baud rate resolution, defined by FP  $\times$  1/8.

block then ceases sending data to memory. At the end of frame reception, the receive block indicates to the DMA block whether the frame is good or bad. The DMA block recovers the current receive buffer if the frame was bad. The receive block signals the register block to increment the alignment error, the CRC (FCS) error, the short frame, long frame, jabber error, the receive symbol error statistics and the length field mismatch statistics.

The enable bit for jumbo frames in the EMAC\_NCFGR allows the EMAC to receive jumbo frames of up to 10240 bytes in size. This operation does not form part of the IEEE802.3 specification and is disabled by default. When jumbo frames are enabled, frames received with a frame size greater than 10240 bytes are discarded.

## 43.4.6 Address Checking Block

The address checking (or filter) block indicates to the DMA block which receive frames should be copied to memory. Whether a frame is copied depends on what is enabled in the EMAC\_NCFGR, the state of the external match pin, the contents of the specific address and hash registers and the frame's destination address. In this implementation of the EMAC, the frame's source address is not checked. Provided that bit 18 of the EMAC\_NCFGR is not set, a frame is not copied to memory if the EMAC is transmitting in half duplex mode at the time a destination address is received. If bit 18 of the EMAC\_NCFGR is set, frames can be received while transmitting in half-duplex mode.

Ethernet frames are transmitted a byte at a time, least significant bit first. The first six bytes (48 bits) of an Ethernet frame make up the destination address. The first bit of the destination address, the LSB of the first byte of the frame, is the group/individual bit: this is *One* for multicast addresses and *Zero* for unicast. The *All Ones* address is the broadcast address, and a special case of multicast.

The EMAC supports recognition of four specific addresses. Each specific address requires two registers, specific address register bottom and specific address register top. Specific address register bottom stores the first four bytes of the destination address and specific address register top contains the last two bytes. The addresses stored can be specific, group, local or universal.

The destination address of received frames is compared against the data stored in the specific address registers once they have been activated. The addresses are deactivated at reset or when their corresponding specific address register bottom is written. They are activated when specific address register top is written. If a receive frame address matches an active address, the frame is copied to memory.

The following example illustrates the use of the address match registers for a MAC address of 21:43:65:87:A9:CB.

Preamble 55 SFD D5 DA (Octet0 - LSB) 21 DA (Octet 1) 43 DA (Octet 2) 65 DA (Octet 3) 87 DA (Octet 3) 87 DA (Octet 4) A9 DA (Octet5 - MSB) CB SA (LSB) 00 SA 00 SA 00 SA 00 SA 00 SA 00 SA (MSB) 43 SA (LSB) 21

## 43.6.3 Network Status Register

| Name:    | EMAC_NSR   |    |    |    |      |      |    |

|----------|------------|----|----|----|------|------|----|

| Address: | 0xF802C008 |    |    |    |      |      |    |

| Access:  | Read-only  |    |    |    |      |      |    |

| 31       | 30         | 29 | 28 | 27 | 26   | 25   | 24 |

| _        | —          | -  | -  | -  | -    | -    | -  |

|          |            | -  | -  | -  | -    | -    | -  |

| 23       | 22         | 21 | 20 | 19 | 18   | 17   | 16 |

| —        | -          | -  | -  | -  | -    | -    | -  |

|          |            |    |    |    |      |      |    |

| 15       | 14         | 13 | 12 | 11 | 10   | 9    | 8  |

| _        | -          | _  | -  | -  | _    | _    | -  |

|          |            |    |    |    |      |      |    |

| 7        | 6          | 5  | 4  | 3  | 2    | 1    | 0  |

| -        | -          | -  | —  | —  | IDLE | MDIO | -  |

#### • MDIO: MDIO Input Status

Returns status of the mdio\_in pin. Use the PHY Maintenance Register for reading managed frames rather than this bit.

#### • IDLE: PHY Management Logic Status

0: The PHY logic is running.

1: The PHY management logic is idle (i.e., has completed).

## 44.7.21 Base Layer Interrupt Status Register

| Name:    | LCDC_BASEISR |      |     |      |     |    |    |  |  |

|----------|--------------|------|-----|------|-----|----|----|--|--|

| Address: | 0xF8038058   |      |     |      |     |    |    |  |  |

| Access:  | Read-only    |      |     |      |     |    |    |  |  |

| 31       | 30           | 29   | 28  | 27   | 26  | 25 | 24 |  |  |

| -        | -            | -    | -   | -    | -   | -  | -  |  |  |

| 23       | 22           | 21   | 20  | 19   | 18  | 17 | 16 |  |  |

| -        | -            | -    | -   | -    | -   | -  | -  |  |  |

| 15       | 14           | 13   | 12  | 11   | 10  | 9  | 8  |  |  |

| -        | -            | -    | -   | -    | -   | -  | -  |  |  |

| 7        | 6            | 5    | 4   | 3    | 2   | 1  | 0  |  |  |

| -        | OVR          | DONE | ADD | DSCR | DMA | _  | -  |  |  |

#### • DMA: End of DMA Transfer

When set to one this flag indicates that an End of Transfer has been detected. This flag is reset after a read operation.

#### DSCR: DMA Descriptor Loaded

When set to one this flag indicates that a descriptor has been loaded successfully. This flag is reset after a read operation.

#### • ADD: Head Descriptor Loaded

When set to one this flag indicates that the descriptor pointed to by the head register has been loaded successfully. This flag is reset after a read operation.

#### • DONE: End of List Detected

When set to one this flag indicates that an End of List condition has occurred. This flag is reset after a read operation.

#### • OVR: Overflow Detected

When set to one this flag indicates that an overflow occurred. This flag is reset after a read operation.