Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                            |

| Number of I/O              | 51                                                                         |

| Program Memory Size        | 8KB (4K x 16)                                                              |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 1K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f63j90-i-pt |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

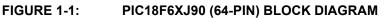

3: Brown-out Reset and Low-Voltage Detect functions are provided when the on-board voltage regulator is enabled.

| Pin Name                                          | Pin Number                                  | Pin                  | Buffer                   | Description                                                                                                                        |  |  |

|---------------------------------------------------|---------------------------------------------|----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                          | TQFP                                        | Туре                 | Туре                     | Description                                                                                                                        |  |  |

|                                                   |                                             |                      |                          | PORTG is a bidirectional I/O port.                                                                                                 |  |  |

| RG0/LCDBIAS0<br>RG0<br>LCDBIAS0                   | 5                                           | I/O<br>I             | ST<br>Analog             | Digital I/O.<br>BIAS0 input for LCD.                                                                                               |  |  |

| RG1/TX2/CK2<br>RG1<br>TX2<br>CK2                  | 6                                           | I/O<br>O<br>I/O      | ST<br>—<br>ST            | Digital I/O.<br>AUSART asynchronous transmit.<br>AUSART synchronous clock (see related RX2/DT2).                                   |  |  |

| RG2/RX2/DT2/VLCAP1<br>RG2<br>RX2<br>DT2<br>VLCAP1 | 7                                           | I/O<br>I<br>I/O<br>I | ST<br>ST<br>ST<br>Analog | Digital I/O.<br>AUSART asynchronous receive.<br>AUSART synchronous data (see related TX2/CK2).<br>LCD charge pump capacitor input. |  |  |

| RG3/VLCAP2<br>RG3<br>VLCAP2                       | 8                                           | I/O<br>I             | ST<br>Analog             | Digital I/O.<br>LCD charge pump capacitor input.                                                                                   |  |  |

| RG4/SEG26<br>RG4<br>SEG26                         | 10                                          | I/O<br>O             | ST<br>Analog             | Digital I/O.<br>SEG26 output for LCD.                                                                                              |  |  |

|                                                   | ompatible input<br>tt Trigger input<br>1Bus | with C               | MOS leve                 | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)               |  |  |

### TABLE 1-4: PIC18F8XJ90 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

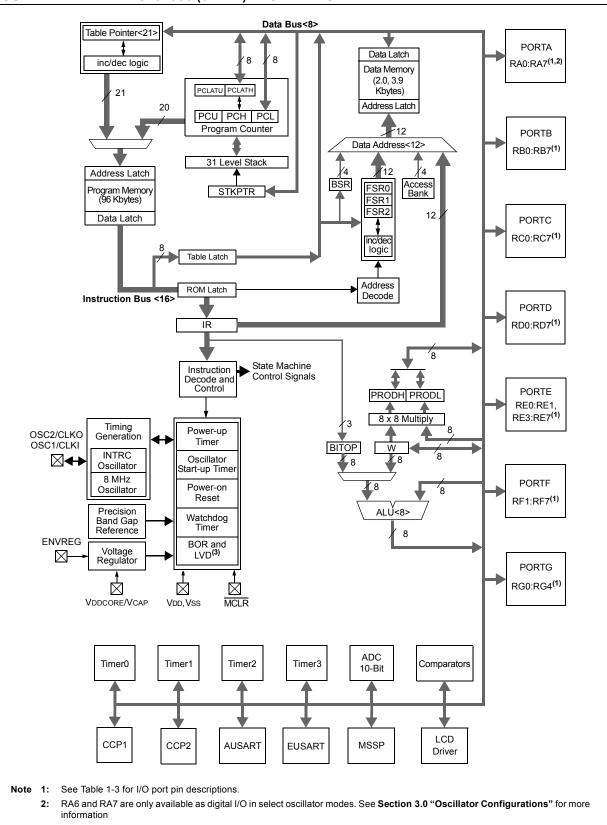

### FIGURE 6-6: DATA MEMORY MAP FOR PIC18FX3J90/X4J90 DEVICES

### 7.2.2 TABLE LATCH REGISTER (TABLAT)

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

### 7.2.3 TABLE POINTER REGISTER (TBLPTR)

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 7-1. These operations on the TBLPTR only affect the low-order 21 bits.

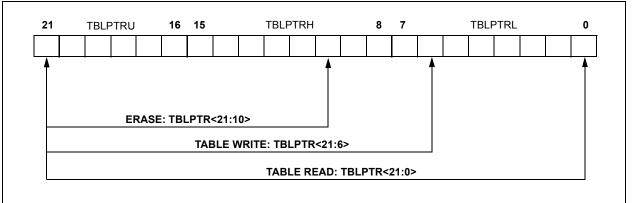

### 7.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the seven LSbs of the Table Pointer register (TBLPTR<6:0>) determine which of the 64 program memory holding registers is written to. When the timed write to program memory begins (via the WR bit), the 12 MSbs of the TBLPTR (TBLPTR<21:10>) determine which program memory block of 1024 bytes is written to. For more detail, see **Section 7.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 12 MSbs of the Table Pointer register point to the 1024-byte block that will be erased. The Least Significant bits are ignored.

Figure 7-3 describes the relevant boundaries of the TBLPTR based on Flash program memory operations.

### TABLE 7-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |  |  |  |  |  |

|--------------------|---------------------------------------------|--|--|--|--|--|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |  |  |  |  |  |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |  |  |  |  |  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |  |  |  |  |  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |  |  |  |  |  |

### FIGURE 7-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

### 9.4 IPR Registers

The IPR registers contain the individual priority bits for the peripheral interrupts. Due to the number of peripheral interrupt sources, there are three Peripheral Interrupt Priority registers (IPR1, IPR2, IPR3). Using the priority bits requires that the Interrupt Priority Enable (IPEN) bit be set.

### REGISTER 9-10: IPR1: PERIPHERAL INTERRUPT PRIORITY REGISTER 1

| U-0          | R/W-1          | R/W-1            | R/W-1            | R/W-1              | U-0             | R/W-1           | R/W-1  |

|--------------|----------------|------------------|------------------|--------------------|-----------------|-----------------|--------|

|              | ADIP           | RC1IP            | TX1IP            | SSPIP              |                 | TMR2IP          | TMR1IP |

| bit 7        |                |                  |                  |                    |                 |                 | bit (  |

|              |                |                  |                  |                    |                 |                 |        |

| Legend:      |                |                  |                  |                    |                 |                 |        |

| R = Readab   | le bit         | W = Writable     | bit              | U = Unimplem       | nented bit, rea | ad as '0'       |        |

| -n = Value a | t POR          | '1' = Bit is set |                  | '0' = Bit is clea  | ared            | x = Bit is unkr | nown   |

|              |                |                  |                  |                    |                 |                 |        |

| bit 7        | Unimplemer     | nted: Read as '  | כ'               |                    |                 |                 |        |

| bit 6        | ADIP: A/D C    | onverter Interru | pt Priority bit  |                    |                 |                 |        |

|              | 1 = High price |                  |                  |                    |                 |                 |        |

|              | 0 = Low prio   | rity             |                  |                    |                 |                 |        |

| bit 5        | RC1IP: EUS     | ART Receive Ir   | terrupt Priority | / bit              |                 |                 |        |

|              | 1 = High prio  | •                |                  |                    |                 |                 |        |

|              | 0 = Low prio   | rity             |                  |                    |                 |                 |        |

| bit 4        | TX1IP: EUS/    | ART Transmit Ir  | terrupt Priorit  | y bit              |                 |                 |        |

|              | 1 = High prio  |                  |                  |                    |                 |                 |        |

|              | 0 = Low prio   | rity             |                  |                    |                 |                 |        |

| bit 3        | SSPIP: Mast    | er Synchronous   | Serial Port Ir   | terrupt Priority b | bit             |                 |        |

|              | 1 = High prio  |                  |                  |                    |                 |                 |        |

|              | 0 = Low prio   | rity             |                  |                    |                 |                 |        |

| bit 2        | Unimplemer     | nted: Read as '  | כ'               |                    |                 |                 |        |

| bit 1        | TMR2IP: TM     | R2 to PR2 Mate   | ch Interrupt Pr  | iority bit         |                 |                 |        |

|              | 1 = High prio  | •                |                  |                    |                 |                 |        |

|              | 0 = Low prio   | rity             |                  |                    |                 |                 |        |

| bit 0        | TMR1IP: TM     | R1 Overflow Int  | errupt Priority  | bit                |                 |                 |        |

|              | 1 = High prio  | ,                |                  |                    |                 |                 |        |

|              | 0 = Low prio   | rity             |                  |                    |                 |                 |        |

| Pin Name       | Function | TRIS<br>Setting                                                 | I/O | I/O<br>Type                                             | Description                                                      |  |  |  |

|----------------|----------|-----------------------------------------------------------------|-----|---------------------------------------------------------|------------------------------------------------------------------|--|--|--|

| RB0/INT0/SEG30 | RB0      | 0                                                               | 0   | DIG                                                     | LATB<0> data output.                                             |  |  |  |

|                |          | 1                                                               | I   | TTL                                                     | PORTB<0> data input; weak pull-up when RBPU bit is cleared.      |  |  |  |

|                | INT0     | 1                                                               | Ι   | ST                                                      | External Interrupt 0 input.                                      |  |  |  |

|                | SEG30    | x                                                               | 0   | ANA                                                     | LCD Segment 30 output; disables all other pin functions.         |  |  |  |

| RB1/INT1/SEG8  | RB1      | 0                                                               | 0   | DIG                                                     | LATB<1> data output.                                             |  |  |  |

|                |          | 1                                                               | Ι   | TTL                                                     | PORTB<1> data input; weak pull-up when RBPU bit is cleared.      |  |  |  |

|                | INT1     | 1                                                               | I   | ST                                                      | External Interrupt 1 input.                                      |  |  |  |

|                |          |                                                                 | ANA | LCD Segment 8 output; disables all other pin functions. |                                                                  |  |  |  |

| RB2/INT2/SEG9  | RB2      | 0                                                               | 0   | DIG                                                     | LATB<2> data output.                                             |  |  |  |

|                |          | 1                                                               | I   | TTL                                                     | PORTB<2> data input; weak pull-up when RBPU bit is cleared.      |  |  |  |

|                | INT2     | 1                                                               | Ι   | ST                                                      | External Interrupt 2 input.                                      |  |  |  |

|                | SEG9     | x O ANA LCD Segment 9 output; disables all other pin functions. |     |                                                         |                                                                  |  |  |  |

| RB3/INT3/SEG10 | RB3      | 0                                                               | 0   | DIG                                                     | LATB<3> data output.                                             |  |  |  |

|                |          | 1                                                               | I   | TTL                                                     | PORTB<3> data input; weak pull-up when RBPU bit is cleared.      |  |  |  |

|                | INT3     | 1                                                               | Ι   | ST                                                      | External Interrupt 3 input.                                      |  |  |  |

|                | SEG10    | x                                                               | 0   | ANA                                                     | LCD Segment 10 output; disables all other pin functions.         |  |  |  |

| RB4/KBI0/SEG11 | RB4      | 0                                                               | 0   | DIG                                                     | LATB<4> data output.                                             |  |  |  |

|                |          | 1                                                               | I   | TTL                                                     | PORTB<4> data input; weak pull-up when RBPU bit is cleared.      |  |  |  |

|                | KBI0     | 1                                                               | I   | TTL                                                     | Interrupt-on-pin change.                                         |  |  |  |

|                | SEG11    | x                                                               | 0   | ANA                                                     | LCD Segment 11 output; disables all other pin functions.         |  |  |  |

| RB5/KBI1/SEG29 | RB5      | 0                                                               | 0   | DIG                                                     | LATB<5> data output.                                             |  |  |  |

|                |          | 1                                                               | Ι   | TTL                                                     | PORTB<5> data input; weak pull-up when RBPU bit is cleared.      |  |  |  |

|                | KBI1     | 1                                                               | Ι   | TTL                                                     | Interrupt-on-pin change.                                         |  |  |  |

|                | SEG29    | x                                                               | 0   | ANA                                                     | LCD Segment 29 output; disables all other pin functions.         |  |  |  |

| RB6/KBI2/PGC   | RB6      | 0                                                               | 0   | DIG                                                     | LATB<6> data output.                                             |  |  |  |

|                |          | 1                                                               | I   | TTL                                                     | PORTB<6> data input; weak pull-up when RBPU bit is cleared.      |  |  |  |

|                | KBI2     | 1                                                               | Ι   | TTL                                                     | Interrupt-on-pin change.                                         |  |  |  |

|                | PGC      | х                                                               | I   | ST                                                      | Serial execution (ICSP™) clock input for ICSP and ICD operation. |  |  |  |

| RB7/KBI3/PGD   | RB7      | 0                                                               | 0   | DIG                                                     | LATB<7> data output.                                             |  |  |  |

|                |          | 1                                                               | I   | TTL                                                     | PORTB<7> data input; weak pull-up when RBPU bit is cleared.      |  |  |  |

|                | KBI3     | 1                                                               | Ι   | TTL                                                     | Interrupt-on-pin change.                                         |  |  |  |

|                | PGD      | x                                                               | 0   | DIG                                                     | Serial execution data output for ICSP and ICD operation.         |  |  |  |

|                |          | x                                                               | Ι   | ST                                                      | Serial execution data input for ICSP and ICD operation.          |  |  |  |

### TABLE 10-5: PORTB FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input,

TTL = TTL Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

## 10.6 PORTE, TRISE and LATE Registers

PORTE is a 7-bit wide, bidirectional port. The corresponding Data Direction and Data Latch registers are TRISE and LATE. All pins on PORTE are digital only and tolerate voltages up to 5.5V.

All pins on PORTE are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output. The RE7 pin is also configurable for open-drain output when CCP2 is active on this pin. Open-drain configuration is selected by setting the CCP2OD control bit (TRISG<6>)

| Note: | These pins are configured as digital inputs |  |

|-------|---------------------------------------------|--|

|       | on any device Reset.                        |  |

Each of the PORTE pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by clearing bit, REPU (PORTG<6>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on any device Reset.

Pins, RE<6:3>, are multiplexed with the LCD common drives. I/O port functions are only available on those PORTE pins depending on which commons are active. The configuration is determined by the LMUX<1:0> control bits (LCDCON<1:0>). The availability is summarized in Table 10-11.

### TABLE 10-11: PORTE PINS AVAILABLE IN DIFFERENT LCD DRIVE CONFIGURATIONS

| LCDCON<br><1:0> | Active LCD<br>Commons      | PORTE Available<br>for I/O |

|-----------------|----------------------------|----------------------------|

| 00              | COM0 RE6, RE5              |                            |

| 01              | COM0, COM1                 | RE6, RE5                   |

| 10              | COM0, COM1<br>and COM2     | RE6                        |

| 11              | All (COM0<br>through COM3) | None                       |

Pins, RE1 and RE0, are multiplexed with the functions of LCDBIAS2 and LCDBIAS1. When LCD bias generation is required (i.e., any application where the device is connected to an external LCD), these pins cannot be used as digital I/O.

| Note: | The pin corresponding to RE2 of other      |

|-------|--------------------------------------------|

|       | PIC18F parts has the function of           |

|       | LCDBIAS3 in this device. It cannot be used |

|       | as digital I/O.                            |

RE7 is multiplexed with LCD segment drive (SEG31) controlled by the LCDSE3<7> bit. I/O port function is only available when the segment is disabled.

RE7 can also be configured as the alternate peripheral pin for the CCP2 module. This is done by clearing the CCP2MX Configuration bit.

#### EXAMPLE 10-5: INITIALIZING PORTE

| CLRF  | PORTE | ; Initialize PORTE by<br>; clearing output |

|-------|-------|--------------------------------------------|

| CLRF  | LATE  | ; data latches<br>; Alternate method       |

| СШКР  | DATE  | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | 03h   | ; Value used to                            |

|       |       | ; initialize data<br>; direction           |

| MOVWF | TRISE |                                            |

|       |       |                                            |

### 11.0 TIMER0 MODULE

The Timer0 module incorporates the following features:

- Software selectable operation as a timer or counter in both 8-bit or 16-bit modes

- Readable and writable registers

- Dedicated 8-bit, software programmable

prescaler

- Selectable clock source (internal or external)

- Edge select for external clock

- Interrupt-on-overflow

The T0CON register (Register 11-1) controls all aspects of the module's operation, including the prescale selection; it is both readable and writable.

A simplified block diagram of the Timer0 module in 8-bit mode is shown in Figure 11-1. Figure 11-2 shows a simplified block diagram of the Timer0 module in 16-bit mode.

### REGISTER 11-1: T0CON: TIMER0 CONTROL REGISTER

| R/W-1  | R/W-1  | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 |

|--------|--------|-------|-------|-------|-------|-------|-------|

| TMR00N | T08BIT | TOCS  | TOSE  | PSA   | T0PS2 | T0PS1 | T0PS0 |

| bit 7  |        |       |       |       |       |       | bit 0 |

| Legend:    |                                                                           |                                                                                                                                                                                                                                                |                                                              |                    |  |  |  |  |  |

|------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|--|--|--|--|--|

| R = Reada  | ble bit                                                                   | W = Writable bit                                                                                                                                                                                                                               | U = Unimplemented bit                                        | , read as '0'      |  |  |  |  |  |

| -n = Value | at POR                                                                    | '1' = Bit is set                                                                                                                                                                                                                               | '0' = Bit is cleared                                         | x = Bit is unknown |  |  |  |  |  |

| bit 7      | TMR0ON:                                                                   | Timer0 On/Off Control bit                                                                                                                                                                                                                      |                                                              |                    |  |  |  |  |  |

|            | 1 = Enable<br>0 = Stops                                                   |                                                                                                                                                                                                                                                |                                                              |                    |  |  |  |  |  |

| bit 6      | <b>T08BIT:</b> T                                                          | imer0 8-Bit/16-Bit Control b                                                                                                                                                                                                                   | it                                                           |                    |  |  |  |  |  |

|            |                                                                           | ) is configured as an 8-bit ti<br>) is configured as a 16-bit ti                                                                                                                                                                               |                                                              |                    |  |  |  |  |  |

| bit 5      | TOCS: Tim                                                                 | ner0 Clock Source Select bi                                                                                                                                                                                                                    | t                                                            |                    |  |  |  |  |  |

|            |                                                                           | tion on T0CKI pin input edg<br>al clock (F0sc/4)                                                                                                                                                                                               | le                                                           |                    |  |  |  |  |  |

| bit 4      | T0SE: Tim                                                                 | TOSE: Timer0 Source Edge Select bit                                                                                                                                                                                                            |                                                              |                    |  |  |  |  |  |

|            |                                                                           | nent on high-to-low transitio<br>nent on low-to-high transitio                                                                                                                                                                                 | •                                                            |                    |  |  |  |  |  |

| bit 3      | PSA: Time                                                                 | er0 Prescaler Assignment b                                                                                                                                                                                                                     | it                                                           |                    |  |  |  |  |  |

|            |                                                                           |                                                                                                                                                                                                                                                | Timer0 clock input bypasses<br>er0 clock input comes from pr |                    |  |  |  |  |  |

| bit 2-0    | T0PS<2:0                                                                  | >: Timer0 Prescaler Select                                                                                                                                                                                                                     | bits                                                         |                    |  |  |  |  |  |

|            | 110 = 1:12 $101 = 1:64$ $100 = 1:32$ $011 = 1:16$ $010 = 1:8$ $001 = 1:4$ | <ul> <li>56 Prescale value</li> <li>28 Prescale value</li> <li>4 Prescale value</li> <li>2 Prescale value</li> <li>6 Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> <li>Prescale value</li> </ul> |                                                              |                    |  |  |  |  |  |

### 12.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt on overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 12-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:    |                      |                                                                    |                                   |                    |  |  |  |  |  |  |

|------------|----------------------|--------------------------------------------------------------------|-----------------------------------|--------------------|--|--|--|--|--|--|

| R = Reada  | ble bit              | W = Writable bit                                                   | U = Unimplemented bit             | , read as '0'      |  |  |  |  |  |  |

| -n = Value | at POR               | '1' = Bit is set                                                   | '0' = Bit is cleared              | x = Bit is unknown |  |  |  |  |  |  |

| bit 7      | <b>RD16:</b> 16      | -Bit Read/Write Mode Enab                                          | le bit                            |                    |  |  |  |  |  |  |

|            |                      | bles register read/write of TIr<br>bles register read/write of Tir | •                                 |                    |  |  |  |  |  |  |

| bit 6      | T1RUN:               | Timer1 System Clock Status                                         | bit                               |                    |  |  |  |  |  |  |

|            |                      | ce clock is derived from Time ce clock is derived from ano         |                                   |                    |  |  |  |  |  |  |

| bit 5-4    | T1CKPS               | <1:0>: Timer1 Input Clock P                                        | rescale Select bits               |                    |  |  |  |  |  |  |

|            | ==•                  | 11 = 1:8 Prescale value                                            |                                   |                    |  |  |  |  |  |  |

|            |                      | ) = 1:4 Prescale value<br>. = 1:2 Prescale value                   |                                   |                    |  |  |  |  |  |  |

|            |                      | 0 = 1:1 Prescale value                                             |                                   |                    |  |  |  |  |  |  |

| bit 3      |                      | N: Timer1 Oscillator Enable                                        | bit                               |                    |  |  |  |  |  |  |

|            | 1 = Time             | r1 oscillator is enabled                                           |                                   |                    |  |  |  |  |  |  |

|            |                      | r1 oscillator is shut off                                          |                                   |                    |  |  |  |  |  |  |

|            |                      |                                                                    | esistor are turned off to elimina | ate power drain.   |  |  |  |  |  |  |

| bit 2      |                      | : Timer1 External Clock Inpu                                       | t Synchronization Select bit      |                    |  |  |  |  |  |  |

|            |                      | <u>IR1CS = 1:</u><br>ot synchronize external clock                 | cinnut                            |                    |  |  |  |  |  |  |

|            |                      | hronize external clock input                                       | ( input                           |                    |  |  |  |  |  |  |

|            | When TM              | IR1CS = 0:                                                         |                                   |                    |  |  |  |  |  |  |

|            | This bit is          | ignored. Timer1 uses the in                                        | ternal clock when TMR1CS =        | 0.                 |  |  |  |  |  |  |

| bit 1      | TMR1CS               | TMR1CS: Timer1 Clock Source Select bit                             |                                   |                    |  |  |  |  |  |  |

|            |                      | rnal clock from pin RC0/T1C<br>nal clock (Fosc/4)                  | SO/T13CKI (on the rising edge     | e)                 |  |  |  |  |  |  |

| bit 0      | TMR10N               | I: Timer1 On bit                                                   |                                   |                    |  |  |  |  |  |  |

|            | 1 = Enat<br>0 = Stop | bles Timer1<br>s Timer1                                            |                                   |                    |  |  |  |  |  |  |

### 15.4 PWM Mode

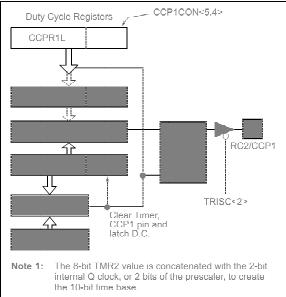

In Pulse-Width Modulation (PWM) mode, the CCP2 pin produces up to a 10-bit resolution PWM output. Since the CCP2 pin is multiplexed with a PORTC or PORTE data latch, the appropriate TRIS bit must be cleared to make the CCP2 pin an output.

| Note: | Clearing the CCP2CON register will force<br>the RC1 or RE7 output latch (depending<br>on device configuration) to the default low<br>level. This is not the PORTC or PORTE |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | I/O data latch.                                                                                                                                                            |

Figure 15-4 shows a simplified block diagram of the CCP1 module in PWM mode.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 15.4.3** "Setup for PWM Operation".

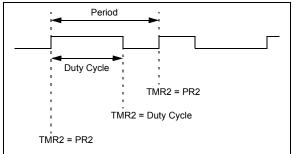

A PWM output (Figure 15-5) has a time base (period) and a time that the output stays high (duty cycle). The frequency of the PWM is the inverse of the period (1/period).

#### FIGURE 15-5: PWM OUTPUT

### 15.4.1 PWM PERIOD

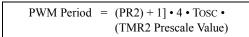

The PWM period is specified by writing to the PR2 register. The PWM period can be calculated using the following formula:

### EQUATION 15-1:

PWM frequency is defined as 1/[PWM period].

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP2 pin is set (exception: if PWM duty cycle = 0%, the CCP2 pin will not be set)

- The PWM duty cycle is latched from CCPR2L into CCPR2H

| R/W-0        | R/W-0                                                                                                                                                                                                                | R-0                                                                                             | R-0                    | R/W-0                            | R/W-0            | R/W-0           | R/W-0 |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------------------------|----------------------------------|------------------|-----------------|-------|

| WFT          | BIASMD                                                                                                                                                                                                               | LCDA                                                                                            | WA                     | LP3                              | LP2              | LP1             | LP0   |

| bit 7        |                                                                                                                                                                                                                      |                                                                                                 | •                      |                                  |                  |                 | bit   |

| Legend:      |                                                                                                                                                                                                                      |                                                                                                 |                        |                                  |                  |                 |       |

| R = Readab   | le bit                                                                                                                                                                                                               | W = Writable                                                                                    | bit                    | U = Unimplem                     | nented bit, read | d as '0'        |       |

| -n = Value a | It POR                                                                                                                                                                                                               | '1' = Bit is set                                                                                |                        | '0' = Bit is clea                | ared             | x = Bit is unkr | nown  |

| bit 7        | WFT: Wavefo                                                                                                                                                                                                          | rm Type Selec                                                                                   | t bit                  |                                  |                  |                 |       |

|              | 1 = Type-B wa                                                                                                                                                                                                        | aveform (phase                                                                                  | e changes on           | each frame bou<br>hin each commo |                  |                 |       |

| bit 6        | BIASMD: Bia<br>When LMUX<<br>0 = Static Bias                                                                                                                                                                         | s Mode Select<br>< <u>1:0&gt; = 00:</u><br>s mode (do not<br>< <u>1:0&gt; = 01 or 1</u><br>node | bit<br>set this bit to |                                  | ,                |                 |       |

|              | When LMUX<                                                                                                                                                                                                           |                                                                                                 | et this bit to '1      | .')                              |                  |                 |       |

| bit 5        | LCDA: LCD A                                                                                                                                                                                                          | Active Status bi                                                                                | t                      |                                  |                  |                 |       |

|              |                                                                                                                                                                                                                      | er module is act<br>er module is ina                                                            |                        |                                  |                  |                 |       |

| bit 4        | 1 = Write into                                                                                                                                                                                                       | te Allow Status<br>the LCDDATA<br>the LCDDATA                                                   | x registers is         |                                  |                  |                 |       |

| bit 3-0      | LP<3:0>: LCI                                                                                                                                                                                                         | D Prescaler Se                                                                                  | lect bits              |                                  |                  |                 |       |

|              | 1111 = 1:16 $1110 = 1:15$ $1101 = 1:14$ $1100 = 1:13$ $1011 = 1:12$ $1010 = 1:11$ $1001 = 1:10$ $1000 = 1:9$ $0111 = 1:8$ $0110 = 1:7$ $0101 = 1:6$ $0100 = 1:5$ $0011 = 1:4$ $0010 = 1:3$ $0001 = 1:2$ $0000 = 1:1$ |                                                                                                 |                        |                                  |                  |                 |       |

### REGISTER 16-2: LCDPS: LCD PHASE REGISTER

### 16.3.3 BIAS CONFIGURATIONS

PIC18F85J90 family devices have four distinct circuit configurations for LCD bias generation:

- · M0: Regulator with Boost

- M1: Regulator without Boost

- · M2: Resistor Ladder with Software Contrast

- M3: Resistor Ladder with Hardware Contrast

### 16.3.3.1 M0 (Regulator with Boost)

In M0 operation, the LCD charge pump feature is enabled. This allows the regulator to generate voltages up to +3.6V to the LCD (as measured at LCDBIAS3).

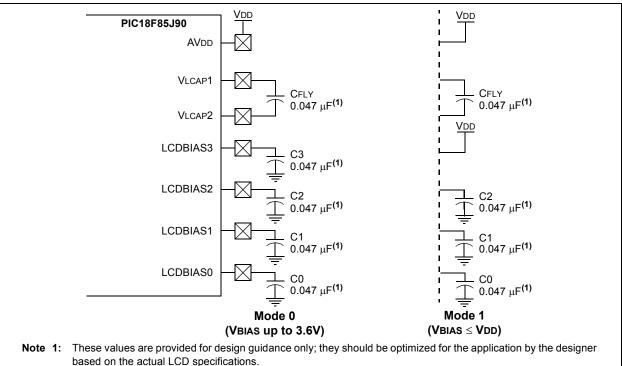

M0 uses a flyback capacitor connected between VLCAP1 and VLCAP2, as well as filter capacitors on LCDBIAS0 through LCDBIAS3, to obtain the required voltage boost (Figure 16-3).

| Note: | When the device is put to Sleep while         |

|-------|-----------------------------------------------|

|       | operating in M0 or M1 mode, make sure         |

|       | that the Bias capacitors are fully discharged |

|       | to get the lowest Sleep current.              |

The output voltage (VBIAS) is the difference of potential between LCDBIAS3 and LCDBIAS0. It is set by the BIAS<2:0> bits which adjust the offset between LCDBIAS0 and VSS. The flyback capacitor (CFLY) acts as a charge storage element for large LCD loads. This mode is useful in those cases where the voltage requirements of the LCD are higher than the micro-controller's VDD. It also permits software control of the display's contrast by adjustment of bias voltage by changing the value of the BIAS bits.

M0 supports Static and 1/3 Bias types. Generation of the voltage levels for 1/3 Bias is handled automatically, but must be configured in software.

M0 is enabled by selecting a valid regulator clock source (CKSEL<1:0> set to any value except '00') and setting the CPEN bit. If static Bias type is required, the MODE13 bit must be cleared.

### 16.3.3.2 M1 (Regulator without Boost)

M1 operation is similar to M0, but does not use the LCD charge pump. It can provide VBIAS up to the voltage level supplied directly to LCDBIAS3. It can be used in cases where VDD for the application is expected to never drop below a level that can provide adequate contrast for the LCD. The connection of external components is very similar to M0, except that LCDBIAS3 must be tied directly to VDD (Figure 16-3).

The BIAS<2:0> bits can still be used to adjust contrast in software by changing VBIAS. As with M0, changing these bits changes the offset between LCDBIAS0 and Vss. In M1, this is reflected in the change between the LCDBIAS0 and the voltage tied to LCDBIAS3. Thus, if VDD should change, VBIAS will also change; where in M0, the level of VBIAS is constant.

Like M0, M1 supports Static and 1/3 Bias types. Generation of the voltage levels for 1/3 Bias is handled automatically but must be configured in software.

M1 is enabled by selecting a valid regulator clock source (CKSEL<1:0> set to any value except '00') and clearing the CPEN bit. If 1/3 Bias type is required, the MODE13 bit should also be set.

### FIGURE 16-3: LCD REGULATOR CONNECTIONS FOR M0 AND M1 CONFIGURATIONS

### 17.3.1 REGISTERS

Each MSSP module has four registers for SPI mode operation. These are:

- MSSP Control Register 1 (SSPCON1)

- MSSP Status Register (SSPSTAT)

- MSSP Serial Receive/Transmit Buffer Register (SSPBUF)

- MSSP Shift Register (SSPSR) Not directly accessible

SSPCON1 and SSPSTAT are the control and status registers in SPI mode operation. The SSPCON1 register is readable and writable. The lower 6 bits of the SSPSTAT are read-only. The upper two bits of the SSPSTAT are read/write.

SSPSR is the shift register used for shifting data in or out. SSPBUF is the buffer register to which data bytes are written to or read from.

In receive operations, SSPSR and SSPBUF together create a double-buffered receiver. When SSPSR receives a complete byte, it is transferred to SSPBUF and the SSPIF interrupt is set.

During transmission, the SSPBUF is not double-buffered. A write to SSPBUF will write to both SSPBUF and SSPSR.

### REGISTER 17-1: SSPSTAT: MSSP STATUS REGISTER (SPI MODE)

| R/W-0                        | R/W-0                          | R-0                           | R-0             | R-0               | R-0             | R0             | R-0         |

|------------------------------|--------------------------------|-------------------------------|-----------------|-------------------|-----------------|----------------|-------------|

| SMP                          | CKE <sup>(1)</sup>             | D/A                           | Р               | S                 | R/W             | UA             | BF          |

| bit 7                        | •                              |                               |                 |                   |                 |                | bit         |

|                              |                                |                               |                 |                   |                 |                |             |

| Legend:                      |                                |                               |                 |                   |                 |                |             |

| R = Readal                   | ole bit                        | W = Writable                  | bit             | U = Unimpler      | mented bit, rea | id as '0'      |             |

| -n = Value a                 | at POR                         | '1' = Bit is set              |                 | '0' = Bit is cle  | ared            | x = Bit is unk | nown        |

|                              |                                |                               |                 |                   |                 |                |             |

| bit 7                        | SMP: Sample                    | e bit                         |                 |                   |                 |                |             |

|                              | <u>SPI Master m</u>            |                               |                 |                   |                 |                |             |

|                              |                                | a sampled at en               |                 |                   |                 |                |             |

|                              | 0 = input data<br>SPI Slave mo | a sampled at mi               | dole of data of | Sulput time       |                 |                |             |

|                              |                                | e cleared when t              | SPI is used ir  | n Slave mode.     |                 |                |             |

| bit 6                        |                                | ock Select bit <sup>(1)</sup> |                 |                   |                 |                |             |

|                              | 1 = Transmit                   | occurs on trans               | ition from act  | ive to Idle clock | state           |                |             |

|                              | 0 = Transmit                   | occurs on trans               | ition from Idle | e to active clock | state           |                |             |

| bit 5                        | D/A: Data/Ad                   | Idress bit                    |                 |                   |                 |                |             |

|                              | Used in I <sup>2</sup> C™      | <sup>4</sup> mode only.       |                 |                   |                 |                |             |

| bit 4                        | P: Stop bit                    |                               |                 |                   |                 |                |             |

|                              | Used in I <sup>2</sup> C n     | node only. This               | bit is cleared  | when the MSSI     | P module is dis | abled, SSPEN   | is cleared. |

| bit 3                        | S: Start bit                   |                               |                 |                   |                 |                |             |

|                              | Used in I <sup>2</sup> C n     | node only.                    |                 |                   |                 |                |             |

| bit 2                        | R/W: Read/V                    | Vrite Information             | ı bit           |                   |                 |                |             |

|                              | Used in I <sup>2</sup> C n     | node only.                    |                 |                   |                 |                |             |

| bit 1 UA: Update Address bit |                                |                               |                 |                   |                 |                |             |

|                              | Used in I <sup>2</sup> C n     | node only.                    |                 |                   |                 |                |             |

| bit 0                        | BF: Buffer Fu                  | ull Status bit (Re            | ceive mode o    | only)             |                 |                |             |

|                              |                                | complete, SSPE                |                 |                   |                 |                |             |

|                              | 0 = Receive I                  | not complete, S               | SPBUF is err    | npty              |                 |                |             |

Note 1: Polarity of clock state is set by the CKP bit (SSPCON1<4>).

| R/W-0                        | R-1                                              | R/W-0                                                                  | R/W-0            | R/W-0                                     | U-0             | R/W-0           | R/W-0            |

|------------------------------|--------------------------------------------------|------------------------------------------------------------------------|------------------|-------------------------------------------|-----------------|-----------------|------------------|

| ABDOVF                       | RCIDL                                            | RXDTP                                                                  | TXCKP            | BRG16                                     | —               | WUE             | ABDEN            |

| bit 7                        |                                                  |                                                                        |                  |                                           |                 |                 | bit              |

| Logondi                      |                                                  |                                                                        |                  |                                           |                 |                 |                  |

| <b>Legend:</b><br>R = Readab | le bit                                           | W = Writable                                                           | bit              | U = Unimplem                              | ented bit. read | d as '0'        |                  |

| -n = Value a                 | It POR                                           | '1' = Bit is set                                                       |                  | '0' = Bit is clea                         |                 | x = Bit is unk  | nown             |

|                              |                                                  |                                                                        |                  |                                           |                 |                 |                  |

| bit 7                        | 1 = A BRG I                                      | uto-Baud Acquis<br>rollover has occ<br>6 rollover has oc               | urred during A   | Status bit<br>uto-Baud Rate [             | Detect mode (r  | must be cleare  | d in software)   |

| bit 6                        |                                                  | eive Operation I                                                       |                  |                                           |                 |                 |                  |

|                              | 1 = Receive                                      | operation is Idl                                                       | е                |                                           |                 |                 |                  |

| bit 5                        | RXDTP: Red                                       | ceived Data Pola                                                       | arity Select bit | (Asynchronous                             | mode only)      |                 |                  |

|                              | <u>Asynchronou</u><br>1 = RX data<br>0 = RX data |                                                                        | nverted          |                                           |                 |                 |                  |

| bit 4                        | TXCKP: Clo                                       | ck and Data Pol                                                        | arity Select bit | t                                         |                 |                 |                  |

|                              | Asynchronou<br>1 = Idle state                    |                                                                        | K) is a low leve | el                                        |                 |                 |                  |

|                              |                                                  | <u>s mode:</u><br>e for clock (CK)<br>e for clock (CK)                 |                  |                                           |                 |                 |                  |

| bit 3                        | 1 = 16-bit Ba                                    |                                                                        | ator – SPBRG     | e bit<br>6H1 and SPBRG<br>⊢only (Compatib |                 | 3RGH1 value i   | gnored           |

| bit 2                        | Unimpleme                                        | nted: Read as '                                                        | כי               |                                           |                 |                 |                  |

| bit 1                        | WUE: Wake                                        | -up Enable bit                                                         |                  |                                           |                 |                 |                  |

|                              | hardwar                                          | T will continue to<br>re on following ri<br>not monitored o<br>s mode: | sing edge        | RX1 pin – interru<br>detected             | upt generated   | on falling edge | e; bit cleared i |

| bit 0                        | ABDEN: Aut                                       | o-Baud Detect I                                                        | Enable bit       |                                           |                 |                 |                  |

|                              | cleared<br>0 = Baud ra                           | baud rate meas<br>in hardware upo<br>te measuremen                     | on completion.   |                                           | r. Requires re  | ception of a S  | vnc field (55h   |

|                              | Synchronous<br>Unused in th                      |                                                                        |                  |                                           |                 |                 |                  |

|             |                       | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                       |            |                             |                       |            |                             |                       |            |                             |

|-------------|-----------------------|-------------------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc = 40.000 MHz     |                               |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |            |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | _                     |                               |                             |                       |            |                             | _                     |            | _                           | _                     | _          |                             |

| 1.2         | —                     | _                             | —                           | 1.221                 | 1.73       | 255                         | 1.202                 | 0.16       | 129                         | 1.201                 | -0.16      | 103                         |

| 2.4         | 2.441                 | 1.73                          | 255                         | 2.404                 | 0.16       | 129                         | 2.404                 | 0.16       | 64                          | 2.403                 | -0.16      | 51                          |

| 9.6         | 9.615                 | 0.16                          | 64                          | 9.766                 | 1.73       | 31                          | 9.766                 | 1.73       | 15                          | 9.615                 | -0.16      | 12                          |

| 19.2        | 19.531                | 1.73                          | 31                          | 19.531                | 1.73       | 15                          | 19.531                | 1.73       | 7                           | _                     | _          | _                           |

| 57.6        | 56.818                | -1.36                         | 10                          | 62.500                | 8.51       | 4                           | 52.083                | -9.58      | 2                           | —                     | _          | _                           |

| 115.2       | 125.000               | 8.51                          | 4                           | 104.167               | -9.58      | 2                           | 78.125                | -32.18     | 1                           | _                     | _          | _                           |

| TABLE 18-3: BAUD RATES FOR ASYNCHRONOUS MODES |

|-----------------------------------------------|

|-----------------------------------------------|

|             |                       |                  | S                           | YNC = 0, E            | BRGH = (   | , BRG16 =                   | 0                     |            |                             |

|-------------|-----------------------|------------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fos                   | Fosc = 4.000 MHz |                             |                       | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error       | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         | 0.300                 | 0.16             | 207                         | 0.300                 | -0.16      | 103                         | 0.300                 | -0.16      | 51                          |

| 1.2         | 1.202                 | 0.16             | 51                          | 1.201                 | -0.16      | 25                          | 1.201                 | -0.16      | 12                          |

| 2.4         | 2.404                 | 0.16             | 25                          | 2.403                 | -0.16      | 12                          | —                     | _          | _                           |

| 9.6         | 8.929                 | -6.99            | 6                           | —                     | _          | _                           | —                     | _          | _                           |

| 19.2        | 20.833                | 8.51             | 2                           | —                     | _          | _                           | —                     | _          | _                           |

| 57.6        | 62.500                | 8.51             | 0                           | —                     | _          | _                           | —                     | _          | _                           |

| 115.2       | 62.500                | -45.75           | 0                           | _                     | _          | _                           | _                     | _          | _                           |

|             |                       |            |                             |                       | SYNC       | = 0, BRGH                   | <b>i =</b> 1, BRG     | <b>16 =</b> 0 |                             |                       |            |                             |

|-------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|---------------|-----------------------------|-----------------------|------------|-----------------------------|

| BAUD        | Fosc = 40.000 MHz     |            |                             | Fosc = 20.000 MHz     |            |                             | Fosc = 10.000 MHz     |               |                             | Fosc = 8.000 MHz      |            |                             |

| RATE<br>(K) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error    | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) |

| 0.3         |                       |            | _                           |                       | _          |                             | _                     |               | _                           | _                     | _          | _                           |

| 1.2         | —                     | _          | _                           | —                     | _          | _                           | —                     | _             | —                           | _                     | _          | —                           |

| 2.4         | —                     | _          | _                           | —                     | _          | _                           | 2.441                 | 1.73          | 255                         | 2.403                 | -0.16      | 207                         |

| 9.6         | 9.766                 | 1.73       | 255                         | 9.615                 | 0.16       | 129                         | 9.615                 | 0.16          | 64                          | 9.615                 | -0.16      | 51                          |

| 19.2        | 19.231                | 0.16       | 129                         | 19.231                | 0.16       | 64                          | 19.531                | 1.73          | 31                          | 19.230                | -0.16      | 25                          |

| 57.6        | 58.140                | 0.94       | 42                          | 56.818                | -1.36      | 21                          | 56.818                | -1.36         | 10                          | 55.555                | 3.55       | 8                           |

| 115.2       | 113.636               | -1.36      | 21                          | 113.636               | -1.36      | 10                          | 125.000               | 8.51          | 4                           | —                     | _          | _                           |

|              |                       |            | S                           | YNC = 0, E            | BRGH = 1   | , BRG16 =                   | 0                     |            | SYNC = 0, BRGH = 1, BRG16 = 0 |  |  |  |  |  |  |  |  |  |

|--------------|-----------------------|------------|-----------------------------|-----------------------|------------|-----------------------------|-----------------------|------------|-------------------------------|--|--|--|--|--|--|--|--|--|

| BAUD<br>RATE | Fosc = 4.000 MHz      |            |                             | Fos                   | c = 2.000  | MHz                         | Fosc = 1.000 MHz      |            |                               |  |  |  |  |  |  |  |  |  |

| (K)          | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate<br>(K) | %<br>Error | SPBRG<br>value<br>(decimal)   |  |  |  |  |  |  |  |  |  |

| 0.3          |                       |            | _                           |                       |            | _                           | 0.300                 | -0.16      | 207                           |  |  |  |  |  |  |  |  |  |

| 1.2          | 1.202                 | 0.16       | 207                         | 1.201                 | -0.16      | 103                         | 1.201                 | -0.16      | 51                            |  |  |  |  |  |  |  |  |  |

| 2.4          | 2.404                 | 0.16       | 103                         | 2.403                 | -0.16      | 51                          | 2.403                 | -0.16      | 25                            |  |  |  |  |  |  |  |  |  |

| 9.6          | 9.615                 | 0.16       | 25                          | 9.615                 | -0.16      | 12                          | _                     | _          | —                             |  |  |  |  |  |  |  |  |  |

| 19.2         | 19.231                | 0.16       | 12                          | —                     | _          | _                           | —                     | _          | _                             |  |  |  |  |  |  |  |  |  |

| 57.6         | 62.500                | 8.51       | 3                           | —                     | _          | _                           | —                     | _          | _                             |  |  |  |  |  |  |  |  |  |

| 115.2        | 125.000               | 8.51       | 1                           | —                     | _          | —                           | —                     | _          | _                             |  |  |  |  |  |  |  |  |  |

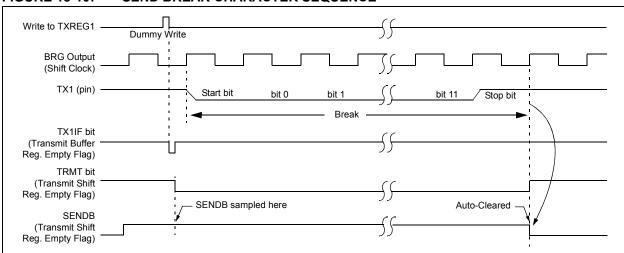

### 18.3.5 BREAK CHARACTER SEQUENCE

The Enhanced USART module has the capability of sending the special Break character sequences that are required by the LIN/J2602 bus standard. The Break character transmit consists of a Start bit, followed by twelve '0' bits and a Stop bit. The Frame Break character is sent whenever the SENDB and TXEN bits (TXSTA<3> and TXSTA<5>) are set while the Transmit Shift register is loaded with data. Note that the value of data written to TXREG1 will be ignored and all '0's will be transmitted.

The SENDB bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN/J2602 specification).

Note that the data value written to the TXREG1 for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence.

The TRMT bit indicates when the transmit operation is active or Idle, just as it does during normal transmission. See Figure 18-10 for the timing of the Break character sequence.

### 18.3.5.1 Break and Sync Transmit Sequence

The following sequence will send a message frame header made up of a Break, followed by an Auto-Baud Sync byte. This sequence is typical of a LIN/J2602 bus master.

- 1. Configure the EUSART for the desired mode.

- 2. Set the TXEN and SENDB bits to set up the Break character.

- 3. Load the TXREG1 with a dummy character to initiate transmission (the value is ignored).

- 4. Write '55h' to TXREG1 to load the Sync character into the transmit FIFO buffer.

- 5. After the Break has been sent, the SENDB bit is reset by hardware. The Sync character now transmits in the preconfigured mode.

When the TXREG1 becomes empty, as indicated by the TX1IF, the next data byte can be written to TXREG1.

### 18.3.6 RECEIVING A BREAK CHARACTER

The Enhanced USART module can receive a Break character in two ways.