Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                             |

| Number of I/O              | 51                                                                          |

| Program Memory Size        | 8KB (4K x 16)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f63j90t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

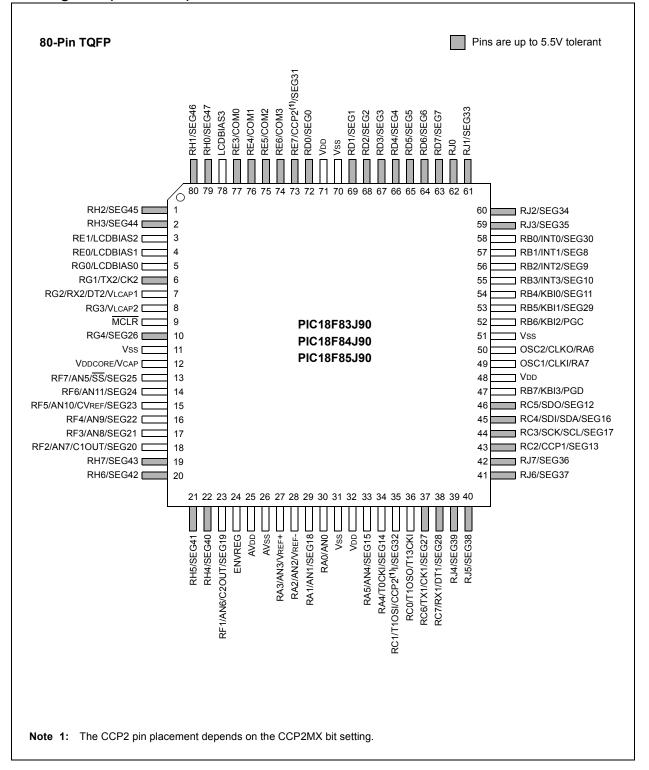

#### **Pin Diagrams (Continued)**

## 1.2 LCD Driver

The on-chip LCD driver includes many features that make the integration of displays in low-power applications easier. These include an integrated voltage regulator with charge pump that allows contrast control in software and display operation above device VDD.

### 1.3 Other Special Features

- Communications: The PIC18F85J90 family incorporates a range of serial communication peripherals, including an Addressable USART, a separate Enhanced USART that supports LIN/J2602 Specification 1.2, and one Master SSP module capable of both SPI and I<sup>2</sup>C<sup>™</sup> (Master and Slave) modes of operation.

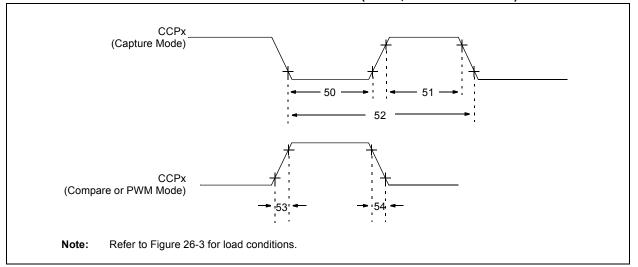

- CCP Modules: All devices in the family incorporate two Capture/Compare/PWM (CCP) modules. Up to four different time bases may be used to perform several different operations at once.

- **10-Bit A/D Converter:** This module incorporates programmable acquisition time, allowing for a channel to be selected and a conversion to be initiated without waiting for a sampling period and thus, reducing code overhead.

- Extended Watchdog Timer (WDT): This enhanced version incorporates a 16-bit prescaler, allowing an extended time-out range that is stable across operating voltage and temperature. See Section 26.0 "Electrical Characteristics" for time-out periods.

### 1.4 Details on Individual Family Members

Devices in the PIC18F85J90 family are available in 64-pin and 80-pin packages. Block diagrams for the two groups are shown in Figure 1-1 and Figure 1-2.

The devices are differentiated from each other in four ways:

- Flash program memory (three sizes, ranging from 8 Kbytes for PIC18FX3J90 devices to 32 Kbytes for PIC18FX5J90 devices).

- Data RAM (1024 bytes for PIC18FX3J90 and PIC18FX4J90 devices, 2048 bytes for PIC18FX5J90 devices).

- I/O ports (7 bidirectional ports on 64-pin devices, 9 bidirectional ports on 80-pin devices).

- LCD Pixels: 132 pixels (33 SEGs x 4 COMs) can be driven by 64-pin devices; 192 pixels (48 SEGs x 4 COMs) can be driven by 80-pin devices.

All other features for devices in this family are identical. These are summarized in Table 1-1 and Table 1-2.

The pinouts for all devices are listed in Table 1-3 and Table 1-4.

| Pin Name                               | Pin Number | Pin             | Buffer               | Description                                                                                                          |

|----------------------------------------|------------|-----------------|----------------------|----------------------------------------------------------------------------------------------------------------------|

| Pin Name                               | TQFP       | Туре            | Туре                 | Description                                                                                                          |

|                                        |            |                 |                      | PORTB is a bidirectional I/O port. PORTB can be software<br>programmed for internal weak pull-ups on all inputs.     |

| RB0/INT0/SEG30<br>RB0<br>INT0<br>SEG30 | 48         | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External Interrupt 0.<br>SEG30 output for LCD.                                                       |

| RB1/INT1/SEG8<br>RB1<br>INT1<br>SEG8   | 47         | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External Interrupt 1.<br>SEG8 output for LCD.                                                        |

| RB2/INT2/SEG9<br>RB2<br>INT2<br>SEG9   | 46         | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External Interrupt 2.<br>SEG9 output for LCD.                                                        |

| RB3/INT3/SEG10<br>RB3<br>INT3<br>SEG10 | 45         | I/O<br>I<br>O   | TTL<br>ST<br>Analog  | Digital I/O.<br>External Interrupt 3.<br>SEG10 output for LCD.                                                       |

| RB4/KBI0/SEG11<br>RB4<br>KBI0<br>SEG11 | 44         | I/O<br>I<br>O   | TTL<br>TTL<br>Analog | Digital I/O.<br>Interrupt-on-change pin.<br>SEG11 output for LCD.                                                    |

| RB5/KBI1/SEG29<br>RB5<br>KBI1<br>SEG29 | 43         | I/O<br>I<br>O   | TTL<br>TTL<br>Analog | Digital I/O.<br>Interrupt-on-change pin.<br>SEG29 output for LCD.                                                    |

| RB6/KBI2/PGC<br>RB6<br>KBI2<br>PGC     | 42         | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP™ programming clock pin                      |

| RB7/KBI3/PGD<br>RB7<br>KBI3<br>PGD     | 37         | I/O<br>I<br>I/O | TTL<br>TTL<br>ST     | Digital I/O.<br>Interrupt-on-change pin.<br>In-Circuit Debugger and ICSP programming data pin.                       |

|                                        | MBus       |                 |                      | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |

| TABLE 1-3: | PIC18F6XJ90 PINOUT I/O DESCRIPTIONS ( |  |

|------------|---------------------------------------|--|

|            |                                       |  |

**Note 1:** Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

| Pin Name                                                                                                                                                                                                                   | Pin Number | Pin                  | Buffer                   | Description                                                                                                                        |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name                                                                                                                                                                                                                   | TQFP       | Туре                 | Туре                     | Description                                                                                                                        |  |  |  |

|                                                                                                                                                                                                                            |            |                      |                          | PORTG is a bidirectional I/O port.                                                                                                 |  |  |  |

| RG0/LCDBIAS0<br>RG0<br>LCDBIAS0                                                                                                                                                                                            | 5          | I/O<br>I             | ST<br>Analog             | Digital I/O.<br>BIAS0 input for LCD.                                                                                               |  |  |  |

| RG1/TX2/CK2<br>RG1<br>TX2<br>CK2                                                                                                                                                                                           | 6          | I/O<br>O<br>I/O      | ST<br>—<br>ST            | Digital I/O.<br>AUSART asynchronous transmit.<br>AUSART synchronous clock (see related RX2/DT2).                                   |  |  |  |

| RG2/RX2/DT2/VLCAP1<br>RG2<br>RX2<br>DT2<br>VLCAP1                                                                                                                                                                          | 7          | I/O<br>I<br>I/O<br>I | ST<br>ST<br>ST<br>Analog | Digital I/O.<br>AUSART asynchronous receive.<br>AUSART synchronous data (see related TX2/CK2).<br>LCD charge pump capacitor input. |  |  |  |

| RG3/VLCAP2<br>RG3<br>VLCAP2                                                                                                                                                                                                | 8          | I/O<br>I             | ST<br>Analog             | Digital I/O.<br>LCD charge pump capacitor input.                                                                                   |  |  |  |

| RG4/SEG26<br>RG4<br>SEG26                                                                                                                                                                                                  | 10         | I/O<br>O             | ST<br>Analog             | Digital I/O.<br>SEG26 output for LCD.                                                                                              |  |  |  |

| Legend:TTL= TTL compatible inputCMOS= CMOS compatible input or outputST= Schmitt Trigger input with CMOS levelsAnalog= Analog inputI= InputO= OutputP= PowerOD= Open-Drain (no P diode to VDD) $l^2C^{TM} = l^2C/SMBus$ II |            |                      |                          |                                                                                                                                    |  |  |  |

#### TABLE 1-4: PIC18F8XJ90 PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

## 4.0 POWER-MANAGED MODES

The PIC18F85J90 family devices provide the ability to manage power consumption by simply managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. For the sake of managing power in an application, there are three primary modes of operation:

- Run mode

- Idle mode

- · Sleep mode

These modes define which portions of the device are clocked and at what speed. The Run and Idle modes may use any of the three available clock sources (primary, secondary or internal oscillator block); the Sleep mode does not use a clock source.

The power-managed modes include several power-saving features offered on previous PIC<sup>®</sup> devices. One is the clock switching feature, offered in other PIC18 devices, allowing the controller to use the Timer1 oscillator in place of the primary oscillator. Also included is the Sleep mode, offered by all PIC devices, where all device clocks are stopped.

#### 4.1 Selecting Power-Managed Modes

Selecting a power-managed mode requires two decisions: if the CPU is to be clocked or not and which clock source is to be used. The IDLEN bit (OSCCON<7>) controls CPU clocking, while the SCS<1:0> bits (OSCCON<1:0>) select the clock source. The individual modes, bit settings, clock sources and affected modules are summarized in Table 4-1.

### 4.1.1 CLOCK SOURCES

The SCS<1:0> bits allow the selection of one of three clock sources for power-managed modes. They are:

- the primary clock, as defined by the FOSC<2:0> Configuration bits

- the secondary clock (Timer1 oscillator)

- · the internal oscillator

#### 4.1.2 ENTERING POWER-MANAGED MODES

Switching from one power-managed mode to another begins by loading the OSCCON register. The SCS<1:0> bits select the clock source and determine which Run or Idle mode is to be used. Changing these bits causes an immediate switch to the new clock source, assuming that it is running. The switch may also be subject to clock transition delays. These are discussed in **Section 4.1.3 "Clock Transitions and Status Indicators"** and subsequent sections.

Entry to the power-managed Idle or Sleep modes is triggered by the execution of a SLEEP instruction. The actual mode that results depends on the status of the IDLEN bit.

Depending on the current mode and the mode being switched to, a change to a power-managed mode does not always require setting all of these bits. Many transitions may be done by changing the oscillator select bits, or changing the IDLEN bit, prior to issuing a SLEEP instruction. If the IDLEN bit is already configured correctly, it may only be necessary to perform a SLEEP instruction to switch to the desired mode.

| ., .= == |             |                                                 |         |                                       |                                                                                 |  |  |  |  |  |

|----------|-------------|-------------------------------------------------|---------|---------------------------------------|---------------------------------------------------------------------------------|--|--|--|--|--|

|          | oso         | CON bits                                        | Modul   | e Clocking                            | Augilable Cleak and Occillator Source                                           |  |  |  |  |  |

| Mode     | IDLEN<7>(1) | DLEN<7> <sup>(1)</sup> SCS<1:0> CPU Peripherals |         | Available Clock and Oscillator Source |                                                                                 |  |  |  |  |  |

| Sleep    | 0           | N/A                                             | Off     | Off                                   | None – All clocks are disabled                                                  |  |  |  |  |  |

| PRI_RUN  | N/A         | 10                                              | Clocked | Clocked                               | Primary – HS, EC, HSPLL, ECPLL;<br>this is the normal full-power execution mode |  |  |  |  |  |

| SEC_RUN  | N/A         | 01                                              | Clocked | Clocked                               | Secondary – Timer1 Oscillator                                                   |  |  |  |  |  |

| RC_RUN   | N/A         | 11                                              | Clocked | Clocked                               | Internal Oscillator                                                             |  |  |  |  |  |

| PRI_IDLE | 1           | 10                                              | Off     | Clocked                               | Primary – HS, EC, HSPLL, ECPLL                                                  |  |  |  |  |  |

| SEC_IDLE | 1           | 01                                              | Off     | Clocked                               | Secondary – Timer1 Oscillator                                                   |  |  |  |  |  |

| RC_IDLE  | 1           | 11                                              | Off     | Clocked                               | Internal Oscillator                                                             |  |  |  |  |  |

TABLE 4-1: POWER-MANAGED MODES

**Note 1:** IDLEN reflects its value when the SLEEP instruction is executed.

| TABLE 6-3: | PIC18F85J90 FAMILY REGISTER FILE SUMMARY ( | CONTINUED) | 1 |

|------------|--------------------------------------------|------------|---|

|            |                                            |            |   |

| TABLE 0-3             |                                       | 8282790              |                         | <b>KEGISTE</b>        | K FILE SI            | UIVIIVIART           |                              | IUED)    |                      |                    |

|-----------------------|---------------------------------------|----------------------|-------------------------|-----------------------|----------------------|----------------------|------------------------------|----------|----------------------|--------------------|

| File Name             | Bit 7                                 | Bit 6                | Bit 5                   | Bit 4                 | Bit 3                | Bit 2                | Bit 1                        | Bit 0    | Value on<br>POR, BOR | Details<br>on page |

| TMR0H                 | Timer0 Regis                          | ster High Byte       |                         |                       |                      |                      |                              |          | 0000 0000            | 58, 139            |

| TMR0L                 | Timer0 Regis                          | ster Low Byte        |                         |                       |                      |                      |                              |          | xxxx xxxx            | 58, 139            |

| TOCON                 | TMR00N                                | T08BIT               | TOCS                    | T0SE                  | PSA                  | T0PS2                | T0PS1                        | T0PS0    | 1111 1111            | 58, 137            |

| OSCCON                | IDLEN                                 | IRCF2                | IRCF1                   | IRCF0                 | OSTS                 | IOFS                 | SCS1                         | SCS0     | 0100 q000            | 36, 58             |

| LCDREG                | _                                     | CPEN                 | BIAS2                   | BIAS1                 | BIAS0                | MODE13               | CKSEL1                       | CKSEL0   | -011 1100            | 58, 169            |

| WDTCON                | REGSLP                                | _                    | _                       |                       | _                    | _                    | _                            | SWDTEN   | 00                   | 58, 298            |

| RCON                  | IPEN                                  | _                    | CM                      | RI                    | TO                   | PD                   | POR                          | BOR      | 0-11 11q0            | 52, 58             |

| TMR1H                 | Timer1 Regis                          | ster High Byte       |                         | xxxx xxxx             | 58, 145              |                      |                              |          |                      |                    |

| TMR1L                 | Timer1 Regis                          | ster Low Byte        |                         |                       |                      |                      |                              |          | xxxx xxxx            | 58, 145            |

| T1CON                 | RD16                                  | T1RUN                | T1CKPS1                 | T1CKPS0               | T10SCEN              | T1SYNC               | TMR1CS                       | TMR10N   | 0000 0000            | 58, 141            |

| TMR2                  | Timer2 Regis                          | ster                 |                         |                       |                      |                      |                              |          | 0000 0000            | 58, 148            |

| PR2                   | Timer2 Perio                          | d Register           |                         |                       |                      |                      |                              |          | 1111 1111            | 58, 148            |

| T2CON                 | _                                     | T2OUTPS3             | T2OUTPS2                | T2OUTPS1              | T2OUTPS0             | TMR2ON               | T2CKPS1                      | T2CKPS0  | -000 0000            | 58, 147            |

| SSPBUF                | MSSP Receive Buffer/Transmit Register |                      |                         |                       |                      |                      |                              |          |                      | 58, 199,<br>234    |

| SSPADD                | MSSP Addre                            | ess Register in      | I <sup>2</sup> C™ Slave | mode. MSSP            | 1 Baud Rate F        | Reload Registe       | er in I <sup>2</sup> C Maste | er mode. | 0000 0000            | 58, 234            |

| SSPSTAT               | SMP                                   | CKE                  | D/Ā                     | Р                     | S                    | R/W                  | UA                           | BF       | 0000 0000            | 58, 192,<br>201    |

| SSPCON1               | WCOL                                  | SSPOV                | SSPEN                   | СКР                   | SSPM3                | SSPM2                | SSPM1                        | SSPM0    | 0000 0000            | 58, 193,<br>202    |

| SSPCON2               | GCEN                                  | ACKSTAT              | ACKDT                   | ACKEN                 | RCEN                 | PEN                  | RSEN                         | SEN      | 0000 0000            | 58, 203,           |

|                       | GCEN                                  | ACKSTAT              | ADMSK5(3)               | ADMSK4 <sup>(3)</sup> | ADMSK3(3)            | ADMSK2(3)            | ADMSK1(3)                    | SEN      |                      | 204                |

| ADRESH                | A/D Result R                          | egister High E       | Byte                    |                       | •                    | •                    |                              | •        | xxxx xxxx            | 59, 279            |

| ADRESL                | A/D Result R                          | egister Low B        | yte                     |                       |                      |                      |                              |          | xxxx xxxx            | 59, 279            |

| ADCON0                | ADCAL                                 | _                    | CHS3                    | CHS2                  | CHS1                 | CHS0                 | GO/DONE                      | ADON     | 0-00 0000            | 59, 271            |

| ADCON1                | _                                     | _                    | VCFG1                   | VCFG0                 | PCFG3                | PCFG2                | PCFG1                        | PCFG0    | 00 0000              | 59, 272            |

| ADCON2                | ADFM                                  | _                    | ACQT2                   | ACQT1                 | ACQT0                | ADCS2                | ADCS1                        | ADCS0    | 0-00 0000            | 59, 273            |

| LCDDATA4              | S39C0 <sup>(2)</sup>                  | S38C0 <sup>(2)</sup> | S37C0 <sup>(2)</sup>    | S36C0 <sup>(2)</sup>  | S35C0 <sup>(2)</sup> | S34C0 <sup>(2)</sup> | S33C0 <sup>(2)</sup>         | S32C0    | xxxx xxxx            | 59, 167            |

| LCDDATA3              | S31C0                                 | S30C0                | S29C0                   | S28C0                 | S27C0                | S26C0                | S25C0                        | S24C0    | xxxx xxxx            | 59, 167            |

| LCDDATA2              | S23C0                                 | S22C0                | S21C0                   | S20C0                 | S19C0                | S18C0                | S17C0                        | S16C0    | xxxx xxxx            | 59, 167            |

| LCDDATA1              | S15C0                                 | S14C0                | S13C0                   | S12C0                 | S11C0                | S10C0                | S09C0                        | S08C0    | xxxx xxxx            | 59, 167            |

| LCDDATA0              | S07C0                                 | S06C0                | S05C0                   | S04C0                 | S03C0                | S02C0                | S01C0                        | S00C0    | xxxx xxxx            | 59, 167            |

| LCDSE5 <sup>(2)</sup> | SE47                                  | SE46                 | SE45                    | SE44                  | SE43                 | SE42                 | SE41                         | SE40     | 0000 0000            | 59, 166            |

| LCDSE4                | SE39 <sup>(2)</sup>                   | SE38 <sup>(2)</sup>  | S37 <sup>(2)</sup>      | SE36 <sup>(2)</sup>   | SE35 <sup>(2)</sup>  | SE34 <sup>(2)</sup>  | SE33 <sup>(2)</sup>          | SE32     | 0000 0000            | 59, 166            |

| LCDSE3                | SE31                                  | SE30                 | SE29                    | SE28                  | SE27                 | SE26                 | SE25                         | SE24     | 0000 0000            | 59, 166            |

| LCDSE2                | SE23                                  | SE22                 | SE21                    | SE20                  | SE19                 | SE18                 | SE17                         | SE16     | 0000 0000            | 59, 166            |

| LCDSE1                | SE15                                  | SE14                 | SE13                    | SE12                  | SE11                 | SE10                 | SE09                         | SE08     | 0000 0000            | 59, 166            |

| CVRCON                | CVREN                                 | CVROE                | CVRR                    | CVRSS                 | CVR3                 | CVR2                 | CVR1                         | CVR0     | 0000 0000            | 59, 287            |

| CMCON                 | C2OUT                                 | C1OUT                | C2INV                   | C1INV                 | CIS                  | CM2                  | CM1                          | CM0      | 0000 0111            | 59, 281            |

| TMR3H                 | Timer3 Regis                          | ster High Byte       |                         |                       |                      |                      |                              |          | xxxx xxxx            | 59, 151            |

| TMR3L                 | Timer3 Regis                          | ster Low Byte        |                         |                       |                      |                      |                              |          | xxxx xxxx            | 59, 151            |

| T3CON                 | RD16                                  | T3CCP2               | T3CKPS1                 | T3CKPS0               | T3CCP1               | T3SYNC               | TMR3CS                       | TMR3ON   | 0000 0000            | 59, 149            |

**Legend:** x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved, do not modify

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: These registers and/or bits are available only on 80-pin devices; otherwise, they are unimplemented and read as '0'. Reset states shown are for 80-pin devices.

3: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C<sup>™</sup> Slave mode. See Section 17.4.3.2 "Address Masking" for details.

4: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 3.4.3 "PLL Frequency Multiplier" for details.

5: RA6/RA7 and their associated latch and direction bits are configured as port pins only when the internal oscillator is selected as the default clock source (FOSC2 Configuration bit = 0); otherwise, they are disabled and these bits read as '0'.

| R/W-1      | R/W-1                                       | R/W-1                              | R/W-1             | R/W-1             | R/W-1            | R/W-1            | R/W-1         |  |  |  |

|------------|---------------------------------------------|------------------------------------|-------------------|-------------------|------------------|------------------|---------------|--|--|--|

| RBPU       | INTEDG0                                     | INTEDG1                            | INTEDG2           | INTEDG3           | TMR0IP           | INT3IP           | RBIP          |  |  |  |

| bit 7      |                                             |                                    |                   |                   |                  |                  | bit C         |  |  |  |

|            |                                             |                                    |                   |                   |                  |                  |               |  |  |  |

| Legend:    |                                             |                                    |                   |                   |                  |                  |               |  |  |  |

| R = Read   |                                             | W = Writable                       | bit               | •                 | nented bit, read |                  |               |  |  |  |

| -n = Value | e at POR                                    | '1' = Bit is set                   |                   | '0' = Bit is clea | ared             | x = Bit is unkn  | iown          |  |  |  |

| bit 7      | <b>RBPU</b> : PORT                          | B Pull-up Enat                     | ole bit           |                   |                  |                  |               |  |  |  |

|            |                                             | B pull-ups are                     |                   |                   |                  |                  |               |  |  |  |

|            | 0 = PORTB p                                 | oull-ups are ena                   | abled by individ  | lual port latch v | alues            |                  |               |  |  |  |

| bit 6      | INTEDG0: Ex                                 | ternal Interrupt                   | 0 Edge Select     | bit               |                  |                  |               |  |  |  |

|            |                                             | on rising edge                     |                   |                   |                  |                  |               |  |  |  |

|            | •                                           | on falling edge                    |                   |                   |                  |                  |               |  |  |  |

| bit 5      |                                             | ternal Interrupt                   | 1 Edge Select     | bit               |                  |                  |               |  |  |  |

|            |                                             | on rising edge on falling edge     |                   |                   |                  |                  |               |  |  |  |

| bit 4      | •                                           | •••                                | 2 Edge Soled      | hit.              |                  |                  |               |  |  |  |

| DIL 4      |                                             | ternal Interrupt<br>on rising edge | 2 Euge Select     | DIL               |                  |                  |               |  |  |  |

|            | •                                           | on falling edge                    |                   |                   |                  |                  |               |  |  |  |

| bit 3      | •                                           | ternal Interrupt                   | 3 Edge Select     | bit               |                  |                  |               |  |  |  |

|            |                                             | on rising edge                     | 0                 |                   |                  |                  |               |  |  |  |

|            | 0 = Interrupt on falling edge               |                                    |                   |                   |                  |                  |               |  |  |  |

| bit 2      | TMR0IP: TMF                                 | R0 Overflow Int                    | errupt Priority   | bit               |                  |                  |               |  |  |  |

|            | 1 = High prio                               | •                                  |                   |                   |                  |                  |               |  |  |  |

|            | 0 = Low prior                               | -                                  |                   |                   |                  |                  |               |  |  |  |

| bit 1      |                                             | External Interro                   | upt Priority bit  |                   |                  |                  |               |  |  |  |

|            | 1 = High prio<br>0 = Low prior              |                                    |                   |                   |                  |                  |               |  |  |  |

| bit 0      |                                             |                                    | rupt Drigrity bit |                   |                  |                  |               |  |  |  |

| DILU       | 1 = High prio                               | rt Change Inter                    |                   |                   |                  |                  |               |  |  |  |

|            | 0 = Low prior                               |                                    |                   |                   |                  |                  |               |  |  |  |

| Note:      | Interrupt flag bits                         | are set when a                     | an interrupt co   | ndition occurs    | regardless of t  | he state of its  | corresponding |  |  |  |

|            | enable bit or the g<br>are clear prior to g | global interrupt                   | enable bit. Use   | er software sho   | uld ensure the   | appropriate inte |               |  |  |  |

#### REGISTER 9-2: INTCON2: INTERRUPT CONTROL REGISTER 2

## 15.0 CAPTURE/COMPARE/PWM (CCP) MODULES

PIC18F85J90 family devices have two CCP (Capture/Compare/PWM) modules, designated CCP1 and CCP2. Both modules implement standard Capture, Compare and Pulse-Width Modulation (PWM) modes.

Each CCP module contains a 16-bit register which can operate as a 16-bit Capture register, a 16-bit Compare register or a PWM Master/Slave Duty Cycle register. For the sake of clarity, all CCP module operation in the following sections is described with respect to CCP2, but is equally applicable to CCP1.

#### **REGISTER 15-1: CCPxCON: CCPx CONTROL REGISTER (CCP1, CCP2 MODULES)**

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-------|-----|-------|-------|--------|--------|--------|--------|

| —     | —   | DCxB1 | DCxB0 | CCPxM3 | CCPxM2 | CCPxM1 | CCPxM0 |

| bit 7 |     |       |       |        |        |        | bit 0  |

|       |     |       |       |        |        |        |        |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7-6 | Unimplemented: Read as '0'                                                                                                                                                      |  |  |  |  |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 5-4 | DCxB<1:0>: PWM Duty Cycle bit 1 and bit 0 for CCPx Module                                                                                                                       |  |  |  |  |  |  |

|         | Capture mode:                                                                                                                                                                   |  |  |  |  |  |  |

|         | Unused.                                                                                                                                                                         |  |  |  |  |  |  |

|         | Compare mode:                                                                                                                                                                   |  |  |  |  |  |  |

|         | Unused.                                                                                                                                                                         |  |  |  |  |  |  |

|         | PWM mode:                                                                                                                                                                       |  |  |  |  |  |  |

|         | These bits are the two Least Significant bits (bit 1 and bit 0) of the 10-bit PWM duty cycle. The eight Most Significant bits (DCx<9:2>) of the duty cycle are found in CCPRxL. |  |  |  |  |  |  |

| bit 3-0 | CCPxM<3:0>: CCPx Module Mode Select bits                                                                                                                                        |  |  |  |  |  |  |

|         | 0000 = Capture/Compare/PWM disabled (resets CCPx module)                                                                                                                        |  |  |  |  |  |  |

|         | 0001 = Reserved                                                                                                                                                                 |  |  |  |  |  |  |

|         | 0010 = Compare mode, toggle output on match (CCPxIF bit is set)                                                                                                                 |  |  |  |  |  |  |

|         | 0011 = Reserved                                                                                                                                                                 |  |  |  |  |  |  |

|         | 0100 = Capture mode, every falling edge                                                                                                                                         |  |  |  |  |  |  |

|         | 0101 = Capture mode, every rising edge                                                                                                                                          |  |  |  |  |  |  |

|         | 0110 = Capture mode, every 4th rising edge                                                                                                                                      |  |  |  |  |  |  |

|         | 0111 = Capture mode, every 16th rising edge                                                                                                                                     |  |  |  |  |  |  |

|         | 1000 = Compare mode: initialize CCPx pin low; on compare match, force CCPx pin high (CCPxIF bit<br>is set)                                                                      |  |  |  |  |  |  |

|         | 1001 = Compare mode: initialize CCPx pin high; on compare match, force CCPx pin low (CCPxIF bit is set)                                                                         |  |  |  |  |  |  |

|         | 1010 = Compare mode: generate software interrupt on compare match (CCPxIF bit is set, CCPx pin<br>reflects I/O state)                                                           |  |  |  |  |  |  |

|         | 1011 = Compare mode: Special Event Trigger; reset timer; start A/D conversion on CCPx match<br>(CCPxIF bit is set) <sup>(1)</sup>                                               |  |  |  |  |  |  |

|         | 11xx = PWM mode                                                                                                                                                                 |  |  |  |  |  |  |

### 16.1.2 LCD DATA REGISTERS

Once the module is initialized for the LCD panel, the individual bits of the LCDDATA23:LCDDATA0 registers are cleared or set to represent a clear or dark pixel, respectively. Specific sets of LCDDATA registers are used with specific segments and common signals. Each bit represents a unique combination of a specific segment connected to a specific common.

Individual LCDDATA bits are named by the convention "SxxCy", with "xx" as the segment number and "y" as the common number. The relationship is summarized in Table 16-2. The prototype LCDDATA register is shown in Register 16-4.

Note: In 64-pin devices, writing into the registers LCDDATA5, LCDDATA11, LCDDATA17, and LCDDATA23 will not affect the status of any pixels.

#### REGISTER 16-4: LCDDATAX: LCD DATA REGISTERS

| R/W-0      | R/W-0  |

|------------|------------|------------|------------|------------|------------|------------|--------|

| S(n + 7)Cy | S(n + 6)Cy | S(n + 5)Cy | S(n + 4)Cy | S(n + 3)Cy | S(n + 2)Cy | S(n + 1)Cy | S(n)Cy |

| bit 7      |            |            |            |            |            |            | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7-0 | S(n + 7)Cy:S(n)Cy: Pixel On bits                                    |

|---------|---------------------------------------------------------------------|

|         | For LCDDATA0 through LCDDATA5: n = (8x), y = 0                      |

|         | <u>For LCDDATA6 through LCDDATA11: n = (8(x – 6)), y = 1</u>        |

|         | <u>For LCDDATA12 through LCDDATA17: n = (8(x – 12)), y = 2</u>      |

|         | <u>For LCDDATA18 through LCDDATA23: n = (8(x – 18)), y = 3</u>      |

|         | <ul><li>1 = Pixel on (dark)</li><li>0 = Pixel off (clear)</li></ul> |

#### TABLE 16-2: LCDDATA REGISTERS AND BITS FOR SEGMENT AND COM COMBINATIONS

| Sogmonto      | COM Lines               |                          |                          |                          |  |  |  |

|---------------|-------------------------|--------------------------|--------------------------|--------------------------|--|--|--|

| Segments      | 0                       | 1                        | 2                        | 3                        |  |  |  |

| 0 through 7   | LCDDATA0                | LCDDATA6                 | LCDDATA12                | LCDDATA18                |  |  |  |

| 0 through 7   | S00C0:S07C0             | S00C1:S07C1              | S00C2:S07C2              | S00C3:S07C3              |  |  |  |

| 8 through 15  | LCDDATA1                | LCDDATA7                 | LCDDATA13                | LCDDATA19                |  |  |  |

| o unough 15   | S08C0:S15C0             | S08C1:S15C1              | S08C2:S15C2              | S08C0:S15C3              |  |  |  |

| 16 through 22 | LCDDATA2                | LCDDATA8                 | LCDDATA14                | LCDDATA20                |  |  |  |

| 16 through 23 | S16C0:S23C0             | S16C1:S23C1              | S16C2:S23C2              | S16C3:S23C3              |  |  |  |

| 24 through 21 | LCDDATA3                | LCDDATA9                 | LCDDATA15                | LCDDATA21                |  |  |  |

| 24 through 31 | S24C0:S31C0             | S24C1:S31C1              | S24C2:S31C2              | S24C3:S31C3              |  |  |  |

| 22 through 20 | LCDDATA4 <sup>(1)</sup> | LCDDATA10 <sup>(1)</sup> | LCDDATA16 <sup>(1)</sup> | LCDDATA22 <sup>(1)</sup> |  |  |  |

| 32 through 39 | S32C0:S39C0             | S32C1:S39C1              | S32C2:S39C2              | S32C3:S39C3              |  |  |  |

| 40 through 47 | LCDDATA5 <sup>(2)</sup> | LCDDATA11 <sup>(2)</sup> | LCDDATA17 <sup>(2)</sup> | LCDDATA23 <sup>(2)</sup> |  |  |  |

| 40 tinough 47 | S40C0:S47C0             | S40C1:S47C1              | S40C2:S47C2              | S40C3:S47C3              |  |  |  |

**Note 1:** Bits<7:1> of these registers are not implemented in 64-pin devices. Bit 0 of these registers (SEG32Cy) is always implemented.

2: These registers are not implemented on 64-pin devices.

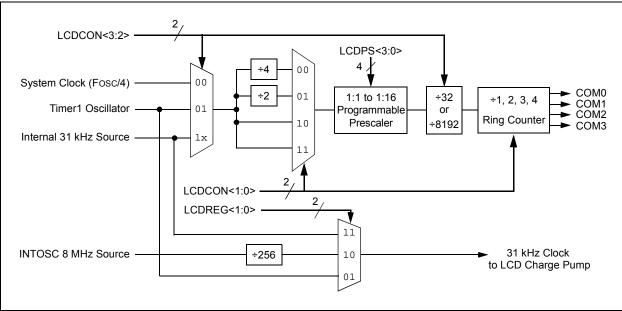

## 16.2 LCD Clock Source

The LCD driver module generates its internal clock from 3 possible sources:

- System clock (Fosc/4)

- · Timer1 oscillator

- INTRC source

The LCD clock generator uses a configurable divide-by-32/divide-by-8192 postscaler to produce a baseline frequency of about 1 kHz nominal, regardless of the source selected. The clock source selection and the postscaler configuration are determined by the Clock Source Select bits, CS<1:0> (LCDCON<3:2>).

An additional programmable prescaler is used to derive the LCD frame frequency from the 1 kHz baseline. The prescaler is configured using the LP<3:0> bits (LCDPS<3:0>) for any one of 16 options, ranging from 1:1 to 1:16.

Proper timing for waveform generation is set by the LMUX<1:0> bits (LCDCON<1:0>). These bits determine which Commons Multiplexing mode is to be used, and divide down the LCD clock source as required. They also determine the configuration of the ring counter that is used to switch the LCD commons on or off.

#### 16.2.1 LCD VOLTAGE REGULATOR CLOCK SOURCE

In addition to the clock source for LCD timing, a separate 31 kHz nominal clock is required for the LCD charge pump. This is provided from a distinct branch of the LCD clock source.

The charge pump clock can use either the Timer1 oscillator or the INTRC source, as well as the 8 MHz INTOSC source (after being divided by 256 by a prescaler). The charge pump clock source is configured using the CKSEL<1:0> bits (LCDREG<1:0>).

#### 16.2.2 CLOCK SOURCE CONSIDERATIONS

When using the system clock as the LCD clock source, it is assumed that the system clock frequency is a nominal 32 MHz (for a Fosc/4 frequency of 8 MHz). Because the prescaler option for the Fosc/4 clock selection is fixed at divide-by-8192, system clock speeds that differ from 32 MHz will produce frame frequencies and refresh rates different than discussed in this chapter. The user will need to keep this in mind when designing the display application.

The Timer1 and INTRC sources can be used as LCD clock sources when the device is in Sleep mode. To use the Timer1 oscillator, it is necessary to set the T1OSCEN bit (T1CON<3>). Selecting either Timer1 or INTRC as the LCD clock source will not automatically activate these sources.

Similarly, selecting the INTOSC as the charge pump clock source will not turn the oscillator on. To use INTOSC, it must be selected as the system clock source by using the FOSC2 Configuration bit.

If Timer1 is used as a clock source for the device, either as an LCD clock source or for any other purpose, LCD segment 32 become unavailable.

#### FIGURE 16-2: LCD CLOCK GENERATION

NOTES:

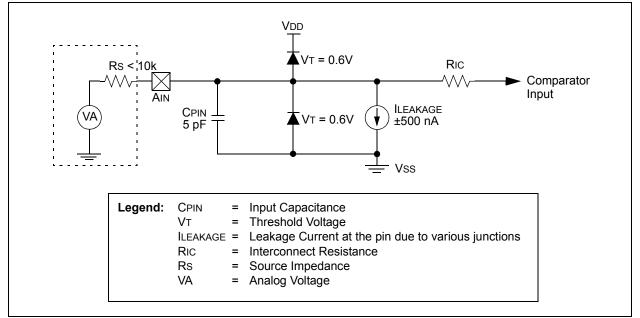

### 21.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 21-4. Since the analog pins are connected to a digital output, they have reverse biased diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this

range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up condition may occur. A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current.

FIGURE 21-4: COMPARATOR ANALOG INPUT MODEL

#### TABLE 21-1: REGISTERS ASSOCIATED WITH COMPARATOR MODULE

| Name   | Bit 7    | Bit 6     | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | Reset<br>Values<br>on page |

|--------|----------|-----------|--------|--------|--------|--------|--------|-------|----------------------------|

| INTCON | GIE/GIEH | PEIE/GIEL | TMR0IE | INT0IE | RBIE   | TMR0IF | INT0IF | RBIF  | 57                         |

| PIR2   | OSCFIF   | CMIF      |        | —      | BCLIF  | LVDIF  | TMR3IF | _     | 60                         |

| PIE2   | OSCFIE   | CMIE      |        | —      | BCLIE  | LVDIE  | TMR3IE | _     | 60                         |

| IPR2   | OSCFIP   | CMIP      | _      | _      | BCLIP  | LVDIP  | TMR3IP |       | 60                         |

| CMCON  | C2OUT    | C10UT     | C2INV  | C1INV  | CIS    | CM2    | CM1    | CM0   | 59                         |

| CVRCON | CVREN    | CVROE     | CVRR   | CVRSS  | CVR3   | CVR2   | CVR1   | CVR0  | 59                         |

| PORTF  | RF7      | RF6       | RF5    | RF4    | RF3    | RF2    | RF1    | _     | 60                         |

| LATF   | LATF7    | LATF6     | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  |       | 60                         |

| TRISF  | TRISF7   | TRISF6    | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | _     | 60                         |

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the comparator module.

#### REGISTER 23-8: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| R/W-0                 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0                 |

|-----------------------|-----|-----|-----|-----|-----|-----|-----------------------|

| REGSLP <sup>(1)</sup> | —   | —   | —   | —   | —   |     | SWDTEN <sup>(2)</sup> |

| bit 7                 |     |     |     |     |     |     | bit 0                 |

|                       |     |     |     |     |     |     |                       |

| Legend:               |     |     |     |     |     |     |                       |

| =ogonan           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 7                                 | REGSLP: Voltage Regulator Low-Power Operation Enable bit <sup>(1)</sup>                                                                                                       |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | <ul> <li>1 = On-chip regulator enters low-power operation when device enters Sleep mode</li> <li>0 = On-chip regulator continues to operate normally in Sleep mode</li> </ul> |

| bit 6-1                               | Unimplemented: Read as '0'                                                                                                                                                    |

| bit 0                                 | SWDTEN: Software Controlled Watchdog Timer Enable bit <sup>(2)</sup>                                                                                                          |

|                                       | 1 = Watchdog Timer is on                                                                                                                                                      |

|                                       | 0 = Watchdog Timer is off                                                                                                                                                     |

| · · · · · · · · · · · · · · · · · · · |                                                                                                                                                                               |

**Note 1:** The REGSLP bit is automatically cleared when a Low-Voltage Detect condition occurs.

2: This bit has no effect if the Configuration bit, WDTEN, is enabled.

TABLE 23-3: SUMMARY OF WATCHDOG TIMER REGISTERS

| Name   | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  | Reset Values<br>on page |

|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------------------------|

| RCON   | IPEN   | _     | CM    | RI    | TO    | PD    | POR   | BOR    | 58                      |

| WDTCON | REGSLP | _     | _     | _     | _     | _     |       | SWDTEN | 58                      |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Watchdog Timer.

| CPFS                                                                                                                                                                                                                                                             | SGT                  | Compare f                                  | with W, Skip                                                                                                            | if f > W                  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|

| Synta                                                                                                                                                                                                                                                            | ax:                  | CPFSGT                                     | CPFSGT f {,a}                                                                                                           |                           |  |  |  |  |

| Oper                                                                                                                                                                                                                                                             | ands:                | $0 \leq f \leq 255$                        |                                                                                                                         |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                  |                      | a ∈ [0,1]                                  |                                                                                                                         |                           |  |  |  |  |

| Oper                                                                                                                                                                                                                                                             | ation:               | (f) – (W),<br>skip if (f) ><br>(unsigned o | (W)<br>comparison)                                                                                                      |                           |  |  |  |  |

| Statu                                                                                                                                                                                                                                                            | s Affected:          | None                                       |                                                                                                                         |                           |  |  |  |  |

| Enco                                                                                                                                                                                                                                                             | dina:                | 0110                                       | 010a fff                                                                                                                | f ffff                    |  |  |  |  |

|                                                                                                                                                                                                                                                                  | ription:             | location 'f'                               | Compares the contents of data memory<br>location 'f' to the contents of the W by<br>performing an unsigned subtraction. |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                  |                      | contents of<br>instruction                 | nts of 'f' are gro<br>WREG, then t<br>is discarded ar<br>istead, making<br>istruction.                                  | he fetched<br>nd a NOP is |  |  |  |  |

|                                                                                                                                                                                                                                                                  |                      |                                            | he Access Bar<br>he BSR is use                                                                                          |                           |  |  |  |  |

| If 'a' is '0' and the extended instru<br>set is enabled, this instruction op<br>in Indexed Literal Offset Address<br>mode whenever f ≤ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented a<br>Bit-Oriented Instructions in Ind<br>Literal Offset Mode" for details. |                      |                                            |                                                                                                                         |                           |  |  |  |  |

| Word                                                                                                                                                                                                                                                             | s:                   | 1                                          |                                                                                                                         |                           |  |  |  |  |

| Cycle                                                                                                                                                                                                                                                            |                      |                                            | cycles if skip ar<br>a 2-word instru                                                                                    |                           |  |  |  |  |

| QC                                                                                                                                                                                                                                                               | ycle Activity:<br>Q1 | Q2                                         | Q3                                                                                                                      | Q4                        |  |  |  |  |

|                                                                                                                                                                                                                                                                  | Decode               | Read                                       | Process                                                                                                                 | No                        |  |  |  |  |

|                                                                                                                                                                                                                                                                  | Decode               | register 'f'                               | Data                                                                                                                    | operation                 |  |  |  |  |

| lf sk                                                                                                                                                                                                                                                            | ip:                  | Ŭ                                          |                                                                                                                         |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                  | Q1                   | Q2                                         | Q3                                                                                                                      | Q4                        |  |  |  |  |

|                                                                                                                                                                                                                                                                  | No                   | No                                         | No                                                                                                                      | No                        |  |  |  |  |

|                                                                                                                                                                                                                                                                  | operation            | operation                                  | operation                                                                                                               | operation                 |  |  |  |  |

| IT SK                                                                                                                                                                                                                                                            | ip and followe       |                                            |                                                                                                                         | Q4                        |  |  |  |  |

| 1                                                                                                                                                                                                                                                                | Q1<br>No             | Q2<br>No                                   | Q3<br>No                                                                                                                | No                        |  |  |  |  |

|                                                                                                                                                                                                                                                                  | operation            | operation                                  | operation                                                                                                               | operation                 |  |  |  |  |

|                                                                                                                                                                                                                                                                  | No                   | No                                         | No                                                                                                                      | No                        |  |  |  |  |

|                                                                                                                                                                                                                                                                  | operation            | operation                                  | operation                                                                                                               | operation                 |  |  |  |  |

| <u>Exan</u>                                                                                                                                                                                                                                                      | <u>iple:</u>         | HERE<br>NGREATER<br>GREATER                | CPFSGT RE                                                                                                               | G, 0                      |  |  |  |  |

|                                                                                                                                                                                                                                                                  | Before Instruc       |                                            |                                                                                                                         |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                  | PC<br>W              | = Ac<br>= ?                                | dress (HERE                                                                                                             | )                         |  |  |  |  |

|                                                                                                                                                                                                                                                                  | After Instructio     | -                                          |                                                                                                                         |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                  | If REG               | > W                                        |                                                                                                                         |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                  | PC<br>If REG<br>PC   | = Ac<br>≤ W                                | ldress (GREA<br>;<br>ldress (NGREA                                                                                      |                           |  |  |  |  |

|                                                                                                                                                                                                                                                                  |                      |                                            |                                                                                                                         |                           |  |  |  |  |

| CPFSLT                                                                                                                                                                          |                              | Compare f with W, Skip if f < W                          |                                                  |                                      |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------------------------------------------------------|--------------------------------------------------|--------------------------------------|--|--|--|

| Syntax:                                                                                                                                                                         |                              | CPFSLT                                                   | f {,a}                                           |                                      |  |  |  |

| Operands                                                                                                                                                                        | S:                           | 0 ≤ f ≤ 255<br>a ∈ [0,1]                                 |                                                  |                                      |  |  |  |

| Operation                                                                                                                                                                       | ו:                           | (f) – (W),<br>skip if (f) < (W)<br>(unsigned comparison) |                                                  |                                      |  |  |  |

| Status Af                                                                                                                                                                       | fected:                      | None                                                     |                                                  |                                      |  |  |  |

| Encoding                                                                                                                                                                        | J:                           | 0110                                                     | 000a fi                                          | fff ffff                             |  |  |  |

| Descriptio                                                                                                                                                                      | on:                          | location 'f'                                             | the contents of<br>to the content<br>an unsigned | •                                    |  |  |  |

| If the contents of 'f' are less than th<br>contents of W, then the fetched<br>instruction is discarded and a NOP i<br>executed instead, making this a<br>two-cycle instruction. |                              |                                                          |                                                  |                                      |  |  |  |

|                                                                                                                                                                                 |                              | -                                                        | he BSR is us                                     | ank is selected.<br>ed to select the |  |  |  |

| Words:                                                                                                                                                                          |                              | 1                                                        |                                                  |                                      |  |  |  |

| Cycles:                                                                                                                                                                         |                              |                                                          | ycles if skip a<br>a 2-word instr                |                                      |  |  |  |

| Q Cycle                                                                                                                                                                         | Activity:                    |                                                          |                                                  |                                      |  |  |  |

|                                                                                                                                                                                 | Q1                           | Q2                                                       | Q3                                               | Q4                                   |  |  |  |