Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                             |

| Number of I/O              | 51                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f64j90t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

| Features                               | PIC18F63J90                                                                     | PIC18F63J90 PIC18F64J90   |          |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------|---------------------------|----------|--|--|--|

| Operating Frequency                    | DC – 40 MHz                                                                     |                           |          |  |  |  |

| Program Memory (Bytes)                 | 8K                                                                              | 16K                       | 32K      |  |  |  |

| Program Memory (Instructions)          | 4096                                                                            | 8192                      | 16384    |  |  |  |

| Data Memory (Bytes)                    | 1024                                                                            | 1024                      | 2048     |  |  |  |

| Interrupt Sources                      |                                                                                 | 27                        |          |  |  |  |

| I/O Ports                              |                                                                                 | Ports A, B, C, D, E, F, G |          |  |  |  |

| LCD Driver (available pixels to drive) | 132 (33 SEGs x 4 COMs)                                                          |                           |          |  |  |  |

| Timers                                 |                                                                                 | 4                         |          |  |  |  |

| Capture/Compare/PWM Modules            |                                                                                 | 2                         |          |  |  |  |

| Serial Communications                  | MSSP, Ad                                                                        | dressable USART, Enhanc   | ed USART |  |  |  |

| 10-Bit Analog-to-Digital Module        |                                                                                 | 12 Input Channels         |          |  |  |  |

| Resets (and Delays)                    | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WDT (PWRT, OST) |                           |          |  |  |  |

| Instruction Set                        | 75 Instructions, 83 with Extended Instruction Set enabled                       |                           |          |  |  |  |

| Packages                               |                                                                                 | 64-pin TQFP               |          |  |  |  |

## TABLE 1-1: DEVICE FEATURES FOR THE PIC18F85J90 FAMILY (64-PIN DEVICES)

#### TABLE 1-2: DEVICE FEATURES FOR THE PIC18F85J90 FAMILY (80-PIN DEVICES)

| Features                               | PIC18F83J90                                                                     | PIC18F84J90                     | PIC18F85J90 |  |  |  |

|----------------------------------------|---------------------------------------------------------------------------------|---------------------------------|-------------|--|--|--|

| Operating Frequency                    | DC – 40 MHz                                                                     |                                 |             |  |  |  |

| Program Memory (Bytes)                 | 8K                                                                              | 16K                             | 32K         |  |  |  |

| Program Memory (Instructions)          | 4096                                                                            | 8192                            | 16384       |  |  |  |

| Data Memory (Bytes)                    | 1024                                                                            | 1024                            | 2048        |  |  |  |

| Interrupt Sources                      |                                                                                 | 27                              | ·           |  |  |  |

| I/O Ports                              | F                                                                               | Ports A, B, C, D, E, F, G, H, J |             |  |  |  |

| LCD Driver (available pixels to drive) | 192 (48 SEGs x 4 COMs)                                                          |                                 |             |  |  |  |

| Timers                                 |                                                                                 | 4                               |             |  |  |  |

| Capture/Compare/PWM Modules            |                                                                                 | 2                               |             |  |  |  |

| Serial Communications                  | MSSP, Ad                                                                        | dressable USART, Enhand         | xed USART   |  |  |  |

| 10-Bit Analog-to-Digital Module        |                                                                                 | 12 Input Channels               |             |  |  |  |

| Resets (and Delays)                    | POR, BOR, RESET Instruction, Stack Full, Stack Underflow, MCLR, WDT (PWRT, OST) |                                 |             |  |  |  |

| Instruction Set                        | Set 75 Instructions, 83 with Extended Instruction Set enabled                   |                                 |             |  |  |  |

| Packages                               |                                                                                 | 80-pin TQFP                     |             |  |  |  |

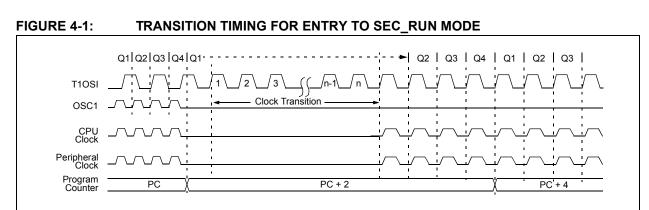

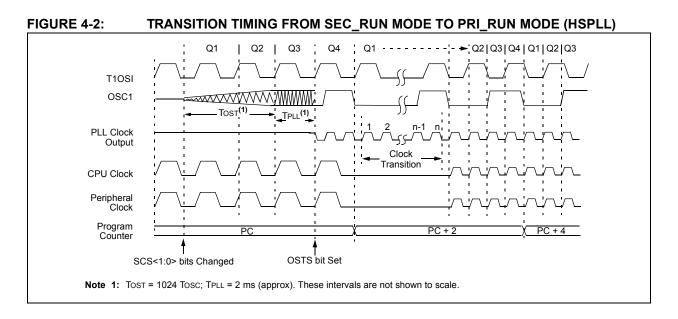

Note: The Timer1 oscillator should already be running prior to entering SEC\_RUN mode. If the T1OSCEN bit is not set when the SCS<1:0> bits are set to '01', entry to SEC\_RUN mode will not occur. If the Timer1 oscillator is enabled, but not yet running, device clocks will be delayed until the oscillator has started. In such situations, initial oscillator operation is far from stable and unpredictable operation may result. On transitions from SEC\_RUN mode to PRI\_RUN mode, the peripherals and CPU continue to be clocked from the Timer1 oscillator while the primary clock is started. When the primary clock becomes ready, a clock switch back to the primary clock occurs (see Figure 4-2). When the clock switch is complete, the T1RUN bit is cleared, the OSTS bit is set and the primary clock is providing the clock. The IDLEN and SCS bits are not affected by the wake-up; the Timer1 oscillator continues to run.

A CM Reset behaves similarly to a Master Clear Reset, RESET instruction, WDT time-out or Stack Event Resets. As with all hard and power Reset events, the device Configuration Words are reloaded from the Flash Configuration Words in program memory as the device restarts.

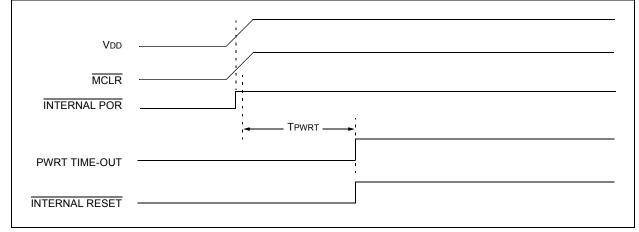

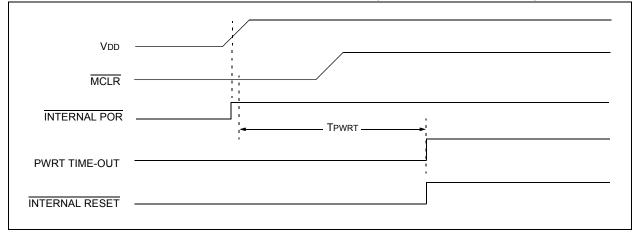

## 5.6 Power-up Timer (PWRT)

PIC18F85J90 family devices incorporate an on-chip Power-up Timer (PWRT) to help regulate the Power-on Reset process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F85J90 family devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset. The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 for details.

## 5.6.1 TIME-OUT SEQUENCE

If enabled, the PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-3, Figure 5-4, Figure 5-5 and Figure 5-6 all depict time-out sequences on power-up with the Power-up Timer enabled.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the PWRT will expire. Bringing MCLR high will begin execution immediately (Figure 5-5). This is useful for testing purposes, or to synchronize more than one PIC18FXXXX device operating in parallel.

#### FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

| Pin Name        | Function | TRIS<br>Setting | I/O | l/O<br>Type          | Description                                              |  |

|-----------------|----------|-----------------|-----|----------------------|----------------------------------------------------------|--|

| RH0/SEG47       | RH0      | 0               | 0   | DIG                  | LATH<0> data output.                                     |  |

|                 |          | 1               | I   | ST                   | PORTH<0> data input.                                     |  |

|                 | SEG47    | x               | 0   | ANA                  | LCD Segment 47 output; disables all other pin functions. |  |

| RH1/SEG46       | RH1      | 0               | 0   | DIG                  | LATH<1> data output.                                     |  |

|                 |          | 1               | Ι   | ST                   | PORTH<1> data input.                                     |  |

|                 | SEG46    | x               | 0   | ANA                  | LCD Segment 46 output; disables all other pin functions. |  |

| RH2/SEG45       | RH2      | 0               | 0   | DIG                  | LATH<2> data output.                                     |  |

|                 |          | 1               | Ι   | ST                   | ST PORTH<2> data input.                                  |  |

|                 | SEG45    | x               | 0   | ANA                  | LCD Segment 45 output; disables all other pin functions. |  |

| RH3/SEG44 RH3 0 |          | 0               | DIG | LATH<3> data output. |                                                          |  |

|                 |          | 1               | Ι   | ST                   | PORTH<3> data input.                                     |  |

|                 | SEG44    | x               | 0   | ANA                  | LCD Segment 44 output; disables all other pin functions. |  |

| RH4/SEG40       | RH4      | 0               | 0   | DIG                  | LATH<4> data output.                                     |  |

|                 |          | 1               | -   | ST                   | PORTH<4> data input.                                     |  |

|                 | SEG40    | x               | 0   | ANA                  | LCD Segment 40 output; disables all other pin functions. |  |

| RH5/SEG41       | RH5      | 0               | 0   | DIG                  | LATH<5> data output.                                     |  |

|                 |          | 1               |     | ST                   | PORTH<5> data input.                                     |  |

|                 | SEG41    | x               | 0   | ANA                  | LCD Segment 41 output; disables all other pin functions. |  |

| RH6/SEG42       | RH6      | 0               | 0   | DIG                  | LATH<6> data output.                                     |  |

|                 |          | 1               | Ι   | ST                   | PORTH<6> data input.                                     |  |

|                 | SEG42    | x               | 0   | ANA                  | LCD Segment 42 output; disables all other pin functions. |  |

| RH7/SEG43       | RH7      | 0               | 0   | DIG                  | LATH<7> data output.                                     |  |

|                 |          | 1               | Ι   | ST                   | PORTH<7> data input.                                     |  |

|                 | SEG43    | x               | 0   | ANA                  | LCD Segment 43 output; disables all other pin functions. |  |

## TABLE 10-18: PORTH FUNCTIONS

Legend: O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, x = Don't care (TRIS bit does not affect port direction or is overridden for this option).

| Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|--------|--------|--------|--------|--------|--------|--------|--------|--------|----------------------------|

| PORTH  | RH7    | RH6    | RH5    | RH4    | RH3    | RH2    | RH1    | RH0    | 60                         |

| LATH   | LATH7  | LATH6  | LATH5  | LATH4  | LATH3  | LATH2  | LATH1  | LATH0  | 60                         |

| TRISH  | TRISH7 | TRISH6 | TRISH5 | TRISH4 | TRISH3 | TRISH2 | TRISH1 | TRISH0 | 60                         |

| LCDSE5 | SE47   | SE46   | SE45   | SE44   | SE43   | SE42   | SE41   | SE40   | 59                         |

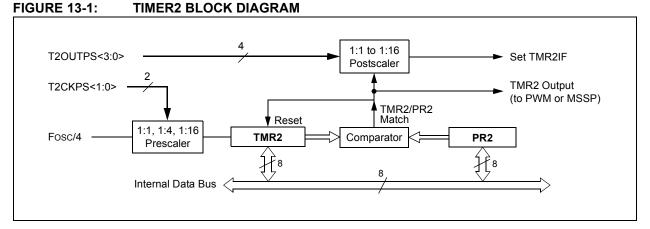

## 13.2 Timer2 Interrupt

Timer2 can also generate an optional device interrupt. The Timer2 output signal (TMR2 to PR2 match) provides the input for the 4-bit output counter/postscaler. This counter generates the TMR2 match interrupt flag which is latched in TMR2IF (PIR1<1>). The interrupt is enabled by setting the TMR2 Match Interrupt Enable bit, TMR2IE (PIE1<1>).

A range of 16 postscale options (from 1:1 through 1:16 inclusive) can be selected with the postscaler control bits, T2OUTPS<3:0> (T2CON<6:3>).

## 13.3 Timer2 Output

The unscaled output of TMR2 is available primarily to the CCP modules, where it is used as a time base for operations in PWM mode.

Timer2 can be optionally used as the shift clock source for the MSSP module operating in SPI mode. Additional information is provided in Section 17.0 "Master Synchronous Serial Port (MSSP) Module".

## TABLE 13-1: REGISTERS ASSOCIATED WITH TIMER2 AS A TIMER/COUNTER

| TABLE 13-1. REGISTERS ASSOCIATED WITH TIMERZ AS A TIMERCOUNTER |                 |              |          |          |          |        |         |         |                            |

|----------------------------------------------------------------|-----------------|--------------|----------|----------|----------|--------|---------|---------|----------------------------|

| Name                                                           | Bit 7           | Bit 6        | Bit 5    | Bit 4    | Bit 3    | Bit 2  | Bit 1   | Bit 0   | Reset<br>Values<br>on page |

| INTCON                                                         | GIE/GIEH        | PEIE/GIEL    | TMR0IE   | INT0IE   | RBIE     | TMR0IF | INT0IF  | RBIF    | 57                         |

| PIR1                                                           | _               | ADIF         | RC1IF    | TX1IF    | SSPIF    | _      | TMR2IF  | TMR1IF  | 60                         |

| PIE1                                                           | _               | ADIE         | RC1IE    | TX1IE    | SSPIE    | _      | TMR2IE  | TMR1IE  | 60                         |

| IPR1                                                           | —               | ADIP         | RC1IP    | TX1IP    | SSPIP    | _      | TMR2IP  | TMR1IP  | 60                         |

| TMR2                                                           | Timer2 Register |              |          |          |          |        |         |         | 58                         |

| T2CON                                                          | _               | T2OUTPS3     | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | 58                         |

| PR2                                                            | Timer2 Peri     | iod Register |          |          |          |        |         |         | 58                         |

**Legend:** — = unimplemented, read as '0'. Shaded cells are not used by the Timer2 module.

## 14.2 Timer3 16-Bit Read/Write Mode

Timer3 can be configured for 16-bit reads and writes (see Figure 14-2). When the RD16 control bit (T3CON<7>) is set, the address for TMR3H is mapped to a buffer register for the high byte of Timer3. A read from TMR3L will load the contents of the high byte of Timer3 into the Timer3 High Byte Buffer register. This provides the user with the ability to accurately read all 16 bits of Timer1 without having to determine whether a read of the high byte, followed by a read of the low byte, has become invalid due to a rollover between reads.

A write to the high byte of Timer3 must also take place through the TMR3H Buffer register. The Timer3 high byte is updated with the contents of TMR3H when a write occurs to TMR3L. This allows a user to write all 16 bits to both the high and low bytes of Timer3 at once.

The high byte of Timer3 is not directly readable or writable in this mode. All reads and writes must take place through the Timer3 High Byte Buffer register.

Writes to TMR3H do not clear the Timer3 prescaler. The prescaler is only cleared on writes to TMR3L.

## 14.3 Using the Timer1 Oscillator as the Timer3 Clock Source

The Timer1 internal oscillator may be used as the clock source for Timer3. The Timer1 oscillator is enabled by setting the T1OSCEN (T1CON<3>) bit. To use it as the Timer3 clock source, the TMR3CS bit must also be set. As previously noted, this also configures Timer3 to increment on every rising edge of the oscillator source.

The Timer1 oscillator is described in Section 12.0 "Timer1 Module".

## 14.4 Timer3 Interrupt

The TMR3 register pair (TMR3H:TMR3L) increments from 0000h to FFFFh and overflows to 0000h. The Timer3 interrupt, if enabled, is generated on overflow and is latched in interrupt flag bit, TMR3IF (PIR2<1>). This interrupt can be enabled or disabled by setting or clearing the Timer3 Interrupt Enable bit, TMR3IE (PIE2<1>).

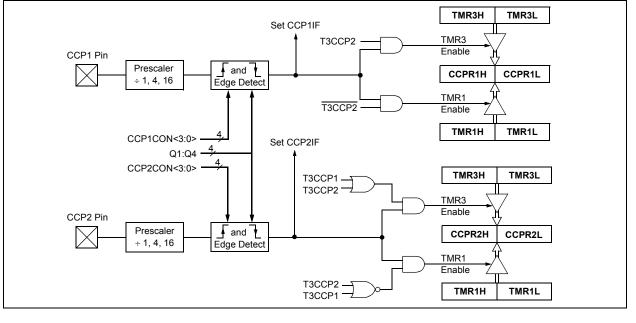

## 14.5 Resetting Timer3 Using the CCP Special Event Trigger

If CCP1 or CCP2 is configured to use Timer3 and to generate a Special Event Trigger in Compare mode (CCPxM<3:0> = 1011), this signal will reset Timer3. The trigger from CCP2 will also start an A/D conversion if the A/D module is enabled (see **Section 15.3.4** "**Special Event Trigger**" for more information).

The module must be configured as either a timer or synchronous counter to take advantage of this feature. When used this way, the CCPRxH:CCPRxL register pair effectively becomes a period register for Timer3.

If Timer3 is running in Asynchronous Counter mode, the Reset operation may not work.

In the event that a write to Timer3 coincides with a Special Event Trigger from a CCP module, the write will take precedence.

**Note:** The Special Event Triggers from the CCPx module will not set the TMR3IF interrupt flag bit (PIR2<1>).

| Name     | Bit 7                          | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2           | Bit 1  | Bit 0  | Reset<br>Values<br>on page |

|----------|--------------------------------|-----------|---------|---------|---------|-----------------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH                       | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF          | INT0IF | RBIF   | 57                         |

| PIR2     | OSCFIF                         | CMIF      | _       | —       | BCLIF   | LVDIF           | TMR3IF | _      | 60                         |

| PIE2     | OSCFIE                         | CMIE      | _       | —       | BCLIE   | LVDIE           | TMR3IE | _      | 60                         |

| IPR2     | OSCFIP                         | CMIP      | _       | —       | BCLIP   | LVDIP           | TMR3IP | —      | 60                         |

| TMR3L    | TMR3L Timer3 Register Low Byte |           |         |         |         |                 |        |        | 59                         |

| TMR3H    | R3H Timer3 Register High Byte  |           |         |         |         |                 |        |        | 59                         |

| T1CON    | RD16                           | T1RUN     | T1CKPS1 | T1CKPS0 | T10SCEN | T1SYNC          | TMR1CS | TMR10N | 58                         |

| T3CON    | RD16                           | T3CCP2    | T3CKPS1 | T3CKPS0 | T3CCP1  | <b>T3SYNC</b>   | TMR3CS | TMR3ON | 59                         |

| Lawawala |                                |           |         |         |         | Les Ale e There | 0 1 1  |        |                            |

TABLE 14-1: REGISTERS ASSOCIATED WITH TIMER3 AS A TIMER/COUNTER

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the Timer3 module.

| CCP1 Mode | CCP2 Mode | Interaction                                                                                                                                                                                                                                                           |

|-----------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Capture   | Capture   | Each module can use TMR1 or TMR3 as the time base. The time base can be different for each CCP.                                                                                                                                                                       |

| Capture   | Compare   | CCP2 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Automatic A/D conversions on a trigger event can also be done. Operation of CCP1 could be affected if it is using the same timer as a time base. |

| Compare   | Capture   | CCP1 can be configured for the Special Event Trigger to reset TMR1 or TMR3 (depending upon which time base is used). Operation of CCP2 could be affected if it is using the same timer as a time base.                                                                |

| Compare   | Compare   | Either module can be configured for the Special Event Trigger to reset the time base.<br>Automatic A/D conversions on CCP2 trigger event can be done. Conflicts may occur if<br>both modules are using the same time base.                                            |

| Capture   | PWM       | None                                                                                                                                                                                                                                                                  |

| Compare   | PWM       | None                                                                                                                                                                                                                                                                  |

| PWM       | Capture   | None                                                                                                                                                                                                                                                                  |

| PWM       | Compare   | None                                                                                                                                                                                                                                                                  |

| PWM       | PWM       | Both PWMs will have the same frequency and update rate (TMR2 interrupt).                                                                                                                                                                                              |

TABLE 15-2: INTERACTIONS BETWEEN CCP1 AND CCP2 FOR TIMER RESOURCES

## 15.2 Capture Mode

In Capture mode, the CCPR2H:CCPR2L register pair captures the 16-bit value of the TMR1 or TMR3 register when an event occurs on the CCP2 pin (RC1 or RE7, depending on device configuration). An event is defined as one of the following:

- every falling edge

- every rising edge

- every 4th rising edge

- every 16th rising edge

The event is selected by the mode select bits, CCP2M<3:0> (CCP2CON<3:0>). When a capture is made, the interrupt request flag bit, CCP2IF (PIR3<2>), is set; it must be cleared in software. If another capture occurs before the value in register, CCPR2, is read, the old captured value is overwritten by the new captured value.

## 15.2.1 CCP PIN CONFIGURATION

In Capture mode, the appropriate CCPx pin should be configured as an input by setting the corresponding TRIS direction bit.

**Note:** If RC1/CCP2 or RE7/CCP2 is configured as an output, a write to the port can cause a capture condition.

## 15.2.2 TIMER1/TIMER3 MODE SELECTION

The timers that are to be used with the capture feature (Timer1 and/or Timer3) must be running in Timer mode or Synchronized Counter mode. In Asynchronous Counter mode, the capture operation may not work. The timer to be used with each CCP module is selected in the T3CON register (see Section 15.1.1 "CCP Modules and Timer Resources").

## 15.2.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP2IE bit (PIE3<2>) clear to avoid false interrupts and should clear the flag bit, CCP2IF, following any such change in operating mode.

## 15.2.4 CCP PRESCALER

There are four prescaler settings in Capture mode. They are specified as part of the operating mode selected by the mode select bits (CCP2M<3:0>). Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any Reset will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared; therefore, the first capture may be from a non-zero prescaler. Example 15-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 15-1: CHANGING BETWEEN CAPTURE PRESCALERS

| ; Turn CCP module off |

|-----------------------|

| ; Load WREG with the  |

| ; new prescaler mode  |

| ; value and CCP ON    |

| ; Load CCP2CON with   |

| ; this value          |

|                       |

## FIGURE 15-2: CAPTURE MODE OPERATION BLOCK DIAGRAM

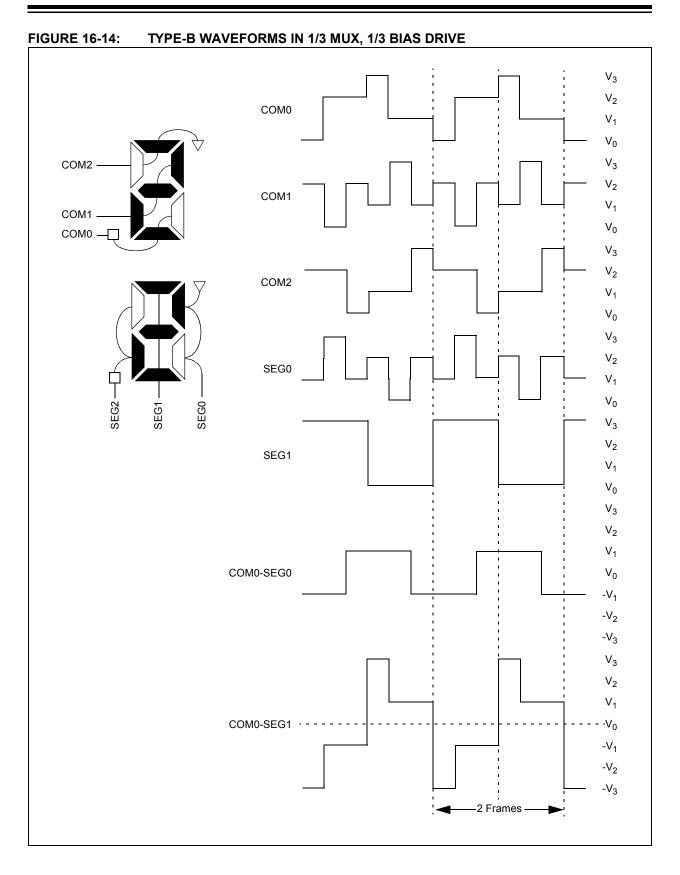

## 16.7 LCD Frame Frequency

The rate at which the COM and SEG outputs changes is called the LCD frame frequency. Frame frequency is set by the LP<3:0> bits (LCDPS<3:0>), and is also affected by the Multiplex mode being used. The relationship between the Multiplex mode, LP bits setting and frame rate is shown in Table 16-4 and Table 16-5.

#### TABLE 16-4: FRAME FREQUENCY FORMULAS

| Multiplex<br>Mode | Frame Frequency (Hz)                 |  |  |  |  |

|-------------------|--------------------------------------|--|--|--|--|

| Static            | Clock source/(4 x 1 x (LP3:LP0 + 1)) |  |  |  |  |

| 1/2               | Clock source/(2 x 2 x (LP3:LP0 + 1)) |  |  |  |  |

| 1/3               | Clock source/(1 x 3 x (LP3:LP0 + 1)) |  |  |  |  |

| 1/4               | Clock source/(1 x 4 x (LP3:LP0 + 1)) |  |  |  |  |

#### TABLE 16-5: APPROXIMATE FRAME FREQUENCY (IN Hz) FOR LP PRESCALER SETTINGS

| LP<3:0> | Multiplex Mode |     |     |     |  |  |  |  |

|---------|----------------|-----|-----|-----|--|--|--|--|

| LP<3:02 | Static         | 1/2 | 1/3 | 1/4 |  |  |  |  |

| 1       | 125            | 125 | 167 | 125 |  |  |  |  |

| 2       | 83             | 83  | 111 | 83  |  |  |  |  |

| 3       | 62             | 62  | 83  | 62  |  |  |  |  |

| 4       | 50             | 50  | 67  | 50  |  |  |  |  |

| 5       | 42             | 42  | 56  | 42  |  |  |  |  |

| 6       | 36             | 36  | 48  | 36  |  |  |  |  |

| 7       | 31             | 31  | 42  | 31  |  |  |  |  |

## 16.8 LCD Waveform Generation

LCD waveform generation is based on the principle that the net AC voltage across the dark pixel should be maximized and the net AC voltage across the clear pixel should be minimized. The net DC voltage across any pixel should be zero.

The COM signal represents the time slice for each common, while the SEG contains the pixel data. The pixel signal (COM-SEG) will have no DC component and it can take only one of the two rms values. The higher rms value will create a dark pixel and a lower rms value will create a clear pixel.

As the number of commons increases, the delta between the two rms values decreases. The delta represents the maximum contrast that the display can have.

The LCDs can be driven by two types of waveform: Type-A and Type-B. In the Type-A waveform, the phase changes within each common type, whereas in the Type-B waveform, the phase changes on each frame boundary. Thus, the Type-A waveform maintains 0 VDc over a single frame, whereas the Type-B waveform takes two frames.

| Note 1: | If the power-managed Sleep mode is        |

|---------|-------------------------------------------|

|         | invoked while the LCD Sleep bit is set    |

|         | (LCDCON<6> is '1'), take care to execute  |

|         | Sleep only when the VDC on all the pixels |

|         | is '0'.                                   |

|         |                                           |

2: When the LCD clock source is the system clock, the LCD module will go to Sleep if the microcontroller goes into Sleep mode, regardless of the setting of the SPLEN bit. Thus, always take care to see that the VDC on all pixels is '0' whenever Sleep mode is invoked.

Figure 16-6 through Figure 16-16 provide waveforms for static, half multiplex, one-third multiplex and quarter multiplex drives for Type-A and Type-B waveforms.

© 2010 Microchip Technology Inc.

## 17.4.3.2 Address Masking

Masking an address bit causes that bit to become a "don't care". When one address bit is masked, two addresses will be Acknowledged and cause an interrupt. It is possible to mask more than one address bit at a time, which makes it possible to Acknowledge up to 31 addresses in 7-bit mode and up to 63 addresses in 10-bit mode (see Example 17-2).

The  $I^2C$  Slave behaves the same way whether address masking is used or not. However, when address masking is used, the  $I^2C$  slave can Acknowledge multiple addresses and cause interrupts. When this occurs, it is necessary to determine which address caused the interrupt by checking SSPBUF.

In 7-Bit Address mode, address mask bits, ADMSK<5:1> (SSPCON<5:1>), mask the corresponding address bits in the SSPADD register. For any ADMSK bits that are set (ADMSK<n> = 1), the corresponding address bit is ignored (SSPADD<n> = x). For the module to issue an address Acknowledge, it is sufficient to match only on addresses that do not have an active address mask.

## EXAMPLE 17-2: ADDRESS MASKING EXAMPLES

In 10-Bit Address mode, the ADMSK<5:2> bits mask the corresponding address bits in the SSPADD register. In addition, ADMSK1 simultaneously masks the two LSbs of the address (SSPADD<1:0>). For any ADMSK bits that are active (ADMSK<n> = 1), the corresponding address bit is ignored (SSPADD<n> = x). Also note, that although in 10-Bit Addressing mode, the upper address bits reuse part of the SSPADD register bits. The address mask bits do not interact with those bits; they only affect the lower address bits.

**Note 1:** ADMSK1 masks the two Least Significant bits of the address.

The two Most Significant bits of the address are not affected by address masking.

#### 7-Bit Addressing:

SSPADD<7:1> = A0h (1010000) (SSPADD<0> is assumed to be '0')

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A2h, A4h, A6h, A8h, AAh, ACh, AEh

#### 10-Bit Addressing:

SSPADD<7:0> = A0h (10100000) (the two MSbs of the address are ignored in this example, since they are not affected by masking)

ADMSK<5:1> = 00111

Addresses Acknowledged: A0h, A1h, A2h, A3h, A4h, A5h, A6h, A7h, A8h, A9h, AAh, ABh, ACh, ADh, AEh, AFh

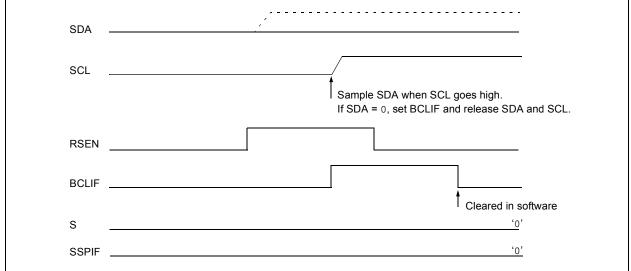

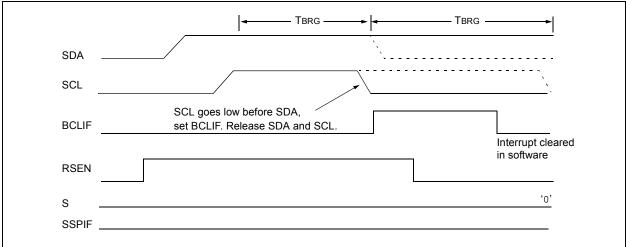

## 17.4.17.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level.

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1'.

When the user deasserts SDA and the pin is allowed to float high, the BRG is loaded with SSPADD<6:0> and counts down to 0. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', see Figure 17-31). If SDA is sampled high, the BRG is reloaded and begins counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition (see Figure 17-32).

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

#### FIGURE 17-32: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

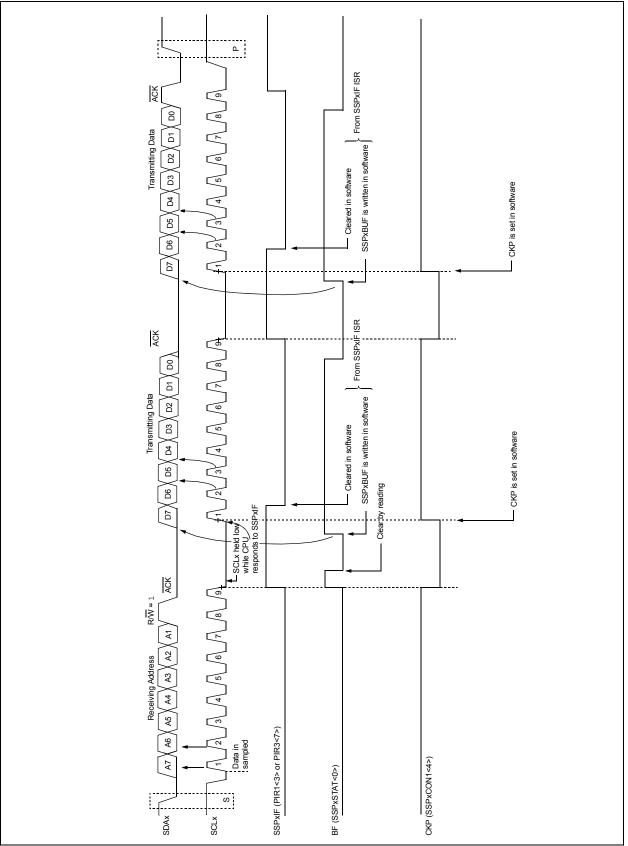

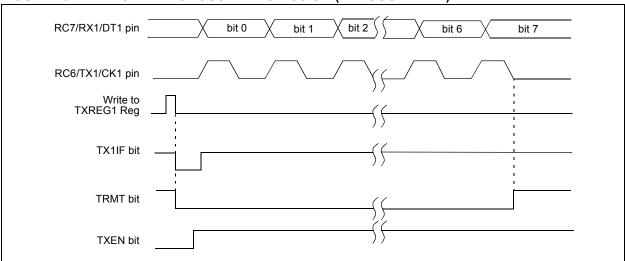

## FIGURE 18-12: SYNCHRONOUS TRANSMISSION (THROUGH TXEN)

## TABLE 18-7: REGISTERS ASSOCIATED WITH SYNCHRONOUS MASTER TRANSMISSION

| Name     | Bit 7                                         | Bit 6       | Bit 5  | Bit 4  | Bit 3 | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values<br>on Page |

|----------|-----------------------------------------------|-------------|--------|--------|-------|--------|--------|--------|----------------------------|

| INTCON   | GIE/GIEH                                      | PEIE/GIEL   | TMR0IE | INT0IE | RBIE  | TMR0IF | INT0IF | RBIF   | 57                         |

| PIR1     | _                                             | ADIF        | RC1IF  | TX1IF  | SSPIF | _      | TMR2IF | TMR1IF | 60                         |

| PIE1     | _                                             | ADIE        | RC1IE  | TX1IE  | SSPIE | _      | TMR2IE | TMR1IE | 60                         |

| IPR1     | —                                             | ADIP        | RC1IP  | TX1IP  | SSPIP | —      | TMR2IP | TMR1IP | 60                         |

| RCSTA1   | SPEN                                          | RX9         | SREN   | CREN   | ADDEN | FERR   | OERR   | RX9D   | 59                         |

| TXREG1   | EUSART T                                      | ransmit Reg | ister  |        |       |        |        |        | 59                         |

| TXSTA1   | CSRC                                          | TX9         | TXEN   | SYNC   | SENDB | BRGH   | TRMT   | TX9D   | 59                         |

| BAUDCON1 | ABDOVF                                        | RCIDL       | RXDTP  | TXCKP  | BRG16 | —      | WUE    | ABDEN  | 61                         |

| SPBRGH1  | EUSART Baud Rate Generator Register High Byte |             |        |        |       |        |        | 61     |                            |

| SPBRG1   | EUSART Baud Rate Generator Register Low Byte  |             |        |        |       |        | 59     |        |                            |

| LATG     | U2OD                                          | U10D        |        | LATG4  | LATG3 | LATG2  | LATG1  | LATG0  | 60                         |

Legend: — = unimplemented, read as '0'. Shaded cells are not used for synchronous master transmission.

| Exclusive                                                                                                                                                                                                                                       | OR W with f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| XORWF                                                                                                                                                                                                                                           | f {,d {,a}}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| (W) .XOR. (                                                                                                                                                                                                                                     | (f) $\rightarrow$ dest                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| N, Z                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 0001                                                                                                                                                                                                                                            | 10da ff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ff ffff                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| Exclusive OR the contents of W with register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in the register 'f'.                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing<br>mode whenever f ≤ 95 (5Fh). See<br>Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 1                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 1                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

| Q2                                                                                                                                                                                                                                              | Q3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Q4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| Read<br>register 'f'                                                                                                                                                                                                                            | Process<br>Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Write to destination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| on<br>= AFh<br>= B5h                                                                                                                                                                                                                            | REG, 1, 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|                                                                                                                                                                                                                                                 | XORWF<br>$0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$<br>$a \in [0,1]$<br>(W) .XOR. (<br>N, Z<br>0001<br>Exclusive C<br>register 'f'. I<br>in W. If 'd' is<br>in the regist<br>If 'a' is '0', tl<br>If 'a' is '0', al<br>set is enabl<br>in Indexed I<br>mode when<br>Section 24<br>Bit-Oriente<br>Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>XORWF F<br>on<br>= AFh | $0 \le f \le 255$ $d \in [0,1]$ $a \in [0,1]$ $(W) .XOR. (f) \rightarrow dest$ $N, Z$ $\boxed{0001  10da  ff:}$ Exclusive OR the content<br>register 'f'. If 'd' is '0', the r<br>in W. If 'd' is '1', the result<br>in the register 'f'. If 'a' is '0', the Access Bai<br>If 'a' is '0', the Access Bai<br>If 'a' is '0', the Access Bai<br>If 'a' is '1', the BSR is use<br>GPR bank. If 'a' is '0' and the extend<br>set is enabled, this instruc-<br>in Indexed Literal Offset A<br>mode whenever $f \le 95$ (5)<br>Section 24.2.3 "Byte-Or<br>Bit-Oriented Instruction<br>Literal Offset Mode" for<br>1 1 2 2 2 Q3 Read Process<br>register 'f' Data XORWF REG, 1, 0 On $= AFh$ $= B5h$ |  |  |

|              |       |                                        | Standard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |      |     |       |                                               |

|--------------|-------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-----------------------------------------------|

| Param<br>No. | Sym   | Characteristic                         | Min                                                                                                                                    | Тур† | Max | Units | Conditions                                    |

|              |       | Program Flash Memory                   |                                                                                                                                        |      |     |       |                                               |

| D130         | Eр    | Cell Endurance                         | 100                                                                                                                                    | 1K   | —   | E/W   | -40°C to +85°C                                |

| D131         | Vpr   | VDD for Read                           | VMIN                                                                                                                                   | —    | 3.6 | V     | Vмın = Minimum operating<br>voltage           |

| D132         | Vpew  | Voltage for Self-Timed Erase or Write: |                                                                                                                                        |      |     |       |                                               |

|              |       | VDD                                    | 2.35                                                                                                                                   | _    | 3.6 | V     | ENVREG tied to VDD                            |

|              |       | VDDCORE                                | 2.25                                                                                                                                   | _    | 2.7 | V     | ENVREG tied to Vss                            |

| D133A        | Tiw   | Self-Timed Write Cycle Time            | _                                                                                                                                      | 2.8  | _   | ms    |                                               |

| D133B        | TIE   | Self-Timed Block Erased Cycle<br>Time  | _                                                                                                                                      | 33   | —   | ms    |                                               |

| D134         | TRETD | Characteristic Retention               | 20                                                                                                                                     | —    | —   | Year  | Provided no other specifications are violated |

| D135         | IDDP  | Supply Current during<br>Programming   | -                                                                                                                                      | 3    | 7   | mA    |                                               |

| D1xxx        | TWE   | Writes per Erase Cycle                 | —                                                                                                                                      |      | 1   |       | Per one physical word address                 |

#### TABLE 26-1: MEMORY PROGRAMMING REQUIREMENTS

† Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 26-2: COMPARATOR SPECIFICATIONS

| <b>Operating Conditions:</b> $3.0V \le V_{DD} \le 3.6V$ , $-40^{\circ}C \le TA \le +85^{\circ}C$ (unless otherwise stated) |        |                                            |     |      |            |       |          |

|----------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------|-----|------|------------|-------|----------|

| Param<br>No.                                                                                                               | Sym    | Characteristics                            | Min | Тур  | Мах        | Units | Comments |

| D300                                                                                                                       | VIOFF  | Input Offset Voltage                       | _   | ±5.0 | ±25        | mV    |          |

| D301                                                                                                                       | VICM   | Input Common Mode Voltage                  | 0   |      | AVDD - 1.5 | V     |          |

| D302                                                                                                                       | CMRR   | Common Mode Rejection Ratio                | 55  | _    | —          | dB    |          |

| D303                                                                                                                       | TRESP  | Response Time <sup>(1)</sup>               | _   | 150  | 400        | ns    |          |

| D304                                                                                                                       | Тмс2оv | Comparator Mode Change to<br>Output Valid* | —   | —    | 10         | μS    |          |

| D305                                                                                                                       | Virv   | Internal Reference Voltage                 | _   | 1.2  | _          | V     |          |

**Note 1:** Response time measured with one comparator input at (AVDD – 1.5)/2, while the other input transitions from Vss to VDD.

## 26.4 AC (Timing) Characteristics

#### 26.4.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2ppS                | 3                               | 3. TCC:ST | (I <sup>2</sup> C specifications only) |

|----------------------------|---------------------------------|-----------|----------------------------------------|

| 2. TppS                    |                                 | 4. Ts     | (I <sup>2</sup> C specifications only) |

| Т                          |                                 |           |                                        |

| F                          | Frequency                       | Т         | Time                                   |

| Lowercase le               | etters (pp) and their meanings: |           |                                        |

| рр                         |                                 |           |                                        |

| сс                         | CCP1                            | osc       | OSC1                                   |

| ck                         | CLKO                            | rd        | RD                                     |

| cs                         | CS                              | rw        | RD or WR                               |

| di                         | SDI                             | sc        | SCK                                    |

| do                         | SDO                             | SS        | SS                                     |

| dt                         | Data in                         | tO        | TOCKI                                  |

| io                         | I/O port                        | t1        | T13CKI                                 |

| mc                         | MCLR                            | wr        | WR                                     |

| Uppercase le               | etters and their meanings:      | •         |                                        |

| S                          |                                 |           |                                        |

| F                          | Fall                            | Р         | Period                                 |

| н                          | High                            | R         | Rise                                   |

| 1                          | Invalid (High-Impedance)        | V         | Valid                                  |

| L                          | Low                             | Z         | High-Impedance                         |

| I <sup>2</sup> C only      |                                 |           |                                        |

| AA                         | output access                   | High      | High                                   |

| BUF                        | Bus free                        | Low       | Low                                    |

| TCC:ST (I <sup>2</sup> C s | specifications only)            |           |                                        |

| CC                         |                                 |           |                                        |

| HD                         | Hold                            | SU        | Setup                                  |

| ST                         |                                 |           |                                        |

| DAT                        | DATA input hold                 | STO       | Stop condition                         |

| STA                        | Start condition                 |           |                                        |

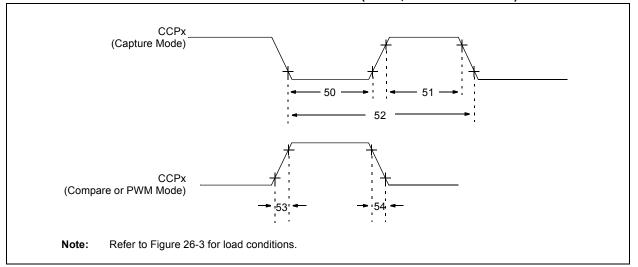

#### FIGURE 26-8: CAPTURE/COMPARE/PWM TIMINGS (CCP1, CCP2 MODULES)

TABLE 26-13: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP1, CCP2 MODULES)

| Param<br>No. | Symbol   | С                | haracteristic  | Min                    | Мах | Units | Conditions                         |

|--------------|----------|------------------|----------------|------------------------|-----|-------|------------------------------------|

| 50           | TccL     | CCPx Input Low   | No prescaler   | 0.5 Tcy + 20           |     | ns    |                                    |

|              | Tim      | Time             | With prescaler | 10                     | _   | ns    |                                    |

| 51           | ТссН     | CCPx Input       | No prescaler   | 0.5 Tcy + 20           | _   | ns    |                                    |

|              | High Tim | High Time        | With prescaler | 10                     | -   | ns    |                                    |

| 52           | TCCP     | CCPx Input Perio | bd             | <u>3 Tcy + 40</u><br>N | _   | ns    | N = prescale<br>value (1, 4 or 16) |

| 53           | TccR     | CCPx Output Fal  | ll Time        | —                      | 25  | ns    |                                    |

| 54           | TccF     | CCPx Output Fal  | ll Time        | —                      | 25  | ns    |                                    |

| Transition for Entry to SEC_RUN Mode45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|