Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 40MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                            |

| Number of I/O              | 51                                                                         |

| Program Memory Size        | 32KB (16K x 16)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | •                                                                          |

| RAM Size                   | 2K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                  |

| Data Converters            | A/D 12x10b                                                                 |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65j90-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-4: PIC18F8XJ90 PINOUT I/O DESCRIPTIONS

| Din Nama                                 | Pin Number | Pin           | Buffer                  | Description                                                                                                                                                                           |

|------------------------------------------|------------|---------------|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                                 | TQFP       | Type          | Type                    | Description                                                                                                                                                                           |

| MCLR                                     | 9          | I             | ST                      | Master Clear (input) or programming voltage (input). This pin is an active-low Reset to the device.                                                                                   |

| OSC1/CLKI/RA7<br>OSC1<br>CLKI            | 49         | 1             | CMOS<br>CMOS            | Oscillator crystal or external clock input. Oscillator crystal input. External clock source input. Always associated with pin function OSC1. (See related OSC1/CLKI, OSC2/CLKO pins.) |

| RA7                                      |            | I/O           | TTL                     | General purpose I/O pin.                                                                                                                                                              |

| OSC2/CLKO/RA6<br>OSC2                    | 50         | 0             | _                       | Oscillator crystal or clock output. Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode.                                                           |

| CLKO                                     |            | 0             | _                       | In EC modes, OSC2 pin outputs CLKO, which has 1/4 the frequency of OSC1 and denotes the instruction cycle rate.                                                                       |

| RA6                                      |            | I/O           | TTL                     | General purpose I/O pin.                                                                                                                                                              |

|                                          |            |               |                         | PORTA is a bidirectional I/O port.                                                                                                                                                    |

| RA0/AN0<br>RA0<br>AN0                    | 30         | I/O<br>I      | TTL<br>Analog           | Digital I/O.<br>Analog Input 0.                                                                                                                                                       |

| RA1/AN1/SEG18<br>RA1<br>AN1<br>SEG18     | 29         | I/O<br>I<br>O | TTL<br>Analog<br>Analog | Digital I/O. Analog Input 1. SEG18 output for LCD.                                                                                                                                    |

| RA2/AN2/VREF-<br>RA2<br>AN2<br>VREF-     | 28         | I/O<br>I<br>I | TTL<br>Analog<br>Analog | Digital I/O.<br>Analog Input 2.<br>A/D reference voltage (low) input.                                                                                                                 |

| RA3/AN3/VREF+<br>RA3<br>AN3<br>VREF+     | 27         | I/O<br>I<br>I | TTL<br>Analog<br>Analog | Digital I/O.<br>Analog Input 3.<br>A/D reference voltage (high) input.                                                                                                                |

| RA4/T0CKI/SEG14<br>RA4<br>T0CKI<br>SEG14 | 34         | I/O<br>I<br>O | ST/OD<br>ST<br>Analog   | Digital I/O. Open-drain when configured as output.<br>Timer0 external clock input.<br>SEG14 output for LCD.                                                                           |

| RA5/AN4/SEG15<br>RA5<br>AN4<br>SEG15     | 33         | I/O<br>I<br>O | TTL<br>Analog<br>Analog | Digital I/O.<br>Analog Input 4.<br>SEG15 output for LCD.                                                                                                                              |

| RA6                                      |            |               |                         | See the OSC2/CLKO/RA6 pin.                                                                                                                                                            |

| RA7                                      |            |               |                         | See the OSC1/CLKI/RA7 pin.                                                                                                                                                            |

**Legend:** TTL = TTL compatible input CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels Analog = Analog input O = Output

P = Power OD = Open-Drain (no P diode to VDD)

$I^2C^{TM} = I^2C/SMBus$

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

TABLE 1-4: PIC18F8XJ90 PINOUT I/O DESCRIPTIONS (CONTINUED)

| Din Name                  | Pin Number     | Pin      | Buffer       | Description                                                                                                                     |

|---------------------------|----------------|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------|

| Pin Name                  | TQFP           | Type     | Type         | Description                                                                                                                     |

|                           |                |          |              | PORTJ is a bidirectional I/O port.                                                                                              |

| RJ0                       | 62             | I/O      | ST           | Digital I/O.                                                                                                                    |

| RJ1/SEG33<br>RJ1<br>SEG33 | 61             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG33 output for LCD.                                                                                           |

| RJ2/SEG34<br>RJ2<br>SEG34 | 60             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG34 output for LCD.                                                                                           |

| RJ3/SEG35<br>RJ3<br>SEG35 | 59             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG35 output for LCD.                                                                                           |

| RJ4/SEG39<br>RJ4<br>SEG39 | 39             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG39 output for LCD.                                                                                           |

| RJ5/SEG38<br>RJ5<br>SEG38 | 40             | I/O<br>O | ST<br>Analog | Digital I/O<br>SEG38 output for LCD.                                                                                            |

| RJ6/SEG37<br>RJ6<br>SEG37 | 41             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG37 output for LCD.                                                                                           |

| RJ7/SEG36<br>RJ7<br>SEG36 | 42             | I/O<br>O | ST<br>Analog | Digital I/O.<br>SEG36 output for LCD.                                                                                           |

| Vss                       | 11, 31, 51, 70 | Р        | _            | Ground reference for logic and I/O pins.                                                                                        |

| VDD                       | 32, 48, 71     | Р        | _            | Positive supply for logic and I/O pins.                                                                                         |

| AVss                      | 26             | Р        | _            | Ground reference for analog modules.                                                                                            |

| AVDD                      | 25             | Р        | _            | Positive supply for analog modules.                                                                                             |

| ENVREG                    | 24             | ı        | ST           | Enable for on-chip voltage regulator.                                                                                           |

| VDDCORE/VCAP<br>VDDCORE   | 12             | Р        | _            | Core logic power or external filter capacitor connection.  Positive supply for microcontroller core logic (regulator disabled). |

| VCAP                      |                | Р        | _            | External filter capacitor connection (regulator enabled).                                                                       |

Legend: TTL = TTL compatible input

CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

Analog = Analog input

I = Input

O = Output OD = Open-Drain (no P diode to VDD)

P = Power

$I^2C^{TM} = I^2C/SMBus$

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

### 2.0 GUIDELINES FOR GETTING STARTED WITH PIC18FJ MICROCONTROLLERS

### 2.1 Basic Connection Requirements

Getting started with the PIC18F85J90 family family of 8-bit microcontrollers requires attention to a minimal set of device pin connections before proceeding with development.

The following pins must always be connected:

- All VDD and Vss pins (see Section 2.2 "Power Supply Pins")

- All AVDD and AVSs pins, regardless of whether or not the analog device features are used (see Section 2.2 "Power Supply Pins")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- ENVREG (if implemented) and VCAP/VDDCORE pins (see Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)")

These pins must also be connected if they are being used in the end application:

- PGC/PGD pins used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes (see Section 2.5 "ICSP Pins")

- OSCI and OSCO pins when an external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

VREF+/VREF- pins are used when external voltage reference for analog modules is implemented

**Note:** The AVDD and AVSS pins must always be connected, regardless of whether any of the analog modules are being used.

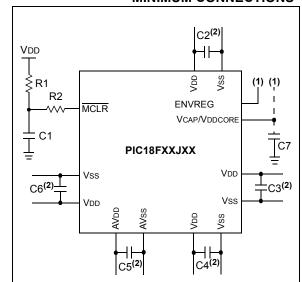

The minimum mandatory connections are shown in Figure 2-1.

## FIGURE 2-1: RECOMMENDED MINIMUM CONNECTIONS

### Key (all values are recommendations):

C1 through C6: 0.1  $\mu$ F, 20V ceramic

C7: 10  $\mu\text{F}$ , 6.3V or greater, tantalum or ceramic

R1:  $10 \text{ k}\Omega$ R2:  $100\Omega$  to  $470\Omega$

Note 1: See Section 2.4 "Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)" for explanation of ENVREG pin connections.

2: The example shown is for a PIC18F device with five VDD/Vss and AVDD/AVss pairs. Other devices may have more or less pairs; adjust the number of decoupling capacitors appropriately.

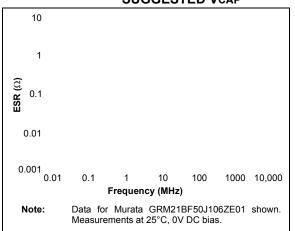

## 2.4 Voltage Regulator Pins (ENVREG and VCAP/VDDCORE)

The on-chip voltage regulator enable pin, ENVREG, must always be connected directly to either a supply voltage or to ground. Tying ENVREG to VDD enables the regulator, while tying it to ground disables the regulator. Refer to **Section 23.3 "On-Chip Voltage Regulator"** for details on connecting and using the on-chip regulator.

When the regulator is enabled, a low-ESR (<  $5\Omega$ ) capacitor is required on the VCAP/VDDCORE pin to stabilize the voltage regulator output voltage. The VCAP/VDDCORE pin must not be connected to VDD and must use a capacitor of 10  $\mu F$  connected to ground. The type can be ceramic or tantalum. A suitable example is the Murata GRM21BF50J106ZE01 (10  $\mu F,~6.3V$ ) or equivalent. Designers may use Figure 2-3 to evaluate ESR equivalence of candidate devices.

It is recommended that the trace length not exceed 0.25 inch (6 mm). Refer to **Section 26.0 "Electrical Characteristics"** for additional information.

When the regulator is disabled, the VCAP/VDDCORE pin must be tied to a voltage supply at the VDDCORE level. Refer to **Section 26.0** "**Electrical Characteristics**" for information on VDD and VDDCORE.

Note that the "LF" versions of some low pin count PIC18FJ parts (e.g., the PIC18LF45J10) do not have the ENVREG pin. These devices are provided with the voltage regulator permanently disabled; they must always be provided with a supply voltage on the VDDCORE pin.

FIGURE 2-3: FREQUENCY vs. ESR

PERFORMANCE FOR

SUGGESTED VCAP

#### 2.5 ICSP Pins

The PGC and PGD pins are used for In-Circuit Serial Programming  $^{\text{TM}}$  (ICSP $^{\text{TM}}$ ) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of ohms, not to exceed  $100\Omega$ .

Pull-up resistors, series diodes, and capacitors on the PGC and PGD pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin input voltage high (VIH) and input low (VIL) requirements.

For device emulation, ensure that the "Communication Channel Select" (i.e., PGCx/PGDx pins) programmed into the device matches the physical connections for the ICSP to the Microchip debugger/emulator tool.

For more information on available Microchip development tools connection requirements, refer to Section 24.0 "Development Support".

### 3.2 Control Registers

The OSCCON register (Register 3-1) controls the main aspects of the device clock's operation. It selects the oscillator type to be used, which of the power-managed modes to invoke and the output frequency of the INTOSC source. It also provides status on the oscillators.

The OSCTUNE register (Register 3-2) controls the tuning and operation of the internal oscillator block. It also implements the PLLEN bits, which control the operation of the Phase Locked Loop (PLL) in Internal Oscillator modes (see **Section 3.4.3 "PLL Frequency Multiplier"**).

### REGISTER 3-1: OSCCON: OSCILLATOR CONTROL REGISTER

| R/W-0 | R/W-1                | R/W-0                | R/W-0                | R <sup>(1)</sup> | R-0  | R/W-0               | R/W-0               |

|-------|----------------------|----------------------|----------------------|------------------|------|---------------------|---------------------|

| IDLEN | IRCF2 <sup>(2)</sup> | IRCF1 <sup>(2)</sup> | IRCF0 <sup>(2)</sup> | OSTS             | IOFS | SCS1 <sup>(4)</sup> | SCS0 <sup>(4)</sup> |

| bit 7 |                      |                      |                      |                  |      |                     | bit 0               |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7 IDLEN: Idle Enable bit

1 = Device enters an Idle mode when a SLEEP instruction is executed

0 = Device enters Sleep mode when a SLEEP instruction is executed

bit 6-4 IRCF<2:0>: INTOSC Source Frequency Select bits<sup>(2)</sup>

111 = 8 MHz (INTOSC drives clock directly)

110 = 4 MHz

101 = 2 MHz

100 = 1 MHz (default)

011 = 500 kHz

010 = 250 kHz

001 = 125 kHz

000 = 31 kHz (from either INTOSC/256 or INTRC)(3)

bit 3 OSTS: Oscillator Start-up Time-out Status bit (1)

1 = Oscillator Start-up Timer (OST) time-out has expired; primary oscillator is running

0 = Oscillator Start-up Timer (OST) time-out is running; primary oscillator is not ready

bit 2 IOFS: INTOSC Frequency Stable bit

1 = Fast RC oscillator frequency is stable

0 = Fast RC oscillator frequency is not stable

bit 1-0 SCS<1:0:> System Clock Select bits<sup>(4)</sup>

11 = Internal oscillator block

10 = Primary oscillator

01 = Timer1 oscillator

When FOSC2 = 1:

00 = Primary oscillator

When FOSC2 = 0:

00 = Internal oscillator

- Note 1: Reset state depends on state of the IESO Configuration bit.

- 2: Modifying these bits will cause an immediate clock frequency switch if the internal oscillator is providing the device clocks.

- 3: Source selected by the INTSRC bit (OSCTUNE<7>), see text.

- 4: Modifying these bits will cause an immediate clock source switch.

TABLE 5-2: INITIALIZATION CONDITIONS FOR ALL REGISTERS (CONTINUED)

| Register | Applicable Devices |             | Power-on Reset,<br>Brown-out Reset | MCLR Resets WDT Reset RESET Instruction Stack Resets CM Resets | Wake-up via WDT or Interrupt |

|----------|--------------------|-------------|------------------------------------|----------------------------------------------------------------|------------------------------|

| CCPR2L   | PIC18F6XJ90        | PIC18F8XJ90 | xxxx xxxx                          | uuuu uuuu                                                      | uuuu uuuu                    |

| CCP2CON  | PIC18F6XJ90        | PIC18F8XJ90 | 00 0000                            | 00 0000                                                        | uu uuuu                      |

| SPBRG2   | PIC18F6XJ90        | PIC18F8XJ90 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                    |

| RCREG2   | PIC18F6XJ90        | PIC18F8XJ90 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                    |

| TXREG2   | PIC18F6XJ90        | PIC18F8XJ90 | 0000 0000                          | 0000 0000                                                      | uuuu uuuu                    |

| TXSTA2   | PIC18F6XJ90        | PIC18F8XJ90 | 0000 -010                          | 0000 -010                                                      | uuuu -uuu                    |

| RCSTA2   | PIC18F6XJ90        | PIC18F8XJ90 | 0000 000x                          | 0000 000x                                                      | uuuu uuuu                    |

- **Legend:** u = unchanged, x = unknown, = unimplemented bit, read as '0', <math>q = value depends on condition. Shaded cells indicate conditions do not apply for the designated device.

- Note 1: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the TOSU, TOSH and TOSL are updated with the current value of the PC. The STKPTR is modified to point to the next location in the hardware stack.

- 2: When the wake-up is due to an interrupt and the GIEL or GIEH bit is set, the PC is loaded with the interrupt vector (0008h or 0018h).

- **3:** One or more bits in the INTCONx or PIRx registers will be affected (to cause wake-up).

- 4: See Table 5-1 for Reset value for specific condition.

- **5:** Bits 6 and 7 of PORTA, LATA and TRISA are enabled depending on the oscillator mode selected. When not enabled as PORTA pins, they are disabled and read as '0'.

### 6.0 MEMORY ORGANIZATION

There are two types of memory in PIC18 Flash microcontroller devices:

- · Program Memory

- · Data RAM

As Harvard architecture devices, the data and program memories use separate busses; this allows for concurrent access of the two memory spaces.

Additional detailed information on the operation of the Flash program memory is provided in **Section 7.0 "Flash Program Memory"**.

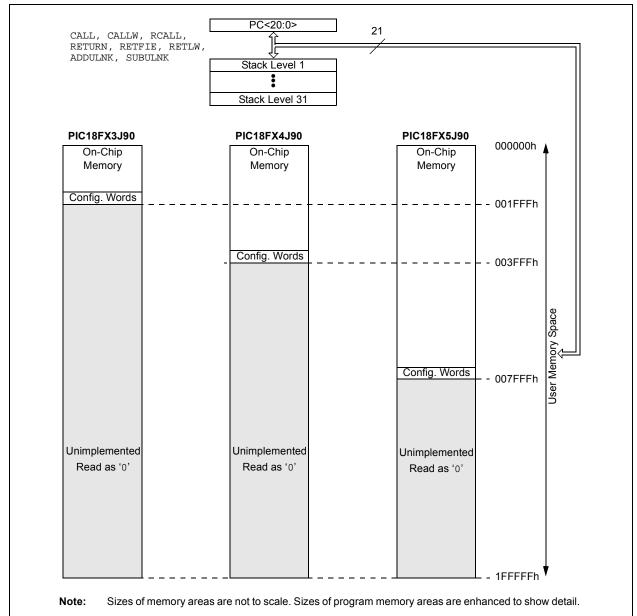

### 6.1 Program Memory Organization

PIC18 microcontrollers implement a 21-bit program counter which is capable of addressing a 2-Mbyte program memory space. Accessing a location between the upper boundary of the physically implemented memory and the 2-Mbyte address will return all '0's (a NOP instruction).

The entire PIC18F85J90 family offers a range of on-chip Flash program memory sizes, from 8 Kbytes (up to 4,096 single-word instructions) to 32 Kbytes (32,768 single-word instructions). The program memory maps for individual family members are shown in Figure 6-1.

FIGURE 6-1: MEMORY MAPS FOR PIC18F85J90 FAMILY DEVICES

TABLE 10-7: PORTC FUNCTIONS

| Pin Name              | Function            | TRIS<br>Setting | I/O      | I/O<br>Type | Description                                                                                                       |

|-----------------------|---------------------|-----------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------|

| RC0/T1OSO/            | RC0                 | 0               | 0        | DIG         | LATC<0> data output.                                                                                              |

| T13CKI                |                     | 1               |          | ST          | PORTC<0> data input.                                                                                              |

|                       | T10S0               | х               | 0        | ANA         | Timer1 oscillator output; enabled when Timer1 oscillator is enabled. Disables digital I/O and LCD segment driver. |

|                       | T13CKI              | 1               | I        | ST          | Timer1/Timer3 counter input.                                                                                      |

| RC1/T1OSI/            | RC1                 | 0               | 0        | DIG         | LATC<1> data output.                                                                                              |

| CCP2/SEG32            |                     | 1               | ı        | ST          | PORTC<1> data input.                                                                                              |

|                       | T1OSI               | х               | I        | ANA         | Timer1 oscillator input.                                                                                          |

|                       | CCP2 <sup>(1)</sup> | 0               | 0        | DIG         | CCP2 compare/PWM output.                                                                                          |

|                       |                     | 1               | I        | ST          | CCP2 capture input.                                                                                               |

|                       | SEG32               | х               | 0        | ANA         | LCD Segment 32 output; disables all other pin functions.                                                          |

| RC2/CCP1/<br>SEG13    | RC2                 | 0               | 0        | DIG         | LATC<2> data output.                                                                                              |

| 02010                 | 0004                | 1               | 1        | ST          | PORTC<2> data input.                                                                                              |

|                       | CCP1                | 0               | 0        | DIG         | CCP1 compare/PWM output; takes priority over port data.                                                           |

|                       | SEG13               | 1               | 0        | ST          | CCP1 capture input.  LCD Segment 13 output; disables all other pin functions.                                     |

| RC3/SCK/SCL/          | RC3                 | x               | 0        | ANA         | LATC<3> data output.                                                                                              |

| SEG17                 | RCS                 | 0               | <u> </u> | ST          | PORTC<3> data output.                                                                                             |

|                       | SCK                 | 0               | 0        | DIG         | SPI clock output (MSSP module); takes priority over port data.                                                    |

|                       | OOK                 | 1               |          | ST          | SPI clock input (MSSP module).                                                                                    |

|                       | SCL                 | 0               | 0        | DIG         | I <sup>2</sup> C™ clock output (MSSP module); takes priority over port data.                                      |

|                       | 002                 | 1               | ı        | I2C         | I <sup>2</sup> C clock input (MSSP module); input type depends on module setting.                                 |

|                       | SEG17               | х               | 0        | ANA         | LCD Segment 17 output; disables all other pin functions.                                                          |

| RC4/SDI/SDA/          | RC4                 | 0               | 0        | DIG         | LATC<4> data output.                                                                                              |

| SEG16                 |                     | 1               | I        | ST          | PORTC<4> data input.                                                                                              |

|                       | SDI                 |                 | I        | ST          | SPI data input (MSSP module).                                                                                     |

|                       | SDA                 | 1               | 0        | DIG         | I <sup>2</sup> C data output (MSSP module); takes priority over port data.                                        |

|                       |                     | 1               | 1        | I2C         | I <sup>2</sup> C data input (MSSP module); input type depends on module setting.                                  |

|                       | SEG16               | х               | 0        | ANA         | LCD Segment 16 output; disables all other pin functions.                                                          |

| RC5/SDO/              | RC5                 | 0               | 0        | DIG         | LATC<5> data output.                                                                                              |

| SEG12                 |                     | 1               | I        | ST          | PORTC<5> data input.                                                                                              |

|                       | SDO                 | 0               | 0        | DIG         | SPI data output (MSSP module).                                                                                    |

|                       | SEG12               | х               | 0        | ANA         | LCD Segment 12 output; disables all other pin functions.                                                          |

| RC6/TX1/CK1/<br>SEG27 | RC6                 | 0               | 0        | DIG         | LATC<6> data output.                                                                                              |

| SEG21                 |                     | 1               | ı        | ST          | PORTC<6> data input.                                                                                              |

|                       | TX1                 | 1               | 0        | DIG         | Synchronous serial data output (EUSART module); takes priority over port data.                                    |

|                       | CK1                 | 1               | 0        | DIG         | Synchronous serial data input (EUSART module); user must configure as an input.                                   |

|                       | 05007               | 1               | 1        | ST          | Synchronous serial clock input (EUSART module).                                                                   |

| DOZIDYA IDTA          | SEG27               | x               | 0        | ANA         | LCD Segment 27 output; disables all other pin functions.                                                          |

| RC7/RX1/DT1/<br>SEG28 | RC7                 | 0               | 0        | DIG         | LATC<7> data output.                                                                                              |

|                       | DV4                 | 1               | - 1      | ST          | PORTC<7> data input.                                                                                              |

|                       | RX1                 | 1               | -        | ST          | Asynchronous serial receive data input (EUSART module).                                                           |

|                       | DT1                 | 1               | 0        | DIG         | Synchronous serial data output (EUSART module); takes priority over port data.                                    |

|                       | SEGOO               | 1               | -        | ST          | Synchronous serial data input (EUSART module); user must configure as an input.                                   |

|                       | SEG28               | Х               | 0        | ANA         | LCD Segment 28 output; disables all other pin functions.                                                          |

**Legend:** O = Output, I = Input, ANA = Analog Signal, DIG = Digital Output, ST = Schmitt Trigger Buffer Input, TTL = TTL Buffer Input,  $ICC = I^2C/SMBus$  Buffer Inp

Note 1: Default assignment for CCP2 when the CCP2MX Configuration bit is set.

### 15.4.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing to the CCPR2L register and to the CCP2CON<5:4> bits. Up to 10-bit resolution is available. The CCPR2L contains the eight MSbs and the CCP2CON<5:4> contains the two LSbs. This 10-bit value is represented by CCPR2L:CCP2CON<5:4>. The following equation is used to calculate the PWM duty cycle in time:

### **EQUATION 15-2:**

CCPR2L and CCP2CON<5:4> can be written to at any time, but the duty cycle value is not latched into CCPR2H until after a match between PR2 and TMR2 occurs (i.e., the period is complete). In PWM mode, CCPR2H is a read-only register.

The CCPR2H register and a 2-bit internal latch are used to double-buffer the PWM duty cycle. This double-buffering is essential for glitchless PWM operation.

When the CCPR2H and 2-bit latch match TMR2, concatenated with an internal 2-bit Q clock or 2 bits of the TMR2 prescaler, the CCP2 pin is cleared.

The maximum PWM resolution (bits) for a given PWM frequency is given by the equation:

### **EQUATION 15-3:**

PWM Resolution (max) =

$$\frac{\log\left(\frac{FOSC}{FPWM}\right)}{\log(2)}$$

bits

**Note:** If the PWM duty cycle value is longer than the PWM period, the CCP2 pin will not be cleared.

TABLE 15-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 40 MHz

| PWM Frequency              | 2.44 kHz | 9.77 kHz | 39.06 kHz | 156.25 kHz | 312.50 kHz | 416.67 kHz |

|----------------------------|----------|----------|-----------|------------|------------|------------|

| Timer Prescaler (1, 4, 16) | 16       | 4        | 1         | 1          | 1          | 1          |

| PR2 Value                  | FFh      | FFh      | FFh       | 3Fh        | 1Fh        | 17h        |

| Maximum Resolution (bits)  | 14       | 12       | 10        | 8          | 7          | 6.58       |

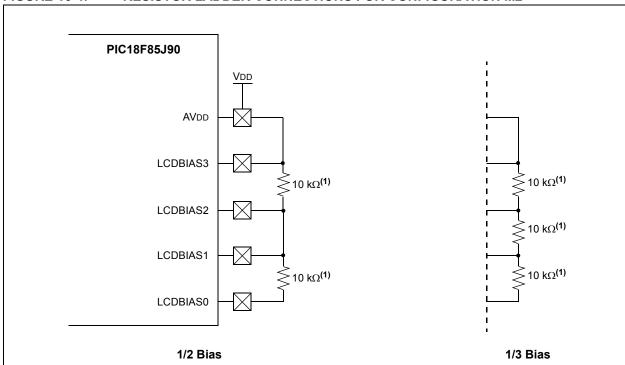

## 16.3.3.3 M2 (Resistor Ladder with Software Contrast)

M2 operation also uses the LCD regulator but disables the charge pump. The regulator's internal voltage reference remains active as a way to regulate contrast. It is used in cases where the current requirements of the LCD exceed the capacity of the regulator's charge pump.

In this configuration, the LCD bias voltage levels are created by an external resistor voltage divider connected across LCDBIAS0 through LCDBIAS3, with the top of the divider tied to VDD (Figure 16-4). The potential at the bottom of the ladder is determined by the LCD regulator's voltage reference, tied internally to LCDBIAS0. The bias type is determined by the voltages on the LCDBIAS pins, which are controlled by the

configuration of the resistor ladder. Most applications using M2 will use a 1/3 or 1/2 Bias type. While Static Bias can also be used, it offers extremely limited contrast range and additional current consumption over other bias generation modes.

Like M1, the LCDBIAS bits can be used to control contrast, limited by the level of VDD supplied to the device. Also, since there is no capacitor required across VLCAP1 and VLCAP2, these pins are available as digital I/O ports, RG2 and RG3.

M2 is selected by clearing the CKSEL<1:0> bits and setting the CPEN bit.

FIGURE 16-4: RESISTOR LADDER CONNECTIONS FOR CONFIGURATION M2

| Bias Level at Pin | Bias Type                        |                                  |  |  |  |

|-------------------|----------------------------------|----------------------------------|--|--|--|

|                   | 1/2 Bias                         | 1/3 Bias                         |  |  |  |

| LCDBIAS0          | (Internal low reference voltage) | (Internal low reference voltage) |  |  |  |

| LCDBIAS1          | 1/2 VBIAS                        | 1/3 VBIAS                        |  |  |  |

| LCDBIAS2          | 1/2 VBIAS                        | 2/3 VBIAS                        |  |  |  |

| LCDBIAS3          | VBIAS (up to AVDD)               | VBIAS (up to AVDD)               |  |  |  |

**Note 1:** These values are provided for design guidance only; they should be optimized for the application by the designer based on the actual LCD specifications.

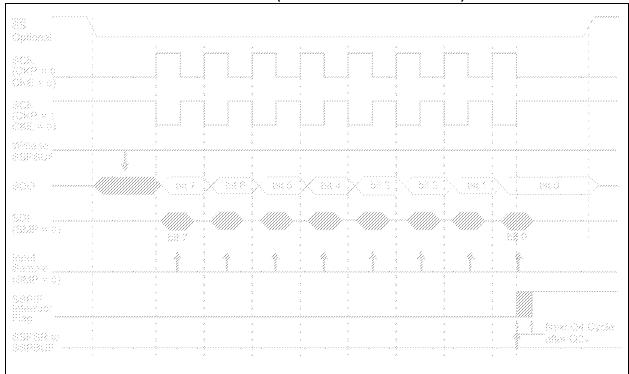

FIGURE 17-5: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 0)

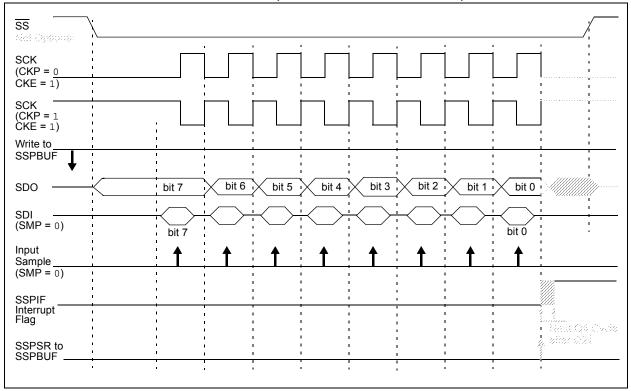

FIGURE 17-6: SPI MODE WAVEFORM (SLAVE MODE WITH CKE = 1)

#### 17.4.2 OPERATION

The MSSP module functions are enabled by setting the MSSP Enable bit, SSPEN (SSPCON1<5>).

The SSPCON1 register allows control of the I<sup>2</sup>C operation. Four mode selection bits (SSPCON1<3:0>) allow one of the following I<sup>2</sup>C modes to be selected:

- I<sup>2</sup>C Master mode, clock = (Fosc/4) x (SSPADD + 1)

- I<sup>2</sup>C Slave mode (7-bit address)

- I<sup>2</sup>C Slave mode (10-bit address)

- I<sup>2</sup>C Slave mode (7-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Slave mode (10-bit address) with Start and Stop bit interrupts enabled

- I<sup>2</sup>C Firmware Controlled Master mode, slave is Idle

Selection of any I<sup>2</sup>C mode, with the SSPEN bit set, forces the SCL and SDA pins to be open-drain, provided these pins are programmed to inputs by setting the appropriate TRISC or TRISD bits. To ensure proper operation of the module, pull-up resistors must be provided externally to the SCL and SDA pins.

#### 17.4.3 SLAVE MODE

In Slave mode, the SCL and SDA pins must be configured as inputs (TRISC<4:3> set). The MSSP module will override the input state with the output data when required (slave-transmitter).

The I<sup>2</sup>C Slave mode hardware will always generate an interrupt on an exact address match. In addition, address masking will also allow the hardware to generate an interrupt for more than one address (up to 31 in 7-bit addressing and up to 63 in 10-bit addressing). Through the mode select bits, the user can also choose to interrupt on Start and Stop bits.

When an address is matched, or the data transfer after an address match is received, the hardware automatically will generate the Acknowledge (ACK) pulse and load the SSPBUF register with the received value currently in the SSPSR register.

Any combination of the following conditions will cause the MSSP module not to give this  $\overline{\mathsf{ACK}}$  pulse:

- The Buffer Full bit, BF (SSPSTAT<0>), was set before the transfer was received.

- The overflow bit, SSPOV (SSPCON1<6>), was set before the transfer was received.

In this case, the SSPSR register value is not loaded into the SSPBUF, but bit SSPIF is set. The BF bit is cleared by reading the SSPBUF register, while bit SSPOV is cleared through software.

The SCL clock input must have a minimum high and low for proper operation. The high and low times of the I<sup>2</sup>C specification, as well as the requirement of the MSSP module, are shown in timing parameter 100 and parameter 101.

#### 17.4.3.1 Addressing

Once the MSSP module has been enabled, it waits for a Start condition to occur. Following the Start condition, the 8 bits are shifted into the SSPSR register. All incoming bits are sampled with the rising edge of the clock (SCL) line. The value of register SSPSR<7:1> is compared to the value of the SSPADD register. The address is compared on the falling edge of the eighth clock (SCL) pulse. If the addresses match and the BF and SSPOV bits are clear, the following events occur:

- The SSPSR register value is loaded into the SSPBUF register.

- 2. The Buffer Full bit, BF, is set.

- 3. An ACK pulse is generated.

- The MSSP Interrupt Flag bit, SSPIF, is set (and interrupt is generated, if enabled) on the falling edge of the ninth SCL pulse.

In 10-Bit Address mode, two address bytes need to be received by the slave. The five Most Significant bits (MSbs) of the first address byte specify if this is a 10-bit address. Bit, R/W (SSPSTAT<2>), must specify a write so the slave device will receive the second address byte. For a 10-bit address, the first byte would equal '11110 A9 A8 0', where 'A9' and 'A8' are the two MSbs of the address. The sequence of events for 10-bit address is as follows, with steps 7 through 9 for the slave-transmitter:

- 1. Receive the first (high) byte of address (bits, SSPIF, BF and UA (SSPSTAT<1>), are set).

- 2. Update the SSPADD register with the second (low) byte of address (clears bit, UA, and releases the SCL line).

- 3. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- Receive second (low) byte of address (SSPIF, BF and UA bits are set).

- Update the SSPADD register with the first (high) byte of address. If match releases SCL line, this will clear the UA bit.

- 6. Read the SSPBUF register (clears bit, BF) and clear flag bit, SSPIF.

- 7. Receive Repeated Start condition.

- 8. Receive first (high) byte of address (SSPIF and BF bits are set).

- 9. Read the SSPBUF register (clears BF bit) and clear flag bit, SSPIF.

### REGISTER 23-1: CONFIG1L: CONFIGURATION REGISTER 1 LOW (BYTE ADDRESS 300000h)

| R/WO-1 | R/WO-1 | R/WO-1 | U-0 | U-0 | U-0 | U-0 | R/WO-1 |

|--------|--------|--------|-----|-----|-----|-----|--------|

| DEBUG  | XINST  | STVREN | _   | _   | _   | _   | WDTEN  |

| bit 7  |        |        |     |     |     |     | bit 0  |

Legend:

R = Readable bit WO = Write-Once bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed '1' = Bit is set '0' = Bit is cleared

bit 7 **DEBUG:** Background Debugger Enable bit

1 = Background debugger disabled; RB6 and RB7 configured as general purpose I/O pins

0 = Background debugger enabled; RB6 and RB7 are dedicated to In-Circuit Debug

bit 6 XINST: Extended Instruction Set Enable bit

1 = Instruction set extension and Indexed Addressing mode enabled

0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)

bit 5 STVREN: Stack Overflow/Underflow Reset Enable bit

1 = Reset on stack overflow/underflow enabled0 = Reset on stack overflow/underflow disabled

bit 4-1 **Unimplemented:** Read as '0'

bit 0 WDTEN: Watchdog Timer Enable bit

1 = WDT enabled

0 = WDT disabled (control is placed on the SWDTEN bit)

### REGISTER 23-2: CONFIG1H: CONFIGURATION REGISTER 1 HIGH (BYTE ADDRESS 300001h)

| U-0   | U-0 | U-0 | U-0 | U-0 | R/WO-1 | U-0 | U-0   |

|-------|-----|-----|-----|-----|--------|-----|-------|

| (1)   | (1) | (1) | (1) | (2) | CP0    | _   | _     |

| bit 7 |     |     |     |     |        |     | bit 0 |

Legend:

R = Readable bit WO = Write-Once bit U = Unimplemented bit, read as '0'

-n = Value when device is unprogrammed '1' = Bit is set '0' = Bit is cleared

bit 7-3 **Unimplemented:** Read as '0'

bit 2 **CP0:** Code Protection bit

1 = Program memory is not code-protected

0 = Program memory is code-protected

bit 1-0 Unimplemented: Read as '0'

**Note 1:** The value of these bits in program memory should always be '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

2: This bit should always be maintained as '0'.

| GOTO                                                | Unconditional Branch                                                                                                                                      |                             |                            |                                        |  |  |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|----------------------------|----------------------------------------|--|--|

| Syntax:                                             | GOTO k                                                                                                                                                    | GOTO k                      |                            |                                        |  |  |

| Operands:                                           | $0 \le k \le 10$                                                                                                                                          | 48575                       |                            |                                        |  |  |

| Operation:                                          | $k \rightarrow PC < 20:1 >$                                                                                                                               |                             |                            |                                        |  |  |

| Status Affected:                                    | None                                                                                                                                                      |                             |                            |                                        |  |  |

| Encoding:<br>1st word (k<7:0>)<br>2nd word(k<19:8>) | 1110<br>1111                                                                                                                                              | 1111<br>k <sub>19</sub> kkk | k <sub>7</sub> kkk<br>kkkk | kkkk <sub>0</sub><br>kkkk <sub>8</sub> |  |  |

| Description:                                        | GOTO allows an unconditional branch anywhere within entire 2-Mbyte memory range. The 20-bit value 'k' is loaded into PC<20:1>. GOTO is always a two-cycle |                             |                            |                                        |  |  |

instruction.

Words: 2 Cycles: 2

Q Cycle Activity:

| Q1           | Q2                     | Q3              | Q4                                        |

|--------------|------------------------|-----------------|-------------------------------------------|

| Decode       | Read literal 'k'<7:0>, | No<br>operation | Read literal<br>'k'<19:8>,<br>Write to PC |

| No operation | No operation           | No operation    | No operation                              |

Example: GOTO THERE

After Instruction

PC = Address (THERE)

| INCF              | Increment                                                                                                                                                                                                                                                         | f              |      |                      |  |  |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------|----------------------|--|--|

| Syntax:           | INCF f {,c                                                                                                                                                                                                                                                        | l {,a}}        |      |                      |  |  |

| Operands:         | $0 \le f \le 255$<br>$d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                                                                                               |                |      |                      |  |  |

| Operation:        | (f) + $1 \rightarrow de$                                                                                                                                                                                                                                          | est            |      |                      |  |  |

| Status Affected:  | C, DC, N,                                                                                                                                                                                                                                                         | OV, Z          |      |                      |  |  |

| Encoding:         | 0010                                                                                                                                                                                                                                                              | 10da           | ffff | ffff                 |  |  |

| Description:      | The contents of register 'f' are incremented. If 'd' is '0', the result is placed in W. If 'd' is '1', the result is placed back in register 'f'.                                                                                                                 |                |      |                      |  |  |

|                   | If 'a' is '0', the Access Bank is selected If 'a' is '1', the BSR is used to select the GPR bank.                                                                                                                                                                 |                |      |                      |  |  |

|                   | If 'a' is '0' and the extended instruction set is enabled, this instruction operate in Indexed Literal Offset Addressing mode whenever f ≤ 95 (5Fh). See Section 24.2.3 "Byte-Oriented and Bit-Oriented Instructions in Indexed Literal Offset Mode" for details. |                |      |                      |  |  |

| Words:            | 1                                                                                                                                                                                                                                                                 |                |      |                      |  |  |

| Cycles:           | 1                                                                                                                                                                                                                                                                 |                |      |                      |  |  |

| Q Cycle Activity: |                                                                                                                                                                                                                                                                   |                |      |                      |  |  |

| Q1                | Q2                                                                                                                                                                                                                                                                | Q3             |      | Q4                   |  |  |

| Decode            | Read register 'f'                                                                                                                                                                                                                                                 | Proces<br>Data |      | Write to destination |  |  |

| Example:                                    | INCF             |                    | CNT, | 1, | 0 |

|---------------------------------------------|------------------|--------------------|------|----|---|

| Before Instruct CNT Z C DC After Instructio | =<br>=<br>=<br>= | FFh<br>0<br>?      |      |    |   |

| CNT<br>Z<br>C<br>DC                         | =<br>=<br>=<br>= | 00h<br>1<br>1<br>1 |      |    |   |

| SLE                     | ĒΡ             | Enter Sleep Mode |                                                                                                                                                              |   |                |  |  |  |  |

|-------------------------|----------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|--|--|--|--|

| Synta                   | ax:            | SLEEP            | SLEEP                                                                                                                                                        |   |                |  |  |  |  |

| Oper                    | ands:          | None             | None                                                                                                                                                         |   |                |  |  |  |  |

| Oper                    | ation:         |                  |                                                                                                                                                              |   |                |  |  |  |  |

| Status Affected: TO, PD |                |                  |                                                                                                                                                              |   |                |  |  |  |  |

| Enco                    | ding:          | 0000             | 0000 0000 0000 0011                                                                                                                                          |   |                |  |  |  |  |

| Desc                    | ription:       | cleared. The     | The Power-Down status bit $(\overline{PD})$ is cleared. The Time-out status bit $(\overline{TO})$ is set. The Watchdog Timer and its postscaler are cleared. |   |                |  |  |  |  |

|                         |                | •                | The processor is put into Sleep mode with the oscillator stopped.                                                                                            |   |                |  |  |  |  |

| Word                    | ls:            | 1                | 1                                                                                                                                                            |   |                |  |  |  |  |

| Cycle                   | es:            | 1                |                                                                                                                                                              |   |                |  |  |  |  |

| Q C                     | ycle Activity: |                  |                                                                                                                                                              |   |                |  |  |  |  |

|                         | Q1             | Q2               | Q3                                                                                                                                                           |   | Q4             |  |  |  |  |

|                         | Decode         | No<br>operation  | Process                                                                                                                                                      | s | Go to<br>Sleen |  |  |  |  |

| <u>-xample:</u> |        | SLEEF |

|-----------------|--------|-------|

| Before In       | struc  | ction |

| TO              | =      | ?     |

| PD              | =      | ?     |

| After Inst      | ructio | on    |

| TO              | =      | 1 †   |

| PD              | =      | 0     |

† If WDT causes wake-up, this bit is cleared.

| SUB                    | FWB                                                                                                                                                                                                   | Sub                                                                                                                                                                          | tract f fr                                                        | om W with Bo                                                                                                                  | rrow                                                     |  |  |  |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

| Synta                  | ax:                                                                                                                                                                                                   | SUB                                                                                                                                                                          | FWB f                                                             | {,d {,a}}                                                                                                                     |                                                          |  |  |  |

| •                      | ands:                                                                                                                                                                                                 | $0 \le f \le 255$                                                                                                                                                            |                                                                   |                                                                                                                               |                                                          |  |  |  |

|                        |                                                                                                                                                                                                       | $d \in [0,1]$<br>$a \in [0,1]$                                                                                                                                               |                                                                   |                                                                                                                               |                                                          |  |  |  |

| Oper                   | ation:                                                                                                                                                                                                | $(W) - (f) - (\overline{C}) \rightarrow dest$                                                                                                                                |                                                                   |                                                                                                                               |                                                          |  |  |  |

|                        | s Affected:                                                                                                                                                                                           |                                                                                                                                                                              | V, C, DC                                                          | •                                                                                                                             |                                                          |  |  |  |

| Enco                   | dina:                                                                                                                                                                                                 |                                                                                                                                                                              |                                                                   | 01da fff                                                                                                                      | f ffff                                                   |  |  |  |

| Encoding: Description: |                                                                                                                                                                                                       | Subtract register 'f' and Carry flag (borrow) from W (2's complement method). If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored in register 'f'. |                                                                   |                                                                                                                               |                                                          |  |  |  |

|                        |                                                                                                                                                                                                       | ʻa' is                                                                                                                                                                       | -                                                                 | e Access Bank<br>BSR is used to                                                                                               |                                                          |  |  |  |

|                        |                                                                                                                                                                                                       | set is<br>Inde<br>when<br>Sect<br>Bit-0                                                                                                                                      | s enabled<br>xed Liter<br>never f ≤<br>tion 24.2<br>Oriented      | d the extended<br>d, this instruction<br>al Offset Addre<br>95 (5Fh). See<br>.3 "Byte-Orien<br>Instructions<br>t Mode" for de | on operates in<br>essing mode<br>inted and<br>in Indexed |  |  |  |

| Word                   | s:                                                                                                                                                                                                    | 1                                                                                                                                                                            |                                                                   |                                                                                                                               |                                                          |  |  |  |

| Cycle                  | es:                                                                                                                                                                                                   | 1                                                                                                                                                                            |                                                                   |                                                                                                                               |                                                          |  |  |  |

| Q C                    | ycle Activity:                                                                                                                                                                                        |                                                                                                                                                                              |                                                                   |                                                                                                                               |                                                          |  |  |  |

| ı                      | Q1                                                                                                                                                                                                    |                                                                                                                                                                              | Q2                                                                | Q3                                                                                                                            | Q4                                                       |  |  |  |

|                        | Decode                                                                                                                                                                                                |                                                                                                                                                                              | ead                                                               | Process                                                                                                                       | Write to                                                 |  |  |  |

|                        |                                                                                                                                                                                                       | regi                                                                                                                                                                         | ster 'f'                                                          | Data                                                                                                                          | destination                                              |  |  |  |

|                        | <u>nple 1:</u>                                                                                                                                                                                        |                                                                                                                                                                              | UBFWB                                                             | REG, 1, 0                                                                                                                     |                                                          |  |  |  |

|                        | Before Instruc<br>REG                                                                                                                                                                                 | tion<br>=                                                                                                                                                                    | 3                                                                 |                                                                                                                               |                                                          |  |  |  |

|                        | W                                                                                                                                                                                                     | =                                                                                                                                                                            | 2                                                                 |                                                                                                                               |                                                          |  |  |  |

|                        | C<br>After Instructio                                                                                                                                                                                 | =<br>nn                                                                                                                                                                      | 1                                                                 |                                                                                                                               |                                                          |  |  |  |

|                        | REG                                                                                                                                                                                                   | =                                                                                                                                                                            | FF                                                                |                                                                                                                               |                                                          |  |  |  |

|                        | W                                                                                                                                                                                                     | =                                                                                                                                                                            | 2                                                                 |                                                                                                                               |                                                          |  |  |  |

|                        | C<br>Z                                                                                                                                                                                                |                                                                                                                                                                              | Λ                                                                 |                                                                                                                               |                                                          |  |  |  |

| _                      | _                                                                                                                                                                                                     | =                                                                                                                                                                            | 0                                                                 |                                                                                                                               |                                                          |  |  |  |

|                        | N                                                                                                                                                                                                     |                                                                                                                                                                              | 0                                                                 | esult is negativ                                                                                                              | ⁄e                                                       |  |  |  |

|                        | N<br>nple 2:                                                                                                                                                                                          | =<br>=<br>S1                                                                                                                                                                 | 0                                                                 |                                                                                                                               | /e                                                       |  |  |  |

|                        | N<br>n <u>ple 2:</u><br>Before Instruc                                                                                                                                                                | =<br>=<br>S1                                                                                                                                                                 | 0<br>1 ;r<br>UBFWB                                                |                                                                                                                               | ve                                                       |  |  |  |

|                        | N<br>n <u>ple 2:</u><br>Before Instruc<br>REG<br>W                                                                                                                                                    | =<br>=<br>S1<br>tion<br>=<br>=                                                                                                                                               | 0<br>1 ;r<br>UBFWB<br>2<br>5                                      |                                                                                                                               | ve                                                       |  |  |  |

|                        | N nple 2: Before Instruc REG W C                                                                                                                                                                      | =<br>=<br>S1<br>tion<br>=<br>=<br>=                                                                                                                                          | 0<br>1 ;r<br>UBFWB                                                |                                                                                                                               | /e                                                       |  |  |  |