Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                             |

| Number of I/O              | 51                                                                          |

| Program Memory Size        | 32KB (16K x 16)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 2K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

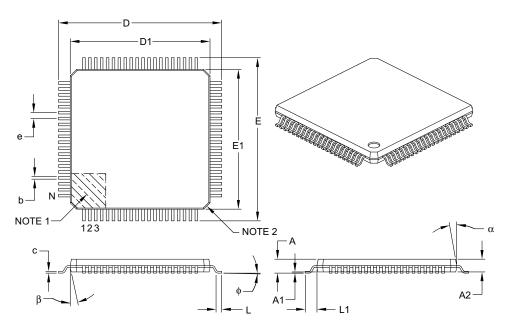

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f65j90t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Din Nama                                                                               | Pin Number       | Pin                | Buffer                           | Description                                                                                                            |  |  |

|----------------------------------------------------------------------------------------|------------------|--------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name                                                                               | TQFP             | Туре               | Туре                             | Description                                                                                                            |  |  |

|                                                                                        |                  |                    |                                  | PORTF is a bidirectional I/O port.                                                                                     |  |  |

| RF1/AN6/C2OUT/SEG19<br>RF1<br>AN6<br>C2OUT<br>SEG19                                    | 23               | I/O<br>I<br>O<br>O | ST<br>Analog<br>—<br>Analog      | Digital I/O.<br>Analog Input 6.<br>Comparator 2 output.<br>SEG19 output for LCD.                                       |  |  |

| RF2/AN7/C1OUT/SEG20<br>RF2<br>AN7<br>C1OUT<br>SEG20                                    | 18               | I/O<br>I<br>O<br>O | ST<br>Analog<br>—<br>Analog      | Digital I/O.<br>Analog Input 7.<br>Comparator 1 output.<br>SEG20 output for LCD.                                       |  |  |

| RF3/AN8/SEG21<br>RF3<br>AN8<br>SEG21                                                   | 17               | I/O<br>I<br>O      | ST<br>Analog<br>Analog           | Digital I/O.<br>Analog Input 8.<br>SEG21 output for LCD.                                                               |  |  |

| RF4/AN9/SEG22<br>RF4<br>AN9<br>SEG22                                                   | 16               | I/O<br>I<br>O      | ST<br>Analog<br>Analog           | Digital I/O.<br>Analog Input 9.<br>SEG22 output for LCD.                                                               |  |  |

| RF5/AN10/CVREF/SEG23<br>RF5<br>AN10<br>CVREF<br>SEG23                                  | 15               | I/O<br>I<br>O<br>O | ST<br>Analog<br>Analog<br>Analog | Digital I/O.<br>Analog Input 10.<br>Comparator reference voltage output.<br>SEG23 output for LCD.                      |  |  |

| RF6/AN11/SEG24<br>RF6<br>AN11<br>SEG24                                                 | 14               | I/O<br>I<br>O      | ST<br>Analog<br>Analog           | Digital I/O.<br>Analog Input 11.<br>SEG24 output for LCD.                                                              |  |  |

| RF7/AN5/SS/SEG25<br>RF7<br>AN5<br>SS<br>SEG25                                          | 13               | I/O<br>O<br>I<br>O | ST<br>Analog<br>TTL<br>Analog    | Digital I/O.<br>Analog Input 5.<br>SPI slave select input.<br>SEG25 output for LCD.                                    |  |  |

| Legend: TTL = TTL cc<br>ST = Schmit<br>I = Input<br>P = Power<br>$I^2C^{TM} = I^2C/SM$ | tt Trigger input | with C             | MOS level                        | CMOS = CMOS compatible input or output<br>s Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD) |  |  |

### TABLE 1-4: PIC18F8XJ90 PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** Default assignment for CCP2 when the CCP2MX Configuration bit is set.

**2:** Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

A CM Reset behaves similarly to a Master Clear Reset, RESET instruction, WDT time-out or Stack Event Resets. As with all hard and power Reset events, the device Configuration Words are reloaded from the Flash Configuration Words in program memory as the device restarts.

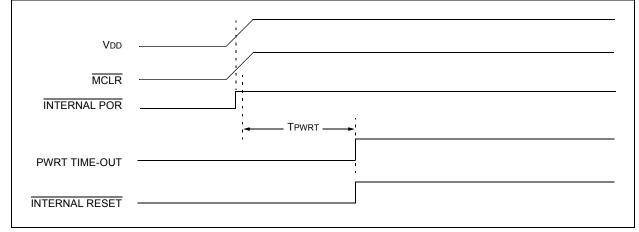

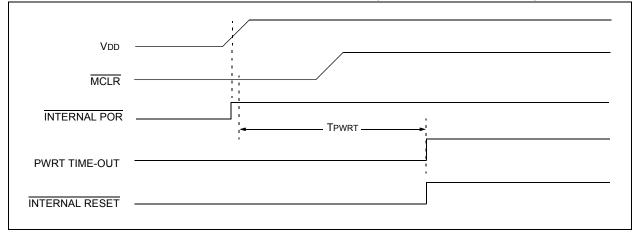

## 5.6 Power-up Timer (PWRT)

PIC18F85J90 family devices incorporate an on-chip Power-up Timer (PWRT) to help regulate the Power-on Reset process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F85J90 family devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset. The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 for details.

### 5.6.1 TIME-OUT SEQUENCE

If enabled, the PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-3, Figure 5-4, Figure 5-5 and Figure 5-6 all depict time-out sequences on power-up with the Power-up Timer enabled.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the PWRT will expire. Bringing MCLR high will begin execution immediately (Figure 5-5). This is useful for testing purposes, or to synchronize more than one PIC18FXXXX device operating in parallel.

#### FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

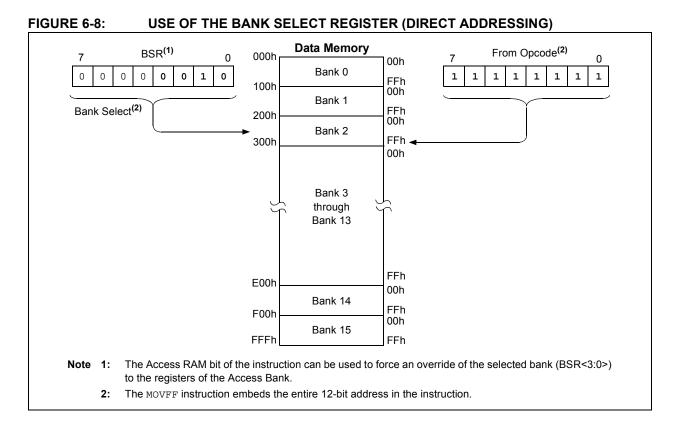

#### 6.3.2 ACCESS BANK

While the use of the BSR with an embedded 8-bit address allows users to address the entire range of data memory, it also means that the user must always ensure that the correct bank is selected. Otherwise, data may be read from, or written to, the wrong location. This can be disastrous if a GPR is the intended target of an operation, but an SFR is written to instead. Verifying and/or changing the BSR for each read or write to data memory can become very inefficient.

To streamline access for the most commonly used data memory locations, the data memory is configured with an Access Bank, which allows users to access a mapped block of memory without specifying a BSR. The Access Bank consists of the first 96 bytes of memory (00h-5Fh) in Bank 0 and the last 160 bytes of memory (60h-FFh) in Bank 15. The lower half is known as the "Access RAM" and is composed of GPRs. The upper half is where the device's SFRs are mapped. These two areas are mapped contiguously in the Access Bank and can be addressed in a linear fashion by an 8-bit address (Figure 6-6).

The Access Bank is used by core PIC18 instructions that include the Access RAM bit (the 'a' parameter in the instruction). When 'a' is equal to '1', the instruction uses the BSR and the 8-bit address included in the opcode for the data memory address. When 'a' is '0',

however, the instruction is forced to use the Access Bank address map; the current value of the BSR is ignored entirely.

Using this "forced" addressing allows the instruction to operate on a data address in a single cycle without updating the BSR first. For 8-bit addresses of 60h and above, this means that users can evaluate and operate on SFRs more efficiently. The Access RAM below 60h is a good place for data values that the user might need to access rapidly, such as immediate computational results or common program variables. Access RAM also allows for faster and more code efficient context saving and switching of variables.

The mapping of the Access Bank is slightly different when the extended instruction set is enabled (XINST Configuration bit = 1). This is discussed in more detail in Section 6.6.3 "Mapping the Access Bank in Indexed Literal Offset Mode".

#### 6.3.3 GENERAL PURPOSE REGISTER FILE

PIC18 devices may have banked memory in the GPR area. This is data RAM which is available for use by all instructions. GPRs start at the bottom of Bank 0 (address 000h) and grow upwards towards the bottom of the SFR area. GPRs are not initialized by a Power-on Reset and are unchanged on all other Resets.

| TABLE 6-3: | PIC18F85J90 FAMILY REGISTER FILE SUMMARY (CONTINUED) |

|------------|------------------------------------------------------|

|------------|------------------------------------------------------|

| File Name                | Bit 7                | Bit 6                | Bit 5                | Bit 4                | Bit 3                | Bit 2                | Bit 1                | Bit 0  | Value on<br>POR, BOR | Details<br>on page |

|--------------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|--------|----------------------|--------------------|

| PORTJ <sup>(2)</sup>     | RJ7                  | RJ6                  | RJ5                  | RJ4                  | RJ3                  | RJ2                  | RJ1                  | RJ0    | xxxx xxxx            | 60, 136            |

| PORTH <sup>(2)</sup>     | RH7                  | RH6                  | RH5                  | RH4                  | RH3                  | RH2                  | RH1                  | RH0    | xxxx xxxx            | 60, 134            |

| PORTG                    | RDPU                 | REPU                 | RJPU <sup>(2)</sup>  | RG4                  | RG3                  | RG2                  | RG1                  | RG0    | 000x xxxx            | 60, 132            |

| PORTF                    | RF7                  | RF6                  | RF5                  | RF4                  | RF3                  | RF2                  | RF1                  | _      | xxxx xxx-            | 60, 130            |

| PORTE                    | RE7                  | RE6                  | RE5                  | RE4                  | RE3                  | _                    | RE1                  | RE0    | xxxx x-xx            | 61, 127            |

| PORTD                    | RD7                  | RD6                  | RD5                  | RD4                  | RD3                  | RD2                  | RD1                  | RD0    | xxxx xxxx            | 61, 125            |

| PORTC                    | RC7                  | RC6                  | RC5                  | RC4                  | RC3                  | RC2                  | RC1                  | RC0    | xxxx xxxx            | 61, 123            |

| PORTB                    | RB7                  | RB6                  | RB5                  | RB4                  | RB3                  | RB2                  | RB1                  | RB0    | xxxx xxxx            | 61, 120            |

| PORTA                    | RA7 <sup>(5)</sup>   | RA6 <sup>(5)</sup>   | RA5                  | RA4                  | RA3                  | RA2                  | RA1                  | RA0    | xx0x 0000            | 61, 117            |

| SPBRGH1                  | EUSART Ba            | ud Rate Gene         | rator High By        | e                    |                      |                      |                      |        | 0000 0000            | 61, 240            |

| BAUDCON1                 | ABDOVF               | RCIDL                | RXDTP                | TXCKP                | BRG16                | _                    | WUE                  | ABDEN  | 0100 0-00            | 61, 238            |

| LCDDATA23 <sup>(2)</sup> | S47C3                | S46C3                | S45C3                | S44C3                | S43C3                | S42C3                | S41C3                | S40C3  | xxxx xxxx            | 61, 167            |

| LCDDATA22                | S39C3 <sup>(2)</sup> | S38C3 <sup>(2)</sup> | S37C3 <sup>(2)</sup> | S36C3 <sup>(2)</sup> | S35C3 <sup>(2)</sup> | S34C3 <sup>(2)</sup> | S33C3 <sup>(2)</sup> | S32C3  | xxxx xxxx            | 61, 167            |

| LCDDATA21                | S31C3                | S30C3                | S29C3                | S28C3                | S27C3                | S26C3                | S25C3                | S24C3  | xxxx xxxx            | 61, 167            |

| LCDDATA20                | S23C3                | S22C3                | S21C3                | S20C3                | S19C3                | S18C3                | S17C3                | S16C3  | xxxx xxxx            | 61, 167            |

| LCDDATA19                | S15C3                | S14C3                | S13C3                | S12C3                | S11C3                | S10C3                | S09C3                | S08C3  | xxxx xxxx            | 61, 167            |

| LCDDATA18                | S07C3                | S06C3                | S05C3                | S04C3                | S03C3                | S02C3                | S01C3                | S00C3  | xxxx xxxx            | 61, 167            |

| LCDDATA17 <sup>(2)</sup> | S47C2                | S46C2                | S45C2                | S44C2                | S43C2                | S42C2                | S41C2                | S40C2  | xxxx xxxx            | 61, 167            |

| LCDDATA16                | S39C2 <sup>(2)</sup> | S38C2 <sup>(2)</sup> | S37C2 <sup>(2)</sup> | S36C2 <sup>(2)</sup> | S35C2 <sup>(2)</sup> | S34C2 <sup>(2)</sup> | S33C2 <sup>(2)</sup> | S32C2  | xxxx xxxx            | 61, 167            |

| LCDDATA15                | S31C2                | S30C2                | S29C2                | S28C2                | S27C2                | S26C2                | S25C2                | S24C2  | xxxx xxxx            | 61, 167            |

| LCDDATA14                | S23C2                | S22C2                | S21C2                | S20C2                | S19C2                | S18C2                | S17C2                | S16C2  | xxxx xxxx            | 61, 167            |

| LCDDATA13                | S15C2                | S14C2                | S13C2                | S12C2                | S11C2                | S10C2                | S09C2                | S08C2  | xxxx xxxx            | 61, 167            |

| LCDDATA12                | S07C2                | S06C2                | S05C2                | S04C2                | S03C2                | S02C2                | S01C2                | S00C2  | xxxx xxxx            | 61, 167            |

| LCDDATA11 <sup>(2)</sup> | S47C1                | S46C1                | S45C1                | S44C1                | S43C1                | S42C1                | S41C1                | S40C1  | xxxx xxxx            | 61, 167            |

| LCDDATA10                | S39C1 <sup>(2)</sup> | S38C1 <sup>(2)</sup> | S37C1 <sup>(2)</sup> | S36C1 <sup>(2)</sup> | S35C1 <sup>(2)</sup> | S34C1 <sup>(2)</sup> | S33C1 <sup>(2)</sup> | S32C1  | xxxx xxxx            | 61, 167            |

| LCDDATA9                 | S31C1                | S30C1                | S29C1                | S28C1                | S27C1                | S26C1                | S25C1                | S24C1  | xxxx xxxx            | 61, 167            |

| LCDDATA8                 | S23C1                | S22C1                | S21C1                | S20C1                | S19C1                | S18C1                | S17C1                | S16C1  | xxxx xxxx            | 61, 167            |

| LCDDATA7                 | S15C1                | S14C1                | S13C1                | S12C1                | S11C1                | S10C1                | S09C1                | S08C1  | xxxx xxxx            | 61, 167            |

| LCDDATA6                 | S07C1                | S06C1                | S05C1                | S04C1                | S03C1                | S02C1                | S01C1                | S00C1  | xxxx xxxx            | 61, 167            |

| LCDDATA5 <sup>(2)</sup>  | S47C0                | S46C0                | S45C0                | S44C0                | S43C0                | S42C0                | S41C0                | S40C0  | xxxx xxxx            | 61, 167            |

| CCPR1H                   | Capture/Com          | pare/PWM R           | egister 1 High       | Byte                 |                      |                      |                      |        | xxxx xxxx            | 61, 154            |

| CCPR1L                   | Capture/Com          | pare/PWM R           | egister 1 Low        | Byte                 |                      |                      |                      |        | xxxx xxxx            | 61, 154            |

| CCP1CON                  | —                    | —                    | DC1B1                | DC1B0                | CCP1M3               | CCP1M2               | CCP1M1               | CCP1M0 | 00 0000              | 61, 153            |

| CCPR2H                   | Capture/Com          | pare/PWM R           | egister 2 High       | Byte                 |                      |                      |                      |        | xxxx xxxx            | 61, 154            |

| CCPR2L                   | Capture/Com          | pare/PWM R           | egister 2 Low        | Byte                 |                      |                      |                      |        | xxxx xxxx            | 62, 154            |

| CCP2CON                  | —                    | _                    | DC2B1                | DC2B0                | CCP2M3               | CCP2M2               | CCP2M1               | CCP2M0 | 00 0000              | 62, 153            |

| SPBRG2                   | AUSART Ba            | ud Rate Gene         | rator Register       |                      |                      |                      |                      |        | 0000 0000            | 62, 260            |

| RCREG2                   | AUSART Re            | ceive Register       |                      |                      |                      |                      |                      |        | 0000 0000            | 62, 265            |

| TXREG2                   | AUSART Tra           | nsmit Registe        | r                    |                      |                      |                      |                      |        | 0000 0000            | 62, 263            |

| TXSTA2                   | CSRC                 | TX9                  | TXEN                 | SYNC                 | —                    | BRGH                 | TRMT                 | TX9D   | 0000 -010            | 62, 258            |

| RCSTA2                   | SPEN                 | RX9                  | SREN                 | CREN                 | ADDEN                | FERR                 | OERR                 | RX9D   | 0000 000x            | 62, 259            |

Legend: x = unknown, u = unchanged, - = unimplemented, q = value depends on condition, r = reserved, do not modify

Note 1: Bit 21 of the PC is only available in Test mode and Serial Programming modes.

2: These registers and/or bits are available only on 80-pin devices; otherwise, they are unimplemented and read as '0'. Reset states shown are for 80-pin devices.

3: Alternate names and definitions for these bits when the MSSP module is operating in I<sup>2</sup>C<sup>™</sup> Slave mode. See Section 17.4.3.2 "Address Masking" for details.

4: The PLLEN bit is only available in specific oscillator configurations; otherwise, it is disabled and reads as '0'. See Section 3.4.3 "PLL Frequency Multiplier" for details.

5: RA6/RA7 and their associated latch and direction bits are configured as port pins only when the internal oscillator is selected as the default clock source (FOSC2 Configuration bit = 0); otherwise, they are disabled and these bits read as '0'.

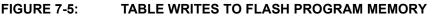

## 7.5 Writing to Flash Program Memory

The minimum programming block is 32 words or 64 bytes. Word or byte programming is not supported.

Table writes are used internally to load the holding registers needed to program the Flash memory. There are 64 holding registers used by the table writes for programming.

Since the Table Latch (TABLAT) is only a single byte, the TBLWT instruction may need to be executed 64 times for each programming operation. All of the table write operations will essentially be short writes because only the holding registers are written. At the end of updating the 64 holding registers, the EECON1 register must be written to in order to start the programming operation with a long write.

The long write is necessary for programming the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer. The on-chip timer controls the write time. The write/erase voltages are generated by an on-chip charge pump, rated to operate over the voltage range of the device.

- Note 1: Unlike previous PIC<sup>®</sup> devices, members of the PIC18F85J90 family do not reset the holding registers after a write occurs. The holding registers must be cleared or overwritten before a programming sequence.

- 2: To maintain the endurance of the program memory cells, each Flash byte should not be programmed more than one time between erase operations. Before attempting to modify the contents of the target cell a second time, a block erase of the target block, or a bulk erase of the entire memory, must be performed.

#### 7.5.1 FLASH PROGRAM MEMORY WRITE SEQUENCE

The sequence of events for programming an internal program memory location should be:

- 1. Read 1024 bytes into RAM.

- 2. Update data values in RAM as necessary.

- 3. Load the Table Pointer register with the address being erased.

- 4. Execute the block erase procedure.

- 5. Load the Table Pointer register with the address of the first byte being written, minus 1.

- 6. Write the 64 bytes into the holding registers with auto-increment.

- 7. Set the WREN bit (EECON1<2>) to enable byte writes.

- 8. Disable interrupts.

- 9. Write 55h to EECON2.

- 10. Write 0AAh to EECON2.

- 11. Set the WR bit; this will begin the write cycle.

- 12. The CPU will stall for the duration of the write for TIW (see parameter D133A).

- 13. Re-enable interrupts.

- 14. Repeat steps 6 through 13 until all 1024 bytes are written to program memory.

- 15. Verify the memory (table read).

An example of the required code is shown in Example 7-3 on the following page.

Note: Before setting the WR bit, the Table Pointer address needs to be within the intended address range of the 64 bytes in the holding register.

## 10.3 PORTB, TRISB and LATB Registers

PORTB is an 8-bit wide, bidirectional port. The corresponding Data Direction and Data Latch registers are TRISB and LATB. All pins on PORTB are digital only and tolerate voltages up to 5.5V.

#### EXAMPLE 10-2: INITIALIZING PORTB

| CLRF  | PORTB | ; Initialize PORTB by<br>; clearing output |

|-------|-------|--------------------------------------------|

|       |       | ; data latches                             |

| CLRF  | LATB  | ; Alternate method                         |

|       |       | ; to clear output                          |

|       |       | ; data latches                             |

| MOVLW | OCFh  | ; Value used to                            |

|       |       | ; initialize data                          |

|       |       | ; direction                                |

| MOVWF | TRISB | ; Set RB<3:0> as inputs                    |

|       |       | ; RB<5:4> as outputs                       |

|       |       | ; RB<7:6> as inputs                        |

|       |       |                                            |

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn <u>on all</u> the pull-ups. This is performed by clearing bit, RBPU (INTCON2<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset.

Four of the PORTB pins (RB<7:4>) have an interrupt-on-change feature. Only pins configured as inputs can cause this interrupt to occur (i.e., any RB<7:4> pin configured as an output is excluded from the interrupt-on-change comparison). The input pins (of RB<7:4>) are compared with the old value latched on the last read of PORTB. The "mismatch" outputs of RB<7:4> are ORed together to generate the RB Port Change Interrupt with Flag bit, RBIF (INTCON<0>).

This interrupt can wake the device from power-managed modes. The user, in the Interrupt Service Routine, can clear the interrupt in the following manner:

- a) Any read or write of PORTB (except with the MOVFF (ANY), PORTB instruction). This will end the mismatch condition.

- b) Wait one instruction cycle (such as executing a NOP instruction).

- c) Clear flag bit, RBIF.

A mismatch condition will continue to set flag bit, RBIF. Reading PORTB will end the mismatch condition and allow flag bit, RBIF, to be cleared after one TCY delay.

The interrupt-on-change feature is recommended for wake-up on key depression operation and operations where PORTB is only used for the interrupt-on-change feature. Polling of PORTB is not recommended while using the interrupt-on-change feature.

RB<5:0> are also multiplexed with LCD segment drives, controlled by bits in the LCDSE1 and LCDSE3 registers. I/O port functionality is only available when the LCD segments are disabled.

| TABLE 10-6: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTB |

|-------------|--------------------------------------------|

|-------------|--------------------------------------------|

| Name    | Bit 7    | Bit 6     | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1  | Bit 0  | Reset<br>Values on<br>page |

|---------|----------|-----------|---------|---------|---------|--------|--------|--------|----------------------------|

| PORTB   | RB7      | RB6       | RB5     | RB4     | RB3     | RB2    | RB1    | RB0    | 61                         |

| LATB    | LATB7    | LATB6     | LATB5   | LATB4   | LATB3   | LATB2  | LATB1  | LATB0  | 60                         |

| TRISB   | TRISB7   | TRISB6    | TRISB5  | TRISB4  | TRISB3  | TRISB2 | TRISB1 | TRISB0 | 60                         |

| INTCON  | GIE/GIEH | PEIE/GIEL | TMR0IE  | INT0IE  | RBIE    | TMR0IF | INT0IF | RBIF   | 57                         |

| INTCON2 | RBPU     | INTEDG0   | INTEDG1 | INTEDG2 | INTEDG3 | TMR0IP | INT3IP | RBIP   | 57                         |

| INTCON3 | INT2IP   | INT1IP    | INT3IE  | INT2IE  | INT1IE  | INT3IF | INT2IF | INT1IF | 57                         |

| LCDSE1  | SE15     | SE14      | SE13    | SE12    | SE11    | SE10   | SE09   | SE08   | 59                         |

| LCDSE3  | SE31     | SE30      | SE29    | SE28    | SE27    | SE26   | SE25   | SE24   | 59                         |

Legend: Shaded cells are not used by PORTB.

# 10.5 PORTD, TRISD and LATD Registers

PORTD is an 8-bit wide, bidirectional port. The corresponding Data Direction and Data Latch registers are TRISD and LATD. All pins on PORTD are digital only and tolerate voltages up to 5.5V.

All pins on PORTD are implemented with Schmitt Trigger input buffers. Each pin is individually configurable as an input or output.

| Note: | These pins are configured as digital inputs |

|-------|---------------------------------------------|

|       | on any device Reset.                        |

Each of the PORTD pins has a weak internal pull-up. A single control bit can turn off all the pull-ups. This is performed by clearing bit, RDPU (PORTG<7>). The weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on all device Resets.

All of the PORTD pins are multiplexed with LCD segment drives, controlled by bits in the LCDSE0 register. I/O port functionality is only available when the LCD segments are disabled.

EXAMPLE 10-4: INITIALIZING PORTD

| CLRF POR  | ; clearing output          |

|-----------|----------------------------|

|           | ; data latches             |

| CLRF LAT  | D ; Alternate method       |

|           | ; to clear output          |

|           | ; data latches             |

| MOVLW OCF | h ; Value used to          |

|           | ; initialize data          |

|           | ; direction                |

| MOVWF TRI | SD ; Set RD<3:0> as inputs |

|           | ; RD<5:4> as outputs       |

|           | ; RD<7:6> as inputs        |

|           |                            |

## 13.0 TIMER2 MODULE

The Timer2 module incorporates the following features:

- 8-bit Timer and Period registers (TMR2 and PR2, respectively)

- Readable and writable (both registers)

- Software programmable prescaler (1:1, 1:4 and 1:16)

- Software programmable postscaler (1:1 through 1:16)

- Interrupt on TMR2 to PR2 match

- Optional use as the shift clock for the MSSP module

The module is controlled through the T2CON register (Register 13-1) which enables or disables the timer and configures the prescaler and postscaler. Timer2 can be shut off by clearing control bit, TMR2ON (T2CON<2>), to minimize power consumption.

A simplified block diagram of the module is shown in Figure 13-1.

## 13.1 Timer2 Operation

In normal operation, TMR2 is incremented from 00h on each clock (Fosc/4). A 4-bit counter/prescaler on the clock input gives direct input, divide-by-4 and divide-by-16 prescale options. These are selected by the prescaler control bits, T2CKPS<1:0> (T2CON<1:0>). The value of TMR2 is compared to that of the Period register, PR2, on each clock cycle. When the two values match, the comparator generates a match signal as the timer output. This signal also resets the value of TMR2 to 00h on the next cycle and drives the output counter/postscaler (see Section 13.2 "Timer2 Interrupt").

The TMR2 and PR2 registers are both directly readable and writable. The TMR2 register is cleared on any device Reset, while the PR2 register initializes at FFh. Both the prescaler and postscaler counters are cleared on the following events:

- a write to the TMR2 register

- · a write to the T2CON register

- any device Reset (Power-on Reset, MCLR Reset, Watchdog Timer Reset or Brown-out Reset)

TMR2 is not cleared when T2CON is written.

#### REGISTER 13-1: T2CON: TIMER2 CONTROL REGISTER

| U-0   | R/W-0    | R/W-0    | R/W-0    | R/W-0    | R/W-0  | R/W-0   | R/W-0   |

|-------|----------|----------|----------|----------|--------|---------|---------|

| —     | T2OUTPS3 | T2OUTPS2 | T2OUTPS1 | T2OUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 |

| bit 7 |          |          |          |          |        |         | bit 0   |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7   | Unimplemented: Read as '0'                        |

|---------|---------------------------------------------------|

| bit 6-3 | T2OUTPS<3:0>: Timer2 Output Postscale Select bits |

|         | 0000 = 1:1 Postscale                              |

|         | 0001 = 1:2 Postscale                              |

|         | •                                                 |

|         | •                                                 |

|         |                                                   |

|         | 1111 = 1:16 Postscale                             |

| bit 2   | TMR2ON: Timer2 On bit                             |

|         | 1 = Timer2 is on                                  |

|         | 0 = Timer2 is off                                 |

| bit 1-0 | T2CKPS<1:0>: Timer2 Clock Prescale Select bits    |

|         | 00 = Prescaler is 1                               |

|         | 01 = Prescaler is 4                               |

|         | 1x = Prescaler is 16                              |

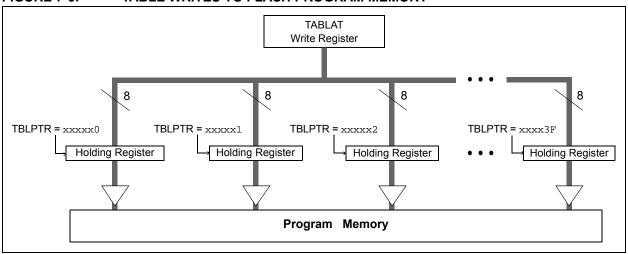

## 15.3 Compare Mode

In Compare mode, the 16-bit CCPR2 register value is constantly compared against either the TMR1 or TMR3 register pair value. When a match occurs, the CCP2 pin can be:

- driven high

- · driven low

- toggled (high-to-low or low-to-high)

- remain unchanged (that is, reflects the state of the I/O latch)

The action on the pin is based on the value of the mode select bits (CCP2M<3:0>). At the same time, the interrupt flag bit, CCP2IF, is set.

#### 15.3.1 CCP PIN CONFIGURATION

The user must configure the CCPx pin as an output by clearing the appropriate TRIS bit.

| Clearing the CCP2CON register will force    |  |  |  |  |  |

|---------------------------------------------|--|--|--|--|--|

| the RC1 or RE7 compare output latch         |  |  |  |  |  |

| (depending on device configuration) to the  |  |  |  |  |  |

| default low level. This is not the PORTC or |  |  |  |  |  |

| PORTE I/O data latch.                       |  |  |  |  |  |

|                                             |  |  |  |  |  |

#### 15.3.2 TIMER1/TIMER3 MODE SELECTION

Timer1 and/or Timer3 must be running in Timer mode, or Synchronized Counter mode, if the CCP module is using the compare feature. In Asynchronous Counter mode, the compare operation may not work.

#### 15.3.3 SOFTWARE INTERRUPT MODE

When the Generate Software Interrupt mode is chosen (CCP2M<3:0> = 1010), the CCP2 pin is not affected. Only a CCP interrupt is generated, if enabled, and the CCP2IE bit is set.

#### 15.3.4 SPECIAL EVENT TRIGGER

Both CCP modules are equipped with a Special Event Trigger. This is an internal hardware signal generated in Compare mode to trigger actions by other modules. The Special Event Trigger is enabled by selecting the Compare Special Event Trigger mode (CCP2M<3:0> = 1011).

For either CCP module, the Special Event Trigger resets the timer register pair for whichever timer resource is currently assigned as the module's time base. This allows the CCPRx registers to serve as a programmable period register for either timer.

The Special Event Trigger for CCP2 can also start an A/D conversion. In order to do this, the A/D Converter must already be enabled.

**Note:** The Special Event Trigger of CCP1 only resets Timer1/Timer3 and cannot start an A/D conversion even when the A/D Converter is enabled.

## FIGURE 15-3: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 17.4.10 I<sup>2</sup>C MASTER MODE TRANSMISSION

Transmission of a data byte, a 7-bit address or the other half of a 10-bit address is accomplished by simply writing a value to the SSPBUF register. This action will set the Buffer Full bit, BF, and allow the Baud Rate Generator to begin counting and start the next transmission. Each bit of address/data will be shifted out onto the SDA pin after the falling edge of SCL is asserted (see data hold time specification parameter 106). SCL is held low for one Baud Rate Generator rollover count (TBRG). Data should be valid before SCL is released high (see data setup time specification parameter 107). When the SCL pin is released high, it is held that way for TBRG. The data on the SDA pin must remain stable for that duration and some hold time after the next falling edge of SCL. After the eighth bit is shifted out (the falling edge of the eighth clock), the BF flag is cleared and the master releases SDA. This allows the slave device being addressed to respond with an ACK bit during the ninth bit time if an address match occurred, or if data was received properly. The status of ACK is written into the ACKDT bit on the falling edge of the ninth clock. If the master receives an Acknowledge, the Acknowledge Status bit, ACKSTAT, is cleared; if not, the bit is set. After the ninth clock, the SSPIF bit is set and the master clock (Baud Rate Generator) is suspended until the next data byte is loaded into the SSPBUF, leaving SCL low and SDA unchanged (Figure 17-23).

After the write to the SSPBUF, each bit of the address will be shifted out on the falling edge of SCL until all seven address bits and the R/W bit are completed. On the falling edge of the eighth clock, the master will deassert the SDA pin, allowing the slave to respond with an Acknowledge. On the falling edge of the ninth clock, the master will sample the SDA pin to see if the address was recognized by a slave. The status of the ACK bit is loaded into the ACKSTAT status bit (SSPCON2<6>). Following the falling edge of the ninth clock transmission of the address, the SSPIF is set, the BF flag is cleared and the Baud Rate Generator is turned off until another write to the SSPBUF takes place, holding SCL low and allowing SDA to float.

#### 17.4.10.1 BF Status Flag

In Transmit mode, the BF bit (SSPSTAT<0>) is set when the CPU writes to SSPBUF and is cleared when all 8 bits are shifted out.

## 17.4.10.2 WCOL Status Flag

If the user writes to the SSPBUF when a transmit is already in progress (i.e., SSPSR is still shifting out a data byte), the WCOL is set and the contents of the buffer are unchanged (the write doesn't occur) after 2 TcY after the SSPBUF write. If SSPBUF is rewritten within 2 TcY, the WCOL bit is set and SSPBUF is updated. This may result in a corrupted transfer. The user should verify that the WCOL is clear after each write to SSPBUF to ensure the transfer is correct. In all cases, WCOL must be cleared in software.

## 17.4.10.3 ACKSTAT Status Flag

In Transmit mode, the ACKSTAT bit (SSPCON2<6>) is cleared when the slave has sent an Acknowledge  $(\overline{ACK} = 0)$  and is set when the slave does not Acknowledge  $(\overline{ACK} = 1)$ . A slave sends an Acknowledge when it has recognized its address (including a general call), or when the slave has properly received its data.

## 17.4.11 I<sup>2</sup>C MASTER MODE RECEPTION

Master mode reception is enabled by programming the Receive Enable bit, RCEN (SSPCON2<3>).

Note: The MSSP module must be in an Idle state before the RCEN bit is set or the RCEN bit will be disregarded.

The Baud Rate Generator begins counting and on each rollover, the state of the SCL pin changes (high-to-low/low-to-high) and data is shifted into the SSPSR. After the falling edge of the eighth clock, the receive enable flag is automatically cleared, the contents of the SSPSR are loaded into the SSPBUF, the BF flag bit is set, the SSPIF flag bit is set and the Baud Rate Generator is suspended from counting, holding SCL low. The MSSP is now in Idle state awaiting the next command. When the buffer is read by the CPU, the BF flag bit is automatically cleared. The user can then send an Acknowledge bit at the end of reception by setting the Acknowledge Sequence Enable bit, ACKEN (SSPCON2<4>).

## 17.4.11.1 BF Status Flag

In receive operation, the BF bit is set when an address or data byte is loaded into SSPBUF from SSPSR. It is cleared when the SSPBUF register is read.

## 17.4.11.2 SSPOV Status Flag

In receive operation, the SSPOV bit is set when 8 bits are received into the SSPSR and the BF flag bit is already set from a previous reception.

#### 17.4.11.3 WCOL Status Flag

If the user writes the SSPBUF when a receive is already in progress (i.e., SSPSR is still shifting in a data byte), the WCOL bit is set and the contents of the buffer are unchanged (the write doesn't occur).

| R/W-0       | R/W-0                             | R/W-0                                                | R/W-0         | R/W-0             | R/W-0            | R-1             | R/W-0 |

|-------------|-----------------------------------|------------------------------------------------------|---------------|-------------------|------------------|-----------------|-------|

| CSRC        | TX9                               | TXEN <sup>(1)</sup>                                  | SYNC          | SENDB             | BRGH             | TRMT            | TX9D  |

| oit 7       |                                   |                                                      |               | ·                 |                  |                 | bit   |

|             |                                   |                                                      |               |                   |                  |                 |       |

| Legend:     |                                   |                                                      |               |                   |                  |                 |       |

| R = Readab  | le bit                            | W = Writable                                         | bit           | U = Unimplem      | nented bit, read | d as '0'        |       |

| n = Value a | t POR                             | '1' = Bit is set                                     |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 7       | CSRC: Clock                       | k Source Select                                      | bit           |                   |                  |                 |       |

|             | <u>Asynchronou</u><br>Don't care. | <u>is mode:</u>                                      |               |                   |                  |                 |       |

|             |                                   | <u>s mode:</u><br>node (clock gen<br>ode (clock from |               |                   |                  |                 |       |

| bit 6       |                                   | ansmit Enable I                                      |               | 0)                |                  |                 |       |

|             |                                   | 9-bit transmissio                                    |               |                   |                  |                 |       |

|             | 0 = Selects                       | 8-bit transmissio                                    | on            |                   |                  |                 |       |

| oit 5       | TXEN: Trans                       | smit Enable bit <sup>(1</sup>                        | )             |                   |                  |                 |       |

|             | 1 = Transmi<br>0 = Transmi        |                                                      |               |                   |                  |                 |       |

| oit 4       | SYNC: AUS                         | ART Mode Sele                                        | ct bit        |                   |                  |                 |       |

|             | 1 = Synchro<br>0 = Asynchr        |                                                      |               |                   |                  |                 |       |

| oit 3       | SENDB: Ser                        | nd Break Chara                                       | cter bit      |                   |                  |                 |       |

|             | <u>Asynchronou</u>                | <u>is mode:</u>                                      |               |                   |                  |                 |       |

|             |                                   | vnc Break on ne<br>eak transmissio                   |               | n (cleared by ha  | ardware upon c   | completion)     |       |

|             | <u>Synchronous</u><br>Don't care. | <u>s mode:</u>                                       |               |                   |                  |                 |       |

| oit 2       | BRGH: High                        | Baud Rate Sel                                        | ect bit       |                   |                  |                 |       |

|             | Asynchronou<br>1 = High spe       | eed                                                  |               |                   |                  |                 |       |

|             | 0 = Low spe                       | <u>s mode:</u>                                       |               |                   |                  |                 |       |

| bit 1       | Unused in th<br>TRMT: Trans       | smit Shift Regist                                    | er Status bit |                   |                  |                 |       |

|             | 1 = TSR em<br>0 = TSR full        |                                                      |               |                   |                  |                 |       |

| bit 0       | TX9D: 9th bi                      | t of Transmit Da                                     | ita           |                   |                  |                 |       |

|             | Can be addre                      | ess/data bit or a                                    | parity bit.   |                   |                  |                 |       |

|             | REN/CREN ov                       |                                                      |               |                   |                  |                 |       |

## REGISTER 18-1: TXSTA1: EUSART TRANSMIT STATUS AND CONTROL REGISTER

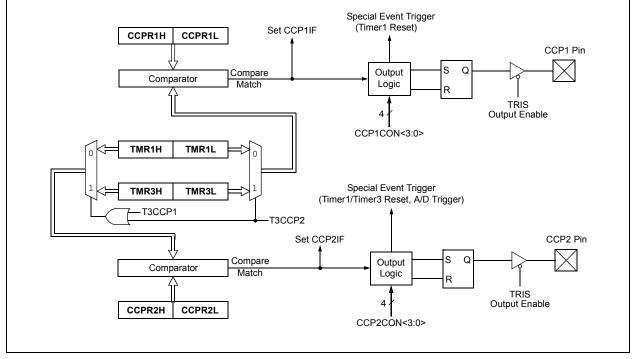

#### FIGURE 22-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

## 22.2 Voltage Reference Accuracy/Error

The full range of voltage reference cannot be realized due to the construction of the module. The transistors on the top and bottom of the resistor ladder network (Figure 22-1) keep CVREF from approaching the reference source rails. The voltage reference is derived from the reference source; therefore, the CVREF output changes with fluctuations in that source. The tested absolute accuracy of the voltage reference can be found in **Section 26.0 "Electrical Characteristics"**.

## 22.3 Operation During Sleep

When the device wakes up from Sleep through an interrupt or a Watchdog Timer time-out, the contents of the CVRCON register are not affected. To minimize current consumption in Sleep mode, the voltage reference should be disabled.

## 22.4 Effects of a Reset

A device Reset disables the voltage reference by clearing bit, CVREN (CVRCON<7>). This Reset also disconnects the reference from the RA2 pin by clearing bit, CVROE (CVRCON<6>) and selects the high-voltage range by clearing bit, CVRR (CVRCON<5>). The CVR value select bits are also cleared.

## 22.5 Connection Considerations

The voltage reference module operates independently of the comparator module. The output of the reference generator may be connected to the RF5 pin if the CVROE bit is set. Enabling the voltage reference output onto RA2 when it is configured as a digital input will increase current consumption. Connecting RF5 as a digital output with CVRSS enabled will also increase current consumption.

The RF5 pin can be used as a simple D/A output with limited drive capability. Due to the limited current drive capability, a buffer must be used on the voltage reference output for external connections to VREF. Figure 22-2 shows an example buffering technique.

PLL (HS+PLL)

#### REGISTER 23-3: CONFIG2L: CONFIGURATION REGISTER 2 LOW (BYTE ADDRESS 300002h)

| R/WO-1 | R/WO-1 | U-0 | U-0 | U-0 | R/WO-1 | R/WO-1 | R/WO-1 |

|--------|--------|-----|-----|-----|--------|--------|--------|

| IESO   | FCMEN  | —   | —   | —   | FOSC2  | FOSC1  | FOSC0  |

| bit 7  |        |     |     |     |        |        | bit 0  |

|        |        |     |     |     |        |        |        |

| Legend:                                |                     |                     |                      |

|----------------------------------------|---------------------|---------------------|----------------------|

| R = Readable bit                       | WO = Write-Once bit | U = Unimplemented I | bit, read as '0'     |

| -n = Value when device is unprogrammed |                     | '1' = Bit is set    | '0' = Bit is cleared |

| bit 7   | IESO: Two-Speed Start-up (Internal/External Oscillator Switchover) Control bit<br>1 = Two-Speed Start-up is enabled<br>0 = Two-Speed Start-up is disabled |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | FCMEN: Fail-Safe Clock Monitor Enable bit                                                                                                                 |

|         | 1 = Fail-Safe Clock Monitor is enabled                                                                                                                    |

|         | 0 = Fail-Safe Clock Monitor is disabled                                                                                                                   |

| bit 5-3 | Unimplemented: Read as '0'                                                                                                                                |

| bit 2-0 | FOSC<2:0>: Oscillator Selection bits                                                                                                                      |

|         | 111 = OSC1/OSC2 as primary; EC oscillator with CLKO function and software controlled<br>PLL (EC+PLL)                                                      |

|         | 110 = OSC1/OSC2 as primary; EC oscillator with CLKO function (EC)                                                                                         |

|         | 101 = OSC1/OSC2 as primary; HS oscillator with software controlled PLL (HS+PLL)                                                                           |

|         | 100 = OSC1/OSC2 as primary; HS oscillator (HS)                                                                                                            |

|         | 011 = INTOSC with CLKO as primary; port function on RA7; EC oscillator with CLKO function and                                                             |

|         | software controlled PLL (EC+PLL)                                                                                                                          |

|         | 010 = INTOSC with CLKO as primary; port function on RA7; EC oscillator with CLKO function                                                                 |

|         | 001 = INTOSC as primary with port function on RA6/RA7; HS oscillator with software controlled                                                             |

|         |                                                                                                                                                           |

000 = INTOSC as primary with port function on RA6/RA7; HS oscillator (HS)

| BTFSC               |                                                             | Bit Test File                                                                      | , Skip if Clear                                                                                                             |                                                                 | BTFS    | S                                                                       | Bit Test File                                                                  | , Skip if Set                                                                                                                         |                                                         |

|---------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|---------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Syntax:             |                                                             | BTFSC f, b                                                                         | {,a}                                                                                                                        |                                                                 | Synta   | IX:                                                                     | BTFSS f, b {                                                                   | ,a}                                                                                                                                   |                                                         |

| Operands:           |                                                             | $\begin{array}{l} 0 \leq f \leq 255 \\ 0 \leq b \leq 7 \\ a \in [0,1] \end{array}$ |                                                                                                                             |                                                                 | Opera   | ands:                                                                   | 0 ≤ f ≤ 255<br>0 ≤ b < 7<br>a ∈ [0,1]                                          |                                                                                                                                       |                                                         |

| Operation:          |                                                             | skip if (f <b>)</b>                                                                | = 0                                                                                                                         |                                                                 | Opera   | ation:                                                                  | skip if (f <b>)</b>                                                            | = 1                                                                                                                                   |                                                         |

| Status Affect       | cted:                                                       | None                                                                               |                                                                                                                             |                                                                 | Statu   | s Affected:                                                             | None                                                                           |                                                                                                                                       |                                                         |

| Encoding:           |                                                             | 1011                                                                               | bbba ff                                                                                                                     | ff ffff                                                         | Enco    | ding:                                                                   | 1010                                                                           | bbba ffi                                                                                                                              | f ffff                                                  |

| Description         | :                                                           | instruction is<br>the next instruction<br>current instruction<br>and a NOP is      | gister 'f' is '0', t<br>skipped. If bit<br>ruction fetched<br>uction executio<br>executed instruction.                      | 'b' is '0', then<br>during the<br>n is discarded<br>ead, making | Desc    | ription:                                                                | instruction is<br>the next instruction<br>current instruction<br>and a NOP is  | gister 'f' is '1', t<br>skipped. If bit<br>ruction fetched<br>uction execution<br>executed inste<br>cle instruction.                  | 'b' is '1', then<br>during the<br>n is discarded        |

|                     |                                                             |                                                                                    | e Access Banł<br>BSR is used to                                                                                             | is selected. If select the                                      |         |                                                                         |                                                                                | e Access Bank<br>BSR is used to                                                                                                       |                                                         |

|                     |                                                             | is enabled, ti<br>Indexed Liter<br>whenever f ≤<br>Section 24.2<br>Bit-Oriented    | d the extended<br>nis instruction<br>ral Offset Addr<br>95 (5Fh). See<br>2.3 "Byte-Orie<br>I Instructions<br>et Mode" for d | essing mode<br>nted and<br>in Indexed                           |         |                                                                         | set is enable<br>Indexed Liter<br>whenever f ≤<br>Section 24.2<br>Bit-Oriented | d the extended<br>d, this instruction<br>ral Offset Addro<br>S 95 (5Fh). See<br>2.3 "Byte-Orient<br>I Instructions<br>of Mode" for de | on operates in<br>essing mode<br>nted and<br>in Indexed |

| Words:              |                                                             | 1                                                                                  |                                                                                                                             |                                                                 | Word    | s:                                                                      | 1                                                                              |                                                                                                                                       |                                                         |

| Cycles:             |                                                             | •                                                                                  | cles if skip and<br>2-word instruc                                                                                          |                                                                 | Cycle   | s:                                                                      |                                                                                | /cles if skip and<br>a 2-word instru                                                                                                  |                                                         |

| Q Cycle Ad          | ctivity:                                                    |                                                                                    |                                                                                                                             |                                                                 | QC      | cle Activity:                                                           |                                                                                |                                                                                                                                       |                                                         |

| (                   | Q1                                                          | Q2                                                                                 | Q3                                                                                                                          | Q4                                                              |         | Q1                                                                      | Q2                                                                             | Q3                                                                                                                                    | Q4                                                      |

| Dee                 | code                                                        | Read                                                                               | Process                                                                                                                     | No                                                              |         | Decode                                                                  | Read                                                                           | Process                                                                                                                               | No                                                      |

| lf skip:            |                                                             | register 'f'                                                                       | Data                                                                                                                        | operation                                                       | lf ski  | n.                                                                      | register 'f'                                                                   | Data                                                                                                                                  | operation                                               |

|                     | Q1                                                          | Q2                                                                                 | Q3                                                                                                                          | Q4                                                              | 11 5 11 | ρ.<br>Q1                                                                | Q2                                                                             | Q3                                                                                                                                    | Q4                                                      |

|                     | No                                                          | No                                                                                 | No                                                                                                                          | No                                                              |         | No                                                                      | No                                                                             | No                                                                                                                                    | No                                                      |

| oper                | ration                                                      | operation                                                                          | operation                                                                                                                   | operation                                                       |         | operation                                                               | operation                                                                      | operation                                                                                                                             | operation                                               |

| •                   |                                                             | by 2-word inst                                                                     |                                                                                                                             | _                                                               | lf ski  | •                                                                       | by 2-word inst                                                                 |                                                                                                                                       |                                                         |

|                     | Q1                                                          | Q2                                                                                 | Q3                                                                                                                          | Q4                                                              | l       | Q1                                                                      | Q2                                                                             | Q3                                                                                                                                    | Q4                                                      |

|                     | No<br>ration                                                | No<br>operation                                                                    | No<br>operation                                                                                                             | No<br>operation                                                 |         | No<br>operation                                                         | No<br>operation                                                                | No<br>operation                                                                                                                       | No<br>operation                                         |

|                     | No                                                          | No                                                                                 | No                                                                                                                          | No                                                              |         | No                                                                      | No                                                                             | No                                                                                                                                    | No                                                      |

|                     | ration                                                      | operation                                                                          | operation                                                                                                                   | operation                                                       |         | operation                                                               | operation                                                                      | operation                                                                                                                             | operation                                               |

| Example:            |                                                             | HERE BI<br>FALSE :<br>TRUE :                                                       | FSC FLAG                                                                                                                    | , l, O                                                          | Exam    | iple:                                                                   | HERE BI<br>FALSE :<br>TRUE :                                                   | TFSS FLAG                                                                                                                             | , 1, 0                                                  |

| P<br>After Iı<br>If | e Instructi<br>PC<br>nstruction<br>FLAG<1<br>PC<br>f FLAG<1 | = add<br>n<br>1> = 0;<br>= add                                                     | ress (HERE)<br>ress (TRUE)                                                                                                  |                                                                 |         | Before Instruct<br>PC<br>After Instructio<br>If FLAG<<br>PC<br>If FLAG< | = add<br>n<br>1> = 0;<br>= add                                                 | ress (HERE)<br>ress (False)                                                                                                           |                                                         |

|                     | PC                                                          |                                                                                    | ress (False                                                                                                                 | )                                                               |         | PC                                                                      | · · · · ·                                                                      | ress (TRUE)                                                                                                                           |                                                         |

| CAL         | LW                                    | Subroutine                                                                                              | Subroutine Call Using WREG                                                                                                                                                                                                                                                                                                                                |                 |  |  |  |  |

|-------------|---------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Synta       | ax:                                   | CALLW                                                                                                   |                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| Oper        | ands:                                 | None                                                                                                    |                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| Oper        | ation:                                | (W) → PCL<br>(PCLATH) -                                                                                 | $(PC + 2) \rightarrow TOS,$<br>$(W) \rightarrow PCL,$<br>$(PCLATH) \rightarrow PCH,$<br>$(PCLATU) \rightarrow PCU$                                                                                                                                                                                                                                        |                 |  |  |  |  |

| Statu       | is Affected:                          | None                                                                                                    |                                                                                                                                                                                                                                                                                                                                                           |                 |  |  |  |  |

| Enco        | oding:                                | 0000                                                                                                    | 0000 000                                                                                                                                                                                                                                                                                                                                                  | 01 0100         |  |  |  |  |

| Desc        | ription                               | pushed ont<br>contents of<br>existing val<br>contents of<br>latched into<br>respectively<br>executed as | First, the return address (PC + 2) is<br>pushed onto the return stack. Next, the<br>contents of W are written to PCL; the<br>existing value is discarded. Then, the<br>contents of PCLATH and PCLATU are<br>latched into PCH and PCU,<br>respectively. The second cycle is<br>executed as a NOP instruction while the<br>new next instruction is fetched. |                 |  |  |  |  |

|             |                                       |                                                                                                         | Unlike CALL, there is no option to update W, STATUS or BSR.                                                                                                                                                                                                                                                                                               |                 |  |  |  |  |