Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 40MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                           |

| Peripherals                | Brown-out Detect/Reset, LCD, LVD, POR, PWM, WDT                             |

| Number of I/O              | 67                                                                          |

| Program Memory Size        | 16KB (8K x 16)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                   |

| Data Converters            | A/D 12x10b                                                                  |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 80-TQFP                                                                     |

| Supplier Device Package    | 80-TQFP (12x12)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18f84j90t-i-pt |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | Device Overview                                                              | 9     |  |  |  |  |

|-------|------------------------------------------------------------------------------|-------|--|--|--|--|

| 2.0   | Guidelines for Getting Started with PIC18FJ Microcontrollers                 | 31    |  |  |  |  |

| 3.0   | Oscillator Configurations                                                    | 35    |  |  |  |  |

| 4.0   | Power-Managed Modes                                                          | 43    |  |  |  |  |

| 5.0   | Reset                                                                        | 51    |  |  |  |  |

| 6.0   | Memory Organization                                                          | 63    |  |  |  |  |

| 7.0   | Flash Program Memory                                                         | 87    |  |  |  |  |

| 8.0   | 8 x 8 Hardware Multiplier                                                    | 97    |  |  |  |  |

| 9.0   | Interrupts                                                                   | 99    |  |  |  |  |

| 10.0  | I/O Ports                                                                    | . 115 |  |  |  |  |

| 11.0  | Timer0 Module                                                                | . 137 |  |  |  |  |

| 12.0  | Timer1 Module                                                                | . 141 |  |  |  |  |

| 13.0  | Timer2 Module                                                                | . 147 |  |  |  |  |

| 14.0  | Timer3 Module                                                                | . 149 |  |  |  |  |

| 15.0  | Capture/Compare/PWM (CCP) Modules                                            | . 153 |  |  |  |  |

| 16.0  | Liquid Crystal Display (LCD) Driver Module                                   | . 163 |  |  |  |  |

| 17.0  | Master Synchronous Serial Port (MSSP) Module                                 |       |  |  |  |  |

| 18.0  | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART)    | . 235 |  |  |  |  |

|       | Addressable Universal Synchronous Asynchronous Receiver Transmitter (AUSART) |       |  |  |  |  |

| 20.0  | 10-bit Analog-to-Digital Converter (A/D) Module                              | . 271 |  |  |  |  |

| 21.0  | Comparator Module                                                            |       |  |  |  |  |

| 22.0  | Comparator Voltage Reference Module                                          | . 287 |  |  |  |  |

| 23.0  | Special Features of the CPU                                                  | . 291 |  |  |  |  |

| 24.0  | Instruction Set Summary                                                      |       |  |  |  |  |

| 25.0  | Development Support                                                          | . 355 |  |  |  |  |

|       | Electrical Characteristics                                                   |       |  |  |  |  |

|       | Packaging Information                                                        |       |  |  |  |  |

|       | ndix A: Revision History                                                     |       |  |  |  |  |

| Appe  | ndix B: Migration Between High-End Device Families                           | . 400 |  |  |  |  |

| Index | · ·····                                                                      | . 403 |  |  |  |  |

|       | Aicrochip Web Site                                                           |       |  |  |  |  |

|       | ustomer Change Notification Service4                                         |       |  |  |  |  |

|       | omer Support                                                                 |       |  |  |  |  |

|       | er Response                                                                  |       |  |  |  |  |

| Produ | roduct Identification System                                                 |       |  |  |  |  |

## 1.0 DEVICE OVERVIEW

This document contains device-specific information for the following devices:

- PIC18F63J90 PIC18F83J90

- PIC18F64J90

- PIC18F84J90

- PIC18F65J90 PIC18F85J90

This family combines the traditional advantages of all PIC18 microcontrollers – namely, high computational performance and a rich feature set – with a versatile on-chip LCD driver, while maintaining an extremely competitive price point. These features make the PIC18F85J90 family a logical choice for many high-performance applications where price is a primary consideration.

## 1.1 Core Features

### 1.1.1 nanoWatt TECHNOLOGY

All of the devices in the PIC18F85J90 family incorporate a range of features that can significantly reduce power consumption during operation. Key items include:

- Alternate Run Modes: By clocking the controller from the Timer1 source or the internal RC oscillator, power consumption during code execution can be reduced by as much as 90%.

- Multiple Idle Modes: The controller can also run with its CPU core disabled but the peripherals still active. In these states, power consumption can be reduced even further, to as little as 4% of normal operation requirements.

- **On-the-Fly Mode Switching:** The power-managed modes are invoked by user code during operation, allowing the user to incorporate power-saving ideas into their application's software design.

## 1.1.2 OSCILLATOR OPTIONS AND FEATURES

All of the devices in the PIC18F85J90 family offer six different oscillator options, allowing users a range of choices in developing application hardware. These include:

- Two Crystal modes, using crystals or ceramic resonators.

- Two External Clock modes, offering the option of a divide-by-4 clock output.

- A Phase Lock Loop (PLL) frequency multiplier, available to the External Oscillator modes which allows clock speeds of up to 40 MHz.

- An internal oscillator block which provides an 8 MHz clock (±2% accuracy) and an INTRC source (approximately 31 kHz, stable over temperature and VDD), as well as a range of six user-selectable clock frequencies, between 125 kHz to 4 MHz, for a total of eight clock frequencies. This option frees the two oscillator pins for use as additional general purpose I/O.

The internal oscillator block provides a stable reference source that gives the family additional features for robust operation:

- Fail-Safe Clock Monitor: This option constantly monitors the main clock source against a reference signal provided by the internal oscillator. If a clock failure occurs, the controller is switched to the internal oscillator, allowing for continued low-speed operation or a safe application shutdown.

- **Two-Speed Start-up:** This option allows the internal oscillator to serve as the clock source from Power-on Reset, or wake-up from Sleep mode, until the primary clock source is available.

## 1.1.3 MEMORY OPTIONS

The PIC18F85J90 family provides a range of program memory options, from 8 Kbytes to 32 Kbytes of code space. The Flash cells for program memory are rated to last up to 1000 erase/write cycles. Data retention without refresh is conservatively estimated to be greater than 20 years.

The PIC18F85J90 family also provides plenty of room for dynamic application data, with up to 2048 bytes of data RAM.

## 1.1.4 EXTENDED INSTRUCTION SET

The PIC18F85J90 family implements the optional extension to the PIC18 instruction set, adding 8 new instructions and an Indexed Addressing mode. Enabled as a device configuration option, the extension has been specifically designed to optimize re-entrant application code originally developed in high-level languages, such as 'C'.

### 1.1.5 EASY MIGRATION

Regardless of the memory size, all devices share the same rich set of peripherals, allowing for a smooth migration path as applications grow and evolve.

The consistent pinout scheme used throughout the entire family also aids in migrating to the next larger device. This is true when moving between the 64-pin members, between the 80-pin members, or even jumping from 64-pin to 80-pin devices.

The PIC18F85J90 family is also largely pin compatible with other PIC18 families, such as the PIC18F8720 and PIC18F8722, as well as the PIC18F8490 family of microcontrollers with LCD drivers. This allows a new dimension to the evolution of applications, allowing developers to select different price points within Microchip's PIC18 portfolio, while maintaining a similar feature set.

| Pin Name                  | Pin Number     | Pin<br>Type | Buffer       | Description                                                                                                                          |  |  |

|---------------------------|----------------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Fill Name                 | TQFP           |             | Туре         | Description                                                                                                                          |  |  |

|                           |                |             |              | PORTJ is a bidirectional I/O port.                                                                                                   |  |  |

| RJ0                       | 62             | I/O         | ST           | Digital I/O.                                                                                                                         |  |  |

| RJ1/SEG33<br>RJ1<br>SEG33 | 61             | I/O<br>O    | ST<br>Analog | Digital I/O.<br>SEG33 output for LCD.                                                                                                |  |  |

| RJ2/SEG34<br>RJ2<br>SEG34 | 60             | I/O<br>O    | ST<br>Analog | Digital I/O.<br>SEG34 output for LCD.                                                                                                |  |  |

| RJ3/SEG35<br>RJ3<br>SEG35 | 59             | I/O<br>O    | ST<br>Analog | Digital I/O.<br>SEG35 output for LCD.                                                                                                |  |  |

| RJ4/SEG39<br>RJ4<br>SEG39 | 39             | I/O<br>O    | ST<br>Analog | Digital I/O.<br>SEG39 output for LCD.                                                                                                |  |  |

| RJ5/SEG38<br>RJ5<br>SEG38 | 40             | I/O<br>O    | ST<br>Analog | Digital I/O<br>SEG38 output for LCD.                                                                                                 |  |  |

| RJ6/SEG37<br>RJ6<br>SEG37 | 41             | I/O<br>O    | ST<br>Analog | Digital I/O.<br>SEG37 output for LCD.                                                                                                |  |  |

| RJ7/SEG36<br>RJ7<br>SEG36 | 42             | I/O<br>O    | ST<br>Analog | Digital I/O.<br>SEG36 output for LCD.                                                                                                |  |  |

| Vss                       | 11, 31, 51, 70 | Р           |              | Ground reference for logic and I/O pins.                                                                                             |  |  |

| Vdd                       | 32, 48, 71     | Ρ           |              | Positive supply for logic and I/O pins.                                                                                              |  |  |

| AVss                      | 26             | Р           |              | Ground reference for analog modules.                                                                                                 |  |  |

| AVdd                      | 25             | Р           | —            | Positive supply for analog modules.                                                                                                  |  |  |

| ENVREG                    | 24             | Ι           | ST           | Enable for on-chip voltage regulator.                                                                                                |  |  |

| Vddcore/Vcap<br>Vddcore   | 12             | Ρ           | _            | Core logic power or external filter capacitor connection.<br>Positive supply for microcontroller core logic<br>(regulator disabled). |  |  |

| VCAP                      |                | Р           |              | External filter capacitor connection (regulator enabled)                                                                             |  |  |

|                           | r              | with C      | MOS leve     | CMOS = CMOS compatible input or output<br>Analog = Analog input<br>O = Output<br>OD = Open-Drain (no P diode to VDD)                 |  |  |

| TABLE 1-4: | PIC18F8XJ90 PINOUT I/O DESCRIPTIONS ( | CONTINUED) | ) |

|------------|---------------------------------------|------------|---|

|            |                                       |            |   |

**Note 1:** Default assignment for CCP2 when the CCP2MX Configuration bit is set.

2: Alternate assignment for CCP2 when the CCP2MX Configuration bit is cleared.

NOTES:

## 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device, with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits, including microcontrollers, to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

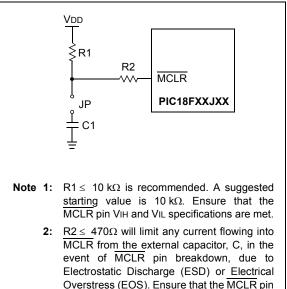

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: Device Reset, and Device Programming and Debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented, depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the MCLR pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

VIH and VIL specifications are met.

A CM Reset behaves similarly to a Master Clear Reset, RESET instruction, WDT time-out or Stack Event Resets. As with all hard and power Reset events, the device Configuration Words are reloaded from the Flash Configuration Words in program memory as the device restarts.

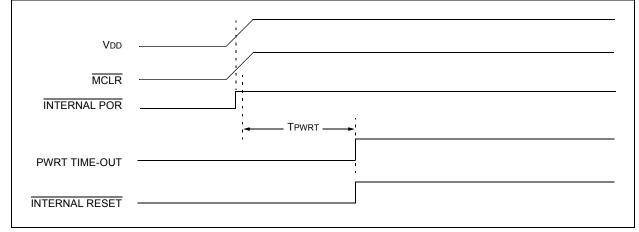

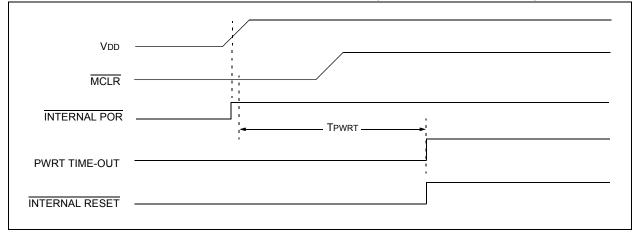

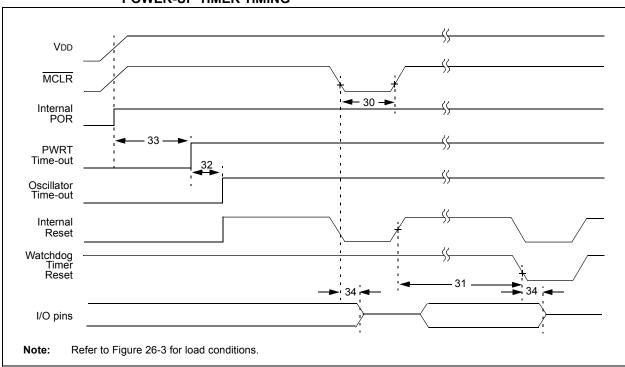

## 5.6 Power-up Timer (PWRT)

PIC18F85J90 family devices incorporate an on-chip Power-up Timer (PWRT) to help regulate the Power-on Reset process. The PWRT is always enabled. The main function is to ensure that the device voltage is stable before code is executed.

The Power-up Timer (PWRT) of the PIC18F85J90 family devices is an 11-bit counter which uses the INTRC source as the clock input. This yields an approximate time interval of 2048 x 32  $\mu$ s = 65.6 ms. While the PWRT is counting, the device is held in Reset. The power-up time delay depends on the INTRC clock and will vary from chip-to-chip due to temperature and process variation. See DC parameter 33 for details.

## 5.6.1 TIME-OUT SEQUENCE

If enabled, the PWRT time-out is invoked after the POR pulse has cleared. The total time-out will vary based on the status of the PWRT. Figure 5-3, Figure 5-4, Figure 5-5 and Figure 5-6 all depict time-out sequences on power-up with the Power-up Timer enabled.

Since the time-outs occur from the POR pulse, if MCLR is kept low long enough, the PWRT will expire. Bringing MCLR high will begin execution immediately (Figure 5-5). This is useful for testing purposes, or to synchronize more than one PIC18FXXXX device operating in parallel.

### FIGURE 5-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR NOT TIED TO VDD): CASE 1

## 6.3 Data Memory Organization

| Note: | The operation of some aspects of data    |

|-------|------------------------------------------|

|       | memory are changed when the PIC18        |

|       | extended instruction set is enabled. See |

|       | Section 6.6 "Data Memory and the         |

|       | Extended Instruction Set" for more       |

|       | information.                             |

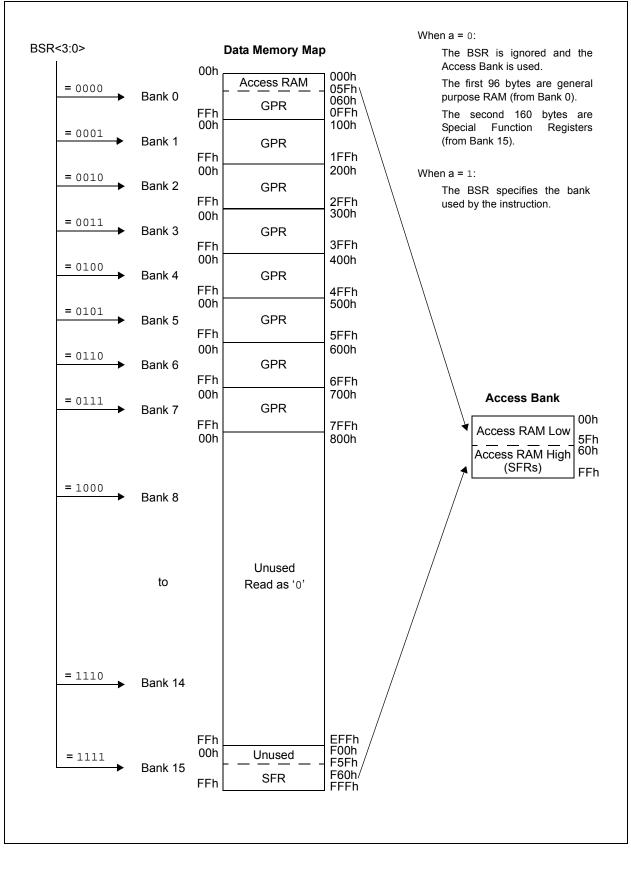

The data memory in PIC18 devices is implemented as static RAM. Each register in the data memory has a 12-bit address, allowing up to 4096 bytes of data memory. The memory space is divided into as many as 16 banks that contain 256 bytes each. The PIC18FX3J90/X4J90 devices, with up to 16 Kbytes of program memory, implement 4 complete banks for a total of 1024 bytes. PIC18FX5J90 devices, with 32 Kbytes of program memory, implement 8 complete banks for a total of 2048 bytes. Figure 6-6 and Figure 6-7 show the data memory organization for the devices.

The data memory contains Special Function Registers (SFRs) and General Purpose Registers (GPRs). The SFRs are used for control and status of the controller and peripheral functions, while GPRs are used for data storage and scratchpad operations in the user's application. Any read of an unimplemented location will read as '0's.

The instruction set and architecture allow operations across all banks. The entire data memory may be accessed by Direct, Indirect or Indexed Addressing modes. Addressing modes are discussed later in this section.

To ensure that commonly used registers (select SFRs and select GPRs) can be accessed in a single cycle, PIC18 devices implement an Access Bank. This is a 256-byte memory space that provides fast access to select SFRs and the lower portion of GPR Bank 0 without using the BSR. **Section 6.3.2 "Access Bank"** provides a detailed description of the Access RAM.

### 6.3.1 BANK SELECT REGISTER

Large areas of data memory require an efficient addressing scheme to make rapid access to any address possible. Ideally, this means that an entire address does not need to be provided for each read or write operation. For PIC18 devices, this is accomplished with a RAM banking scheme. This divides the memory space into 16 contiguous banks of 256 bytes. Depending on the instruction, each location can be addressed directly by its full 12-bit address, or an 8-bit low-order address and a 4-bit Bank Pointer.

Most instructions in the PIC18 instruction set make use of the Bank Pointer, known as the Bank Select Register (BSR). This SFR holds the 4 Most Significant bits (MSbs) of a location's address; the instruction itself includes the 8 Least Significant bits (LSbs). Only the four lower bits of the BSR are implemented (BSR<3:0>). The upper four bits are unused; they will always read '0' and cannot be written to. The BSR can be loaded directly by using the MOVLB instruction.

The value of the BSR indicates the bank in data memory. The 8 bits in the instruction show the location in the bank and can be thought of as an offset from the bank's lower boundary. The relationship between the BSR's value and the bank division in data memory is shown in Figure 6-8.

Since up to 16 registers may share the same low-order address, the user must always be careful to ensure that the proper bank is selected before performing a data read or write. For example, writing what should be program data to an 8-bit address of F9h while the BSR is 0Fh, will end up resetting the program counter.

While any bank can be selected, only those banks that are actually implemented can be read or written to. Writes to unimplemented banks are ignored, while reads from unimplemented banks will return '0's. Even so, the STATUS register will still be affected as if the operation was successful. The data memory map in Figure 6-6 indicates which banks are implemented.

In the core PIC18 instruction set, only the MOVFF instruction fully specifies the 12-bit address of the source and target registers. This instruction ignores the BSR completely when it executes. All other instructions include only the low-order address as an operand and must use either the BSR or the Access Bank to locate their target registers.

## FIGURE 6-7: DATA MEMORY MAP FOR PIC18FX5J90 DEVICES

## 7.2.2 TABLE LATCH REGISTER (TABLAT)

The Table Latch (TABLAT) is an 8-bit register mapped into the SFR space. The Table Latch register is used to hold 8-bit data during data transfers between program memory and data RAM.

#### 7.2.3 TABLE POINTER REGISTER (TBLPTR)

The Table Pointer (TBLPTR) register addresses a byte within the program memory. The TBLPTR is comprised of three SFR registers: Table Pointer Upper Byte, Table Pointer High Byte and Table Pointer Low Byte (TBLPTRU:TBLPTRH:TBLPTRL). These three registers join to form a 22-bit wide pointer. The low-order 21 bits allow the device to address up to 2 Mbytes of program memory space. The 22nd bit allows access to the device ID, the user ID and the Configuration bits.

The Table Pointer register, TBLPTR, is used by the TBLRD and TBLWT instructions. These instructions can update the TBLPTR in one of four ways based on the table operation. These operations are shown in Table 7-1. These operations on the TBLPTR only affect the low-order 21 bits.

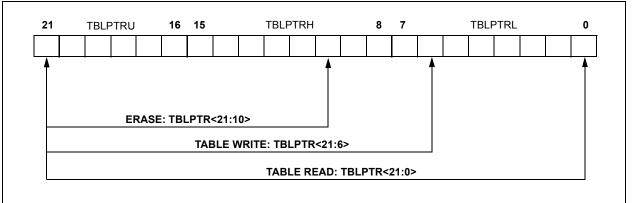

## 7.2.4 TABLE POINTER BOUNDARIES

TBLPTR is used in reads, writes and erases of the Flash program memory.

When a TBLRD is executed, all 22 bits of the TBLPTR determine which byte is read from program memory into TABLAT.

When a TBLWT is executed, the seven LSbs of the Table Pointer register (TBLPTR<6:0>) determine which of the 64 program memory holding registers is written to. When the timed write to program memory begins (via the WR bit), the 12 MSbs of the TBLPTR (TBLPTR<21:10>) determine which program memory block of 1024 bytes is written to. For more detail, see **Section 7.5 "Writing to Flash Program Memory"**.

When an erase of program memory is executed, the 12 MSbs of the Table Pointer register point to the 1024-byte block that will be erased. The Least Significant bits are ignored.

Figure 7-3 describes the relevant boundaries of the TBLPTR based on Flash program memory operations.

#### TABLE 7-1: TABLE POINTER OPERATIONS WITH TBLRD AND TBLWT INSTRUCTIONS

| Example            | Operation on Table Pointer                  |  |  |  |  |  |  |

|--------------------|---------------------------------------------|--|--|--|--|--|--|

| TBLRD*<br>TBLWT*   | TBLPTR is not modified                      |  |  |  |  |  |  |

| TBLRD*+<br>TBLWT*+ | TBLPTR is incremented after the read/write  |  |  |  |  |  |  |

| TBLRD*-<br>TBLWT*- | TBLPTR is decremented after the read/write  |  |  |  |  |  |  |

| TBLRD+*<br>TBLWT+* | TBLPTR is incremented before the read/write |  |  |  |  |  |  |

#### FIGURE 7-3: TABLE POINTER BOUNDARIES BASED ON OPERATION

## 7.4 Erasing Flash Program Memory

The minimum erase block is 512 words or 1024 bytes. Only through the use of an external programmer, or through ICSP control, can larger blocks of program memory be Bulk Erased. Word erase in the Flash array is not supported.

When initiating an erase sequence from the microcontroller itself, a block of 1024 bytes of program memory is erased. The Most Significant 12 bits of the TBLPTR<21:10> point to the block being erased; TBLPTR<9:0> are ignored.

The EECON1 register commands the erase operation. The WREN bit must be set to enable write operations. The FREE bit is set to select an erase operation. For protection, the write initiate sequence for EECON2 must be used.

A long write is necessary for erasing the internal Flash. Instruction execution is halted while in a long write cycle. The long write will be terminated by the internal programming timer.

### 7.4.1 FLASH PROGRAM MEMORY ERASE SEQUENCE

The sequence of events for erasing a block of internal program memory location is:

- 1. Load the Table Pointer register with the address of the block being erased.

- 2. Set the WREN and FREE bits (EECON1<2,4>) to enable the erase operation.

- 3. Disable interrupts.

- 4. Write 55h to EECON2.

- 5. Write 0AAh to EECON2.

- 6. Set the WR bit; this will begin the erase cycle.

- The CPU will stall for the duration of the erase for TIE (see parameter D133B).

- 8. Re-enable interrupts.

### EXAMPLE 7-2: ERASING A FLASH PROGRAM MEMORY BLOCK

|             | MOVLW<br>MOVWF<br>MOVLW<br>MOVWF<br>MOVLW<br>MOVWF | CODE_ADDR_UPPER<br>TBLPTRU<br>CODE_ADDR_HIGH<br>TBLPTRH<br>CODE_ADDR_LOW<br>TBLPTRL |   | load TBLPTR with the base<br>address of the memory block |

|-------------|----------------------------------------------------|-------------------------------------------------------------------------------------|---|----------------------------------------------------------|

| ERASE_BLOCK |                                                    |                                                                                     |   |                                                          |

|             | BSF                                                | EECON1, WREN                                                                        | ; | enable write to memory                                   |

|             | BSF                                                | EECON1, FREE                                                                        | ; | enable Erase operation                                   |

|             | BCF                                                | INTCON, GIE                                                                         | ; | disable interrupts                                       |

| Required    | MOVLW                                              | 55h                                                                                 |   |                                                          |

| Sequence    | MOVWF                                              | EECON2                                                                              | ; | write 55h                                                |

|             | MOVLW                                              | 0AAh                                                                                |   |                                                          |

|             | MOVWF                                              | EECON2                                                                              | ; | write OAAh                                               |

|             | BSF                                                | EECON1, WR                                                                          | ; | start erase (CPU stall)                                  |

|             | BSF                                                | INTCON, GIE                                                                         | ; | re-enable interrupts                                     |

## 12.0 TIMER1 MODULE

The Timer1 timer/counter module incorporates these features:

- Software selectable operation as a 16-bit timer or counter

- Readable and writable 8-bit registers (TMR1H and TMR1L)

- Selectable clock source (internal or external) with device clock or Timer1 oscillator internal options

- Interrupt on overflow

- Reset on CCP Special Event Trigger

- Device clock status flag (T1RUN)

A simplified block diagram of the Timer1 module is shown in Figure 12-1. A block diagram of the module's operation in Read/Write mode is shown in Figure 12-2.

The module incorporates its own low-power oscillator to provide an additional clocking option. The Timer1 oscillator can also be used as a low-power clock source for the microcontroller in power-managed operation.

Timer1 can also be used to provide Real-Time Clock (RTC) functionality to applications with only a minimal addition of external components and code overhead.

Timer1 is controlled through the T1CON Control register (Register 12-1). It also contains the Timer1 Oscillator Enable bit (T1OSCEN). Timer1 can be enabled or disabled by setting or clearing control bit, TMR1ON (T1CON<0>).

| R/W-0 | R-0   | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-------|-------|---------|---------|---------|--------|--------|--------|

| RD16  | T1RUN | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7 |       |         |         |         |        |        | bit 0  |

### REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| Legend:    |                      |                                                                    |                                   |                    |  |  |  |  |

|------------|----------------------|--------------------------------------------------------------------|-----------------------------------|--------------------|--|--|--|--|

| R = Reada  | ble bit              | W = Writable bit                                                   | U = Unimplemented bit             | , read as '0'      |  |  |  |  |

| -n = Value | at POR               | '1' = Bit is set                                                   | '0' = Bit is cleared              | x = Bit is unknown |  |  |  |  |

| bit 7      | <b>RD16:</b> 16      | B-Bit Read/Write Mode Enab                                         | le bit                            |                    |  |  |  |  |

|            |                      | bles register read/write of TIr<br>bles register read/write of Tir | •                                 |                    |  |  |  |  |

| bit 6      | T1RUN:               | Timer1 System Clock Status                                         | bit                               |                    |  |  |  |  |

|            |                      | ce clock is derived from Time ce clock is derived from ano         |                                   |                    |  |  |  |  |

| bit 5-4    | T1CKPS               | <1:0>: Timer1 Input Clock P                                        | rescale Select bits               |                    |  |  |  |  |

|            | ==•                  | Prescale value                                                     |                                   |                    |  |  |  |  |

|            |                      | = 1:4 Prescale value                                               |                                   |                    |  |  |  |  |

|            |                      | Prescale value<br>Prescale value                                   |                                   |                    |  |  |  |  |

| bit 3      |                      | N: Timer1 Oscillator Enable                                        | bit                               |                    |  |  |  |  |

|            | 1 = Time             | r1 oscillator is enabled                                           |                                   |                    |  |  |  |  |

|            |                      | r1 oscillator is shut off                                          |                                   |                    |  |  |  |  |

|            |                      |                                                                    | esistor are turned off to elimina | ate power drain.   |  |  |  |  |

| bit 2      |                      | : Timer1 External Clock Inpu                                       | t Synchronization Select bit      |                    |  |  |  |  |

|            |                      | <u>IR1CS = 1:</u><br>ot synchronize external clock                 | cinnut                            |                    |  |  |  |  |

|            |                      | hronize external clock input                                       | ( input                           |                    |  |  |  |  |

|            | When TM              | IR1CS = 0:                                                         |                                   |                    |  |  |  |  |

|            | This bit is          | ignored. Timer1 uses the in                                        | ternal clock when TMR1CS =        | 0.                 |  |  |  |  |

| bit 1      | TMR1CS               | : Timer1 Clock Source Select                                       | ct bit                            |                    |  |  |  |  |

|            |                      | rnal clock from pin RC0/T1C<br>nal clock (Fosc/4)                  | SO/T13CKI (on the rising edge     | e)                 |  |  |  |  |

| bit 0      | TMR10N               | I: Timer1 On bit                                                   |                                   |                    |  |  |  |  |

|            | 1 = Enat<br>0 = Stop | bles Timer1<br>s Timer1                                            |                                   |                    |  |  |  |  |

## 16.1 LCD Registers

The LCD driver module has 33 registers:

- LCD Control Register (LCDCON)

- LCD Phase Register (LCDPS)

- LCD Regulator Control Register (LCDREG)

- Six LCD Segment Enable Registers (LCDSE5:LCDSE0)

- 24 LCD Data Registers (LCDDATA23:LCDDATA0)

#### 16.1.1 LCD CONTROL REGISTERS

The LCDCON register, shown in Register 16-1, controls the overall operation of the module. Once the module is configured, the LCDEN (LCDCON<7>) bit is used to enable or disable the LCD module. The LCD panel can also operate during Sleep by clearing the SLPEN (LCDCON<6>) bit.

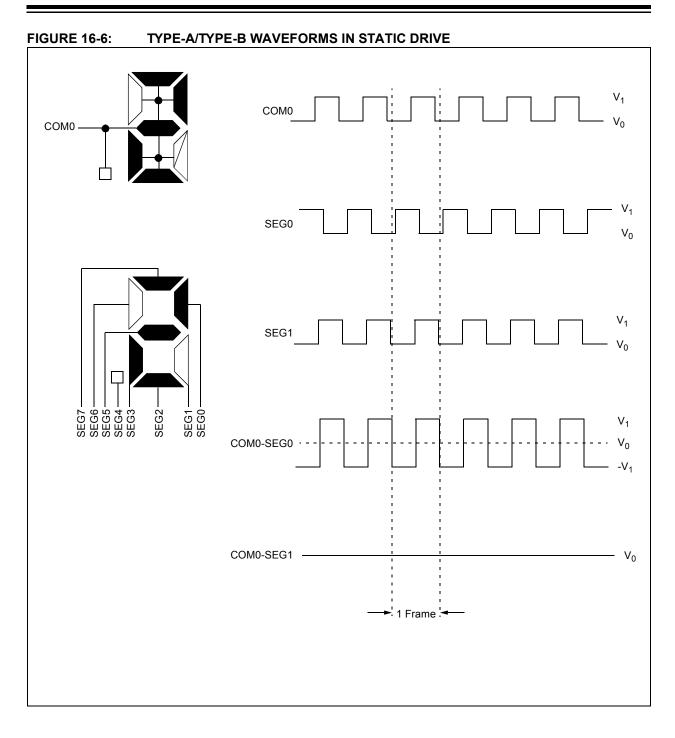

The LCDPS register, shown in Register 16-2, configures the LCD clock source prescaler and the type of waveform: Type-A or Type-B. Details on these features are provided in Section 16.2 "LCD Clock Source", Section 16.3 "LCD Bias Generation" and Section 16.8 "LCD Waveform Generation".

The LCDREG register is described in Section 16.3 "LCD Bias Generation".

The LCD Segment Enable registers (LCDSEx) configure the functions of the port pins. Setting the segment enable bit for a particular segment configures that pin as an LCD driver. The prototype LCDSE register is shown in Register 16-3. There are six LCDSE registers (LCDSE5:LCDSE0) listed in Table 16-1.

## REGISTER 16-1: LCDCON: LCD CONTROL REGISTER

| R/W-0        | R/W-0         | R/C-0              | U-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

|--------------|---------------|--------------------|----------------|-------------------|------------------|-----------------|-------|

| LCDEN        | SLPEN         | WERR               | —              | CS1               | CS0              | LMUX1           | LMUX0 |

| bit 7        | •             |                    |                |                   |                  |                 | bit 0 |

|              |               |                    |                |                   |                  |                 |       |

| Legend:      |               | C = Clearable      | bit            |                   |                  |                 |       |

| R = Readab   | ole bit       | W = Writable       | oit            | U = Unimplem      | nented bit, read | d as '0'        |       |

| -n = Value a | it POR        | '1' = Bit is set   |                | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

|              |               |                    |                |                   |                  |                 |       |

| bit 7        | LCDEN: LCD    | Driver Enable      | bit            |                   |                  |                 |       |

|              |               | er module is en    |                |                   |                  |                 |       |

|              | 0 = LCD drive | er module is dis   | abled          |                   |                  |                 |       |

| bit 6        | SLPEN: LCD    | Driver Enable      | in Sleep mode  | bit               |                  |                 |       |

|              |               | er module is dis   |                |                   |                  |                 |       |

|              | 0 = LCD drive | er module is ena   | abled in Sleep | mode              |                  |                 |       |

| bit 5        |               | Write Failed Er    |                |                   |                  |                 |       |

|              |               | Ax register writte | en while LCDP  | S<4> = 0 (mus     | t be cleared in  | software)       |       |

|              | 0 = No LCD v  |                    |                |                   |                  |                 |       |

| bit 4        | Unimplemen    | ted: Read as '0    | )'             |                   |                  |                 |       |

| bit 3-2      |               | ock Source Sele    | ect bits       |                   |                  |                 |       |

|              | 1x = INTRC (  |                    |                |                   |                  |                 |       |

|              | 01 = T13CKI   | · /                |                |                   |                  |                 |       |

| h:1 0        | ,             | clock (Fosc/4)     | at bita        |                   |                  |                 |       |

| bit 1-0      | LMUX<1:0>:    | Commons Sele       |                |                   |                  | 1               |       |

|              |               |                    | м              | aximum Numb       | er of Pixels:    |                 |       |

|        | LMUX<1:0> | Multiplex Type  | Maximum Nur | nber of Pixels: | Rise Type  |  |

|--------|-----------|-----------------|-------------|-----------------|------------|--|

| LIVIUX | 1:0>      | PIC18F6XJ       |             | PIC18F8XJ90     | Bias Type  |  |

| 00     |           | Static (COM0)   | 33          | 48              | Static     |  |

| 01     |           | 1/2 (COM1:COM0) | 66          | 96              | 1/2 or 1/3 |  |

| 10     |           | 1/3 (COM2:COM0) | 99          | 144             | 1/2 or 1/3 |  |

| 11     |           | 1/4 (COM3:COM0) | 132         | 192             | 1/3        |  |

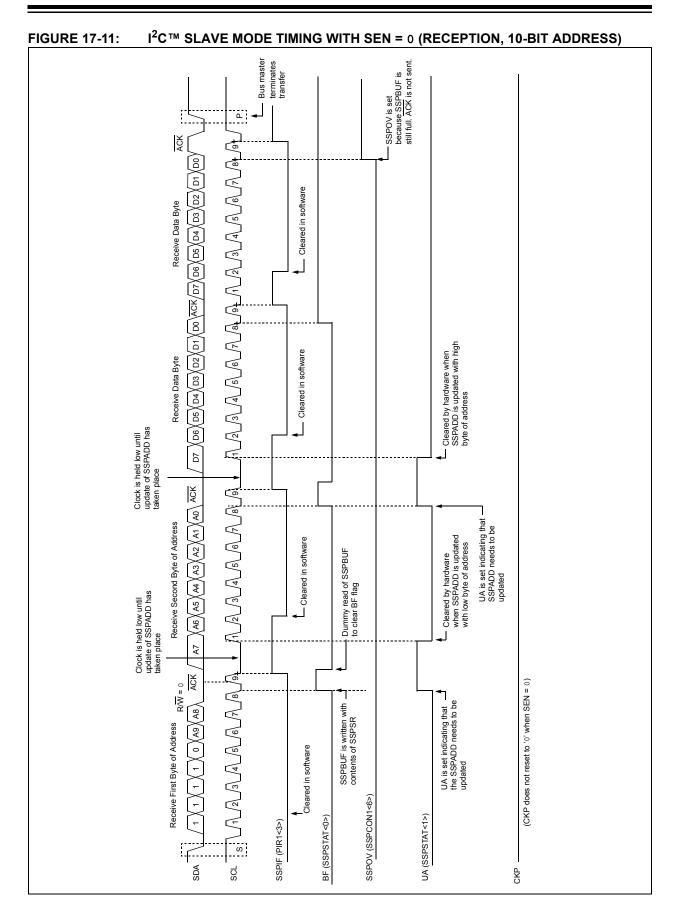

## 17.4.6.1 I<sup>2</sup>C Master Mode Operation

The master device generates all of the serial clock pulses and the Start and Stop conditions. A transfer is ended with a Stop condition or with a Repeated Start condition. Since the Repeated Start condition is also the beginning of the next serial transfer, the I<sup>2</sup>C bus will not be released.

In Master Transmitter mode, serial data is output through SDA, while SCL outputs the serial clock. The first byte transmitted contains the slave address of the receiving device (7 bits) and the Read/Write (R/W) bit. In this case, the R/W bit will be logic '0'. Serial data is transmitted 8 bits at a time. After each byte is transmitted, an Acknowledge bit is received. Start and Stop conditions are output to indicate the beginning and the end of a serial transfer.

In Master Receive mode, the first byte transmitted contains the slave address of the transmitting device (7 bits) and the  $R/\overline{W}$  bit. In this case, the  $R/\overline{W}$  bit will be logic '1'. Thus, the first byte transmitted is a 7-bit slave address followed by a '1' to indicate the receive bit. Serial data is received via SDA, while SCL outputs the serial clock. Serial data is received 8 bits at a time. After each byte is received, an Acknowledge bit is transmitted. Start and Stop conditions indicate the beginning and end of transmission.

The Baud Rate Generator used for the SPI mode operation is used to set the SCL clock frequency for either 100 kHz, 400 kHz or 1 MHz  $I^2$ C operation. See **Section 17.4.7 "Baud Rate"** for more details.

A typical transmit sequence would go as follows:

- 1. The user generates a Start condition by setting the Start Enable bit, SEN (SSPCON2<0>).

- 2. SSPIF is set. The MSSP module will wait the required start time before any other operation takes place.

- 3. The user loads the SSPBUF with the slave address to transmit.

- 4. The address is shifted out of the SDA pin until all 8 bits are transmitted.

- 5. The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 6. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 7. The user loads the SSPBUF with eight bits of data.

- 8. Data is shifted out of the SDA pin until all 8 bits are transmitted.

- The MSSP module shifts in the ACK bit from the slave device and writes its value into the SSPCON2 register (SSPCON2<6>).

- 10. The MSSP module generates an interrupt at the end of the ninth clock cycle by setting the SSPIF bit.

- 11. The user generates a Stop condition by setting the Stop Enable bit, PEN (SSPCON2<2>).

- 12. The interrupt is generated once the Stop condition is complete.

ADD W to f

## 24.1.1 STANDARD INSTRUCTION SET

| ADDLW                                    | ADD Litera             | al to W                         | ADDWF      |      |                                                    |

|------------------------------------------|------------------------|---------------------------------|------------|------|----------------------------------------------------|

| Syntax:                                  | ADDLW                  | k                               |            |      | Syntax:                                            |

| Operands:                                | $0 \le k \le 255$      |                                 | Operands:  |      |                                                    |

| Operation:                               | $(W) + k \rightarrow $ | W                               |            |      |                                                    |

| Status Affected:                         | N, OV, C, E            | DC, Z                           | Operation: |      |                                                    |

| Encoding:                                | 0000                   | 1111 k                          | kkk ł      | kkkk | Status Affected:                                   |

| Description:                             |                        | ts of W are a<br>'k' and the re |            |      | Encoding:<br>Description:                          |

| Words:                                   | 1                      |                                 |            |      |                                                    |

| Cycles:                                  | 1                      |                                 |            |      |                                                    |

| Q Cycle Activity:                        |                        |                                 |            |      |                                                    |

| Q1                                       | Q2                     | Q3                              | Q          | 24   |                                                    |

| Decode                                   | Read<br>literal 'k'    | Process<br>Data                 | Write<br>W |      |                                                    |

| <u>Example:</u><br>Before Instruc<br>W = |                        | 15h                             |            |      |                                                    |

| After Instruction                        |                        |                                 |            |      | Words:                                             |

| W =                                      | 25h                    |                                 |            |      | Cycles:                                            |

|                                          |                        |                                 |            |      | Q Cycle Activit                                    |

|                                          |                        |                                 |            |      | Q1                                                 |

|                                          |                        |                                 |            |      | Decode                                             |

|                                          |                        |                                 |            |      | Example:                                           |

|                                          |                        |                                 |            |      | Before Ins<br>W<br>REG<br>After Instru<br>W<br>REG |

| Syntax:                                                         | ADDWF                                                                              | f {,d {,a}]                                                                                                                | }                                               |                                 |  |

|-----------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------------|--|

| Operands:                                                       | $\begin{array}{l} 0 \leq f \leq 255 \\ d  \in  [0,1] \\ a  \in  [0,1] \end{array}$ |                                                                                                                            |                                                 |                                 |  |

| Operation:                                                      | $(W) + (f) \rightarrow$                                                            | dest                                                                                                                       |                                                 |                                 |  |

| Status Affected:                                                | N, OV, C, D                                                                        | )C, Z                                                                                                                      |                                                 |                                 |  |

| Encoding:                                                       | 0010                                                                               | 01da                                                                                                                       | fff                                             | f ffff                          |  |

| Description:                                                    | result is sto                                                                      | Add W to register 'f'. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'. |                                                 |                                 |  |

|                                                                 | ,                                                                                  |                                                                                                                            |                                                 | k is selected.<br>to select the |  |

|                                                                 |                                                                                    | ed, this in<br>Literal Of<br>never f ≤ 9<br>.2.3 "Byt                                                                      | nstructi<br>fset Ad<br>95 (5Ff<br><b>e-Orie</b> | h). See<br>ented and            |  |

|                                                                 | Literal Offs                                                                       |                                                                                                                            |                                                 |                                 |  |

| Words:                                                          |                                                                                    |                                                                                                                            |                                                 |                                 |  |

| Words:<br>Cycles:                                               | Literal Offs                                                                       |                                                                                                                            |                                                 |                                 |  |

|                                                                 | Literal Offs                                                                       |                                                                                                                            |                                                 |                                 |  |

| Cycles:                                                         | Literal Offs                                                                       |                                                                                                                            |                                                 |                                 |  |

| Cycles:<br>Q Cycle Activity:                                    | Literal Offs<br>1<br>1                                                             | set Mode                                                                                                                   | " for d                                         | etails.                         |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode<br><u>Example:</u> | Literal Offs<br>1<br>1<br>Q2<br>Read<br>register 'f'<br>ADDWF                      | Q3<br>Proces                                                                                                               | ss                                              | Q4<br>Write to                  |  |

| Cycles:<br>Q Cycle Activity:<br>Q1<br>Decode                    | Literal Offs 1 1 2 Q2 Read register 'f' ADDWF tion = 17h = 0C2h                    | Q3<br>Proce:<br>Data                                                                                                       | ss                                              | Q4<br>Write to                  |  |

**Note:** All PIC18 instructions may take an optional label argument preceding the instruction mnemonic for use in symbolic addressing. If a label is used, the instruction format then becomes: {label} instruction argument(s).

| BCF                                                                                                                                                                                                                                         | Bit Clear f                                                               | BN                                                             | Branch if N                                                                                               | legative            |                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|------------------------|

| Syntax:                                                                                                                                                                                                                                     | BCF f, b {,a}                                                             | Syntax:                                                        | BN n                                                                                                      |                     |                        |

| Operands:                                                                                                                                                                                                                                   | $0 \leq f \leq 255$                                                       | Operands:                                                      | $-128 \le n \le 127$                                                                                      |                     |                        |

|                                                                                                                                                                                                                                             | 0 ≤ b ≤ 7<br>a ∈ [0,1]                                                    | Operation:                                                     | if Negative<br>(PC) + 2 + 2                                                                               |                     |                        |

| Operation:                                                                                                                                                                                                                                  | $0 \rightarrow f \le b >$                                                 | Status Affected:                                               | None                                                                                                      |                     |                        |

| Status Affected:                                                                                                                                                                                                                            | None                                                                      | Encoding:                                                      | 1110                                                                                                      | 0110 nn             | nn nnnn                |

| Encoding:                                                                                                                                                                                                                                   | 1001 bbba ffff ffff                                                       | Description:                                                   | -                                                                                                         | tive bit is '1', th |                        |

| Description:                                                                                                                                                                                                                                | Bit 'b' in register 'f' is cleared.                                       | 2000                                                           | program wi                                                                                                |                     |                        |

| If 'a' is '0', the Access Bank is selected.<br>If 'a' is '1', the BSR is used to select the<br>GPR bank.<br>If 'a' is '0' and the extended instruction<br>set is enabled, this instruction operates<br>in Indexed Literal Offset Addressing |                                                                           |                                                                | added to the incremente                                                                                   | d to fetch the      | e PC will have<br>next |

|                                                                                                                                                                                                                                             |                                                                           |                                                                | instruction, the new address will be<br>PC + 2 + 2n. This instruction is then a<br>two-cycle instruction. |                     |                        |

|                                                                                                                                                                                                                                             | mode whenever f $\leq$ 95 (5Fh). See                                      | Words:                                                         | 1                                                                                                         |                     |                        |

|                                                                                                                                                                                                                                             | Section 24.2.3 "Byte-Oriented and<br>Bit-Oriented Instructions in Indexed | Cycles:                                                        | 1(2)                                                                                                      |                     |                        |

|                                                                                                                                                                                                                                             | Literal Offset Mode" for details.                                         | Q Cycle Activity:                                              |                                                                                                           |                     |                        |

| Words:                                                                                                                                                                                                                                      | 1                                                                         | If Jump:                                                       |                                                                                                           |                     |                        |

| Cycles:                                                                                                                                                                                                                                     | 1                                                                         | Q1                                                             | Q2                                                                                                        | Q3                  | Q4                     |

| Q Cycle Activity:                                                                                                                                                                                                                           |                                                                           | Decode                                                         | Read literal<br>'n'                                                                                       | Process<br>Data     | Write to<br>PC         |

| Q1                                                                                                                                                                                                                                          | Q2 Q3 Q4                                                                  | No                                                             | No                                                                                                        | No                  | No                     |

| Decode                                                                                                                                                                                                                                      | Read Process Write                                                        | operation                                                      | operation                                                                                                 | operation           | operation              |

|                                                                                                                                                                                                                                             | register 'f' Data register 'f'                                            | If No Jump:                                                    |                                                                                                           |                     |                        |

|                                                                                                                                                                                                                                             |                                                                           | Q1                                                             | Q2                                                                                                        | Q3                  | Q4                     |

| Example:                                                                                                                                                                                                                                    | BCF FLAG_REG, 7, 0                                                        | Decode                                                         | Read literal<br>'n'                                                                                       | Process<br>Data     | No<br>operation        |

| Before Instruc                                                                                                                                                                                                                              |                                                                           |                                                                |                                                                                                           | Data                | operation              |

| After Instructio                                                                                                                                                                                                                            | EG = C7h<br>on                                                            | Example:                                                       | HERE                                                                                                      | BN Jump             |                        |

| FLAG_REG = 47h                                                                                                                                                                                                                              |                                                                           | Before Instruction<br>PC = address (HERE)<br>After Instruction |                                                                                                           |                     |                        |

|                                                                                                                                                                                                                                             |                                                                           |                                                                |                                                                                                           |                     |                        |

|                                                                                                                                                                                                                                             |                                                                           | If Negati                                                      | ve = 0;                                                                                                   | . 1                 |                        |

|                                                                                                                                                                                                                                             |                                                                           | PC                                                             | = ad                                                                                                      | dress (HERE         | + 2)                   |

| TBLWT                                                            | Table Wri                                                                                                                                                                                                                                                                                                                                                                          | te                        |                       |                       |  |

|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------------------|-----------------------|--|

| Syntax:                                                          | TBLWT ( *                                                                                                                                                                                                                                                                                                                                                                          | <sup>;</sup> ; *+; *-; +* | *)                    |                       |  |

| Operands:                                                        | None                                                                                                                                                                                                                                                                                                                                                                               |                           |                       |                       |  |

| Operation:                                                       | if TBLWT*,<br>(TABLAT) $\rightarrow$ Holding Register;<br>TBLPTR – No Change<br>if TBLWT*+,<br>(TABLAT) $\rightarrow$ Holding Register;<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR<br>if TBLWT*-,<br>(TABLAT) $\rightarrow$ Holding Register;<br>(TBLPTR) – 1 $\rightarrow$ TBLPTR<br>if TBLWT+*,<br>(TBLPTR) + 1 $\rightarrow$ TBLPTR;                                                  |                           |                       |                       |  |

|                                                                  | (TABLAT)                                                                                                                                                                                                                                                                                                                                                                           | $\rightarrow$ Holding     | g Register            |                       |  |

| Status Affected:                                                 | None                                                                                                                                                                                                                                                                                                                                                                               | r                         | 1                     |                       |  |

| Encoding:                                                        | 0000                                                                                                                                                                                                                                                                                                                                                                               | 0000                      | 0000                  | 11nn                  |  |

|                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    |                           |                       | nn=0 *<br>=1 *+       |  |

|                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    |                           |                       | =2 *-                 |  |

|                                                                  |                                                                                                                                                                                                                                                                                                                                                                                    |                           |                       | =3 +*                 |  |