Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\sim$

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 13                                                                             |

| Program Memory Size        | 12KB (12K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x12b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 18-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp201-e-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

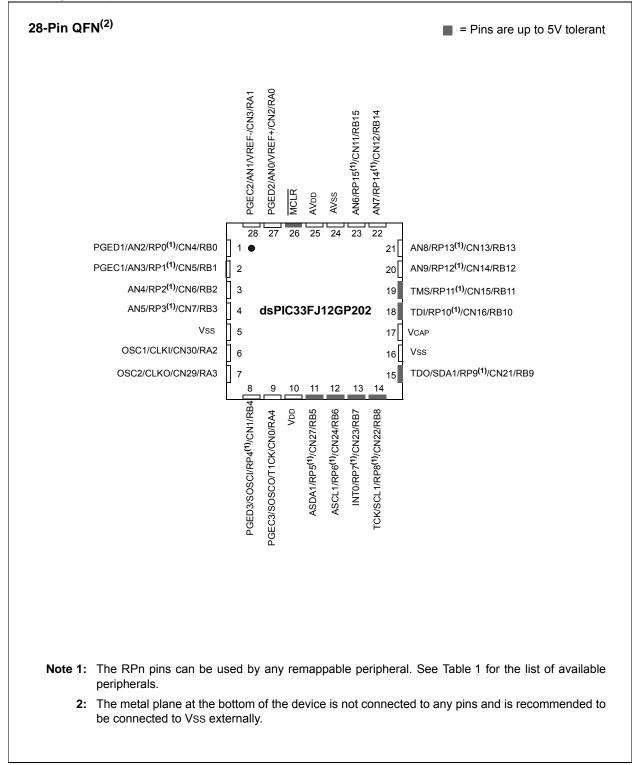

### dsPIC33FJ12GP201/202 Product Families

The device names, pin counts, memory sizes, and peripheral availability of each family are listed below, followed by their pinout diagrams.

|                  |      | ory                             |                |                    | Ren              | nappa         | ble Per                    | ipher | als                                |     |                   |                    |                |                              |

|------------------|------|---------------------------------|----------------|--------------------|------------------|---------------|----------------------------|-------|------------------------------------|-----|-------------------|--------------------|----------------|------------------------------|

| Device           | Pins | Program Flash Memory<br>(Kbyte) | RAM<br>(Kbyte) | Remappable<br>Pins | 16-bit Timer     | Input Capture | Output Compare<br>Std. PWM | UART  | External Interrupts <sup>(2)</sup> | IdS | 10-Bit/12-Bit ADC | I <sup>2</sup> Стм | I/O Pins (Max) | Packages                     |

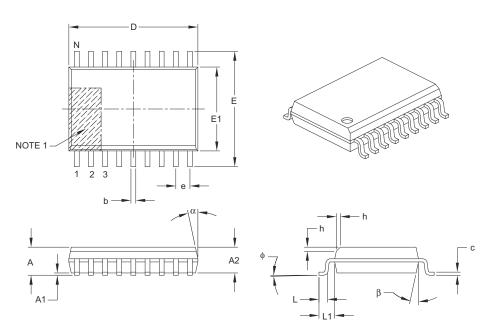

| dsPIC33FJ12GP201 | 18   | 12                              | 1              | 8                  | 3 <sup>(1)</sup> | 4             | 2                          | 1     | 3                                  | 1   | 1 ADC,<br>6 ch    | 1                  | 13             | PDIP<br>SOIC                 |

| dsPIC33FJ12GP202 | 28   | 12                              | 1              | 16                 | 3 <sup>(1)</sup> | 4             | 2                          | 1     | 3                                  | 1   | 1 ADC,<br>10 ch   | 1                  | 21             | SPDIP<br>SOIC<br>SSOP<br>QFN |

# TABLE 1: dsPIC33FJ12GP201/202 CONTROLLER FAMILIES

Note 1: Only two out of three timers are remappable.

**2:** Only two out of three interrupts are remappable.

### **Pin Diagrams (Continued)**

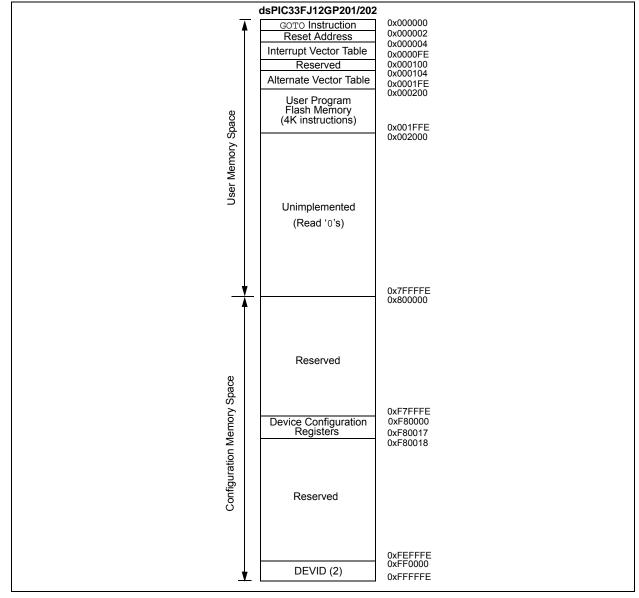

# 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Program Memory" (DS70202) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

The dsPIC33FJ12GP201/202 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 Program Address Space

The program address memory space of the dsPIC33FJ12GP201/202 devices is 4M instructions. The space is addressable by a 24-bit value derived either from the 23-bit PC during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

User application access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

The memory map for the dsPIC33FJ12GP201/202 family of devices is shown in Figure 4-1.

FIGURE 4-1: PROGRAM MEMORY FOR dsPIC33FJ12GP201/202 DEVICES

| TABLE 4-1: | <b>CPU CORE REGISTERS MAP</b> |

|------------|-------------------------------|

|------------|-------------------------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                          | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7         | Bit 6  | Bit 5     | Bit 4          | Bit 3        | Bit 2       | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|---------------------------------|--------|--------|--------|--------|---------|---------------|---------------|--------|-----------|----------------|--------------|-------------|---------|-------|---------------|

| WREG0    | 0000        |        | Working Register 0              |        |        |        |        |         |               |               |        | 0000      |                |              |             |         |       |               |

| WREG1    | 0002        |        | Working Register 1              |        |        |        |        |         |               |               |        | 0000      |                |              |             |         |       |               |

| WREG2    | 0004        |        | Working Register 2              |        |        |        |        |         |               |               |        | 0000      |                |              |             |         |       |               |

| WREG3    | 0006        |        |                                 |        |        |        |        |         | Working Re    | gister 3      |        |           |                |              |             |         |       | 0000          |

| WREG4    | 0008        |        | Working Register 4              |        |        |        |        |         |               |               |        |           | 0000           |              |             |         |       |               |

| WREG5    | 000A        |        |                                 |        |        |        |        |         |               |               |        | 0000      |                |              |             |         |       |               |

| WREG6    | 000C        |        |                                 |        |        |        |        |         | Working Re    | gister 6      |        |           |                |              |             |         |       | 0000          |

| WREG7    | 000E        |        |                                 |        |        |        |        |         | Working Re    | gister 7      |        |           |                |              |             |         |       | 0000          |

| WREG8    | 0010        |        |                                 |        |        |        |        |         | Working Re    | gister 8      |        |           |                |              |             |         |       | 0000          |

| WREG9    | 0012        |        |                                 |        |        |        |        |         | Working Re    | gister 9      |        |           |                |              |             |         |       | 0000          |

| WREG10   | 0014        |        |                                 |        |        |        |        |         | Working Re    | gister 10     |        |           |                |              |             |         |       | 0000          |

| WREG11   | 0016        |        |                                 |        |        |        |        |         | Working Re    | gister 11     |        |           |                |              |             |         |       | 0000          |

| WREG12   | 0018        |        |                                 |        |        |        |        |         | Working Re    | gister 12     |        |           |                |              |             |         |       | 0000          |

| WREG13   | 001A        |        | Working Register 13             |        |        |        |        |         |               |               | 0000   |           |                |              |             |         |       |               |

| WREG14   | 001C        |        | Working Register 14             |        |        |        |        |         |               |               | 0000   |           |                |              |             |         |       |               |

| WREG15   | 001E        |        | Working Register 15             |        |        |        |        |         |               |               | 0800   |           |                |              |             |         |       |               |

| SPLIM    | 0020        |        | Stack Pointer Limit Register    |        |        |        |        |         |               |               | xxxx   |           |                |              |             |         |       |               |

| ACCAL    | 0022        |        | Accumulator A Low Word Register |        |        |        |        |         |               |               | 0000   |           |                |              |             |         |       |               |

| ACCAH    | 0024        |        |                                 |        |        |        |        | Accum   | ulator A High | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCAU    | 0026        |        |                                 |        |        |        |        | Accumu  | lator A Uppe  | er Word Reg   | jister |           |                |              |             |         |       | 0000          |

| ACCBL    | 0028        |        |                                 |        |        |        |        | Accum   | ulator B Low  | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCBH    | 002A        |        |                                 |        |        |        |        | Accum   | ulator B High | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCBU    | 002C        |        |                                 |        |        |        |        | Accumu  | lator B Uppe  | er Word Reg   | jister |           |                |              |             |         |       | 0000          |

| PCL      | 002E        |        |                                 |        |        |        |        | Program | Counter Lo    | w Word Reg    | gister |           |                |              |             |         |       | 0000          |

| PCH      | 0030        | —      | _                               | —      | _      | _      | _      | _       | _             |               |        | Progra    | m Counter      | High Byte R  | legister    |         |       | 0000          |

| TBLPAG   | 0032        | —      | —                               | _      | —      | _      | —      | _       | —             |               |        | Table F   | Page Addre     | ss Pointer R | Register    |         |       | 0000          |

| PSVPAG   | 0034        | _      | _                               | _      | _      | _      | _      | -       | _             |               | Progra | am Memory | v Visibility P | age Address  | s Pointer R | egister |       | 0000          |

| RCOUNT   | 0036        |        |                                 |        |        |        |        | Repe    | at Loop Cou   | inter Registe | er     |           |                |              |             |         |       | xxxx          |

| DCOUNT   | 0038        |        |                                 |        |        |        |        |         | DCOUNT        | <15:0>        |        |           |                |              |             |         |       | xxxx          |

| DOSTARTL | 003A        |        |                                 |        |        |        |        | DOS     | TARTL<15:     | 1>            |        |           |                |              |             |         | 0     | xxxx          |

| DOSTARTH | 003C        | _      | _                               | _      | _      | _      | _      | _       | _             | —             | _      |           |                | DOSTAF       | RTH<5:0>    |         |       | 00xx          |

| DOENDL   | 003E        |        |                                 |        |        |        |        | DOE     | NDL<15:1      | >             |        |           |                |              |             |         | 0     | xxxx          |

| DOENDH   | 0040        | _      | —                               | _      | —      | —      | —      | _       | _             | _             | —      |           |                | DOE          | NDH         |         |       | 00xx          |

| SR       | 0042        | OA     | OB                              | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2          | IPL1   | IPL0      | RA             | N            | OV          | Z       | С     | 0000          |

| CORCON   | 0044        | _      | —                               | _      | US     | EDT    |        | DL<2:0> |               | SATA          | SATB   | SATDW     | ACCSAT         | IPL3         | PSV         | RND     | IF    | 0020          |

| MODCON   | 0046        | XMODEN | YMODEN                          | _      | _      |        | BWN    | /<3:0>  |               |               | YWM    | <3:0>     |                |              | XWN         | 1<3:0>  |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Addressing Mode                                           | Description                                                                                            |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                                      | The address of the file register is specified explicitly.                                              |

| Register Direct                                           | The contents of a register are accessed directly.                                                      |

| Register Indirect                                         | The contents of Wn forms the Effective Address (EA.)                                                   |

| Register Indirect Post-Modified                           | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified                            | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset (Register Indexed) | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset                     | The sum of Wn and a literal forms the EA.                                                              |

### TABLE 4-22: FUNDAMENTAL ADDRESSING MODES SUPPORTED

# 4.3.3 MOVE AND ACCUMULATOR INSTRUCTIONS

Move instructions and the DSP accumulator class of instructions provide a greater degree of addressing flexibility than other instructions. In addition to the addressing modes supported by most MCU instructions, move and accumulator instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared by both source and destination (but typically only used by one).

In summary, the following addressing modes are supported by move and accumulator instructions:

- Register Direct

- Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

### 4.3.4 MAC INSTRUCTIONS

The dual source operand DSP instructions (CLR, ED, EDAC, MAC, MPY, MPY.N, MOVSAC, and MSC), also referred to as MAC instructions, use a simplified set of addressing modes to allow the user application to effectively manipulate the data pointers through register indirect tables.

The two-source operand prefetch registers must be members of the set {W8, W9, W10, W11}. For data reads, W8 and W9 are always directed to the X RAGU, and W10 and W11 are always directed to the Y AGU. The effective addresses generated (before and after modification) must, therefore, be valid addresses within X data space for W8 and W9 and Y data space for W10 and W11.

| Note: | Register                                 | Indirect | with | Register | Offset |  |  |  |  |

|-------|------------------------------------------|----------|------|----------|--------|--|--|--|--|

|       | Addressing mode is available only for W9 |          |      |          |        |  |  |  |  |

|       | (in X space) and W11 (in Y space).       |          |      |          |        |  |  |  |  |

In summary, the following addressing modes are supported by the  ${\tt MAC}$  class of instructions:

- Register Indirect

- Register Indirect Post-Modified by 2

- · Register Indirect Post-Modified by 4

- · Register Indirect Post-Modified by 6

- Register Indirect with Register Offset (Indexed)

#### 4.3.5 OTHER INSTRUCTIONS

In addition to the addressing modes outlined previously, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, such as ADD Acc, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the EA calculation associated with any W register.

Address boundaries check for addresses equal to:

- The upper boundary addresses for incrementing buffers

- The lower boundary addresses for decrementing buffers

It is important to realize that the address boundaries also check for addresses less than or greater than these addresses. Address changes can, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected effective address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the effective address. When an address offset (such as [W7+W2]) is used, Modulo Address correction is performed, but the contents of the register remain unchanged.

# 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which can be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

# 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled in any of these situations:

- BWM bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing)

- The BREN bit is set in the XBREV register

- The addressing mode used is Register Indirect with Pre-Increment or Post-Increment

If the length of a bit-reversed buffer is  $M = 2^{N}$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point,' which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | word-sized data (LSB of every EA is       |  |  |  |  |  |  |  |

|       | always clear). The XB value is scaled     |  |  |  |  |  |  |  |

|       | accordingly to generate compatible (byte) |  |  |  |  |  |  |  |

|       | addresses.                                |  |  |  |  |  |  |  |

When enabled, Bit-Reversed Addressing is executed only for Register Indirect with Pre-Increment or Post-Increment Addressing, and word-sized data writes. It will not function for any other addressing mode or for byte-sized data, and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB), and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word-sized data is a requirement, the LSb of the EA is ignored (and always clear).

Note: Modulo Addressing and Bit-Reversed Addressing should not be enabled together. If an application attempts to do so, Bit-Reversed Addressing will assume priority when active for the X WAGU, and X WAGU Modulo Addressing will be disabled. However, Modulo Addressing will continue to function in the X RAGU.

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

# **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-up Reset has occurred

- 0 = A Power-up Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

| U-0           | U-0                                          | R/W-0                            | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W-0         |  |  |  |

|---------------|----------------------------------------------|----------------------------------|-----------------|------------------|-----------------|-----------------|---------------|--|--|--|

| —             | _                                            | AD1IF                            | U1TXIF          | U1RXIF           | SPI1IF          | SPI1EIF         | T3IF          |  |  |  |

| bit 15        |                                              |                                  |                 |                  |                 |                 | bit           |  |  |  |

| R/W-0         | R/W-0                                        | R/W-0                            | U-0             | R/W-0            | R/W-0           | R/W-0           | R/W-0         |  |  |  |

| T2IF          | OC2IF                                        | IC2IF                            | _               | T1IF             | OC1IF           | IC1IF           | <b>INT0IF</b> |  |  |  |

| bit 7         |                                              |                                  |                 |                  |                 |                 | bit           |  |  |  |

| Legend:       |                                              |                                  |                 |                  |                 |                 |               |  |  |  |

| R = Readable  | e bit                                        | W = Writable                     | bit             | U = Unimpler     | nented bit, rea | d as '0'        |               |  |  |  |

| -n = Value at | POR                                          | '1' = Bit is se                  | t               | '0' = Bit is cle | ared            | x = Bit is unkr | iown          |  |  |  |

| bit 15-14     | Unimpleme                                    | nted: Read as                    | <b>'</b> ∩'     |                  |                 |                 |               |  |  |  |

| bit 13        | -                                            | 1 Conversion (                   |                 | runt Elan Statu  | s hit           |                 |               |  |  |  |

| bit 10        | 1 = Interrupt                                | request has or<br>request has no | curred          | lupt hag otatu   | 5 51            |                 |               |  |  |  |

| bit 12        | •                                            | RT1 Transmitte                   |                 | a Status bit     |                 |                 |               |  |  |  |

|               |                                              | request has or                   |                 | 5                |                 |                 |               |  |  |  |

|               | 0 = Interrupt                                | request has no                   | ot occurred     |                  |                 |                 |               |  |  |  |

| bit 11        |                                              | RT1 Receiver                     |                 | Status bit       |                 |                 |               |  |  |  |

|               |                                              | request has or request has no    |                 |                  |                 |                 |               |  |  |  |

| bit 10        | SPI1IF: SPI1 Event Interrupt Flag Status bit |                                  |                 |                  |                 |                 |               |  |  |  |

|               |                                              | request has or                   |                 |                  |                 |                 |               |  |  |  |

| bit 9         | -                                            | request has no                   |                 | hit              |                 |                 |               |  |  |  |

| DIL 9         |                                              | I1 Fault Interru                 |                 | DIL              |                 |                 |               |  |  |  |

|               |                                              | request has no                   |                 |                  |                 |                 |               |  |  |  |

| bit 8         | T3IF: Timer3                                 | Interrupt Flag                   | Status bit      |                  |                 |                 |               |  |  |  |

|               |                                              | request has or<br>request has no |                 |                  |                 |                 |               |  |  |  |

| bit 7         | T2IF: Timer2                                 | Interrupt Flag                   | Status bit      |                  |                 |                 |               |  |  |  |

|               | 1 = Interrupt                                | request has or                   | curred          |                  |                 |                 |               |  |  |  |

|               | •                                            | request has no                   |                 |                  |                 |                 |               |  |  |  |

| bit 6         | -                                            | out Compare Cl                   |                 | upt Flag Status  | bit             |                 |               |  |  |  |

|               |                                              | request has or request has no    |                 |                  |                 |                 |               |  |  |  |

| bit 5         | -                                            | Capture Chanr                    |                 | Flag Status bit  |                 |                 |               |  |  |  |

|               | -                                            | request has or                   | •               | lug olaldo oli   |                 |                 |               |  |  |  |

|               |                                              | request has no                   |                 |                  |                 |                 |               |  |  |  |

| bit 4         | Unimpleme                                    | nted: Read as                    | '0'             |                  |                 |                 |               |  |  |  |

| bit 3         | T1IF: Timer1                                 | Interrupt Flag                   | Status bit      |                  |                 |                 |               |  |  |  |

|               |                                              | request has or request has no    |                 |                  |                 |                 |               |  |  |  |

| bit 2         | OC1IF: Outp                                  | out Compare Cl                   | nannel 1 Interr | upt Flag Status  | bit             |                 |               |  |  |  |

|               | 1 = Interrupt<br>0 = Interrupt               | request has or                   |                 |                  |                 |                 |               |  |  |  |

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0U-0U-0U-0U-0U-0bit 15U-0R/W-1R/W-0R/W-0U-0U-0-INT2IP<2:0>bit 7Legend:<br>R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>- n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknbit 15-7Unimplemented: Read as '0'<br>bit 6-4INT2IP<2:0>: External Interrupt 2 Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) <td< th=""><th></th><th></th><th></th><th></th><th></th><th></th><th></th><th></th></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |                |                     |                                                 |                  |      |                    |       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------|---------------------|-------------------------------------------------|------------------|------|--------------------|-------|--|--|--|

| U-0       R/W-1       R/W-0       R/W-0       U-0       U-0       U-0         —       INT2IP<2:0>       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       … | U-0             | U-0            | U-0                 | U-0                                             | U-0              | U-0  | U-0                | U-0   |  |  |  |

| U-0       R/W-1       R/W-0       R/W-0       U-0       U-0       U-0         —       INT2IP<2:0>       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       —       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       …       … | —               | —              | —                   | _                                               |                  | —    | —                  | —     |  |  |  |

| INT2IP<2:0>       -       -       -         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unkn         bit 15-7       Unimplemented: Read as '0'       bit 6-4       INT2IP<2:0>: External Interrupt 2 Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       •       •         •       •       •         001 = Interrupt is priority 1       000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                            | bit 15          |                |                     |                                                 |                  |      |                    | bit 8 |  |  |  |

| INT2IP<2:0>       -       -       -         bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unkn         bit 15-7       Unimplemented: Read as '0'       bit 6-4       INT2IP<2:0>: External Interrupt 2 Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)       •       •         •       •       •         001 = Interrupt is priority 1       000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                |                     |                                                 |                  |      |                    |       |  |  |  |

| bit 7         Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unkn         bit 15-7       Unimplemented: Read as '0'         bit 6-4       INT2IP<2:0>: External Interrupt 2 Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U-0             | R/W-1          | R/W-0               | R/W-0                                           | U-0              | U-0  | U-0                | U-0   |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unkn         bit 15-7       Unimplemented: Read as '0'         bit 6-4       INT2IP<2:0>: External Interrupt 2 Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | —               |                | INT2IP<2:0>         |                                                 |                  | —    | _                  | —     |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unkn         bit 15-7       Unimplemented: Read as '0'         bit 6-4       INT2IP<2:0>: External Interrupt 2 Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 7           |                |                     |                                                 |                  |      |                    | bit 0 |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unkn         bit 15-7       Unimplemented: Read as '0'         bit 6-4       INT2IP<2:0>: External Interrupt 2 Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |                |                     |                                                 |                  |      |                    |       |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unkn         bit 15-7       Unimplemented: Read as '0'         bit 6-4       INT2IP<2:0>: External Interrupt 2 Priority bits         111 = Interrupt is priority 7 (highest priority interrupt)         •         •         001 = Interrupt is priority 1         000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Legend:         |                |                     |                                                 |                  |      |                    |       |  |  |  |

| bit 15-7 Unimplemented: Read as '0'<br>bit 6-4 INT2IP<2:0>: External Interrupt 2 Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | R = Readable    | e bit          | W = Writable        | Vritable bit U = Unimplemented bit, read as '0' |                  |      |                    |       |  |  |  |

| bit 6-4 INT2IP<2:0>: External Interrupt 2 Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | -n = Value at I | POR            | '1' = Bit is set    |                                                 | '0' = Bit is cle | ared | x = Bit is unknown |       |  |  |  |

| bit 6-4 INT2IP<2:0>: External Interrupt 2 Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |                |                     |                                                 |                  |      |                    |       |  |  |  |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 15-7        | Unimplemen     | ted: Read as '      | כ'                                              |                  |      |                    |       |  |  |  |

| •<br>•<br>001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 6-4         | INT2IP<2:0>:   | External Interr     | upt 2 Priority                                  | bits             |      |                    |       |  |  |  |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | 111 = Interrup | ot is priority 7 (I | highest priorit                                 | y interrupt)     |      |                    |       |  |  |  |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | •              |                     |                                                 |                  |      |                    |       |  |  |  |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | •              |                     |                                                 |                  |      |                    |       |  |  |  |

| 000 = Interrupt source is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | •              |                     |                                                 |                  |      |                    |       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                |                     | ahlad                                           |                  |      |                    |       |  |  |  |

| bit 5-0 Onimplemented. Neau as 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | hit 3_0         | -              |                     |                                                 |                  |      |                    |       |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DIL 3-0         | omplemen       | ieu. Nedu as        | J                                               |                  |      |                    |       |  |  |  |

### REGISTER 7-17: IPC7: INTERRUPT PRIORITY CONTROL REGISTER 7

| U-0           | U-0          | R/W-0             | R/W-0   | R/W-0             | U-0  | U-0            | U-0   |

|---------------|--------------|-------------------|---------|-------------------|------|----------------|-------|

| _             | —            | T3MD              | T2MD    | T1MD              | _    |                | _     |

| bit 15        |              |                   |         |                   |      |                | bit   |

|               |              |                   |         |                   |      |                |       |

| R/W-0         | U-0          | R/W-0             | U-0     | R/W-0             | U-0  | U-0            | R/W-0 |

| I2C1MD        |              | U1MD              | —       | SPI1MD            | —    |                | AD1MD |

| bit 7         |              |                   |         |                   |      |                | bit   |

|               |              |                   |         |                   |      |                |       |

| Legend:       |              |                   |         |                   |      |                |       |

| R = Readabl   |              | W = Writable      |         | U = Unimplem      |      |                |       |

| -n = Value at | POR          | '1' = Bit is set  |         | '0' = Bit is clea | ared | x = Bit is unk | nown  |

|               |              |                   |         |                   |      |                |       |

| bit 15-14     | -            | nted: Read as '   |         |                   |      |                |       |

| bit 13        |              | r3 Module Disal   |         |                   |      |                |       |

|               |              | nodule is enable  |         |                   |      |                |       |

| bit 12        |              | r2 Module Disal   |         |                   |      |                |       |

|               | 1 = Timer2 r | module is disabl  | ed      |                   |      |                |       |

|               | 0 = Timer2 r | module is enable  | ed      |                   |      |                |       |

| bit 11        | T1MD: Time   | er1 Module Disal  | ole bit |                   |      |                |       |

|               | -            | nodule is disabl  |         |                   |      |                |       |

|               |              | nodule is enable  |         |                   |      |                |       |

| bit 10-8      | -            | nted: Read as '   |         |                   |      |                |       |

| bit 7         | -            | C1 Module Disal   |         |                   |      |                |       |

|               |              | dule is enabled   |         |                   |      |                |       |

| bit 6         | Unimpleme    | nted: Read as '   | 0'      |                   |      |                |       |

| bit 5         | -            | T1 Module Disa    |         |                   |      |                |       |

|               | 1 = UART1    | module is disabl  | ed      |                   |      |                |       |

|               | 0 = UART1    | module is enabl   | ed      |                   |      |                |       |

| bit 4         | Unimpleme    | nted: Read as '   | 0'      |                   |      |                |       |

| bit 3         |              | PI1 Module Disa   |         |                   |      |                |       |

|               |              | odule is disabled |         |                   |      |                |       |

| bit 2-1       |              | nted: Read as '   | 0'      |                   |      |                |       |

| bit 0         | -            | C1 Module Disa    |         |                   |      |                |       |

|               |              | nodule is disable |         |                   |      |                |       |

|               |              |                   |         |                   |      |                |       |

**Note 1:** PCFGx bits have no effect if the ADC module is disabled by setting this bit. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

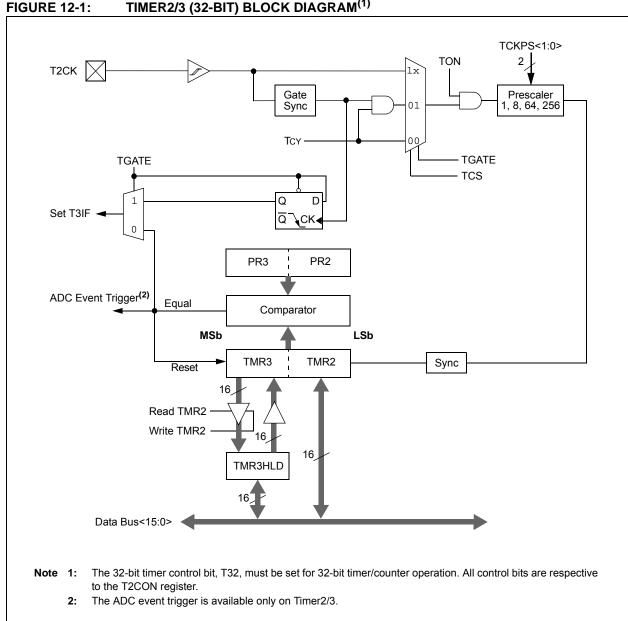

#### TIMER2/3 (32-BIT) BLOCK DIAGRAM<sup>(1)</sup> FIGURE 12-1:

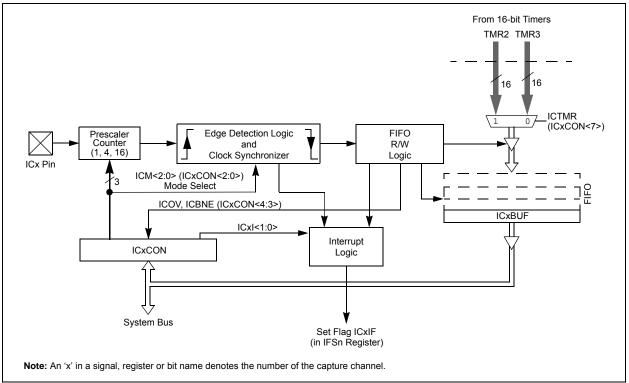

# 13.0 INPUT CAPTURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJ12GP201/202 devices support up to eight input capture channels.

The Input Capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- Simple Capture Event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Prescaler Capture Event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each Input Capture channel can select one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on Input Capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- · Use of Input Capture to provide additional

#### FIGURE 13-1: INPUT CAPTURE BLOCK DIAGRAM

# REGISTER 18-6: AD1CSSL: ADC1 INPUT SCAN SELECT REGISTER LOW<sup>(1,2)</sup>

| U-0     | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|---------|-------|-------|-------|-------|-------|-------|-------|

| —       | —     | —     | _     | _     | —     | CSS9  | CSS8  |

| bit 15  |       |       |       |       | •     |       | bit 8 |

|         |       |       |       |       |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| CSS7    | CSS6  | CSS5  | CSS4  | CSS3  | CSS2  | CSS1  | CSS0  |

| bit 7   |       |       | •     | •     | •     |       | bit 0 |

|         |       |       |       |       |       |       |       |

| Legend: |       |       |       |       |       |       |       |

| Legena.           |                            |                      |                    |

|-------------------|----------------------------|----------------------|--------------------|

| R = Readable bit  | U = Unimplemented bit, rea | ad as '0'            |                    |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CSS<9:0>: ADC Input Scan Selection bits

1 = Select ANx for input scan

0 = Skip ANx for input scan

**2:** CSSx = ANx, where x = 0 through 9.

# REGISTER 18-7: AD1PCFGL: ADC1 PORT CONFIGURATION REGISTER LOW<sup>(1,2,3)</sup>

| U-0     | U-0   | U-0   | U-0   | U-0   | U-0   | R/W-0 | R/W-0 |

|---------|-------|-------|-------|-------|-------|-------|-------|

| —       | —     | —     | _     |       | —     | PCFG9 | PCFG8 |

| bit 15  |       |       |       |       |       |       | bit 8 |

|         |       |       |       |       |       |       |       |

| R/W-0   | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

| PCFG7   | PCFG6 | PCFG5 | PCFG4 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7   |       |       |       |       |       |       | bit 0 |

|         |       |       |       |       |       |       |       |

| Legend: |       |       |       |       |       |       |       |

| Logona.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0

PCFG<9:0>: ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss 0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

#### Note 1: On devices without 10 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- **2:** PCFGx = ANx, where x = 0 through 9.

- 3: PCFGx bits have no effect if the ADC module is disabled by setting the ADxMD bit in the PMDx register. When that bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

Note 1: On devices without 10 analog inputs, all AD1CSSL bits can be selected by user application. However, inputs selected for scan without a corresponding input on device converts VREFL.

| TABLE 19-2: | USFICSSE | J12GP201/202 CONFIGURATION BITS DESCRIPTION                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit Field   | Register | RTSP<br>Effect                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |

| BWRP        | FBS      | Immediate                                                                                                       | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                               |  |

| BSS<2:0>    | FBS      | Immediate                                                                                                       | Boot Segment Program Flash Code Protection Size<br>x11 = No Boot program Flash segment                                                                                                                                                                                                                                                                                                              |  |

|             |          |                                                                                                                 | Boot space is 256 Instruction Words (except interrupt vectors)<br>110 = Standard security; boot program Flash segment ends at 0x0003FE<br>010 = High security; boot program Flash segment ends at 0x0003FE                                                                                                                                                                                          |  |

|             |          |                                                                                                                 | Boot space is 768 Instruction Words (except interrupt vectors)<br>101 = Standard security; boot program Flash segment, ends at 0x0007FE<br>001 = High security; boot program Flash segment ends at 0x0007FE                                                                                                                                                                                         |  |

|             |          |                                                                                                                 | Boot space is 1792 Instruction Words (except interrupt vectors)<br>100 = Standard security; boot program Flash segment ends at 0x000FFE<br>000 = High security; boot program Flash segment ends at 0x000FFE                                                                                                                                                                                         |  |

| GSS<1:0>    | FGS      | Immediate                                                                                                       | General Segment Code-Protect bit<br>11 = User program memory is not code-protected<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                                                                  |  |

| GWRP        | FGS      | Immediate                                                                                                       | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                   |  |

| IESO        | FOSCSEL  | Immediate                                                                                                       | <ul> <li>Two-speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start-up device with user-selected oscillator source</li> </ul>                                                                                                                                                   |  |

| FNOSC<2:0>  | FOSCSEL  | If clock<br>switch is<br>enabled,<br>RTSP<br>effect is<br>on any<br>device<br>Reset;<br>otherwise,<br>Immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) oscillator with postscaler<br>110 = Internal Fast RC (FRC) oscillator with divide-by-16<br>101 = LPRC oscillator<br>100 = Secondary (LP) oscillator<br>011 = Primary (XT, HS, EC) oscillator with PLL<br>010 = Primary (XT, HS, EC) oscillator<br>001 = Internal Fast RC (FRC) oscillator with PLL<br>000 = FRC oscillator |  |

| FCKSM<1:0>  | FOSC     | Immediate                                                                                                       | Clock Switching Mode bits<br>1x = Clock switching is disabled, fail-safe clock monitor is disabled<br>01 = Clock switching is enabled, fail-safe clock monitor is disabled<br>00 = Clock switching is enabled, fail-safe clock monitor is enabled                                                                                                                                                   |  |

| IOL1WAY     | FOSC     | Immediate                                                                                                       | Peripheral Pin Select Configuration<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                    |  |

| OSCIOFNC    | FOSC     | Immediate                                                                                                       | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is clock output<br>0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                                                                        |  |

| POSCMD<1:0> | FOSC     | Immediate                                                                                                       | Primary Oscillator Mode Select bits<br>11 = Primary oscillator disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                      |  |

#### TABLE 19-2: dsPIC33FJ12GP201/202 CONFIGURATION BITS DESCRIPTION

| Base<br>Instr<br># | Assembly<br>Mnemonic |                   | Assembly Syntax                     | Description                                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|-------------------|-------------------------------------|-------------------------------------------------------------------|---------------|----------------|--------------------------|

| 48                 | MPY                  | MPY<br>Wm*Wn,Ac   | cc,Wx,Wxd,Wy,Wyd                    | Multiply Wm by Wn to Accumulator                                  | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

|                    |                      | MPY<br>Wm*Wm,Ac   | cc,Wx,Wxd,Wy,Wyd                    | Square Wm to Accumulator                                          | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |

| 49                 | MPY.N                | MPY.N<br>Wm*Wn,Ac | cc,Wx,Wxd,Wy,Wyd                    | -(Multiply Wm by Wn) to Accumulator                               | 1             | 1              | None                     |

| 50                 | MSC                  | MSC               | Wm*Wm,Acc,Wx,Wxd,Wy,Wyd<br>,<br>AWB | Multiply and Subtract from Accumulator                            | 1             | 1              | OA,OB,OAB,<br>SA,SB,SAB  |