Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | dsPIC                                                                          |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 13                                                                             |

| Program Memory Size        | 12KB (12K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 1K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 6x12b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                   |

| Package / Case             | 18-DIP (0.300", 7.62mm)                                                        |

| Supplier Device Package    | 18-PDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp201-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **High-Performance, 16-Bit Digital Signal Controllers**

### **Operating Range:**

- Up to 40 MIPS operation (at 3.0-3.6V):

- Industrial temperature range (-40°C to +85°C)

- Extended temperature range (-40°C to +125°C)

### **High-Performance DSC CPU:**

- · Modified Harvard architecture

- · C compiler optimized instruction set

- · 16 bit wide data path

- 24 bit wide instructions

- Linear program memory addressing up to 4M instruction words

- · Linear data memory addressing up to 64 Kbytes

- · 83 base instructions, mostly one word/one cycle

- Sixteen 16-bit general purpose registers

- Two 40-bit accumulators with rounding and saturation options

- · Flexible and powerful addressing modes:

- Indirect

- Modulo

- Bit-Reversed

- Software stack

- 16 x 16 fractional/integer multiply operations

- · 32/16 and 16/16 divide operations

- · Single-cycle multiply and accumulate:

- Accumulator write back for DSP operationsDual data fetch

- · Up to ±16-bit shifts for up to 40-bit data

### **Interrupt Controller:**

- 5-cycle latency

- · Up to 21 available interrupt sources

- · Up to three external interrupts

- Seven programmable priority levels

- Four processor exceptions

### **On-Chip Flash and SRAM:**

- Flash program memory (12 Kbytes)

- Data SRAM (1024 bytes)

- Boot and General Security for Program Flash

### **Digital I/O:**

- · Peripheral Pin Select Functionality

- Up to 21 programmable digital I/O pins

- · Wake-up/interrupt-on-change for up to 21 pins

- · Output pins can drive from 3.0V to 3.6V

- Up to 5V output with open drain configurations on 5V tolerant pins

- 4 mA sink on all I/O pins

#### System Management:

- · Flexible clock options:

- External, crystal, resonator, internal RC

- Fully integrated Phase-Locked Loop (PLL)

- Extremely low-jitter PLL

- Power-up Timer

- Oscillator Start-up Timer/Stabilizer

- · Watchdog Timer with its own RC oscillator

- · Fail-Safe Clock Monitor

- · Reset by multiple sources

#### **Power Management:**

- · On-chip 2.5V voltage regulator

- · Switch between clock sources in real time

- · Idle, Sleep and Doze modes with fast wake-up

### Timers/Capture/Compare:

- · Timer/Counters, up to three 16-bit timers:

- Can pair up to make one 32-bit timer

- One timer runs as Real-Time Clock with external 32.768 kHz oscillator

- Programmable prescaler

- Input Capture (up to four channels):

- Capture on up, down, or both edges

- 16-bit capture input functions

- 4-deep FIFO on each capture

- Output Compare (up to two channels):

- Single or Dual 16-bit Compare mode

- 16-bit Glitchless PWM Mode

## REGISTER 3-1: SR: CPU STATUS REGISTER (CONTINUED)

| bit 8  |    | DC: MCU ALU Half Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |    | 1 = A carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred                                                                                                                                                                                                                                                                                                     |

|        |    | <ul> <li>0 = No carry-out from the 4th low-order bit (for byte-sized data) or 8th low-order bit (for word-sized data) of the result occurred</li> </ul>                                                                                                                                                                                                                                                                                |

| bit 7- | 5  | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                      |

|        |    | <pre>111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled<br/>110 = CPU Interrupt Priority Level is 6 (14)<br/>101 = CPU Interrupt Priority Level is 5 (13)<br/>100 = CPU Interrupt Priority Level is 4 (12)<br/>011 = CPU Interrupt Priority Level is 3 (11)<br/>010 = CPU Interrupt Priority Level is 2 (10)<br/>001 = CPU Interrupt Priority Level is 1 (9)<br/>000 = CPU Interrupt Priority Level is 0 (8)</pre> |

| bit 4  |    | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                                                                                                                                                             |

|        |    | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                                                                                                                                                                         |

| bit 3  |    | N: MCU ALU Negative bit                                                                                                                                                                                                                                                                                                                                                                                                                |

|        |    | <ul> <li>1 = Result was negative</li> <li>0 = Result was non-negative (zero or positive)</li> </ul>                                                                                                                                                                                                                                                                                                                                    |

| bit 2  |    | OV: MCU ALU Overflow bit                                                                                                                                                                                                                                                                                                                                                                                                               |

|        |    | This bit is used for signed arithmetic (2's complement). It indicates an overflow of a magnitude that causes the sign bit to change state.<br>1 = Overflow occurred for signed arithmetic (in this arithmetic operation)<br>0 = No overflow occurred                                                                                                                                                                                   |

| bit 1  |    | Z: MCU ALU Zero bit                                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |    | <ul> <li>1 = An operation that affects the Z bit has set it at some time in the past</li> <li>0 = The most recent operation that affects the Z bit has cleared it (i.e., a non-zero result)</li> </ul>                                                                                                                                                                                                                                 |

| bit 0  |    | C: MCU ALU Carry/Borrow bit                                                                                                                                                                                                                                                                                                                                                                                                            |

|        |    | <ul> <li>1 = A carry-out from the MSb of the result occurred</li> <li>0 = No carry-out from the MSb of the result occurred</li> </ul>                                                                                                                                                                                                                                                                                                  |

| Note   | 1: | This bit can be read or cleared (not set).                                                                                                                                                                                                                                                                                                                                                                                             |

|        | 2: | The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = $1$ . User interrupts are disabled when                                                                                                                                                                                                                            |

3: The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

IPL<3> = 1.

|                                                                                            |                                                                                                |                   |               |                  | 11.0   | U-0             | 11.0     |  |  |  |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------|---------------|------------------|--------|-----------------|----------|--|--|--|

| R/W-0                                                                                      | R-0                                                                                            | U-0               | U-0           | U-0              | U-0    | 0-0             | U-0      |  |  |  |

| ALTIVT                                                                                     | DISI                                                                                           | —                 |               | _                | —      | _               | <u> </u> |  |  |  |

| bit 15                                                                                     |                                                                                                |                   |               |                  |        |                 | bit 8    |  |  |  |

|                                                                                            |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

| U-0                                                                                        | U-0                                                                                            | U-0               | U-0           | U-0              | R/W-0  | R/W-0           | R/W-0    |  |  |  |

|                                                                                            | —                                                                                              | _                 |               |                  | INT2EP | INT1EP          | INT0EP   |  |  |  |

| bit 7 bit 0                                                                                |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

|                                                                                            |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

| Legend:                                                                                    |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                       |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

| -n = Value at                                                                              | POR                                                                                            | '1' = Bit is set  |               | '0' = Bit is cle | eared  | x = Bit is unkr | nown     |  |  |  |

|                                                                                            |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

| bit 15                                                                                     | ALTIVT: Enab                                                                                   | le Alternate Inf  | errupt Vector | Table bit        |        |                 |          |  |  |  |

|                                                                                            |                                                                                                | ate vector tabl   | -             |                  |        |                 |          |  |  |  |

|                                                                                            |                                                                                                | lard (default) ve |               |                  |        |                 |          |  |  |  |

| bit 14                                                                                     |                                                                                                | struction Status  |               |                  |        |                 |          |  |  |  |

|                                                                                            | 1 = DISI instruction is active<br>0 = DISI instruction is not active                           |                   |               |                  |        |                 |          |  |  |  |

| bit 13-3                                                                                   |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

|                                                                                            | -                                                                                              | ted: Read as '(   |               |                  | 4 L H  |                 |          |  |  |  |

| bit 2                                                                                      |                                                                                                | rnal Interrupt 2  | -             | Polarity Selec   | t Dit  |                 |          |  |  |  |

| <ul> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul> |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

| bit 1                                                                                      | -                                                                                              |                   |               | Polarity Selec   | t bit  |                 |          |  |  |  |

|                                                                                            | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge |                   |               |                  |        |                 |          |  |  |  |

| 0 = Interrupt on positive edge                                                             |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

| bit 0                                                                                      | INT0EP: Exte                                                                                   | rnal Interrupt 0  | Edge Detect   | Polarity Selec   | t bit  |                 |          |  |  |  |

|                                                                                            |                                                                                                | n negative edg    | •             | -                |        |                 |          |  |  |  |

|                                                                                            |                                                                                                | on positive edge  |               |                  |        |                 |          |  |  |  |

|                                                                                            |                                                                                                |                   |               |                  |        |                 |          |  |  |  |

### REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

### REGISTER 7-10: IEC4: INTERRUPT ENABLE CONTROL REGISTER 0

| U-0                                | U-0                           | U-0             | U-0                                     | U-0                                | U-0 | U-0   | U-0   |

|------------------------------------|-------------------------------|-----------------|-----------------------------------------|------------------------------------|-----|-------|-------|

| _                                  | —                             | —               | _                                       | —                                  | —   | —     |       |

| bit 15                             | bit 15                        |                 |                                         |                                    |     |       | bit 8 |

|                                    |                               |                 |                                         |                                    |     |       |       |

| U-0                                | U-0                           | U-0             | U-0                                     | U-0                                | U-0 | R/W-0 | U-0   |

| —                                  | —                             | —               | _                                       | —                                  |     | U1EIE | —     |

| bit 7                              |                               |                 |                                         |                                    |     |       | bit 0 |

|                                    |                               |                 |                                         |                                    |     |       |       |

| Legend:                            |                               |                 |                                         |                                    |     |       |       |

| R = Readable                       | bit                           | W = Writable    | bit                                     | U = Unimplemented bit, read as '0' |     |       |       |

| -n = Value at POR '1' = Bit is set |                               |                 | '0' = Bit is cleared x = Bit is unknown |                                    |     |       |       |

|                                    |                               |                 |                                         |                                    |     |       |       |

| bit 15-2                           | Unimplemen                    | ted: Read as '  | כ'                                      |                                    |     |       |       |

| bit 1                              | U1EIE: UART                   | 1 Error Interru | pt Enable bit                           |                                    |     |       |       |

|                                    | 1 = Interrupt request enabled |                 |                                         |                                    |     |       |       |

|                                    | 0 = Interrupt r               | equest not ena  | bled                                    |                                    |     |       |       |

bit 0 Unimplemented: Read as '0'

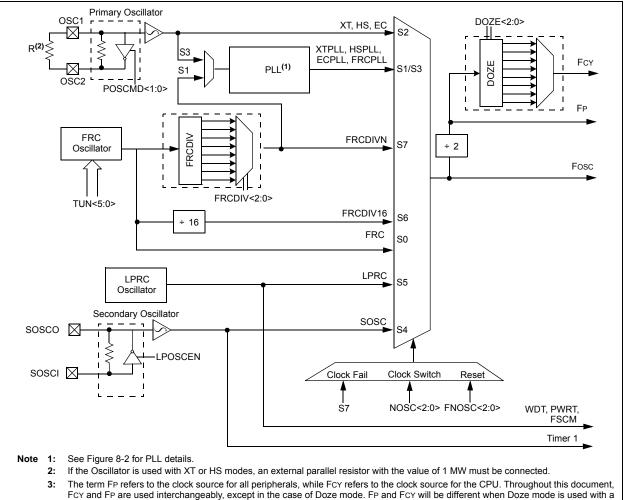

## 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "Oscillator" (DS70186) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJ12GP201/202 oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

A simplified diagram of the oscillator system is shown in Figure 8-1.

### FIGURE 8-1: dsPIC33FJ12GP201/202 OSCILLATOR SYSTEM DIAGRAM

Doze ratio of 1:2 or lower.

| REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER <sup>(2)</sup> |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| R/W-0         | R/W-0                                                                                                                                                                                                           | R/W-1                                                                                 | R/W-1         | R/W-0                      | R/W-0           | R/W-0              | R/W-0      |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|---------------|----------------------------|-----------------|--------------------|------------|--|

| ROI           |                                                                                                                                                                                                                 | DOZE<2:0>                                                                             |               | DOZEN <sup>(1)</sup>       |                 | FRCDIV<2:0>        |            |  |

| bit 15        | •                                                                                                                                                                                                               |                                                                                       |               |                            |                 |                    | bit 8      |  |

| R/W-0         | R/W-1                                                                                                                                                                                                           | U-0                                                                                   | R/W-0         | R/W-0                      |                 | R/W-0              | R/W-0      |  |

|               |                                                                                                                                                                                                                 | 0-0                                                                                   | R/W-U         | R/W-0                      | R/W-0           |                    | R/W-U      |  |

| bit 7         | OST<1:0>                                                                                                                                                                                                        | _                                                                                     |               |                            | PLLPRE<4:0      | >                  | bit (      |  |

| DIL 7         |                                                                                                                                                                                                                 |                                                                                       |               |                            |                 |                    | bit (      |  |

| Legend:       |                                                                                                                                                                                                                 | y = Value set                                                                         | from Configu  | ration bits on PC          | )R              |                    |            |  |

| R = Readabl   | e bit                                                                                                                                                                                                           | W = Writable                                                                          | bit           | U = Unimplem               | ented bit, read | d as '0'           |            |  |

| -n = Value at | POR                                                                                                                                                                                                             | '1' = Bit is set                                                                      |               | '0' = Bit is clea          | ared            | x = Bit is unkn    | iown       |  |

| bit 15        | 1 = Interrupt                                                                                                                                                                                                   | r on Interrupt bi<br>s will clear the I<br>s have no effec                            | DOZEN bit ar  | nd the processor<br>EN bit | clock/periphe   | ral clock ratio is | set to 1:1 |  |

| bit 14-12     | DOZE<2:0>: Processor Clock Reduction Select bits<br>111 = Fcy/128<br>110 = Fcy/64<br>101 = Fcy/32<br>100 = Fcy/16<br>011 = Fcy/8 (default)<br>010 = Fcy/4<br>001 = Fcy/2<br>000 = Fcy/1                         |                                                                                       |               |                            |                 |                    |            |  |

| bit 11        | <b>DOZEN:</b> DOZE Mode Enable bit <sup>(1)</sup><br>1 = DOZE<2:0> field specifies the ratio between the peripheral clocks and the processor clocks<br>0 = Processor clock/peripheral clock ratio forced to 1:1 |                                                                                       |               |                            |                 |                    |            |  |

| bit 10-8      | 111 = FRC d<br>110 = FRC d<br>101 = FRC d<br>100 = FRC d<br>011 = FRC d<br>010 = FRC d<br>001 = FRC d                                                                                                           | ivide by 256<br>ivide by 64<br>ivide by 32<br>ivide by 16<br>ivide by 8<br>ivide by 4 |               | r Postscaler bits          |                 |                    |            |  |

| bit 7-6       | PLLPOST<1:0>: PLL VCO Output Divider Select bits (also denoted as 'N2', PLL postscaler)<br>11 = Output/8<br>10 = Reserved<br>01 = Output/4 (default)<br>00 = Output/2                                           |                                                                                       |               |                            |                 |                    |            |  |

| bit 5         | Unimplemen                                                                                                                                                                                                      | ted: Read as '                                                                        | 0'            |                            |                 |                    |            |  |

| bit 4-0       | PLLPRE<4:0<br>11111 = Inpu<br>00001 = Inpu                                                                                                                                                                      | ut/33                                                                                 | Detector Inpu | t Divider bits (al         | so denoted as   | 'N1', PLL presc    | caler)     |  |

|               | 00001 = Inpt<br>00000 = Inpt                                                                                                                                                                                    |                                                                                       |               |                            |                 |                    |            |  |

- Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register is reset only on a Power-on Reset (POR).

| U-0                               | U-0              | U-0              | U-0            | U-0                                | U-0             | U-0                | R/W-0 <sup>(1)</sup> |  |

|-----------------------------------|------------------|------------------|----------------|------------------------------------|-----------------|--------------------|----------------------|--|

|                                   | —                | —                | —              | —                                  | —               | —                  | PLLDIV<8>            |  |

| bit 15                            |                  |                  |                |                                    |                 |                    | bit 8                |  |

|                                   |                  |                  |                |                                    |                 |                    |                      |  |

| R/W-0                             | R/W-0            | R/W-1            | R/W-1          | R/W-0                              | R/W-0           | R/W-0              | R/W-0                |  |

|                                   |                  |                  | PLLD           | IV<7:0>                            |                 |                    |                      |  |

| bit 7                             |                  |                  |                |                                    |                 |                    | bit 0                |  |

|                                   |                  |                  |                |                                    |                 |                    |                      |  |

| Legend:                           |                  |                  |                |                                    |                 |                    |                      |  |

| R = Readable bit W = Writable bit |                  |                  | bit            | U = Unimplemented bit, read as '0' |                 |                    |                      |  |

| -n = Value at                     | POR              | '1' = Bit is set |                | '0' = Bit is cleared               |                 | x = Bit is unknown |                      |  |

|                                   |                  |                  |                |                                    |                 |                    |                      |  |

| bit 15-9                          | Unimplemen       | ted: Read as '   | 0'             |                                    |                 |                    |                      |  |

| bit 8-0                           | PLLDIV<8:0>      | PLL Feedbac      | k Divisor bits | (also denoted                      | as 'M', PLL mul | tiplier)           |                      |  |

|                                   | 111111111 =      | = 513            |                |                                    |                 |                    |                      |  |

|                                   | •                |                  |                |                                    |                 |                    |                      |  |

|                                   | •                |                  |                |                                    |                 |                    |                      |  |

|                                   | •                |                  |                |                                    |                 |                    |                      |  |

| 000110000 <b>= 50 (default)</b>   |                  |                  |                |                                    |                 |                    |                      |  |

|                                   | •                |                  |                |                                    |                 |                    |                      |  |

|                                   | •                |                  |                |                                    |                 |                    |                      |  |

|                                   | •<br>000000010 = | - 1              |                |                                    |                 |                    |                      |  |

|                                   | 000000010 =      |                  |                |                                    |                 |                    |                      |  |

|                                   | 000000000        |                  |                |                                    |                 |                    |                      |  |

|                                   |                  |                  |                |                                    |                 |                    |                      |  |

# REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

| TABLE 10-1: | SELECTABLE INPUT SOURCES (MAPS INPUT TO FUNCTION) <sup>(1)</sup> |

|-------------|------------------------------------------------------------------|

|-------------|------------------------------------------------------------------|

| Input Name              | Function Name | Register | Configuration<br>Bits |

|-------------------------|---------------|----------|-----------------------|

| External Interrupt 1    | INT1          | RPINR0   | INT1R<4:0>            |

| External Interrupt 2    | INT2          | RPINR1   | INT2R<4:0>            |

| Timer2 External Clock   | T2CK          | RPINR3   | T2CKR<4:0>            |

| Timer3 External Clock   | T3CK          | RPINR3   | T3CKR<4:0>            |

| Input Capture 1         | IC1           | RPINR7   | IC1R<4:0>             |

| Input Capture 2         | IC2           | RPINR7   | IC2R<4:0>             |

| Input Capture 7         | IC7           | RPINR10  | IC7R<4:0>             |

| Input Capture 8         | IC8           | RPINR10  | IC8R<4:0>             |

| Output Compare Fault A  | OCFA          | RPINR11  | OCFAR<4:0>            |

| UART1 Receive           | U1RX          | RPINR18  | U1RXR<4:0>            |

| UART1 Clear To Send     | U1CTS         | RPINR18  | U1CTSR<4:0>           |

| SPI1 Data Input         | SDI1          | RPINR20  | SDI1R<4:0>            |

| SPI1 Clock Input        | SCK1IN        | RPINR20  | SCK1R<4:0>            |

| SPI1 Slave Select Input | SS1IN         | RPINR21  | SS1R<4:0>             |

Note 1: Unless otherwise noted, all inputs use the Schmitt input buffers.

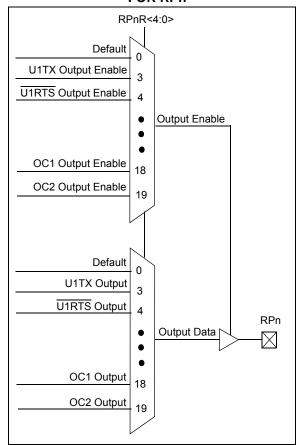

### 10.4.2.2 Output Mapping

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPORx registers are used to control output mapping. Like the RPINRx registers, each register contains sets of 5-bit fields, with each set associated with one RPn pin (see Register 10-10 through Register 10-17). The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 10-2 and Figure 10-2).

The list of peripherals for output mapping also includes a null value of '00000' because of the mapping technique. This permits any given pin to remain unconnected from the output of any of the pin selectable peripherals.

# FIGURE 10-3:

#### MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPn

REGISTER 12-1: T2CON CONTROL REGISTER

| R/W-0         | U-0                                                                                                  | R/W-0           | U-0          | U-0               | U-0             | U-0              | U-0   |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------|-----------------|--------------|-------------------|-----------------|------------------|-------|--|--|--|--|

| TON           | —                                                                                                    | TSIDL           | _            | _                 | _               |                  | _     |  |  |  |  |

| bit 15        |                                                                                                      |                 |              |                   |                 |                  | bit 8 |  |  |  |  |

|               |                                                                                                      |                 |              |                   |                 |                  |       |  |  |  |  |

| U-0           | R/W-0                                                                                                | R/W-0           | R/W-0        | R/W-0             | U-0             | R/W-0            | U-0   |  |  |  |  |

|               | TGATE                                                                                                | TCKP            | S<1:0>       | Т32               | T32 — TCS       |                  |       |  |  |  |  |

| bit 7         |                                                                                                      |                 |              |                   |                 |                  | bit ( |  |  |  |  |

| Legend:       |                                                                                                      |                 |              |                   |                 |                  |       |  |  |  |  |

| R = Readabl   | e bit                                                                                                | W = Writable    | bit          | U = Unimplem      | nented bit, rea | d as '0'         |       |  |  |  |  |

| -n = Value at | POR                                                                                                  | '1' = Bit is se | t            | '0' = Bit is clea | ared            | x = Bit is unkno | own   |  |  |  |  |

| bit 15        | TON: Timer2                                                                                          | On hit          |              |                   |                 |                  |       |  |  |  |  |

| DIL 15        | When $T32 = 2$                                                                                       |                 |              |                   |                 |                  |       |  |  |  |  |

|               | 1 = Starts 32-                                                                                       |                 |              |                   |                 |                  |       |  |  |  |  |

|               | 0 = Stops 32-                                                                                        | bit Timer2/3    |              |                   |                 |                  |       |  |  |  |  |

|               | When T32 = 0:                                                                                        |                 |              |                   |                 |                  |       |  |  |  |  |

|               | 1 = Starts 16-bit Timer2<br>0 = Stops 16-bit Timer2                                                  |                 |              |                   |                 |                  |       |  |  |  |  |

| bit 14        | -                                                                                                    | ited: Read as   | 0'           |                   |                 |                  |       |  |  |  |  |

| bit 13        | -                                                                                                    |                 |              |                   |                 |                  |       |  |  |  |  |

|               | <b>TSIDL:</b> Stop in Idle Mode bit<br>1 = Discontinue module operation when device enters Idle mode |                 |              |                   |                 |                  |       |  |  |  |  |

|               |                                                                                                      | module opera    |              |                   |                 |                  |       |  |  |  |  |

| bit 12-7      | Unimplemen                                                                                           | ted: Read as    | 0'           |                   |                 |                  |       |  |  |  |  |

| bit 6         | TGATE: Timer2 Gated Time Accumulation Enable bit                                                     |                 |              |                   |                 |                  |       |  |  |  |  |

|               | When TCS = 1:                                                                                        |                 |              |                   |                 |                  |       |  |  |  |  |

|               | This bit is ignored.<br>When TCS = 0:                                                                |                 |              |                   |                 |                  |       |  |  |  |  |

|               | 1 = Gated time accumulation enabled                                                                  |                 |              |                   |                 |                  |       |  |  |  |  |

|               | 0 = Gated time accumulation disabled                                                                 |                 |              |                   |                 |                  |       |  |  |  |  |

| bit 5-4       | TCKPS<1:0>                                                                                           | : Timer2 Input  | Clock Presca | ale Select bits   |                 |                  |       |  |  |  |  |

|               | 11 = 1:256                                                                                           |                 |              |                   |                 |                  |       |  |  |  |  |

|               | 10 = 1:64<br>01 = 1:8                                                                                |                 |              |                   |                 |                  |       |  |  |  |  |

|               | 00 = 1:1                                                                                             |                 |              |                   |                 |                  |       |  |  |  |  |

| bit 3         | T32: 32-bit Timer Mode Select bit                                                                    |                 |              |                   |                 |                  |       |  |  |  |  |

|               | 1 = Timer2 and Timer3 form a single 32-bit timer<br>0 = Timer2 and Timer3 act as two 16-bit timers   |                 |              |                   |                 |                  |       |  |  |  |  |

| bit 2         | Unimplemen                                                                                           | ted: Read as    | 0'           |                   |                 |                  |       |  |  |  |  |

| bit 1         | TCS: Timer2                                                                                          | Clock Source    | Select bit   |                   |                 |                  |       |  |  |  |  |

|               |                                                                                                      | clock from pin  | T2CK (on the | rising edge)      |                 |                  |       |  |  |  |  |

|               | 0 = Internal c                                                                                       |                 | - 1          |                   |                 |                  |       |  |  |  |  |

| bit 0         | Unimplemen                                                                                           | ted: Read as    | 0'           |                   |                 |                  |       |  |  |  |  |

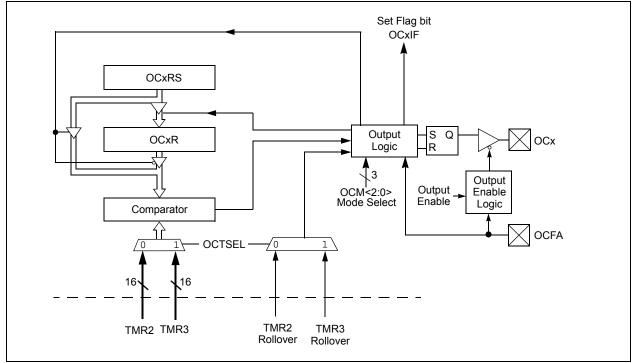

# 14.0 OUTPUT COMPARE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Output Compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the compare register value. The Output Compare module generates either a single output pulse or a sequence of output pulses, by changing the state of the output pin on the compare match events. The Output Compare module can also generate interrupts on compare match events.

The Output Compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- · Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without fault protection

- PWM mode with fault protection

### FIGURE 14-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

NOTES:

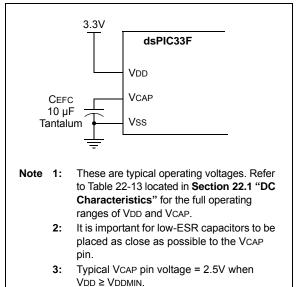

### 19.2 On-Chip Voltage Regulator

The dsPIC33FJ12GP201/202 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, both devices in the dsPIC33FJ12GP201/202 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 19-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 22-13 located in **Section 22.1** "**DC Characteristics**".

| Note: | It is important for low-ESR capacitors to  |

|-------|--------------------------------------------|

|       | be placed as close as possible to the VCAP |

|       | pin.                                       |

On a POR, it takes approximately 20 µs for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

### FIGURE 19-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

### 19.3 BOR Module

The BOR module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

### TABLE 20-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br>#                 | Assembly<br>Mnemonic |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Assembly Syntax                | Description                              | # of<br>Words                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | # of<br>Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Status Flags<br>Affected |

|------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 1                                  | ADD                  | ADD Acc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                | Add Accumulators                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OA,OB,SA,SB              |

|                                    |                      | ADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f                              | f = f + WREG                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C,DC,N,OV,Z              |

|                                    |                      | ADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f,WREG                         | WREG = f + WREG                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C,DC,N,OV,Z              |

|                                    |                      | ADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | #lit10,Wn                      | Wd = lit10 + Wd                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C,DC,N,OV,Z              |

|                                    |                      | ADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Wb,Ws,Wd                       | Wd = Wb + Ws                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C,DC,N,OV,Z              |

|                                    |                      | ADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Wb,#lit5,Wd                    | Wd = Wb + lit5                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | C,DC,N,OV,Z              |

|                                    |                      | ADD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Wso,#Slit4,Acc                 | 16-bit Signed Add to Accumulator         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OA,OB,SA,SB              |