Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

Ξ·ΧΕΙ

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 13                                                                               |

| Program Memory Size        | 12KB (12K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 6x12b                                                                        |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 18-SOIC (0.295", 7.50mm Width)                                                   |

| Supplier Device Package    | 18-SOIC                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp201t-i-so |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz <  $F_{IN}$  < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

When the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV, and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

## 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in the register that correspond to the A/D pins that are initialized by MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE In-Circuit Emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

## 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternately, connect a 1k to 10k resistor between Vss and unused pins and drive the output to logic low.

## TABLE 4-11: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2      | Bit 1    | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|--------|------------|-------|-------|-------|-------|-------|-------|-------|------------|----------|-------|---------------|

| RPINR0       | 0680 | _      | _      |        |        |        | INT1R<4:0> | •     |       | —     | _     |       |       |       | —          |          |       | 1F00          |

| RPINR1       | 0682 | _      | _      |        |        |        | —          |       | —     | _     | _     |       |       |       | INT2R<4:0> | •        |       | 001F          |

| RPINR3       | 0686 |        | -      | -      |        | ٦      | 3CKR<4:0   | >     |       | _     | _     |       |       | ٦     | [2CKR<4:0  | >        |       | 1F1F          |

| RPINR7       | 068E | -      | -      | _      |        |        | IC2R<4:0>  |       |       | _     | _     | _     |       |       | IC1R<4:0>  |          |       | 1F1F          |

| RPINR10      | 0694 |        |        | _      |        |        | IC8R<4:0>  |       |       | _     | _     | _     |       |       | IC7R<4:0>  |          |       | 1F1F          |

| RPINR11      | 0696 | _      | _      | _      | _      | _      | _          | _     | _     | _     | _     | _     |       | (     | DCFAR<4:0  | >        |       | 001F          |

| RPINR18      | 06A4 | _      | _      | _      |        | U      | 1CTSR<4:0  | )>    |       | _     | _     | _     |       | ι     | J1RXR<4:0  | >        |       | 1F1F          |

| RPINR20      | 06A8 | _      | _      | _      |        | 5      | SCK1R<4:0  | >     |       | _     | _     | _     |       | :     | SDI1R<4:0> | <b>`</b> |       | 1F1F          |

| RPINR21      | 06AA | _      | _      | _      | _      |        | _          | _     | _     | _     | _     |       |       |       | SS1R<4:0>  |          |       | 001F          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-12: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dspic33FJ12GP202

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11    | Bit 10    | Bit 9 | Bit 8 | Bit 7 | Bit 6     | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|--------------|------|--------|--------|--------|--------|-----------|-----------|-------|-------|-------|-----------|-------|-------|-------|-----------|-------|-------|---------------|

| RPOR0        | 06C0 | _      |        | _      |        | RP1R<4:0> |           | _     |       | —     | RP0R<4:0> |       |       | 0000  |           |       |       |               |

| RPOR1        | 06C2 | _      |        | _      |        |           | RP3R<4:0> |       |       | _     |           | _     |       |       | RP2R<4:0> |       |       | 0000          |

| RPOR2        | 06C4 | _      |        | _      |        |           | RP5R<4:0> |       |       | _     |           | _     |       |       | RP4R<4:0> |       |       | 0000          |

| RPOR3        | 06C6 | _      |        | _      |        |           | RP7R<4:0> |       |       | _     |           | _     |       |       | RP6R<4:0> |       |       | 0000          |

| RPOR4        | 06C8 | _      |        | _      |        |           | RP9R<4:0> |       |       | _     |           | _     |       |       | RP8R<4:0> |       |       | 0000          |

| RPOR5        | 06CA | _      |        | _      |        | I         | RP11R<4:0 | >     |       | _     |           | _     |       | F     | RP10R<4:0 | >     |       | 0000          |

| RPOR6        | 06CC | _      |        | _      |        | I         | RP13R<4:0 | >     |       | _     |           | _     |       | F     | RP12R<4:0 | >     |       | 0000          |

| RPOR7        | 06CE | _      |        | _      |        | I         | RP15R<4:0 | >     |       | _     |           | _     |       | F     | RP14R<4:0 | >     |       | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-13: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP FOR dsPIC33FJ12GP201

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10     | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2     | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|------------|-------|-------|-------|-------|-------|-------|-------|-----------|-------|-------|---------------|

| RPOR0     | 06C0 | _      | _      | _      |        |        | RP1R<4:0>  |       |       | _     | _     | _     |       |       | RP0R<4:0> |       |       | 0000          |

| RPOR2     | 06C4 | _      | _      | _      | _      | _      | _          | _     | _     | _     | _     | _     |       |       | RP4R<4:0> |       |       | 0000          |

| RPOR3     | 06C6 | _      | _      | _      |        |        | RP7R<4:0>  |       |       | _     | _     | _     | _     | _     | _         | _     | _     | 0000          |

| RPOR4     | 06C8 | _      | —      | _      |        |        | RP9R<4:0>  |       |       |       | _     | _     |       |       | RP8R<4:0> |       |       | 0000          |

| RPOR7     | 06CE | _      | _      | _      |        | F      | RP15R<4:0> | >     |       |       | _     | _     |       | F     | RP14R<4:0 | >     |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# dsPIC33FJ12GP201/202

NOTES:

# dsPIC33FJ12GP201/202

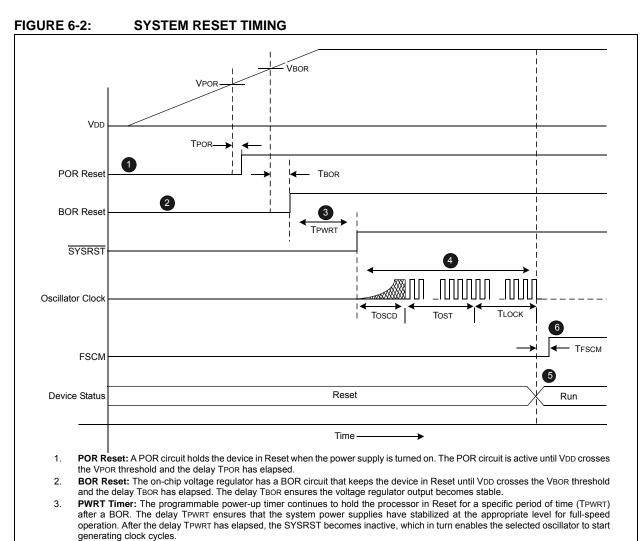

- Oscillator Delay: The total delay for the clock to be ready for various clock source selections are given in Table 6-1. Refer to Section 8.0 "Oscillator Configuration" for more information.

- 5. When the oscillator clock is ready, the processor begins execution from location 0x000000. The user application programs a GOTO instruction at the Reset address, which redirects program execution to the appropriate start-up routine.

- 6. The Fail-safe clock monitor (FSCM), if enabled, begins to monitor the system clock when the system clock is ready and the delay TFSCM elapsed.

| Symbol | Parameter                              | Value            |  |  |  |  |  |  |  |  |

|--------|----------------------------------------|------------------|--|--|--|--|--|--|--|--|

| VPOR   | POR threshold                          | 1.8V nominal     |  |  |  |  |  |  |  |  |

| TPOR   | POR extension time                     | 30 µs maximum    |  |  |  |  |  |  |  |  |

| VBOR   | BOR threshold                          | 2.5V nominal     |  |  |  |  |  |  |  |  |

| TBOR   | BOR extension time                     | 100 μs maximum   |  |  |  |  |  |  |  |  |

| TPWRT  | Programmable<br>power-up time<br>delay | 0-128 ms nominal |  |  |  |  |  |  |  |  |

| TFSCM  | Fail-safe Clock<br>Monitor Delay       | 900 μs maximum   |  |  |  |  |  |  |  |  |

## TABLE 6-2:OSCILLATOR DELAY

| Note: | When the device exits the Reset condi-<br>tion (begins normal operation), the<br>device operating parameters (voltage,<br>frequency, temperature, etc.) must be<br>within their operating ranges, other-<br>wise the device may not function cor-<br>rectly. The user application must<br>ensure that the delay between the time<br><u>power is</u> first applied, and the time<br><u>SYSRST</u> becomes inactive, is long<br>enough to get all operating parameters<br>within specification. |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

#### 6.2 POR

A POR circuit ensures the device is reset from poweron. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 22.0 "Electrical Characteristics" for details.

The POR status bit (POR) in the Reset Control register (RCON<0>) is set to indicate the POR.

#### 6.3 BOR and PWRT

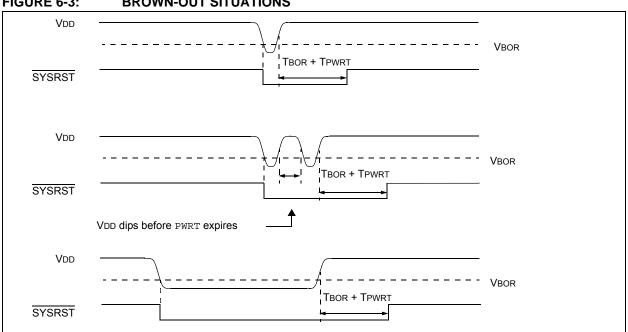

The on-chip regulator has a BOR circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

FIGURE 6-3: **BROWN-OUT SITUATIONS**  The BOR status bit (BOR) in the Reset Control register (RCON<1>) is set to indicate the BOR.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provides eight settings (from 0 ms to 128 ms). Refer to Section 19.0 "Special Features" for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point.

## 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Interrupts" (DS70184) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Microchip dsPIC33FJ12GP201/202 interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJ12GP201/202 CPU. It has the following features:

- Up to eight processor exceptions and software traps

- · Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- · Fixed interrupt entry and return latencies

## 7.1 Interrupt Vector Table

The Interrupt Vector Table is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of eight nonmaskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

The dsPIC33FJ12GP201/202 devices implement up to 21 unique interrupts and four nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

#### 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a way to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications to facilitate evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJ12GP201/202 device clears its registers in response to a Reset, which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. The user application can use a GOTO instruction at the Reset address that redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

## 8.1 CPU Clocking System

The dsPIC33FJ12GP201/202 devices provide seven system clock options:

- Fast RC (FRC) Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- · Low-Power RC (LPRC) Oscillator

- FRC Oscillator with postscaler

## 8.1.1 SYSTEM CLOCK SOURCES

## 8.1.1.1 Fast RC

The Fast RC (FRC) internal oscillator runs at a nominal frequency of 7.37 MHz. User software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> bits (CLKDIV<10:8>).

## 8.1.1.2 Primary

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): The external clock signal is directly applied to the OSC1 pin.

## 8.1.1.3 Secondary

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

#### 8.1.1.4 Low-Power RC

The Low-Power RC (LPRC) internal oscIllator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

## 8.1.1.5 FRC

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 8.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 22-18) and the value of the FRC Oscillator Tuning register (see Register 8-4).

## 8.1.2 SYSTEM CLOCK SELECTION

The oscillator source used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 19.1 "Configuration Bits"** for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose among 12 different clock modes, shown in Table 8-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) FOSC is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device, and speeds up to 40 MHz are supported by the dsPIC33FJ12GP201/202 architecture.

Instruction execution speed or device operating frequency, FCY, is given by Equation 8-1.

#### EQUATION 8-1: DEVICE OPERATING FREQUENCY

FCY = FOSC/2

## 8.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides significant flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 8-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3,..., or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected in the range of 0.8 MHz to 8 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M,' by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2.' This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4, or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

## TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                 | Oscillator<br>Source | POSCMD<1:0> | FNOSC<2:0> | Note |

|-------------------------------------------------|----------------------|-------------|------------|------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal             | xx          | 111        | 1, 2 |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal             | xx          | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                  | Internal             | xx          | 101        | 1    |

| Secondary (Timer1) Oscillator (SOSC)            | Secondary            | xx          | 100        | 1    |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary              | 10          | 011        |      |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary              | 01          | 011        |      |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary              | 00          | 011        | 1    |

| Primary Oscillator (HS)                         | Primary              | 10          | 010        |      |

| Primary Oscillator (XT)                         | Primary              | 01          | 010        |      |

| Primary Oscillator (EC)                         | Primary              | 00          | 010        | 1    |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal             | xx          | 001        | 1    |

| Fast RC Oscillator (FRC)                        | Internal             | xx          | 000        | 1    |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

**2:** This is the default oscillator mode for an unprogrammed (erased) device.

## REGISTER 10-13: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTERS 3

| U-0          | U-0        | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0             | R/W-0    |

|--------------|------------|------------------|-------|------------------|-----------------|-------------------|----------|

| _            | —          | —                |       |                  | RP7R<4:0>       |                   |          |

| bit 15       |            |                  |       |                  |                 |                   | bit 8    |

|              |            |                  |       |                  |                 |                   |          |

| U-0          | U-0        | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0             | R/W-0    |

| —            | —          | —                |       |                  | RP6R<4:0>       |                   |          |

| bit 7        |            |                  |       |                  |                 |                   | bit 0    |

|              |            |                  |       |                  |                 |                   |          |

| Legend:      |            |                  |       |                  |                 |                   |          |

| R = Readab   | le bit     | W = Writable     | bit   | U = Unimpler     | nented bit, rea | d as '0'          |          |

| -n = Value a | t POR      | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr   | nown     |

|              |            |                  |       |                  |                 |                   |          |

| bit 15-13    | Unimplemen | ted: Read as 'o  | כי    |                  |                 |                   |          |

| bit 12-8     |            | Peripheral Outr  |       | s Assigned to F  | RP7 Output Pir  | i bits (see Table | 10-2 for |

| bit 7-5      | Unimplemen | ted: Read as '   | כ'    |                  |                 |                   |          |

|              |            |                  |       |                  |                 |                   |          |

bit 4-0 **RP6R<4:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-14: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTERS 0

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP9R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP8R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 10-2 for peripheral function numbers)

| U-0                 | U-0                            | U-0                                   | R/W-0           | R/W-0              | R/W-0             | R/W-0             | R/W-0              |

|---------------------|--------------------------------|---------------------------------------|-----------------|--------------------|-------------------|-------------------|--------------------|

|                     | _                              | —                                     | DISSCK          | DISSDO             | MODE16            | SMP               | CKE <sup>(1)</sup> |

| bit 15              |                                |                                       |                 |                    |                   |                   | bit                |

|                     |                                |                                       |                 |                    |                   |                   |                    |

| R/W-0               | R/W-0                          | R/W-0                                 | R/W-0           | R/W-0              | R/W-0             | R/W-0             | R/W-0              |

| SSEN <sup>(2)</sup> | CKP                            | MSTEN                                 |                 | SPRE<2:0>(3)       |                   | PPRE<             |                    |

| bit 7               |                                |                                       |                 |                    |                   |                   | bit                |

| Legend:             |                                |                                       |                 |                    |                   |                   |                    |

| R = Readable        | e bit                          | W = Writable                          | bit             | U = Unimplem       | ented bit, read   | l as '0'          |                    |

| -n = Value at       | POR                            | '1' = Bit is set                      |                 | '0' = Bit is clea  | red               | x = Bit is unkn   | iown               |

|                     |                                |                                       |                 |                    |                   |                   |                    |

| bit 15-13           | -                              | nted: Read as '                       |                 |                    |                   |                   |                    |

| bit 12              |                                | able SCKx pin                         |                 | • /                |                   |                   |                    |

|                     |                                | SPI clock is disa<br>SPI clock is ena |                 | tions as I/O       |                   |                   |                    |

| oit 11              |                                | sable SDOx pin                        |                 |                    |                   |                   |                    |

|                     |                                | n is not used by                      |                 | unctions as I/O    |                   |                   |                    |

|                     |                                | n is controlled b                     |                 |                    |                   |                   |                    |

| oit 10              | MODE16: W                      | ord/Byte Comm                         | unication Sel   | ect bit            |                   |                   |                    |

|                     |                                | ication is word-<br>ication is byte-v |                 |                    |                   |                   |                    |

| bit 9               |                                | ata Input Samp                        |                 |                    |                   |                   |                    |

|                     | Master mode                    |                                       |                 |                    |                   |                   |                    |

|                     | 1 = Input dat                  | a sampled at er                       |                 |                    |                   |                   |                    |

|                     |                                | a sampled at m                        | iddle of data o | output time        |                   |                   |                    |

|                     | Slave mode:<br>SMP must be     | e cleared when                        | SPIx is used i  | in Slave mode      |                   |                   |                    |

| bit 8               |                                | lock Edge Sele                        |                 |                    |                   |                   |                    |

|                     |                                | •                                     |                 | on from active cl  | ock state to Id   | le clock state (s | see bit 6)         |

|                     |                                |                                       |                 | on from Idle cloc  | k state to activ  | /e clock state (s | see bit 6)         |

| oit 7               |                                | e Select Enable                       |                 | de) <sup>(2)</sup> |                   |                   |                    |

|                     |                                | used for Slave r                      |                 |                    | <b>t</b> '        |                   |                    |

| -: ·                |                                |                                       |                 | rolled by port fur | ICTION.           |                   |                    |

| bit 6               |                                | Polarity Select b                     |                 | /e state is a low  | lovol             |                   |                    |

|                     |                                |                                       |                 | e state is a high  |                   |                   |                    |

| oit 5               |                                | ster Mode Enab                        |                 | · ·                |                   |                   |                    |

|                     | 1 = Master m<br>0 = Slave mo   |                                       |                 |                    |                   |                   |                    |

|                     | ne CKE bit is no<br>RMEN = 1). | t used in the Fra                     | amed SPI mo     | des. Program th    | is bit to '0' for | the Framed SP     | I modes            |

| -                   | nis bit must be c              | leared when FF                        | RMEN = 1.       |                    |                   |                   |                    |

|                     |                                |                                       |                 | loro to o voluo o  | £ 4 . 4           |                   |                    |

**3:** Do not set both Primary and Secondary prescalers to a value of 1:1.

## REGISTER 17-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <b>BRGH:</b> High Baud Rate Enable bit<br>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)<br>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode) |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits<br>11 = 9-bit data, no parity<br>10 = 8-bit data, odd parity<br>01 = 8-bit data, even parity<br>00 = 8-bit data, no parity                              |

| bit 0   | STSEL: Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                                             |

- **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

## REGISTER 17-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                                                                                |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                                                                         |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                                                                            |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                                                                           |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                                                       |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>                                                        |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                                                      |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                                                                        |

|       | 0 = Framing error has not been detected                                                                                                                                                                                         |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read-only/clear-only)                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 → 0 transition) will reset<br/>the receiver buffer and the UxRSR to the empty state</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                                            |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                   |

**Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

# dsPIC33FJ12GP201/202

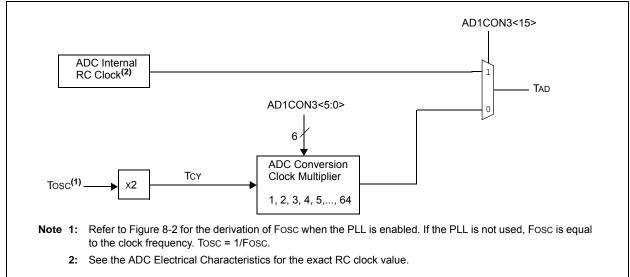

## FIGURE 18-3: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

# dsPIC33FJ12GP201/202

| TABLE 19-2: | USFICSSE |                                                                                                                 | 7202 CONFIGURATION BITS DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Field   | Register | RTSP<br>Effect                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                         |

| BWRP        | FBS      | Immediate                                                                                                       | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                               |

| BSS<2:0>    | FBS      | Immediate                                                                                                       | Boot Segment Program Flash Code Protection Size<br>x11 = No Boot program Flash segment                                                                                                                                                                                                                                                                                                              |

|             |          |                                                                                                                 | Boot space is 256 Instruction Words (except interrupt vectors)<br>110 = Standard security; boot program Flash segment ends at 0x0003FE<br>010 = High security; boot program Flash segment ends at 0x0003FE                                                                                                                                                                                          |

|             |          |                                                                                                                 | Boot space is 768 Instruction Words (except interrupt vectors)<br>101 = Standard security; boot program Flash segment, ends at 0x0007FE<br>001 = High security; boot program Flash segment ends at 0x0007FE                                                                                                                                                                                         |

|             |          |                                                                                                                 | Boot space is 1792 Instruction Words (except interrupt vectors)<br>100 = Standard security; boot program Flash segment ends at 0x000FFE<br>000 = High security; boot program Flash segment ends at 0x000FFE                                                                                                                                                                                         |

| GSS<1:0>    | FGS      | Immediate                                                                                                       | General Segment Code-Protect bit<br>11 = User program memory is not code-protected<br>10 = Standard security<br>0x = High security                                                                                                                                                                                                                                                                  |

| GWRP        | FGS      | Immediate                                                                                                       | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                                                                                                                                                   |

| IESO        | FOSCSEL  | Immediate                                                                                                       | <ul> <li>Two-speed Oscillator Start-up Enable bit</li> <li>1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready</li> <li>0 = Start-up device with user-selected oscillator source</li> </ul>                                                                                                                                                   |

| FNOSC<2:0>  | FOSCSEL  | If clock<br>switch is<br>enabled,<br>RTSP<br>effect is<br>on any<br>device<br>Reset;<br>otherwise,<br>Immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) oscillator with postscaler<br>110 = Internal Fast RC (FRC) oscillator with divide-by-16<br>101 = LPRC oscillator<br>100 = Secondary (LP) oscillator<br>011 = Primary (XT, HS, EC) oscillator with PLL<br>010 = Primary (XT, HS, EC) oscillator<br>001 = Internal Fast RC (FRC) oscillator with PLL<br>000 = FRC oscillator |

| FCKSM<1:0>  | FOSC     | Immediate                                                                                                       | Clock Switching Mode bits<br>1x = Clock switching is disabled, fail-safe clock monitor is disabled<br>01 = Clock switching is enabled, fail-safe clock monitor is disabled<br>00 = Clock switching is enabled, fail-safe clock monitor is enabled                                                                                                                                                   |

| IOL1WAY     | FOSC     | Immediate                                                                                                       | Peripheral Pin Select Configuration<br>1 = Allow only one reconfiguration<br>0 = Allow multiple reconfigurations                                                                                                                                                                                                                                                                                    |

| OSCIOFNC    | FOSC     | Immediate                                                                                                       | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is clock output<br>0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                                                                        |

| POSCMD<1:0> | FOSC     | Immediate                                                                                                       | Primary Oscillator Mode Select bits<br>11 = Primary oscillator disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                                                                      |

#### TABLE 19-2: dsPIC33FJ12GP201/202 CONFIGURATION BITS DESCRIPTION

## 21.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

## 21.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

## 21.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

## 21.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 21.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB IDE compatibility

## 21.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit™ 2 enables in-circuit debugging on most PIC® microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

## 21.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

## 21.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## TABLE 22-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| AC CHARACTERISTICS |        |                                                                     | Standard O<br>Operating to |     | ire -40°           | C ≤TA ≤+8 | 5°C for I | <b>(unless otherwise stated)</b><br>ndustrial<br>Extended |

|--------------------|--------|---------------------------------------------------------------------|----------------------------|-----|--------------------|-----------|-----------|-----------------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                                      |                            | Min | Тур <sup>(1)</sup> | Max       | Units     | Conditions                                                |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                            | 0.8 | _                  | 8         | MHz       | ECPLL, HSPLL, XTPLL<br>modes                              |

| OS51               | Fsys   | On-Chip VCO System Frequency                                        |                            | 100 | —                  | 200       | MHz       | —                                                         |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                       |                            | 0.9 | 1.5                | 3.1       | mS        | —                                                         |

| OS53               | DCLK   | CLKO Stability (Jitter)                                             | (2)                        | -3  | 0.5                | 3         | %         | Measured over 100 ms<br>period                            |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

Peripheral Clock Jitter =

$$\frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$

For example: Fosc = 32 MHz, DCLK = 3%, SPI bit rate clock, (i.e., SCK) is 2 MHz.

$$SPI SCK Jitter = \left\lfloor \frac{D_{CLK}}{\sqrt{\left(\frac{32 \ MHz}{2 \ MHz}\right)}} \right\rfloor = \left\lfloor \frac{3\%}{\sqrt{16}} \right\rfloor = \left\lfloor \frac{3\%}{4} \right\rfloor = 0.75\%$$

## TABLE 22-18: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHARACTERISTICS |                                                   | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for industrial $-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |   |                                       |   |                  |                |  |

|--------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------------------|---|------------------|----------------|--|

| Param<br>No.       | Characteristic Min Typ Max Units Conditions       |                                                                                                                                                                                                           |   |                                       |   |                  | tions          |  |

|                    | Internal FRC Accuracy @ 7.3728 MHz <sup>(1)</sup> |                                                                                                                                                                                                           |   |                                       |   |                  |                |  |

| F20a               | FRC                                               | -2                                                                                                                                                                                                        | — | +2                                    | % | -40°C ≤TA ≤+85°C | VDD = 3.0-3.6V |  |

| F20b               | FRC                                               | -5                                                                                                                                                                                                        | — | +5 % -40°C ≤TA ≤+125°C VDD = 3.0-3.6V |   |                  |                |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

#### TABLE 22-19: INTERNAL RC ACCURACY

| AC CHARACTERISTICS |                                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                                              |     |       |                  |                |  |  |

|--------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----|-------|------------------|----------------|--|--|

| Param<br>No.       | Characteristic                     | Min                                                                                                                                                                              | Тур                                          | Max | Units | Condit           | ions           |  |  |

|                    | LPRC @ 32.768 kHz <sup>(1,2)</sup> |                                                                                                                                                                                  |                                              |     |       |                  |                |  |  |

| F21a               | LPRC                               | -20                                                                                                                                                                              | ±6                                           | +20 | %     | -40°C ≤TA ≤+85°C | VDD = 3.0-3.6V |  |  |

| F21b               | LPRC                               | -70                                                                                                                                                                              | -70 — +70 % -40°C ≤TA ≤+125°C VDD = 3.0-3.6V |     |       |                  |                |  |  |

Note 1: Change of LPRC frequency as VDD changes.

2: LPRC accuracy impacts the Watchdog Timer Time-out Period (TwDT1). See Section 19.4 "Watchdog Timer (WDT)" for more information.

#### TABLE 22-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

|              |        |                                                                               | (unles | ard Ope<br>s otherv<br>ting tem | vise sta | <b>ited)</b><br>e -40°C | ns: 3.0V to 3.6V<br>C ≤TA ≤+85°C for Industrial<br>C ≤TA ≤+125°C for Extended        |

|--------------|--------|-------------------------------------------------------------------------------|--------|---------------------------------|----------|-------------------------|--------------------------------------------------------------------------------------|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                                                 | Min    | Тур <sup>(2)</sup>              | Max      | Units                   | Conditions                                                                           |

| SY10         | ТмсL   | MCLR Pulse-Width (low) <sup>(1)</sup>                                         | 2      |                                 | _        | μs                      | -40°C to +85°C                                                                       |

| SY11         | TPWRT  | Power-up Timer Period <sup>(1)</sup>                                          | _      | 2<br>4<br>16<br>32<br>64<br>128 | _        | ms                      | -40°C to +85°C<br>User programmable                                                  |

| SY12         | TPOR   | Power-on Reset Delay <sup>(3)</sup>                                           | 3      | 10                              | 30       | μs                      | -40°C to +85°C                                                                       |

| SY13         | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset <sup>(1)</sup> | 0.68   | 0.72                            | 1.2      | μs                      |                                                                                      |

| SY20         | Twdt1  | Watchdog Timer Time-out<br>Period <sup>(1)</sup>                              | _      | _                               | _        | ms                      | See Section 19.4 "Watchdog<br>Timer (WDT)" and LPRC<br>parameter F21a (Table 22-19). |

| SY30         | Тоѕт   | Oscillator Start-up Time                                                      | —      | 1024<br>Tosc                    | —        | —                       | Tosc = OSC1 period                                                                   |

| SY35         | TFSCM  | Fail-Safe Clock Monitor<br>Delay <sup>(1)</sup>                               | —      | 500                             | 900      | μs                      | -40°C to +85°C                                                                       |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

3: These parameters are characterized, but are not tested in manufacturing.

## 23.0 PACKAGING INFORMATION

## 23.1 Package Marking Information

## 18-Lead PDIP

#### Example

#### 28-Lead SPDIP

Example

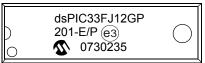

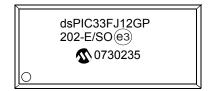

#### 18-Lead SOIC

## Example

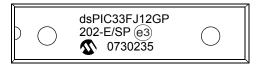

#### 28-Lead SOIC

#### Example

| Legend | : XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>*                                                                                                                                                 | Customer-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (@3)<br>can be found on the outer packaging for this package. |  |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | If the full Microchip part number cannot be marked on one line, it is carried over to the next line, thus limiting the number of available characters for customer-specific information. |                                                                                                                                                                                                                                                                                                                                                                              |  |

#### TABLE 23-1: MAJOR SECTION UPDATES

| Section Name                                 | Update Description                                                                                                                                                                                                                           |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 22.0 "Electrical<br>Characteristics" | Updated Max MIPS value for -40°C to +125°C temperature range in Operating MIPS vs. Voltage (see Table 22-1).                                                                                                                                 |

|                                              | Added 28-pin SSOP package information to Thermal Packaging<br>Characteristics and updated Typical values for all devices (see Table 22-3).                                                                                                   |

|                                              | Removed Typ value for parameter DC12 (see Table 22-4).                                                                                                                                                                                       |

|                                              | Updated Note 2 in Table 22-7: DC Characteristics: Power-Down Current (IPD).                                                                                                                                                                  |

|                                              | Updated MIPS conditions for parameters DC24c, DC44c, DC72a, DC72f, and DC72g (see Table 22-5, Table 22-6, and Table 22-8).                                                                                                                   |

|                                              | Added Note 4 (reference to new table containing digital-only and analog pin information to I/O Pin Input Specifications (see Table 22-9).                                                                                                    |

|                                              | Updated Program Memory parameters (D136a, D136b, D137a, D137b, D138a, and D138b) and added Note 2 (see Table 22-12).                                                                                                                         |

|                                              | Updated Max value for Internal RC Accuracy parameter F21 for -40°C $\leq$ TA $\leq$ +125°C condition and added Note 2 (see Table 22-19).                                                                                                     |

|                                              | Removed all values for Reset, Watchdog Timer, Oscillator Start-up Timer, and Power-up Timer parameter SY20 and updated conditions, which now refers to <b>Section 19.4 "Watchdog Timer (WDT)</b> " and LPRC parameter F21 (see Table 22-21). |

|                                              | The following changes were made to the ADC Module Specifications (Table 22-34):                                                                                                                                                              |

|                                              | Updated Min value for ADC Module Specification parameter AD07                                                                                                                                                                                |

|                                              | Updated Typ value for parameter AD08                                                                                                                                                                                                         |

|                                              | <ul> <li>Removed parameter AD10</li> <li>Added references to Note 1 for parameters AD12 and AD13</li> </ul>                                                                                                                                  |

|                                              | Removed Note 2.                                                                                                                                                                                                                              |

|                                              | The following changes were made to the ADC Module Specifications (12-bit Mode) (Table 22-35):                                                                                                                                                |

|                                              | <ul> <li>Updated Min and Max values for both AD21a parameters (measurements with <i>internal</i> and <i>external</i> VREF+/VREF-).</li> </ul>                                                                                                |

|                                              | <ul> <li>Updated Min, Typ, and Max values for parameter AD24a.</li> </ul>                                                                                                                                                                    |

|                                              | Updated Max value for parameter AD32a.                                                                                                                                                                                                       |

|                                              | Removed Note 1.                                                                                                                                                                                                                              |

|                                              | <ul> <li>Removed VREFL from Conditions for parameters AD21a, AD22a,<br/>AD23a, and AD24a (measurements with <i>internal</i> VREF+/VREF-).</li> </ul>                                                                                         |

|                                              | The following changes were made to the ADC Module Specifications (10-bit Mode) (Table 22-36):                                                                                                                                                |

|                                              | <ul> <li>Updated Min and Max values for parameter AD21b (measurements<br/>with <i>external</i> VREF+/VREF-).</li> </ul>                                                                                                                      |

|                                              | <ul> <li>Removed ± symbol from Min, Typ, and Max values for parameters<br/>AD23b and AD24b (measurements with <i>internal</i> VREF+/VREF-).</li> </ul>                                                                                       |

|                                              | Updated Typ and Max values for parameter AD32b.                                                                                                                                                                                              |

|                                              | Removed Note 1.     Demoved VEEEL from Conditions for parameters AD21a, AD22a                                                                                                                                                                |

|                                              | <ul> <li>Removed VREFL from Conditions for parameters AD21a, AD22a,<br/>AD23a, and AD24a (measurements with <i>internal</i> VREF+/VREF-).</li> </ul>                                                                                         |

|                                              | Updated Min and Typ values for parameters AD60, AD61, AD62, and AD63 and removed Note 3 (see Table 22-37 and Table 22-38).                                                                                                                   |