Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XFI

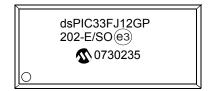

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | <u>.</u>                                                                        |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp202-e-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

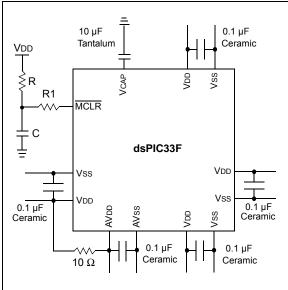

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

# 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

# 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 22.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 19.2 "On-Chip Voltage Regulator"** for details.

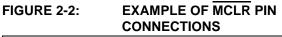

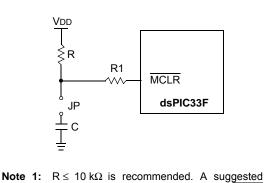

# 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- · Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

- - 2:  $\underline{R1} \leq 470\Omega$  will limit any current flowing into  $\underline{MCLR}$  from the external capacitor C, in the event of  $\underline{MCLR}$  pin breakdown, due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the  $\underline{MCLR}$  pin VIH and VIL specifications are met.

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS70204) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJ12GP201/202 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M by 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ12GP201/202 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJ12GP201/202 instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions. dsPIC33FJ12GP201/202 devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1. The programmer's model for the dsPIC33FJ12GP201/202 is shown in Figure 3-2.

# 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

# 3.2 DSP Engine Overview

The DSP engine features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

# 3.3 Special MCU Features

The dsPIC33FJ12GP201/202 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

#### 4.6 Interfacing Program and Data **Memory Spaces**

The dsPIC33FJ12GP201/202 architecture uses a 24-bit-wide program space and a 16-bit-wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the Microchip dsPIC33FJ12GP201/202 architecture provides two methods by which program space can be accessed during operation:

- · Using table instructions to access individual bytes, or words, anywhere in the program space

- · Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated periodically. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for lookups from a large table of static data. The application can only access the lsw of the program word.

#### 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the MSb of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the MSb of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-24 and Figure 4-7 show how the program EA is created for table operations and remapping accesses from the data EA.

| TABLE 4-24: | PROGR | AM SPACE ADDRE | ESS CONSTRUCTION |

|-------------|-------|----------------|------------------|

|             |       | Access         | Program Sr       |

|                                       | Access        | Program Space Address        |                        |                                     |               |       |  |

|---------------------------------------|---------------|------------------------------|------------------------|-------------------------------------|---------------|-------|--|

| Access Type                           | Space         | <23>                         | <22:16>                | <15>                                | <14:1>        | <0>   |  |

| Instruction Access                    | User          | 0 PC<22:1>                   |                        |                                     |               | 0     |  |

| (Code Execution)                      |               | 0xx xxxx xxxx xxxx xxxx xxx0 |                        |                                     |               |       |  |

| TBLRD/TBLWT<br>(Byte/Word Read/Write) | User          | TB                           | LPAG<7:0>              | Data EA<15:0>                       |               |       |  |

|                                       |               | 0                            | xxx xxxx               | xxxx xx                             | xx xxxx xxxx  |       |  |

|                                       | Configuration | TB                           | LPAG<7:0> Data EA<15:0 |                                     | Data EA<15:0> |       |  |

|                                       |               | 1                            | xxx xxxx               | XXXX X                              | xxx xxxx xxxx |       |  |

| Program Space Visibility              | User          | 0                            | PSVPAG<7               | G<7:0> Data EA<14:0> <sup>(1)</sup> |               | 0>(1) |  |

| (Block Remap/Read)                    |               | 0                            | XXXX XXXX              | 2                                   | xxx xxxx xxxx | xxxx  |  |

Note 1: Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

#### EXAMPLE 5-2: LOADING THE WRITE BUFFERS

| ; | Set up NVMCO  | N for row programming opera | ations                                  |

|---|---------------|-----------------------------|-----------------------------------------|

|   | MOV           | #0x4001, W0                 | ;                                       |

|   | MOV           | W0, NVMCON                  | ; Initialize NVMCON                     |

| ; | Set up a poi  | nter to the first program r | memory location to be written           |

| ; | program memo: | ry selected, and writes ena | abled                                   |

|   | MOV           | #0x0000, W0                 | ;                                       |

|   | MOV           | W0, TBLPAG                  | ; Initialize PM Page Boundary SFR       |

|   | MOV           | #0x6000, W0                 | ; An example program memory address     |

| ; | Perform the ' | TBLWT instructions to write | e the latches                           |

| ; | 0th_program_  | word                        |                                         |

|   | MOV           | #LOW_WORD_0, W2             | ;                                       |

|   | MOV           | <pre>#HIGH_BYTE_0, W3</pre> | ;                                       |

|   | TBLWTL        | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                  | ; Write PM high byte into program latch |

| ; | lst_program_  | word                        |                                         |

|   | MOV           | #LOW_WORD_1, W2             | ;                                       |

|   | MOV           | #HIGH_BYTE_1, W3            | ;                                       |

|   | TBLWTL        | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                  | ; Write PM high byte into program latch |

| ; | 2nd_program   | _word                       |                                         |

|   | MOV           | #LOW_WORD_2, W2             | ;                                       |

|   |               | #HIGH_BYTE_2, W3            | ;                                       |

|   | TBLWTL        | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                  | ; Write PM high byte into program latch |

|   | •             |                             |                                         |

|   | •             |                             |                                         |

|   | •             |                             |                                         |

| ; | 63rd_program  | —                           |                                         |

|   | MOV           | #LOW_WORD_31, W2            | ;                                       |

|   |               | #HIGH_BYTE_31, W3           | ;                                       |

|   |               | W2, [W0]                    | ; Write PM low word into program latch  |

|   | TBLWTH        | W3, [W0++]                  | ; Write PM high byte into program latch |

#### EXAMPLE 5-3: INITIATING A PROGRAMMING SEQUENCE

| DISI |              | ; Block all interrupts with priority <7<br>; for next 5 instructions |

|------|--------------|----------------------------------------------------------------------|

| MOV  | #0x55, W0    |                                                                      |

| MOV  | W0, NVMKEY   | ; Write the 55 key                                                   |

| MOV  | #0xAA, W1 ;  | ;                                                                    |

| MOV  | W1, NVMKEY ; | Write the AA key                                                     |

| BSET | NVMCON, #WR  | Start the erase sequence                                             |

| NOP  | ;            | ; Insert two NOPs after the                                          |

| NOP  | ;            | erase command is asserted                                            |

|      |              |                                                                      |

### 7.3 Interrupt Control and Status Registers

Microchip dsPIC33FJ12GP201/202 devices implement a total of 17 registers for the interrupt controller:

- Interrupt Control Register 1 (INTCON1)

- Interrupt Control Register 2 (INTCON2)

- Interrupt Flag Status Registers (IFSx)

- Interrupt Enable Control Registers (IECx)

- Interrupt Priority Control Registers (IPCx)

- Interrupt Control and Status Register (INTTREG)

#### 7.3.1 INTCON1 AND INTCON2

Global interrupt control functions are controlled from INTCON1 and INTCON2. INTCON1 contains the Interrupt Nesting Disable (NSTDIS) bit as well as the control and status flags for the processor trap sources. The INTCON2 register controls the external interrupt request signal behavior and the use of the Alternate Interrupt Vector Table.

#### 7.3.2 IFSx

The IFS registers maintain all of the interrupt request flags. Each source of interrupt has a status bit, which is set by the respective peripherals or external signal and is cleared via software.

#### 7.3.3 IECx

The IEC registers maintain all of the interrupt enable bits. These control bits are used to individually enable interrupts from the peripherals or external signals.

# 7.3.4 IPCx

The IPC registers are used to set the interrupt priority level for each source of interrupt. Each user interrupt source can be assigned to one of eight priority levels.

#### 7.3.5 INTTREG

The INTTREG register contains the associated interrupt vector number and the new CPU interrupt priority level, which are latched into vector number (VECNUM<6:0>) and interrupt level (ILR<3:0>) bit fields in the INTTREG register. The new interrupt priority level is the priority of the pending interrupt.

The interrupt sources are assigned to the IFSx, IECx, and IPCx registers in the same sequence that they are listed in Table 7-1. For example, the INT0 (External Interrupt 0) is shown as having vector number 8 and a natural order priority of 0. Thus, the INT0IF bit is found in IFS0<0>, the INT0IE bit in IEC0<0>, and the INT0IP bits in the first positions of IPC0 (IPC0<2:0>).

### 7.3.6 STATUS REGISTERS

Although they are not specifically part of the interrupt control hardware, two of the CPU Control registers contain bits that control interrupt functionality:

- The CPU STATUS register, SR, contains the IPL<2:0> bits (SR<7:5>). These bits indicate the current CPU interrupt priority level. The user can change the current CPU priority level by writing to the IPL bits.

- The CORCON register contains the IPL3 bit which, together with IPL<2:0>, also indicates the current CPU priority level. IPL3 is a read-only bit, so that trap events cannot be masked by the user software.

All Interrupt registers are described in Register 7-1 through Register 7-19.

| REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER <sup>(2)</sup> |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| R/W-0         | R/W-0                                                                                                                                  | R/W-1                                                                                 | R/W-1          | R/W-0                              | R/W-0           | R/W-0              | R/W-0      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------|------------------------------------|-----------------|--------------------|------------|

| ROI           |                                                                                                                                        | DOZE<2:0>                                                                             |                | DOZEN <sup>(1)</sup>               |                 | FRCDIV<2:0>        |            |

| bit 15        | •                                                                                                                                      |                                                                                       |                |                                    |                 |                    | bit 8      |

| R/W-0         | R/W-1                                                                                                                                  | U-0                                                                                   | R/W-0          | R/W-0                              |                 | R/W-0              | R/W-0      |

|               |                                                                                                                                        | 0-0                                                                                   | R/W-U          | R/W-0                              | R/W-0           |                    | R/W-U      |

| bit 7         | OST<1:0>                                                                                                                               | _                                                                                     |                |                                    | PLLPRE<4:0      | >                  | bit (      |

| DIL 7         |                                                                                                                                        |                                                                                       |                |                                    |                 |                    | bit (      |

| Legend:       |                                                                                                                                        | y = Value set                                                                         | from Configu   | ration bits on PC                  | )R              |                    |            |

| R = Readabl   | e bit                                                                                                                                  | W = Writable                                                                          | bit            | U = Unimplem                       | ented bit, read | d as '0'           |            |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set                                                                      |                | '0' = Bit is clea                  | ared            | x = Bit is unkn    | iown       |

| bit 15        | 1 = Interrupt                                                                                                                          | r on Interrupt bi<br>s will clear the I<br>s have no effec                            | DOZEN bit ar   | nd the processor<br>EN bit         | clock/periphe   | ral clock ratio is | set to 1:1 |

| bit 14-12     | DOZE<2:0>:<br>111 = FcY/12<br>110 = FcY/62<br>101 = FcY/32<br>100 = FcY/16<br>011 = FcY/8<br>010 = FcY/4<br>001 = FcY/2<br>000 = FcY/1 | 4<br>2<br>3                                                                           | ck Reduction   | Select bits                        |                 |                    |            |

| bit 11        | 1 = DOZE<2                                                                                                                             | ZE Mode Enabl<br>2:0> field specifi<br>or clock/periphe                               | es the ratio b | etween the peri<br>o forced to 1:1 | pheral clocks a | and the process    | or clocks  |

| bit 10-8      | 111 = FRC d<br>110 = FRC d<br>101 = FRC d<br>100 = FRC d<br>011 = FRC d<br>010 = FRC d<br>001 = FRC d                                  | ivide by 256<br>ivide by 64<br>ivide by 32<br>ivide by 16<br>ivide by 8<br>ivide by 4 |                | r Postscaler bits                  |                 |                    |            |

| bit 7-6       | PLLPOST<1<br>11 = Output/8<br>10 = Reserve<br>01 = Output/2<br>00 = Output/2                                                           | 3<br>ed<br>4 (default)                                                                | Output Divide  | er Select bits (als                | o denoted as    | 'N2', PLL posts    | caler)     |

| bit 5         | Unimplemen                                                                                                                             | ted: Read as '                                                                        | 0'             |                                    |                 |                    |            |

| bit 4-0       | PLLPRE<4:0<br>11111 = Inpu<br>00001 = Inpu                                                                                             | ut/33                                                                                 | Detector Inpu  | t Divider bits (al                 | so denoted as   | 'N1', PLL presc    | caler)     |

|               | 00001 = Inpt<br>00000 = Inpt                                                                                                           |                                                                                       |                |                                    |                 |                    |            |

- Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register is reset only on a Power-on Reset (POR).

## 10.4 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low-pin count devices. In an application where more than one peripheral must be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option.

Peripheral pin select configuration enables peripheral set selection and placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, programmers can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Programmers can independently map the input and/or output of most digital peripherals to any one of these I/O pins. Peripheral pin select is performed in software, and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping, when it has been established.

#### 10.4.1 AVAILABLE PINS

The peripheral pin select feature is used with a range of up to 16 pins. The number of available pins depends on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable pin number.

#### 10.4.2 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of special function registers: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 10.4.2.1 Input Mapping

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. A control register associated with a peripheral dictates the pin it will be mapped to. The RPINRx registers are used to configure peripheral input mapping (see Register 10-1 through Register 10-9). Each register contains sets of 5-bit fields, with each set associated with one of the remappable peripherals. Programming a given peripheral's bit field with an appropriate 5-bit value maps the RPn pin with that value to that peripheral. For any given device, the valid range of values for any bit field corresponds to the maximum number of peripheral pin selections supported by the device.

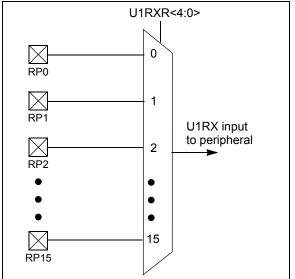

Figure 10-2 Illustrates remappable pin selection for U1RX input.

| Note: | For input mapping only, the Peripheral Pin |

|-------|--------------------------------------------|

|       | Select (PPS) functionality does not have   |

|       | priority over the TRISx settings. There-   |

|       | fore, when configuring the RPn pin for     |

|       | input, the corresponding bit in the TRISx  |

|       | register must also be configured for input |

|       | (i.e., set to '1').                        |

#### 2: REMAPPABLE MUX INPUT FOR U1RX

#### REGISTER 10-8: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| _                                 | _                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      | SCK1R<4:0                                                                                                                                                                                 | 、 <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      | 001111.4.0                                                                                                                                                                                | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| U-0                               | U-0                                                                                                                                                     | R/W-1                                                                                                                                                                                                                                                                                                           | R/W-1                                                                                                                                                                                                                                                                                                                                                                | R/W-1                                                                                                                                                                                     | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| —                                 | —                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      | SDI1R<4:0                                                                                                                                                                                 | 5DI1R<4:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | bit C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|                                   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 | •                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| OR                                | '1' = Bit is set                                                                                                                                        |                                                                                                                                                                                                                                                                                                                 | '0' = Bit is cle                                                                                                                                                                                                                                                                                                                                                     | ared                                                                                                                                                                                      | x = Bit is unkı                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nown                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|                                   |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| -                                 |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| •                                 |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 11111 = Inpu<br>01111 = Inpu<br>• | t tied to Vss<br>t tied to RP15                                                                                                                         | ata Input (SD                                                                                                                                                                                                                                                                                                   | 11) to the corre                                                                                                                                                                                                                                                                                                                                                     | sponaing KPr                                                                                                                                                                              | i pin dits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|                                   | Unimplemen<br>SCK1R<4:0><br>11111 = Inpu<br>01111 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | Unimplemented: Read as '0<br>SCK1R<4:0>: Assign SPI1 (<br>11111 = Input tied to Vss<br>01111 = Input tied to RP15<br>•<br>•<br>•<br>00001 = Input tied to RP1<br>00000 = Input tied to RP0<br>Unimplemented: Read as '0<br>SDI1R<4:0>: Assign SPI1 D<br>11111 = Input tied to Vss<br>01111 = Input tied to RP15 | Unimplemented: Read as '0'<br>SCK1R<4:0>: Assign SPI1 Clock Input (S<br>11111 = Input tied to Vss<br>01111 = Input tied to RP15<br>•<br>•<br>•<br>00001 = Input tied to RP1<br>00000 = Input tied to RP0<br>Unimplemented: Read as '0'<br>SDI1R<4:0>: Assign SPI1 Data Input (SD<br>11111 = Input tied to Vss<br>01111 = Input tied to RP15<br>•<br>•<br>•<br>•<br>• | <pre>DR '1' = Bit is set '0' = Bit is cle Unimplemented: Read as '0' SCK1R&lt;4:0&gt;: Assign SPI1 Clock Input (SCK1IN) to the 11111 = Input tied to Vss 01111 = Input tied to RP15</pre> | DR       '1' = Bit is set       '0' = Bit is cleared         Unimplemented: Read as '0'         SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to the corresponding         1111 = Input tied to Vss         01111 = Input tied to RP15         •         00001 = Input tied to RP1         00000 = Input tied to RP0         Unimplemented: Read as '0'         SD11R<4:0>: Assign SPI1 Data Input (SDI1) to the corresponding RPr         1111 = Input tied to RP15         •         00001 = Input tied to RP1         00001 = Input tied to RP1         01111 = Input tied to RP15         •         •         00001 = Input tied to RP15 | DR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         Unimplemented: Read as '0'       SCK1R<4:0>: Assign SPI1 Clock Input (SCK1IN) to the corresponding RPn pin bits         11111 = Input tied to Vss       01111 = Input tied to RP15         •       •         00001 = Input tied to RP1         00000 = Input tied to RP0         Unimplemented: Read as '0'         SDI1R<4:0>: Assign SPI1 Data Input (SDI1) to the corresponding RPn pin bits         1111 = Input tied to Vss         01111 = Input tied to RP15         •         00001 = Input tied to RP1         00001 = Input tied to RP1         00001 = Input tied to RP15 |  |  |  |

| R/W-0             | R/W-0                                                                 | R/W-0                                                                                                      | U-0                                                          | U-0                                   | U-0             | U-0         | U-0   |  |

|-------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------------|-----------------|-------------|-------|--|

| FRMEN             | SPIFSD                                                                | FRMPOL                                                                                                     |                                                              | —                                     |                 | —           | _     |  |

| bit 15            |                                                                       |                                                                                                            |                                                              |                                       |                 |             | bit 8 |  |

| U-0               | U-0                                                                   | U-0                                                                                                        | U-0                                                          | U-0                                   | U-0             | R/W-0       | U-0   |  |

|                   |                                                                       |                                                                                                            |                                                              |                                       |                 | FRMDLY      |       |  |

| pit 7             |                                                                       |                                                                                                            |                                                              |                                       |                 | TRADET      | bit ( |  |

|                   |                                                                       |                                                                                                            |                                                              |                                       |                 |             |       |  |

| _egend:           |                                                                       |                                                                                                            |                                                              |                                       |                 |             |       |  |

| R = Readable      | e bit                                                                 | W = Writable I                                                                                             | oit                                                          | U = Unimplemented bit, read as '0'    |                 |             |       |  |

| n = Value at      | POR                                                                   | '1' = Bit is set                                                                                           |                                                              | '0' = Bit is cleared x = Bit is unkno |                 |             | own   |  |

| bit 15<br>bit 14  | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD</b> : Fran<br>1 = Frame syn | ned SPIx Supp<br>PIx support en<br>PIx support dis<br>ne Sync Pulse<br>nc pulse input (<br>nc pulse output | abled ( <del>SSx</del> p<br>abled<br>Direction Cor<br>slave) | in used as fram<br>ntrol bit          | e sync pulse in | put/output) |       |  |

| bit 13            |                                                                       | ame Sync Pulse                                                                                             | e Polarity bit                                               |                                       |                 |             |       |  |

|                   |                                                                       | nc pulse is activ                                                                                          |                                                              |                                       |                 |             |       |  |

| bit 12-2          | 0 = Frame sy                                                          |                                                                                                            | ve-low                                                       |                                       |                 |             |       |  |

| bit 12-2<br>bit 1 | 0 = Frame syn<br>Unimplemen<br>FRMDLY: Fra<br>1 = Frame syn           | nc pulse is activ                                                                                          | ve-low<br>)'<br>Edge Select<br>des with first                | bit clock                             |                 |             |       |  |

#### REGISTER 15-3: SPIxCON2: SPIx CONTROL REGISTER 2

| R/W-0         | U-0                                                                                                                                | R/W-0                                                                                                | U-0              | U-0                | R/W-0            | R/W-0           | R/W-0  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|------------------|--------------------|------------------|-----------------|--------|--|--|--|