#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                                  |

| Supplier Device Package    | 28-SOIC                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp202-e-so |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Pin Name                                               | Pin<br>Type              | Buffer<br>Type       | PPS                      | Description                                                                                                                                                                                                                                                        |

|--------------------------------------------------------|--------------------------|----------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AN0-AN9                                                | I                        | Analog               | No                       | Analog input channels.                                                                                                                                                                                                                                             |

| CLKI<br>CLKO                                           | I<br>O                   | ST/CMOS<br>—         | No<br>No                 | External clock source input. Always associated with OSC1 pin function.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal<br>Oscillator mode. Optionally functions as CLKO in RC and EC modes.<br>Always associated with OSC2 pin function. |

| OSC1<br>OSC2                                           | I<br>I/O                 | ST/CMOS              | No<br>No                 | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.<br>Oscillator crystal output. Connects to crystal or resonator in Crystal Oscilla tor mode. Optionally functions as CLKO in RC and EC modes.                                       |

| SOSCI<br>SOSCO                                         | I<br>O                   | ST/CMOS              | No<br>No                 | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.<br>32.768 kHz low-power oscillator crystal output.                                                                                                                                                  |

| CN0-CN7<br>CN11-CN15<br>CN21-CN24<br>CN27<br>CN29-CN30 | I                        | ST                   | No<br>No<br>No<br>No     | Change notification inputs.<br>Can be software programmed for internal weak pull-ups on all inputs.                                                                                                                                                                |

| IC1-IC2<br>IC7-IC8                                     | I                        | ST                   | Yes<br>Yes               | Capture inputs 1/2<br>Capture inputs 7/8                                                                                                                                                                                                                           |

| OCFA<br>OC1-OC2                                        | I<br>O                   | ST<br>—              | Yes<br>Yes               | Compare Fault A input (for Compare Channels 1 and 2).<br>Compare outputs 1 through 2.                                                                                                                                                                              |

| INT0<br>INT1<br>INT2                                   | <br> <br>                | ST<br>ST<br>ST       | No<br>Yes<br>Yes         | External interrupt 0.<br>External interrupt 1.<br>External interrupt 2.                                                                                                                                                                                            |

| RA0-RA4                                                | I/O                      | ST                   | No                       | PORTA is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| RB0-RB15                                               | I/O                      | ST                   | No                       | PORTB is a bidirectional I/O port.                                                                                                                                                                                                                                 |

| T1CK<br>T2CK<br>T3CK                                   |                          | ST<br>ST<br>ST       | No<br>Yes<br>Yes         | Timer1 external clock input.<br>Timer2 external clock input.<br>Timer3 external clock input.                                                                                                                                                                       |

| U1CTS<br>U1RTS<br>U1RX<br>U1TX                         | <br>  0<br>  0           | ST<br>—<br>ST<br>—   | Yes<br>Yes<br>Yes<br>Yes | UART1 clear to send.<br>UART1 ready to send.<br>UART1 receive.<br>UART1 transmit.                                                                                                                                                                                  |

| SCK1<br>SDI1<br>SDO1<br>SS1                            | I/O<br>I<br>O<br>I/O     | ST<br>ST<br>         | Yes<br>Yes<br>Yes<br>Yes | Synchronous serial clock input/output for SPI1.<br>SPI1 data in.<br>SPI1 data out.<br>SPI1 slave synchronization or frame pulse I/O.                                                                                                                               |

| SCL1<br>SDA1<br>ASCL1<br>ASDA1                         | I/O<br>I/O<br>I/O<br>I/O | ST<br>ST<br>ST<br>ST | No<br>No<br>No<br>No     | Synchronous serial clock input/output for I2C1.<br>Synchronous serial data input/output for I2C1.<br>Alternate synchronous serial clock input/output for I2C1.<br>Alternate synchronous serial data input/output for I2C1.                                         |

| TMS<br>TCK<br>TDI<br>TDO                               | <br> <br> <br>0          | ST<br>ST<br>ST<br>—  | No<br>No<br>No<br>No     | JTAG Test mode select pin.<br>JTAG test clock input pin.<br>JTAG test data input pin.<br>JTAG test data output pin.                                                                                                                                                |

| S                                                      | Γ = Schn                 |                      | nput wit                 | apput or outputAnalog = Analog inputP = Powerh CMOS levelsO = OutputI = Input                                                                                                                                                                                      |

TABLE 1-1: **PINOUT I/O DESCRIPTIONS**

ST = Schmitt Trigger input with CMOS levels PPS = Peripheral Pin Select

| TABLE 4-1: | <b>CPU CORE REGISTERS MAP</b> |

|------------|-------------------------------|

|------------|-------------------------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7         | Bit 6  | Bit 5     | Bit 4          | Bit 3        | Bit 2       | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|---------|---------------|---------------|--------|-----------|----------------|--------------|-------------|---------|-------|---------------|

| WREG0    | 0000        |        |        |        |        |        |        |         | Working Re    | gister 0      |        |           |                |              |             |         |       | 0000          |

| WREG1    | 0002        |        |        |        |        |        |        |         | Working Re    | gister 1      |        |           |                |              |             |         |       | 0000          |

| WREG2    | 0004        |        |        |        |        |        |        |         | Working Re    | gister 2      |        |           |                |              |             |         |       | 0000          |

| WREG3    | 0006        |        |        |        |        |        |        |         | Working Re    | gister 3      |        |           |                |              |             |         |       | 0000          |

| WREG4    | 0008        |        |        |        |        |        |        |         | Working Re    | gister 4      |        |           |                |              |             |         |       | 0000          |

| WREG5    | 000A        |        |        |        |        |        |        |         | Working Re    | gister 5      |        |           |                |              |             |         |       | 0000          |

| WREG6    | 000C        |        |        |        |        |        |        |         | Working Re    | gister 6      |        |           |                |              |             |         |       | 0000          |

| WREG7    | 000E        |        |        |        |        |        |        |         | Working Re    | gister 7      |        |           |                |              |             |         |       | 0000          |

| WREG8    | 0010        |        |        |        |        |        |        |         | Working Re    | gister 8      |        |           |                |              |             |         |       | 0000          |

| WREG9    | 0012        |        |        |        |        |        |        |         | Working Re    | gister 9      |        |           |                |              |             |         |       | 0000          |

| WREG10   | 0014        |        |        |        |        |        |        |         | Working Re    | gister 10     |        |           |                |              |             |         |       | 0000          |

| WREG11   | 0016        |        |        |        |        |        |        |         | Working Re    | gister 11     |        |           |                |              |             |         |       | 0000          |

| WREG12   | 0018        |        |        |        |        |        |        |         | Working Re    | gister 12     |        |           |                |              |             |         |       | 0000          |

| WREG13   | 001A        |        |        |        |        |        |        |         | Working Re    | gister 13     |        |           |                |              |             |         |       | 0000          |

| WREG14   | 001C        |        |        |        |        |        |        | ,       | Working Re    | gister 14     |        |           |                |              |             |         |       | 0000          |

| WREG15   | 001E        |        |        |        |        |        |        |         | Working Re    | gister 15     |        |           |                |              |             |         |       | 0800          |

| SPLIM    | 0020        |        |        |        |        |        |        | Stad    | ck Pointer Li | mit Register  | •      |           |                |              |             |         |       | xxxx          |

| ACCAL    | 0022        |        |        |        |        |        |        | Accum   | ulator A Low  | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCAH    | 0024        |        |        |        |        |        |        | Accum   | ulator A High | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCAU    | 0026        |        |        |        |        |        |        | Accumu  | lator A Uppe  | er Word Reg   | jister |           |                |              |             |         |       | 0000          |

| ACCBL    | 0028        |        |        |        |        |        |        | Accum   | ulator B Low  | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCBH    | 002A        |        |        |        |        |        |        | Accum   | ulator B High | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCBU    | 002C        |        |        |        |        |        |        | Accumu  | lator B Uppe  | er Word Reg   | jister |           |                |              |             |         |       | 0000          |

| PCL      | 002E        |        |        |        |        |        |        | Program | Counter Lo    | w Word Reg    | gister |           |                |              |             |         |       | 0000          |

| PCH      | 0030        | —      | _      | —      | _      | _      | _      | _       | _             |               |        | Progra    | m Counter      | High Byte R  | legister    |         |       | 0000          |

| TBLPAG   | 0032        | —      | —      | _      | —      | _      | _      | _       | —             |               |        | Table F   | Page Addre     | ss Pointer R | Register    |         |       | 0000          |

| PSVPAG   | 0034        | _      | _      | _      | _      | _      | _      | -       | _             |               | Progra | am Memory | v Visibility P | age Address  | s Pointer R | egister |       | 0000          |

| RCOUNT   | 0036        |        |        |        |        |        |        | Repe    | at Loop Cou   | inter Registe | er     |           |                |              |             |         |       | xxxx          |

| DCOUNT   | 0038        |        |        |        |        |        |        |         | DCOUNT        | <15:0>        |        |           |                |              |             |         |       | xxxx          |

| DOSTARTL | 003A        |        |        |        |        |        |        | DOS     | TARTL<15:     | 1>            |        |           |                |              |             |         | 0     | xxxx          |

| DOSTARTH | 003C        | _      | _      | _      | _      | _      | _      | _       | _             | —             | _      |           |                | DOSTAF       | RTH<5:0>    |         |       | 00xx          |

| DOENDL   | 003E        |        |        |        |        |        |        | DOE     | NDL<15:1      | >             |        |           |                |              |             |         | 0     | xxxx          |

| DOENDH   | 0040        | _      | —      | _      | —      | —      | —      | _       | _             | _             | —      |           |                | DOE          | NDH         |         |       | 00xx          |

| SR       | 0042        | OA     | OB     | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2          | IPL1   | IPL0      | RA             | N            | OV          | Z       | С     | 0000          |

| CORCON   | 0044        | _      | —      | _      | US     | EDT    |        | DL<2:0> |               | SATA          | SATB   | SATDW     | ACCSAT         | IPL3         | PSV         | RND     | IF    | 0020          |

| MODCON   | 0046        | XMODEN | YMODEN | _      | _      |        | BWN    | /<3:0>  |               |               | YWM    | <3:0>     |                |              | XWN         | 1<3:0>  |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|--------|-------------------------------------|--------|--------|--------|--------|-------|----------|----------|-------|-------|-------|-------|-------|-------|-------|---------------|

| XMODSRT  | 0048        |        |                                     |        |        |        |        | >     | (S<15:1> |          |       |       |       |       |       |       | 0     | xxxx          |

| XMODEND  | 004A        |        |                                     |        |        |        |        | >     | (E<15:1> |          |       |       |       |       |       |       | 1     | xxxx          |

| YMODSRT  | 004C        |        |                                     |        |        |        |        | ١     | /S<15:1> |          |       |       |       |       |       |       | 0     | xxxx          |

| YMODEND  | 004E        |        |                                     |        |        |        |        | ١     | ′E<15:1> |          |       |       |       |       |       |       | 1     | xxxx          |

| XBREV    | 0050        | BREN   |                                     |        |        |        |        |       | >        | (B<14:0> |       |       |       |       |       |       |       | xxxx          |

| DISICNT  | 0052        | —      | Disable Interrupts Counter Register |        |        |        |        |       |          |          |       | xxxx  |       |       |       |       |       |               |

gend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ12GP202

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8   | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|--------|-------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  |        |       |         | CN7IE   | CN6IE   | CN5IE   | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE   | 0000          |

| CNEN2       | 0062        | _       | CN30IE  | CN29IE  |         | CN27IE  |        | _     | CN24IE  | CN23IE  | CN22IE  | CN21IE  |        | _      | _      | _      | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE |        | _     | _       | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE  | 0000          |

| CNPU2       | 006A        | _       | CN30PUE | CN29PUE | _       | CN27PUE | _      |       | CN24PUE | CN23PUE | CN22PUE | CN21PUE | _      |        | _      | _      | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJ12GP201

| SFF<br>Nan |    | SFR<br>Addr | Bit 15 | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10 | Bit 9 | Bit 8 | Bit 7   | Bit 6   | Bit 5   | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|------------|----|-------------|--------|---------|---------|---------|---------|--------|-------|-------|---------|---------|---------|--------|--------|--------|--------|--------|---------------|

| CNE        | N1 | 0060        | _      | _       | _       | CN12IE  | CN11IE  | _      |       | _     | _       |         | CN5IE   | CN4IE  | CN3IE  | CN2IE  | CN1IE  | CN0IE  | 0000          |

| CNE        | N2 | 0062        | _      | CN30IE  | CN29IE  | _       | _       | _      |       | _     | CN23IE  | CN22IE  | CN21IE  | -      | _      | _      | _      | -      | 0000          |

| CNP        | U1 | 0068        | _      | —       | _       | CN12PUE | CN11PUE | _      | _     | _     | _       | _       | CN5PUE  | CN4PUE | CN3PUE | CN2PUE | CN1PUE | CN0PUE | 0000          |

| CNP        | U2 | 006A        | _      | CN30PUE | CN29PUE | _       | _       | _      | _     | _     | CN23PUE | CN22PUE | CN21PUE | _      | _      |        |        |        | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| TABLE 4-4: | INTERRUPT CONTROLLER REGISTER MAP |

|------------|-----------------------------------|

|------------|-----------------------------------|

|             |             |        |        | ••••••     |         |         |        |            |       |          |         |             | -       | -         |        |            |               |               |

|-------------|-------------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|-----------|--------|------------|---------------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3     | Bit 2  | Bit 1      | Bit 0         | All<br>Resets |

| INTCON1     | 0080        | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | -           | MATHERR | ADDRERR   | STKERR | OSCFAIL    | _             | 0000          |

| INTCON2     | 0082        | ALTIVT | DISI   | _          | _       | _       | _      | _          | _     | _        | _       | _           | _       | _         | INT2EP | INT1EP     | INT0EP        | 0000          |

| IFS0        | 0084        | —      | _      | AD1IF      | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    | T3IF  | T2IF     | OC2IF   | IC2IF       | —       | T1IF      | OC1IF  | IC1IF      | <b>INT0IF</b> | 0000          |

| IFS1        | 0086        | _      |        | INT2IF     | _       | _       | _      | _          | _     | IC8IF    | IC7IF   | _           | INT1IF  | CNIF      | _      | MI2C1IF    | SI2C1IF       | 0000          |

| IFS4        | 008C        | —      | _      | _          | _       | _       | -      | —          |       | —        | _       | _           | —       | _         |        | U1EIF      | _             | 0000          |

| IEC0        | 0094        | —      | _      | AD1IE      | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | T3IE  | T2IE     | OC2IE   | IC2IE       | —       | T1IE      | OC1IE  | IC1IE      | INT0IE        | 0000          |

| IEC1        | 0096        | —      | _      | INT2IE     | _       | _       | -      | —          |       | IC8IE    | IC7IE   | _           | INT1IE  | CNIE      |        | MI2C1IE    | SI2C1IE       | 0000          |

| IEC4        | 009C        |        | _      | _          | _       |         |        | —          |       | —        | _       |             | —       | _         |        | U1EIE      |               | 0000          |

| IPC0        | 00A4        |        |        | T1IP<2:0>  | •       |         | Ú      | OC1IP<2:(  | )>    | —        |         | IC1IP<2:0>  |         | _         | 11     | NT0IP<2:0> | •             | 4444          |

| IPC1        | 00A6        |        |        | T2IP<2:0>  | •       |         | Ú      | OC2IP<2:(  | )>    | —        |         | IC2IP<2:0>  |         | _         |        |            |               | 4440          |

| IPC2        | 00A8        | _      | ι      | J1RXIP<2:( | )>      |         |        | SPI1IP<2:0 | )>    | —        | :       | SPI1EIP<2:0 | >       | _         |        | T3IP<2:0>  |               | 4444          |

| IPC3        | 00AA        |        | _      | _          | _       |         |        | —          |       | —        |         | AD1IP<2:0>  | >       | _         | U      | 1TXIP<2:0  | >             | 0044          |

| IPC4        | 00AC        | _      |        | CNIP<2:0>  | >       |         |        | _          |       | —        |         | MI2C1IP<2:0 | )>      | _         | SI     | 2C1IP<2:0  | >             | 4044          |

| IPC5        | 00AE        | —      |        | IC8IP<2:0> | >       | —       |        | IC7IP<2:0  | >     | —        | —       | -           | —       | —         | 11     | NT1IP<2:0> | •             | 4404          |

| IPC7        | 00B2        |        | _      | _          | _       |         |        | —          |       | —        |         | INT2IP<2:0  | >       | _         |        |            |               | 0040          |

| IPC16       | 00C4        | _      | _      | _          | _       | _       |        | _          |       | —        |         | U1EIP<2:0>  | >       | _         | _      |            | _             | 0040          |

| INTTREG     | 00E0        | _      | _      | _          | _       |         | ILR<3  | :0>>       |       | _        |         |             | VE      | CNUM<6:0> |        |            |               | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# REGISTER 5-1: NVMCON: FLASH MEMORY CONTROL REGISTER

| R/SO-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | U-0 | U-0 | U-0 | U-0 | U-0   |

|-----------------------|----------------------|----------------------|-----|-----|-----|-----|-------|

| WR                    | WREN                 | WRERR                | —   | —   | —   | —   | —     |

| bit 15                |                      |                      |     |     |     |     | bit 8 |

| U-0   | R/W-0 <sup>(1)</sup> | U-0 | U-0 | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> | R/W-0 <sup>(1)</sup> |

|-------|----------------------|-----|-----|----------------------|----------------------|----------------------|----------------------|

| _     | ERASE                | —   | —   |                      | NVMOF                | 9<3:0> <b>(2)</b>    |                      |

| bit 7 |                      |     |     |                      |                      |                      | bit 0                |

| Legend:           | SO = Settable only bit |                             |                    |

|-------------------|------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit       | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15   | WR: Write Control bit                                                                               |

|----------|-----------------------------------------------------------------------------------------------------|

|          | 1 = Initiates a Flash memory program or erase operation. The operation is self-timed and the bit is |

|          | cleared by hardware when operation is complete.                                                     |

|          | 0 = Program or erase operation is complete and inactive                                             |

| bit 14   | WREN: Write Enable bit                                                                              |

|          | 1 = Enable Flash program/erase operations                                                           |

|          | 0 = Inhibit Flash program/erase operations                                                          |

| bit 13   | WRERR: Write Sequence Error Flag bit                                                                |

|          | 1 = An improper program or erase sequence attempt or termination has occurred (bit is set           |

|          | automatically on any set attempt of the WR bit)                                                     |

|          | 0 = The program or erase operation completed normally                                               |

| bit 12-7 | Unimplemented: Read as '0'                                                                          |

| bit 6    | ERASE: Erase/Program Enable bit                                                                     |

|          | 1 = Perform the erase operation specified by NVMOP<3:0> on the next WR command                      |

|          | 0 = Perform the program operation specified by NVMOP<3:0> on the next WR command                    |

| bit 5-4  | Unimplemented: Read as '0'                                                                          |

| bit 3-0  | NVMOP<3:0>: NVM Operation Select bits <sup>(2)</sup>                                                |

|          | If ERASE = 1:                                                                                       |

|          | 1111 = Memory bulk erase operation                                                                  |

|          | 1101 = Erase General Segment                                                                        |

|          | 1100 = Erase Secure Segment                                                                         |

|          | 0011 = No operation                                                                                 |

|          | 0010 = Memory page erase operation<br>0001 = No operation                                           |

|          | 0000 = Erase a single Configuration register byte                                                   |

|          |                                                                                                     |

|          | If ERASE = 0:                                                                                       |

|          | 1111 = No operation                                                                                 |

|          | 1101 = No operation<br>1100 = No operation                                                          |

|          | 0011 = Memory word program operation                                                                |

|          | 0010 = No operation                                                                                 |

|          | 0001 = Memory row program operation                                                                 |

|          | 0000 = Program a single Configuration register byte                                                 |

| •• · ·   |                                                                                                     |

| Note 1:  | These bits can only be Reset on POR.                                                                |

# 2: All other combinations of NVMOP<3:0> are unimplemented.

#### 6.2 POR

A POR circuit ensures the device is reset from poweron. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 22.0 "Electrical Characteristics" for details.

The POR status bit (POR) in the Reset Control register (RCON<0>) is set to indicate the POR.

#### 6.3 BOR and PWRT

The on-chip regulator has a BOR circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

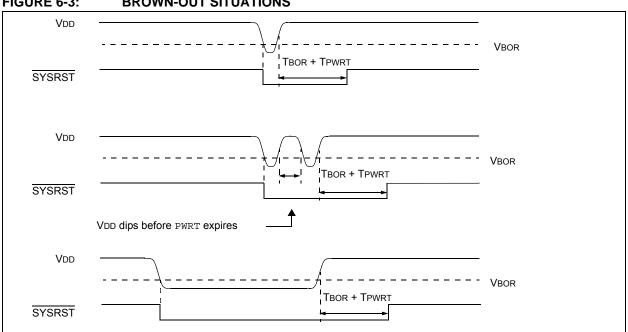

FIGURE 6-3: **BROWN-OUT SITUATIONS**  The BOR status bit (BOR) in the Reset Control register (RCON<1>) is set to indicate the BOR.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provides eight settings (from 0 ms to 128 ms). Refer to Section 19.0 "Special Features" for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point.

# 7.0 INTERRUPT CONTROLLER

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Interrupts" (DS70184) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Microchip dsPIC33FJ12GP201/202 interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the dsPIC33FJ12GP201/202 CPU. It has the following features:

- Up to eight processor exceptions and software traps

- · Seven user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- · Fixed interrupt entry and return latencies

# 7.1 Interrupt Vector Table

The Interrupt Vector Table is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of eight nonmaskable trap vectors, plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this priority is linked to their position in the vector table. Lower addresses generally have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

The dsPIC33FJ12GP201/202 devices implement up to 21 unique interrupts and four nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

## 7.1.1 ALTERNATE INTERRUPT VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a way to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications to facilitate evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

# 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The dsPIC33FJ12GP201/202 device clears its registers in response to a Reset, which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. The user application can use a GOTO instruction at the Reset address that redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1 (CONTINUED)

- bit 2

STKERR: Stack Error Trap Status bit

1 = Stack error trap has occurred

0 = Stack error trap has not occurred

bit 1

OSCFAIL: Oscillator Failure Trap Status bit

1 = Oscillator failure trap has occurred

0 = Oscillator failure trap has not occurred

- bit 0 Unimplemented: Read as '0'

| REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER <sup>(2)</sup> |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| R/W-0         | R/W-0                                                                                                                                  | R/W-1                                                                                 | R/W-1          | R/W-0                              | R/W-0           | R/W-0              | R/W-0      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------|------------------------------------|-----------------|--------------------|------------|

| ROI           |                                                                                                                                        | DOZE<2:0>                                                                             |                | DOZEN <sup>(1)</sup>               |                 | FRCDIV<2:0>        |            |

| bit 15        | •                                                                                                                                      |                                                                                       |                |                                    |                 |                    | bit 8      |

| R/W-0         | R/W-1                                                                                                                                  | U-0                                                                                   | R/W-0          | R/W-0                              |                 | R/W-0              | R/W-0      |

|               |                                                                                                                                        | 0-0                                                                                   | R/W-U          | R/W-0                              | R/W-0           |                    | R/W-U      |

| bit 7         | OST<1:0>                                                                                                                               | _                                                                                     |                |                                    | PLLPRE<4:0      | >                  | bit (      |

| DIL 7         |                                                                                                                                        |                                                                                       |                |                                    |                 |                    | bit (      |

| Legend:       |                                                                                                                                        | y = Value set                                                                         | from Configu   | ration bits on PC                  | )R              |                    |            |

| R = Readabl   | e bit                                                                                                                                  | W = Writable                                                                          | bit            | U = Unimplem                       | ented bit, read | d as '0'           |            |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set                                                                      |                | '0' = Bit is clea                  | ared            | x = Bit is unkn    | iown       |

| bit 15        | 1 = Interrupt                                                                                                                          | r on Interrupt bi<br>s will clear the I<br>s have no effec                            | DOZEN bit ar   | nd the processor<br>EN bit         | clock/periphe   | ral clock ratio is | set to 1:1 |

| bit 14-12     | DOZE<2:0>:<br>111 = FcY/12<br>110 = FcY/62<br>101 = FcY/32<br>100 = FcY/16<br>011 = FcY/8<br>010 = FcY/4<br>001 = FcY/2<br>000 = FcY/1 | 4<br>2<br>3                                                                           | ck Reduction   | Select bits                        |                 |                    |            |

| bit 11        | 1 = DOZE<2                                                                                                                             | ZE Mode Enabl<br>2:0> field specifi<br>or clock/periphe                               | es the ratio b | etween the peri<br>o forced to 1:1 | pheral clocks a | and the process    | or clocks  |

| bit 10-8      | 111 = FRC d<br>110 = FRC d<br>101 = FRC d<br>100 = FRC d<br>011 = FRC d<br>010 = FRC d<br>001 = FRC d                                  | ivide by 256<br>ivide by 64<br>ivide by 32<br>ivide by 16<br>ivide by 8<br>ivide by 4 |                | r Postscaler bits                  |                 |                    |            |

| bit 7-6       | PLLPOST<1<br>11 = Output/8<br>10 = Reserve<br>01 = Output/2<br>00 = Output/2                                                           | 3<br>ed<br>4 (default)                                                                | Output Divide  | er Select bits (als                | o denoted as    | 'N2', PLL posts    | caler)     |

| bit 5         | Unimplemen                                                                                                                             | ted: Read as '                                                                        | 0'             |                                    |                 |                    |            |

| bit 4-0       | PLLPRE<4:0<br>11111 = Inpu<br>00001 = Inpu                                                                                             | ut/33                                                                                 | Detector Inpu  | t Divider bits (al                 | so denoted as   | 'N1', PLL presc    | caler)     |

|               | 00001 = Inpt<br>00000 = Inpt                                                                                                           |                                                                                       |                |                                    |                 |                    |            |

- Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register is reset only on a Power-on Reset (POR).

| U-0           | U-0              | U-0              | U-0            | U-0              | U-0              | U-0            | R/W-0 <sup>(1)</sup> |

|---------------|------------------|------------------|----------------|------------------|------------------|----------------|----------------------|

|               | —                | —                | —              | —                | —                | —              | PLLDIV<8>            |

| bit 15        |                  |                  |                |                  |                  |                | bit 8                |

|               |                  |                  |                |                  |                  |                |                      |

| R/W-0         | R/W-0            | R/W-1            | R/W-1          | R/W-0            | R/W-0            | R/W-0          | R/W-0                |

|               |                  |                  | PLLD           | IV<7:0>          |                  |                |                      |

| bit 7         |                  |                  |                |                  |                  |                | bit 0                |

|               |                  |                  |                |                  |                  |                |                      |

| Legend:       |                  |                  |                |                  |                  |                |                      |

| R = Readabl   | e bit            | W = Writable     | bit            | U = Unimpler     | nented bit, read | as '0'         |                      |

| -n = Value at | POR              | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unk | nown                 |

|               |                  |                  |                |                  |                  |                |                      |

| bit 15-9      | Unimplemen       | ted: Read as '   | 0'             |                  |                  |                |                      |

| bit 8-0       | PLLDIV<8:0>      | PLL Feedbac      | k Divisor bits | (also denoted    | as 'M', PLL mul  | tiplier)       |                      |

|               | 111111111 =      | = 513            |                |                  |                  |                |                      |

|               | •                |                  |                |                  |                  |                |                      |

|               | •                |                  |                |                  |                  |                |                      |

|               | •                |                  |                |                  |                  |                |                      |

|               | 000110000 =      | = 50 (default)   |                |                  |                  |                |                      |

|               | •                |                  |                |                  |                  |                |                      |

|               | •                |                  |                |                  |                  |                |                      |

|               | •<br>000000010 = | - 1              |                |                  |                  |                |                      |

|               | 000000010 =      |                  |                |                  |                  |                |                      |

|               | 000000000        |                  |                |                  |                  |                |                      |

|               |                  |                  |                |                  |                  |                |                      |

# REGISTER 8-3: PLLFBD: PLL FEEDBACK DIVISOR REGISTER<sup>(1)</sup>

Note 1: This register is reset only on a Power-on Reset (POR).

# 12.0 TIMER2/3 FEATURE

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 11. "Timers" (DS70205) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Timer2/3 feature has 32-bit timers that can also be configured as two independent 16-bit timers with selectable operating modes.

As a 32-bit timer, the Timer2/3 feature permits operation in three modes:

- Two Independent 16-bit timers (Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- Single 32-bit timer (Timer2/3)

- Single 32-bit synchronous counter (Timer2/3)

- The Timer2/3 feature also supports:

- Timer gate operation

- Selectable prescaler settings

- Timer operation during Idle and Sleep modes

- · Interrupt on a 32-bit Period register match

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC1 Event Trigger (Timer2/3 only)

Individually, all eight of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the event trigger. The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON and T3CON registers. The T2CON register is shown in generic form in Register 12-1. The T3CON register is shown in Register 12-2.

For 32-bit timer/counter operation, Timer2 is the lsw and Timer3 is the msw of the 32-bit timers.

Note: For 32-bit operation, T3CON control bits are ignored. Only T2CON control bit is used for setup and control. Timer2 clock and gate inputs are used for the 32-bit timer modules, but an interrupt is generated with the Timer3 interrupt flags.

# 12.1 32-bit Operation

To configure the Timer2/3 feature for 32-bit operation:

- 1. Set the corresponding T32 control bit.

- 2. Select the prescaler ratio for Timer2 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the corresponding TCS and TGATE bits.

- 4. Load the timer period value. PR3 contains the msw of the value, while PR2 contains the lsw.

- 5. If interrupts are required, set the interrupt enable bit, T3IE. Use the priority bits T3IP<2:0> to set the interrupt priority. While Timer2 controls the timer, the interrupt appears as a Timer3 interrupt.

- 6. Set the corresponding TON bit.

The timer value at any point is stored in the register pair TMR3:TMR2. TMR3 always contains the msw of the count, while TMR2 contains the lsw.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit corresponding to that timer.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE. Use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit.

## REGISTER 18-4: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 2-1

bit 0

# CH123NA<1:0>: Channel 1, 2, 3 Negative Input Select for Sample A bits dsPIC33FJ12GP201 devices only:

If AD12B = 1:

- 11 = Reserved

- 10 = Reserved

- 01 = Reserved

- 00 = Reserved

### If AD12B = 0:

- 11 = Reserved

- 10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is not connected

- 01 = CH1, CH2, CH3 negative input is VREF-

- 00 = CH1, CH2, CH3 negative input is VREF-

### dsPIC33FJ12GP202 devices only:

If AD12B = 1: 11 = Reserved

- 10 = Reserved

- 01 = Reserved

- 00 = Reserved

### If AD12B = 0:

11 = CH1 negative input is AN9, CH2 and CH3 negative inputs are not connected 10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8 01 = CH1, CH2, CH3 negative input is VREF-00 = CH1, CH2, CH3 negative input is VREF-

CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit

### dsPIC33FJ12GP201 devices only:

<u>If AD12B = 1:</u> 1 = Reserved 0 = Reserved

## If AD12B = 0:

1 = CH1 positive input is AN3, CH2 and CH3 positive inputs are not connected

0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2

## dsPIC33FJ12GP202 devices only:

If AD12B = 1:

1 = Reserved

0 = Reserved

If AD12B = 0:

1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5 0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2

| IABL               | E 20-2:              | INSTRUCTION SET OVERVIEW (CONTINUED) |                       |                                                                                                     |   |                |                            |  |  |  |  |  |  |  |

|--------------------|----------------------|--------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|---|----------------|----------------------------|--|--|--|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                      | Assembly Syntax       | Description                                                                                         |   | # of<br>Cycles | Status Flags<br>Affected   |  |  |  |  |  |  |  |

| 10                 | BTSC                 | BTSC                                 | f,#bit4               | Bit Test f, Skip if Clear                                                                           | 1 | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |  |

|                    |                      | BTSC                                 | Ws,#bit4              | Bit Test Ws, Skip if Clear                                                                          | 1 | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |  |

| 11                 | BTSS                 | BTSS                                 | f,#bit4               | Bit Test f, Skip if Set                                                                             | 1 | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |  |

|                    |                      | BTSS                                 | Ws,#bit4              | Bit Test Ws, Skip if Set                                                                            | 1 | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |  |

| 12                 | BTST                 | BTST                                 | f,#bit4               | Bit Test f                                                                                          | 1 | 1              | Z                          |  |  |  |  |  |  |  |

|                    |                      | BTST.C                               | Ws,#bit4              | Bit Test Ws to C                                                                                    | 1 | 1              | С                          |  |  |  |  |  |  |  |

|                    |                      | BTST.Z                               | Ws,#bit4              | Bit Test Ws to Z                                                                                    | 1 | 1              | Z                          |  |  |  |  |  |  |  |

|                    |                      | BTST.C                               | Ws,Wb                 | Bit Test Ws <wb> to C</wb>                                                                          | 1 | 1              | С                          |  |  |  |  |  |  |  |

|                    |                      | BTST.Z                               | Ws,Wb                 | Bit Test Ws <wb> to Z</wb>                                                                          | 1 | 1              | Z                          |  |  |  |  |  |  |  |

| 13                 | BTSTS                | BTSTS                                | f,#bit4               | Bit Test then Set f                                                                                 | 1 | 1              | Z                          |  |  |  |  |  |  |  |

|                    |                      | BTSTS.C                              | Ws,#bit4              | Bit Test Ws to C, then Set                                                                          | 1 | 1              | С                          |  |  |  |  |  |  |  |

|                    |                      | BTSTS.Z                              | Ws,#bit4              | Bit Test Ws to Z, then Set                                                                          | 1 | 1              | Z                          |  |  |  |  |  |  |  |

| 14                 | CALL                 | CALL                                 | lit23                 | Call subroutine                                                                                     | 2 | 2              | None                       |  |  |  |  |  |  |  |

|                    |                      | CALL                                 | Wn                    | Call indirect subroutine                                                                            | 1 | 2              | None                       |  |  |  |  |  |  |  |

| 15                 | CLR                  | CLR                                  | f                     | f = 0x0000                                                                                          | 1 | 1              | None                       |  |  |  |  |  |  |  |

|                    |                      | CLR                                  | WREG                  | WREG = 0x0000                                                                                       | 1 | 1              | None                       |  |  |  |  |  |  |  |

|                    |                      | CLR                                  | Ws                    | Ws = 0x0000                                                                                         | 1 | 1              | None                       |  |  |  |  |  |  |  |

|                    |                      | CLR                                  | Acc,Wx,Wxd,Wy,Wyd,AWB | Clear Accumulator                                                                                   | 1 | 1              | OA,OB,SA,SB                |  |  |  |  |  |  |  |

| 16                 | CLRWDT               | CLRWDT                               |                       | Clear Watchdog Timer                                                                                | 1 | 1              | WDTO,Sleep                 |  |  |  |  |  |  |  |

| 17                 | СОМ                  | СОМ                                  | f                     | f = f                                                                                               | 1 | 1              | N,Z                        |  |  |  |  |  |  |  |

|                    |                      | СОМ                                  | f,WREG                | WREG = f                                                                                            | 1 | 1              | N,Z                        |  |  |  |  |  |  |  |

|                    |                      | COM                                  | Ws,Wd                 | $Wd = \overline{Ws}$                                                                                | 1 | 1              | N,Z                        |  |  |  |  |  |  |  |

| 18                 | СР                   | CP                                   | f                     | Compare f with WREG                                                                                 | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

| 10                 | 0F                   | CP                                   |                       | Compare Wb with lit5                                                                                | 1 | 1              |                            |  |  |  |  |  |  |  |

|                    |                      |                                      | Wb,#lit5              |                                                                                                     | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

| 19                 | CP0                  | CP                                   | Wb,Ws                 | Compare Wb with Ws (Wb – Ws)                                                                        |   | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

| 19                 | CFU                  | CP0                                  | f                     | Compare f with 0x0000                                                                               | 1 |                | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

| 00                 | 000                  | CP0                                  | Ws                    | Compare Ws with 0x0000                                                                              | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

| 20                 | СРВ                  | CPB                                  | f                     | Compare f with WREG, with Borrow                                                                    | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

|                    |                      | CPB<br>CPB                           | Wb,#lit5<br>Wb,Ws     | Compare Wb with lit5, with Borrow<br>Compare Wb with Ws, with Borrow<br>(Wb – Ws – $\overline{C}$ ) | 1 | 1              | C,DC,N,OV,Z<br>C,DC,N,OV,Z |  |  |  |  |  |  |  |

| 21                 | CPSEQ                | CPSEQ                                | Wb, Wn                | Compare Wb with Wn, skip if =                                                                       | 1 | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |  |

| 22                 | CPSGT                | CPSGT                                | Wb, Wn                | Compare Wb with Wn, skip if >                                                                       | 1 | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |  |

| 23                 | CPSLT                | CPSLT                                | Wb, Wn                | Compare Wb with Wn, skip if <                                                                       | 1 | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |  |

| 24                 | CPSNE                | CPSNE                                | Wb, Wn                | Compare Wb with Wn, skip if ≠                                                                       | 1 | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |  |

| 25                 | DAW                  | DAW                                  | Wn                    | Wn = decimal adjust Wn                                                                              | 1 | 1              | С                          |  |  |  |  |  |  |  |

| 26                 | DEC                  | DEC                                  | f                     | f = f - 1                                                                                           | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

|                    |                      | DEC                                  | f,WREG                | WREG = f – 1                                                                                        | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

|                    |                      | DEC                                  | Ws,Wd                 | Wd = Ws - 1                                                                                         | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

| 27                 | DEC2                 | DEC2                                 | f                     | f = f - 2                                                                                           | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

|                    |                      | DEC2                                 | f,WREG                | WREG = f – 2                                                                                        | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

|                    |                      | DEC2                                 | Ws,Wd                 | Wd = Ws - 2                                                                                         | 1 | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |  |

| 28                 | DISI                 | DISI                                 | #lit14                | Disable Interrupts for k instruction cycles                                                         | 1 | 1              | None                       |  |  |  |  |  |  |  |

# TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

# 22.1 DC Characteristics

| Characteristic | VDD Range  | Temp Range      | Max MIPS             |

|----------------|------------|-----------------|----------------------|

|                | (in Volts) | (in °C)         | dsPIC33FJ12GP201/202 |

|                | 3.0-3.6V   | -40°C to +85°C  | 40                   |

|                | 3.0-3.6V   | -40°C to +125°C | 40                   |

# TABLE 22-1: OPERATING MIPS VS. VOLTAGE

# TABLE 22-2: THERMAL OPERATING CONDITIONS

| Rating                                                                                      | Symbol | Min | Тур         | Max  | Unit |

|---------------------------------------------------------------------------------------------|--------|-----|-------------|------|------|

| Industrial Temperature Devices                                                              |        |     |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40 | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40 | —           | +85  | °C   |

| Extended Temperature Devices                                                                |        |     |             |      |      |

| Operating Junction Temperature Range                                                        | TJ     | -40 | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                         | TA     | -40 | —           | +125 | °C   |

| Power Dissipation:<br>Internal chip power dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$ | PD     | I   | Pint + Pi/c | D    | W    |

| I/O Pin Power Dissipation:<br>$I/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$     |        |     |             |      |      |

| Maximum Allowed Power Dissipation                                                           | PDMAX  | (   | TJ – ΤΑ)/θ. | IA   | W    |

# TABLE 22-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristic                           | Symbol | Тур | Max | Unit | Notes |

|------------------------------------------|--------|-----|-----|------|-------|

| Package Thermal Resistance, 18-pin PDIP  | θja    | 45  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SPDIP | θја    | 45  | —   | °C/W | 1     |

| Package Thermal Resistance, 18-pin SOIC  | θја    | 60  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SOIC  | θја    | 50  | _   | °C/W | 1     |

| Package Thermal Resistance, 28-pin SSOP  | θја    | 71  | —   | °C/W | 1     |

| Package Thermal Resistance, 28-pin QFN   | θја    | 35  | —   | °C/W | 1     |

Note 1: Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHA       | RACTER | ISTICS                                                                         | (unless            | otherwi            | tating Conditions: 3.0V to 3.6V<br>vise stated)<br>perature $-40^{\circ}C \leq TA \leq +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \leq TA \leq +125^{\circ}C$ for Extended |        |                        |  |  |

|--------------|--------|--------------------------------------------------------------------------------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------------------------|--|--|

| Param<br>No. | Symbol | Characteristic                                                                 | Min                | Typ <sup>(1)</sup> | Max                                                                                                                                                                           | Units  | Conditions             |  |  |

|              | VIL    | Input Low Voltage                                                              |                    |                    |                                                                                                                                                                               |        |                        |  |  |

| DI10         |        | I/O pins                                                                       | Vss                | —                  | 0.2 VDD                                                                                                                                                                       | V      |                        |  |  |

| DI15         |        | MCLR                                                                           | Vss                | —                  | 0.2 VDD                                                                                                                                                                       | V      |                        |  |  |

| DI16         |        | I/O Pins with OSC1 or SOSCI                                                    | Vss                | _                  | 0.2 VDD                                                                                                                                                                       | V      |                        |  |  |

| DI18         |        | SDA, SCL                                                                       | Vss                | —                  | 0.3 VDD                                                                                                                                                                       | V      | SMbus disabled         |  |  |

| DI19         |        | SDA, SCL                                                                       | Vss                | —                  | 0.8                                                                                                                                                                           | V      | SMbus enabled          |  |  |

|              | Vih    | Input High Voltage <sup>(10)</sup>                                             |                    |                    |                                                                                                                                                                               |        |                        |  |  |

| DI20         |        | I/O Pins Not 5V Tolerant <sup>(4)</sup><br>I/O Pins 5V Tolerant <sup>(4)</sup> | 0.7 Vdd<br>0.7 Vdd | _                  | Vdd<br>5.5                                                                                                                                                                    | V<br>V |                        |  |  |

| DI21         |        | I/O Pin with Schmitt Trigger<br>Input                                          | 0.7 VDD            | —                  | 0.8 VDD                                                                                                                                                                       | V      |                        |  |  |

| DI25         |        | MCLR                                                                           | 0.8 Vdd            | _                  | Vdd                                                                                                                                                                           | V      |                        |  |  |

| DI26         |        | OSC1 (in XT, HS, and LP modes)                                                 | 0.7 Vdd            | —                  | Vdd                                                                                                                                                                           | V      |                        |  |  |

| DI27         |        | OSC1 (in RC mode)                                                              | 0.9 Vdd            | _                  | Vdd                                                                                                                                                                           | V      |                        |  |  |

| DI28         |        | SDAx, SCLx                                                                     | 0.7 Vdd            | —                  | Vdd                                                                                                                                                                           | V      | SMbus disabled         |  |  |

| DI29         |        | SDAx, SCLx                                                                     | 2.1                | —                  | Vdd                                                                                                                                                                           | V      | SMbus enabled          |  |  |