Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp202-e-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

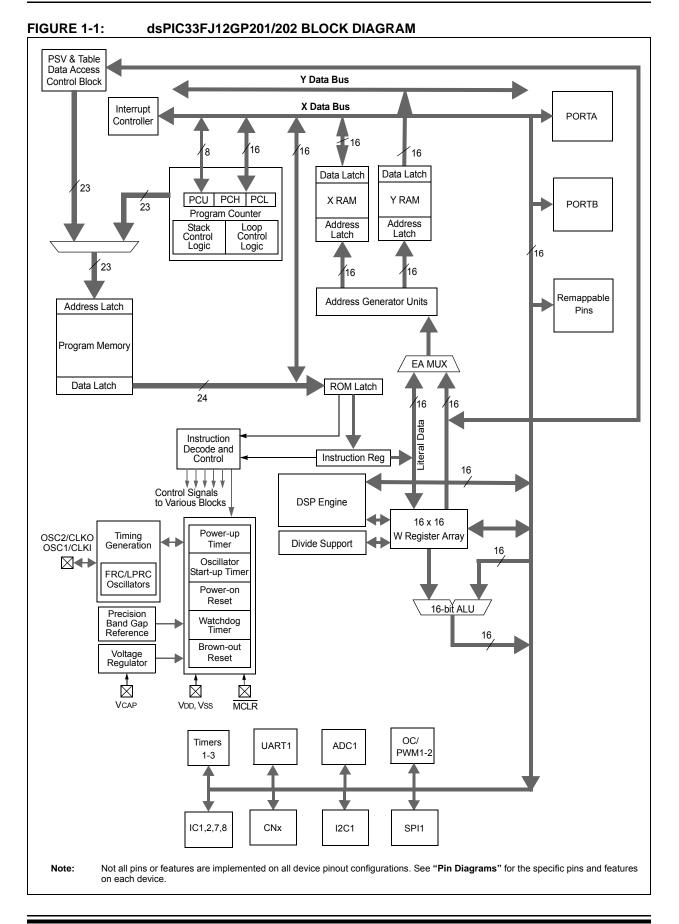

# dsPIC33FJ12GP201/202

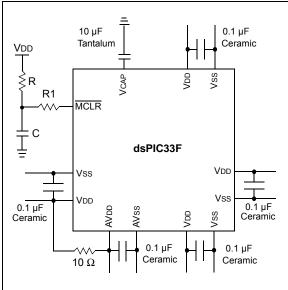

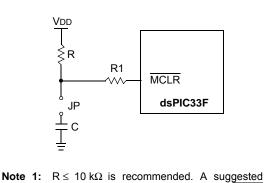

#### FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

## 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including DSCs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

## 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 22.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 19.2 "On-Chip Voltage Regulator"** for details.

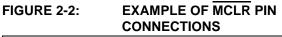

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- · Device Programming and Debugging.

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

- - 2:  $\underline{R1} \leq 470\Omega$  will limit any current flowing into  $\underline{MCLR}$  from the external capacitor C, in the event of  $\underline{MCLR}$  pin breakdown, due to Electrostatic Discharge (ESD) or <u>Electrical</u> Overstress (EOS). Ensure that the  $\underline{MCLR}$  pin VIH and VIL specifications are met.

# dsPIC33FJ12GP201/202

The SA and SB bits are modified each time data passes through the adder/subtracter, but can only be cleared by the user application. When set, they indicate that the accumulator has overflowed its maximum range (bit 31 for 32-bit saturation or bit 39 for 40-bit saturation) and will be saturated (if saturation is enabled). When saturation is not enabled, SA and SB default to bit 39 overflow, and therefore, indicate that a catastrophic overflow has occurred. If the COVTE bit in the INTCON1 register is set, the SA and SB bits will generate an arithmetic warning trap when saturation is disabled.

The Overflow and Saturation Status bits can optionally be viewed in the STATUS Register (SR) as the logical OR of OA and OB (in bit OAB) and the logical OR of SA and SB (in bit SAB). Programs can check one bit in the STATUS register to determine whether either accumulator has overflowed, or one bit to determine whether either accumulator has saturated. This is useful for complex number arithmetic, which typically uses both accumulators.

The device supports three Saturation and Overflow modes:

- Bit 39 Overflow and Saturation:

- When bit 39 overflow and saturation occurs, the saturation logic loads the maximally positive 9.31 value (0x7FFFFFFF) or maximally negative 9.31 value (0x800000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. This condition is referred to as 'super saturation' and provides protection against erroneous data or unexpected algorithm problems (such as gain calculations).

- Bit 31 Overflow and Saturation: When bit 31 overflow and saturation occurs, the saturation logic then loads the maximally positive 1.31 value (0x007FFFFFF) or maximally negative 1.31 value (0x008000000) into the target accumulator. The SA or SB bit is set and remains set until cleared by the user application. When this Saturation mode is in effect, the guard bits are not used, so the OA, OB or OAB bits are never set.

- Bit 39 Catastrophic Overflow: The bit 39 Overflow Status bit from the adder is used to set the SA or SB bit, which remains set until cleared by the user application. No saturation operation is performed and the accumulator is allowed to overflow, destroying its sign. If the COVTE bit in the INTCON1 register is set, a catastrophic overflow can initiate a trap exception.

## 3.6.2.2 Accumulator 'Write Back'

The MAC class of instructions (with the exception of MPY, MPY.N, ED and EDAC) can optionally write a rounded version of the high word (bits 31 through 16) of the accumulator which is not targeted by the instruction into data space memory. The write is

performed across the X bus into combined X and Y address space. The following addressing modes are supported:

- W13, Register Direct: The rounded contents of the non-target accumulator are written into W13 as a 1.15 fraction

- [W13] + = 2, Register Indirect with Post-Increment: The rounded contents of the non-target accumulator are written into the address pointed to by W13 as a 1.15 fraction. W13 is then incremented by 2 (for a word write).

## 3.6.2.3 Round Logic

The round logic is a combinational block that performs a conventional (biased) or convergent (unbiased) round function during an accumulator write (store). The Round mode is determined by the state of the RND bit in the CORCON register. It generates a 16-bit, 1.15 data value that is passed to the data space write saturation logic. If rounding is not indicated by the instruction, a truncated 1.15 data value is stored and the least significant word (lsw) is simply discarded.

Conventional rounding will zero-extend bit 15 of the accumulator and will add it to the ACCxH word (bits 16 through 31 of the accumulator).

- If the ACCxL word (bits 0 through 15 of the accumulator) is between 0x8000 and 0xFFFF (0x8000 included), ACCxH is incremented

- If ACCxL is between 0x0000 and 0x7FFF, ACCxH is left unchanged

A consequence of this algorithm is that over a succession of random rounding operations, the value tends to be biased slightly positive.

Convergent (or unbiased) rounding operates in the same manner as conventional rounding, except when ACCxL equals 0x8000. In this case, the LSb (bit 16 of the accumulator) of ACCxH is examined.

- If it is '1', ACCxH is incremented

- If it is '0', ACCxH is not modified. Assuming that bit 16 is effectively random in nature, this scheme removes any rounding bias that may accumulate.

The SAC and SAC.R instructions store either a truncated (SAC), or rounded (SAC.R) version of the contents of the target accumulator to data memory via the X bus, subject to data saturation (see **Section 3.6.2.4 "Data Space Write Saturation**"). For the MAC class of instructions, the accumulator write-back operation functions in the same manner, addressing combined MCU (X and Y) data space though the X bus. For this class of instructions, the data is always subject to rounding.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the dsPIC33FJ12GP201/202 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decoding, but separate write lines. Data byte writes only write to the corresponding side of the array or register that matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction in progress is completed. If the instruction occurred on a write, the instruction is executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user application to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternately, for 16-bit unsigned data, user applications can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

## 4.2.3 SFR SPACE

The first 2 Kbytes of the near data space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJ12GP201/202 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A complete listing of implemented SFRs, including their addresses, is shown in Table 4-1 through Table 4-21.

| The actual set of peripheral features and<br>interrupts varies by the device. Refer to |  |  |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| the corresponding device tables and                                                    |  |  |  |  |  |  |  |  |  |  |

| pinout diagrams for device-specific information.                                       |  |  |  |  |  |  |  |  |  |  |

|                                                                                        |  |  |  |  |  |  |  |  |  |  |

## 4.2.4 NEAR DATA SPACE

The 8 Kbyte area between 0x0000 and 0x1FFF is referred to as the near data space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV class of instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode with a working register as an address pointer.

| <b>TABLE 4-14:</b> | ADC1 REGISTER MAP FOR dsPIC33FJ12GP201 |

|--------------------|----------------------------------------|

|--------------------|----------------------------------------|

| IADLE 4-  | 14. / |        | EGISTI   |        | FUR as | гюзэг  | JIZGFA    | 201     |          |           |           |       |       |        |           |         |         |               |

|-----------|-------|--------|----------|--------|--------|--------|-----------|---------|----------|-----------|-----------|-------|-------|--------|-----------|---------|---------|---------------|

| File Name | Addr  | Bit 15 | Bit 14   | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9   | Bit 8    | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300  |        |          |        |        |        |           |         | ADC Data | Buffer 0  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF1  | 0302  |        |          |        |        |        |           |         | ADC Data | Buffer 1  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF2  | 0304  |        |          |        |        |        |           |         | ADC Data | Buffer 2  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF3  | 0306  |        |          |        |        |        |           |         | ADC Data | Buffer 3  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF4  | 0308  |        |          |        |        |        |           |         | ADC Data | Buffer 4  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF5  | 030A  |        |          |        |        |        |           |         | ADC Data | Buffer 5  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF6  | 030C  |        |          |        |        |        |           |         | ADC Data | Buffer 6  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF7  | 030E  |        |          |        |        |        |           |         | ADC Data | Buffer 7  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF8  | 0310  |        |          |        |        |        |           |         | ADC Data | Buffer 8  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF9  | 0312  |        |          |        |        |        |           |         | ADC Data | Buffer 9  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFA  | 0314  |        |          |        |        |        |           |         | ADC Data | Buffer 10 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFB  | 0316  |        |          |        |        |        |           |         | ADC Data | Buffer 11 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFC  | 0318  |        |          |        |        |        |           |         | ADC Data | Buffer 12 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFD  | 031A  |        |          |        |        |        |           |         | ADC Data | Buffer 13 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFE  | 031C  |        |          |        |        |        |           |         | ADC Data | Buffer 14 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFF  | 031E  |        |          |        |        |        |           |         | ADC Data | Buffer 15 |           |       |       |        |           |         |         | xxxx          |

| AD1CON1   | 0320  | ADON   | —        | ADSIDL | _      | _      | AD12B     | -       | M<1:0>   |           | SSRC<2:0> |       | —     | SIMSAM | ASAM      | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322  |        | VCFG<2:0 | >      | —      | —      | CSCNA     | -       | PS<1:0>  | BUFS      | —         |       | SMPI  |        |           | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324  | ADRC   | _        | —      |        | S      | SAMC<4:0> |         |          |           |           |       | ADCS  | 8<7:0> | -         |         | r       | 0000          |

| AD1CHS123 | 0326  | —      | —        | —      | —      | —      |           | NB<1:0> | CH123SB  | _         | —         | —     | —     | —      |           | NA<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328  | CH0NB  | —        | —      |        | С      | H0SB<4:0> | >       |          | CH0NA     | —         | —     |       | r      | CH0SA<4:0 |         | r       | 0000          |

| AD1PCFGL  | 032C  |        | _        | —      | _      | _      | _         | -       | —        | PCFG7     | PCFG6     | —     | —     | PCFG3  | PCFG2     | PCFG1   | PCFG0   | 0000          |

| AD1CSSL   | 0330  | —      | —        | —      | —      | _      | —         | —       | —        | CSS7      | CSS6      | —     |       | CSS3   | CSS2      | CSS1    | CSS0    | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| File Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9   | Bit 8    | Bit 7      | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|------|--------|----------|--------|--------|--------|-----------|---------|----------|------------|-----------|-------|-------|--------|----------|---------|---------|---------------|

| ADC1BUF0  | 0300 |        |          | •      |        |        | •         |         | ADC Data | a Buffer 0 |           |       |       | •      |          |         |         | xxxx          |

| ADC1BUF1  | 0302 |        |          |        |        |        |           |         | ADC Data | a Buffer 1 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF2  | 0304 |        |          |        |        |        |           |         | ADC Data | a Buffer 2 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF3  | 0306 |        |          |        |        |        |           |         | ADC Data | a Buffer 3 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF4  | 0308 |        |          |        |        |        |           |         | ADC Data | a Buffer 4 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF5  | 030A |        |          |        |        |        |           |         | ADC Data | a Buffer 5 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF6  | 030C |        |          |        |        |        |           |         | ADC Data | a Buffer 6 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF7  | 030E |        |          |        |        |        |           |         | ADC Data | a Buffer 7 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF8  | 0310 |        |          |        |        |        |           |         | ADC Data | a Buffer 8 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF9  | 0312 |        |          |        |        |        |           |         | ADC Data | a Buffer 9 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFA  | 0314 |        |          |        |        |        |           |         | ADC Data | Buffer 10  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFB  | 0316 |        |          |        |        |        |           |         | ADC Data | Buffer 11  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFC  | 0318 |        |          |        |        |        |           |         | ADC Data | Buffer 12  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFD  | 031A |        |          |        |        |        |           |         | ADC Data | Buffer 13  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFE  | 031C |        |          |        |        |        |           |         | ADC Data | Buffer 14  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFF  | 031E |        |          |        |        |        |           |         | ADC Data | Buffer 15  |           |       |       |        |          |         |         | xxxx          |

| AD1CON1   | 0320 | ADON   | _        | ADSIDL |        | _      | AD12B     | FOR     | M<1:0>   | ç          | SSRC<2:0> | >     | _     | SIMSAM | ASAM     | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322 | Ň      | VCFG<2:0 | >      | —      |        | CSCNA     | CHP     | S<1:0>   | BUFS       | _         |       | SMPI  | <3:0>  |          | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | —        | -      |        |        | SAMC<4:0  | >       |          |            |           |       | ADC   | S<7:0> |          |         |         | 0000          |

| AD1CHS123 | 0326 | _      | _        | _      | _      | _      | CH123N    | NB<1:0> | CH123SB  | _          | _         | _     | _     | —      | CH123    | NA<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _        | _      |        |        | CH0SB<4:0 | -       |          | CH0NA      | _         | —     |       |        | CH0SA<4: |         | 1       | 0000          |

| AD1PCFGL  | 032C | _      | _        | _      | _      |        |           | PCFG9   | PCFG8    | PCFG7      | PCFG6     | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1   | PCFG0   | 0000          |

| AD1CSSL   | 0330 | —      |          | —      | —      | —      | —         | CSS9    | CSS8     | CSS7       | CSS6      | CSS5  | CSS4  | CSS3   | CSS2     | CSS1    | CSS0    | 0000          |

dsPIC33FJ12GP201/202

#### TABLE 4-15: ADC1 REGISTER MAP FOR dsPIC33FJ12GP202

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-20: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7       | Bit 6 | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets   |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------------|-------|-------|-------|------------|-------|-------|-------|-----------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | _      | -      | _     |       | _           | ERASE |       | —     | NVMOP<3:0> |       |       |       | 0000 <b>(1)</b> |

| NVMKEY    | 0766 |        | —      | _      | _      | _      |        | _     | _     | NVMKEY<7:0> |       |       |       |            |       | 0000  |       |                 |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

#### TABLE 4-21: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|-------|--------|-------|-------|-------|---------------|

| PMD1      | 0770 | —      | _      | T3MD   | T2MD   | T1MD   | _      | _     | —     | I2C1MD | _     | U1MD  | _     | SPI1MD | _     | _     | AD1MD | 0000          |

|           |      |        |        |        |        |        |        |       |       |        |       |       |       |        |       |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

Programmers can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to <sup>(0010)</sup> to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 0x55 to NVMKEY.

- d) Write 0xAA to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user application must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                         |

|-------------------------------------------|-----------------------------------------|

| MOV #0x4042, W0                           | i                                       |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Init pointer to row to be ERASED        |                                         |

| MOV #tblpage(PROG_ADDR), W0               | ;                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA[15:0] pointer   |

| TBLWTL W0, [W0]                           | ; Set base address of erase block       |

| DISI #5                                   | ; Block all interrupts with priority <7 |

|                                           | ; for next 5 instructions               |

| MOV #0x55, W0                             |                                         |

| MOV W0, NVMKEY                            | ; Write the 55 key                      |

| MOV #0xAA, W1                             | i                                       |

| MOV W1, NVMKEY                            | ; Write the AA key                      |

| BSET NVMCON, #WR                          | ; Start the erase sequence              |

| NOP                                       | ; Insert two NOPs after the erase       |

| NOP                                       | ; command is asserted                   |

|                                           |                                         |

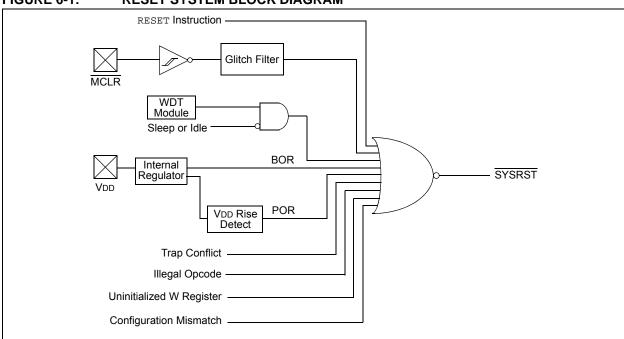

## 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

#### FIGURE 6-1:

## RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

All bits that are set, with the exception of the POR bit (RCON<0>), are cleared during a POR event. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

© 2007-2011 Microchip Technology Inc.

## **REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup> (CONTINUED)**

- bit 1 BOR: Brown-out Reset Flag bit

- 1 = A Brown-out Reset has occurred

0 = A Brown-out Reset has not occurred

- bit 0 **POR:** Power-on Reset Flag bit

- 1 = A Power-up Reset has occurred

- 0 = A Power-up Reset has not occurred

- **Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

- 2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

## REGISTER 7-8: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by Equation 8-2.

#### EQUATION 8-2: Fosc CALCULATION

$$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$$

For example, suppose a 10 MHz crystal is being used, with "XT with PLL" being the selected oscillator mode.

- If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

- If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

## FIGURE 8-2: dsPIC33FJ12GP201/202 PLL BLOCK DIAGRAM

#### **Fvco** 0.8-8.0 MHz 12.5-80 MHz Here<sup>(1)</sup> 100-200 MHz Here<sup>(1)</sup> Here<sup>(1)</sup> Source (Crystal, External Clock PLLPRE Fosc Х VCO PLLPOST or Internal RC) PLLDIV N1 N2 Divide by Divide by Μ 2-33 2, 4, 8 Divide by 2-513 Note 1: This frequency range must be satisfied at all times.

## EQUATION 8-3: XT WITH PLL MODE EXAMPLE

$$F_{CY} = \frac{F_{OSC}}{2} = \frac{1}{2} \left( \frac{10000000 \cdot 32}{2 \cdot 2} \right) = 40 \text{ MIPS}$$

| U-0           | U-0          | R/W-0             | R/W-0   | R/W-0             | U-0  | U-0            | U-0   |

|---------------|--------------|-------------------|---------|-------------------|------|----------------|-------|

| _             | —            | T3MD              | T2MD    | T1MD              | _    |                | _     |

| bit 15        |              |                   |         |                   |      |                | bit   |

|               |              |                   |         |                   |      |                |       |

| R/W-0         | U-0          | R/W-0             | U-0     | R/W-0             | U-0  | U-0            | R/W-0 |

| I2C1MD        |              | U1MD              | —       | SPI1MD            | —    |                | AD1MD |

| bit 7         |              |                   |         |                   |      |                | bit   |

|               |              |                   |         |                   |      |                |       |

| Legend:       |              |                   |         |                   |      |                |       |

| R = Readabl   |              | W = Writable      |         | U = Unimplem      |      |                |       |

| -n = Value at | POR          | '1' = Bit is set  |         | '0' = Bit is clea | ared | x = Bit is unk | nown  |

|               |              |                   |         |                   |      |                |       |

| bit 15-14     | -            | nted: Read as '   |         |                   |      |                |       |

| bit 13        |              | r3 Module Disal   |         |                   |      |                |       |

|               |              | nodule is enable  |         |                   |      |                |       |

| bit 12        |              | r2 Module Disal   |         |                   |      |                |       |

|               | 1 = Timer2 r | module is disabl  | ed      |                   |      |                |       |

|               | 0 = Timer2 r | module is enable  | ed      |                   |      |                |       |

| bit 11        | T1MD: Time   | er1 Module Disal  | ole bit |                   |      |                |       |

|               | -            | nodule is disabl  |         |                   |      |                |       |

|               |              | nodule is enable  |         |                   |      |                |       |

| bit 10-8      | -            | nted: Read as '   |         |                   |      |                |       |

| bit 7         | -            | C1 Module Disal   |         |                   |      |                |       |

|               |              | dule is enabled   |         |                   |      |                |       |

| bit 6         | Unimpleme    | nted: Read as '   | 0'      |                   |      |                |       |

| bit 5         | -            | T1 Module Disa    |         |                   |      |                |       |

|               | 1 = UART1    | module is disabl  | ed      |                   |      |                |       |

|               | 0 = UART1    | module is enabl   | ed      |                   |      |                |       |

| bit 4         | Unimpleme    | nted: Read as '   | 0'      |                   |      |                |       |

| bit 3         |              | PI1 Module Disa   |         |                   |      |                |       |

|               |              | odule is disabled |         |                   |      |                |       |

| bit 2-1       |              | nted: Read as '   | 0'      |                   |      |                |       |

| bit 0         | -            | C1 Module Disa    |         |                   |      |                |       |

|               |              | nodule is disable |         |                   |      |                |       |

|               |              |                   |         |                   |      |                |       |

**Note 1:** PCFGx bits have no effect if the ADC module is disabled by setting this bit. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

## 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT, and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See **"Pin Diagrams"** for the available pins and their functionality.

## 10.2 Configuring Analog Port Pins

The AD1PCFG and TRIS registers control the operation of the Analog-to-Digital (A/D) port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

The AD1PCFGL register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

When the PORT register is read, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

## 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be a NOP. An example is shown in Example 10-1.

## 10.3 Input Change Notification

The input change notification function of the I/O ports allows the dsPIC33FJ12GP201/202 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, up to 21 external signals (CNx pin) can be selected (enabled) for generating an interrupt request on a change-of-state.

Four control registers are associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled when the port pin is configured as a digital output.

| MOV 0xFF00, W0<br>MOV W0, TRISBB | ; Configure PORTB<15:8> as inputs<br>; and PORTB<7:0> as outputs |  |

|----------------------------------|------------------------------------------------------------------|--|

| NOP<br>btss PORTB, #13           | ; Delay 1 cycle<br>; Next Instruction                            |  |

#### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| U-0           | U-0                                                                                                         | U-0                                                                                      | R/W-1          | R/W-1            | R/W-1           | R/W-1            | R/W-1 |

|---------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------|------------------|-----------------|------------------|-------|

| —             | —                                                                                                           | _                                                                                        |                |                  | T3CKR<4:0>      |                  |       |

| bit 15        |                                                                                                             |                                                                                          |                |                  |                 |                  | bit 8 |

|               |                                                                                                             |                                                                                          |                |                  |                 |                  |       |

| U-0           | U-0                                                                                                         | U-0                                                                                      | R/W-1          | R/W-1            | R/W-1           | R/W-1            | R/W-1 |

| —             | —                                                                                                           | —                                                                                        |                |                  | T2CKR<4:0>      | •                |       |

| bit 7         |                                                                                                             |                                                                                          |                |                  |                 |                  | bit ( |

|               |                                                                                                             |                                                                                          |                |                  |                 |                  |       |

| Legend:       |                                                                                                             |                                                                                          |                |                  |                 |                  |       |

| R = Readabl   | le bit                                                                                                      | W = Writable                                                                             | bit            | U = Unimple      | mented bit, rea | d as '0'         |       |

| -n = Value at | t POR                                                                                                       | '1' = Bit is set                                                                         | I              | '0' = Bit is cle | eared           | x = Bit is unki  | nown  |

| bit 7-5       | 01111 = Inpu<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | ut tied to Vss<br>ut tied to RP15<br>ut tied to RP1<br>ut tied to RP0<br>nted: Read as   |                |                  |                 |                  |       |

| bit 4-0       | 11111 = Inpu<br>01111 = Inpu<br>•<br>•<br>•<br>00001 = Inpu                                                 | •: Assign Timer<br>ut tied to Vss<br>ut tied to RP15<br>ut tied to RP1<br>ut tied to RP0 | 2 External Clo | ock (T2CK) to t  | he Correspond   | ing RPn pin bits | 3     |

#### REGISTER 10-3: RPINR3: PERIPHERAL PIN SELECT INPUT REGISTER 3

#### REGISTER 10-13: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTERS 3

| U-0          | U-0        | U-0              | R/W-0 | R/W-0                                   | R/W-0           | R/W-0             | R/W-0    |  |  |

|--------------|------------|------------------|-------|-----------------------------------------|-----------------|-------------------|----------|--|--|

| _            | —          | —                |       |                                         | RP7R<4:0>       |                   |          |  |  |

| bit 15       |            |                  |       |                                         |                 |                   | bit 8    |  |  |

|              |            |                  |       |                                         |                 |                   |          |  |  |

| U-0          | U-0        | U-0              | R/W-0 | R/W-0                                   | R/W-0           | R/W-0             | R/W-0    |  |  |

| —            | —          | —                |       |                                         | RP6R<4:0>       |                   |          |  |  |

| bit 7        |            |                  |       |                                         |                 |                   | bit 0    |  |  |

|              |            |                  |       |                                         |                 |                   |          |  |  |

| Legend:      |            |                  |       |                                         |                 |                   |          |  |  |

| R = Readab   | le bit     | W = Writable     | bit   | U = Unimpler                            | nented bit, rea | d as '0'          |          |  |  |

| -n = Value a | t POR      | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                 |                   |          |  |  |

|              |            |                  |       |                                         |                 |                   |          |  |  |

| bit 15-13    | Unimplemen | ted: Read as 'o  | כי    |                                         |                 |                   |          |  |  |

| bit 12-8     |            | Peripheral Outr  |       | s Assigned to F                         | RP7 Output Pir  | i bits (see Table | 10-2 for |  |  |

| bit 7-5      | Unimplemen | ted: Read as '   | כ'    |                                         |                 |                   |          |  |  |

|              |            |                  |       |                                         |                 |                   |          |  |  |

bit 4-0 **RP6R<4:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-14: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTERS 0

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP9R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP8R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 10-2 for peripheral function numbers)

## REGISTER 10-15: RPOR5: PERIPHERAL PIN SELECT OUTPUT REGISTERS 5

| U-0           | U-0        | U-0                            | R/W-0 | R/W-0                              | R/W-0           | R/W-0             | R/W-0        |  |

|---------------|------------|--------------------------------|-------|------------------------------------|-----------------|-------------------|--------------|--|

| _             | _          | _                              |       |                                    | RP11R<4:0       | >                 |              |  |

| bit 15        |            |                                |       |                                    |                 |                   | bit 8        |  |

|               |            |                                |       |                                    |                 |                   |              |  |

| U-0           | U-0        | U-0                            | R/W-0 | R/W-0                              | R/W-0           | R/W-0             | R/W-0        |  |

| —             | —          | —                              |       |                                    | RP10R<4:0       | >                 |              |  |

| bit 7         |            |                                |       |                                    |                 |                   | bit 0        |  |

|               |            |                                |       |                                    |                 |                   |              |  |

| Legend:       |            |                                |       |                                    |                 |                   |              |  |

| R = Readabl   | le bit     | W = Writable                   | bit   | U = Unimplemented bit, read as '0' |                 |                   |              |  |

| -n = Value at | POR        | '1' = Bit is set               |       | '0' = Bit is cle                   | x = Bit is unkr | t is unknown      |              |  |

|               |            |                                |       |                                    |                 |                   |              |  |

| bit 15-13     | Unimplemen | ted: Read as '                 | כ'    |                                    |                 |                   |              |  |

| bit 12-8      |            | : Peripheral Ounction numbers) | •     | n is Assigned to                   | RP11 Output     | Pin bits (see Tat | ble 10-2 for |  |

|               |            |                                |       |                                    |                 |                   |              |  |

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP10R<4:0>:** Peripheral Output Function is Assigned to RP10 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-16: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTERS 6

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP13R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP12R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP13R<4:0>:** Peripheral Output Function is Assigned to RP13 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP12R<4:0>:** Peripheral Output Function is Assigned to RP12 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### TABLE 22-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| AC CHARACTERISTICS                |       |                                                                     | Standard O<br>Operating to |     | ire -40°           | C ≤TA ≤+8 | 5°C for I                      | <b>(unless otherwise stated)</b><br>ndustrial<br>Extended |

|-----------------------------------|-------|---------------------------------------------------------------------|----------------------------|-----|--------------------|-----------|--------------------------------|-----------------------------------------------------------|

| Param<br>No. Symbol Characteristi |       |                                                                     | tic                        | Min | Тур <sup>(1)</sup> | Max       | Units                          | Conditions                                                |

| OS50                              | Fplli | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                            | 0.8 | _                  | 8         | MHz                            | ECPLL, HSPLL, XTPLL<br>modes                              |

| OS51                              | Fsys  | On-Chip VCO System                                                  | n Frequency                | 100 | —                  | 200       | MHz                            | —                                                         |

| OS52                              | TLOCK | PLL Start-up Time (Lo                                               | ock Time)                  | 0.9 | 1.5                | 3.1       | mS                             | —                                                         |

| OS53                              | DCLK  | CLKO Stability (Jitter)                                             | -3                         | 0.5 | 3                  | %         | Measured over 100 ms<br>period |                                                           |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized by similarity, but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time bases or communication clocks use this formula:

Peripheral Clock Jitter =

$$\frac{DCLK}{\sqrt{\frac{FOSC}{Peripheral Bit Rate Clock}}}$$

For example: Fosc = 32 MHz, DCLK = 3%, SPI bit rate clock, (i.e., SCK) is 2 MHz.

$$SPI SCK Jitter = \left\lfloor \frac{D_{CLK}}{\sqrt{\left(\frac{32 \ MHz}{2 \ MHz}\right)}} \right\rfloor = \left\lfloor \frac{3\%}{\sqrt{16}} \right\rfloor = \left\lfloor \frac{3\%}{4} \right\rfloor = 0.75\%$$

#### TABLE 22-18: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| АС СНА       | RACTERISTICS            | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)      Operating temperature    -40°C ≤TA ≤+85°C for industrial      -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                  |  |  |  |

|--------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|----------------------------------|--|--|--|

| Param<br>No. | Characteristic          | Min                                                                                                                                                                     | Тур                | Max | Units | Units Conditions                 |  |  |  |

|              | Internal FRC Accuracy @ | 7.3728                                                                                                                                                                  | MHz <sup>(1)</sup> |     |       |                                  |  |  |  |

| F20a         | FRC                     | -2                                                                                                                                                                      | —                  | +2  | %     | -40°C ≤TA ≤+85°C VDD = 3.0-3.6V  |  |  |  |

| F20b         | FRC                     | -5                                                                                                                                                                      | —                  | +5  | %     | -40°C ≤TA ≤+125°C VDD = 3.0-3.6V |  |  |  |

**Note 1:** Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

#### TABLE 22-19: INTERNAL RC ACCURACY

| AC CH        | ARACTERISTICS                      | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)      Operating temperature    -40°C ≤TA ≤+85°C for Industrial      -40°C ≤TA ≤+125°C for Extended |    |     |   |                  |                |  |

|--------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----|---|------------------|----------------|--|

| Param<br>No. | Characteristic                     | Min Typ Max Units Conditions                                                                                                                                            |    |     |   |                  | ions           |  |

|              | LPRC @ 32.768 kHz <sup>(1,2)</sup> |                                                                                                                                                                         |    |     |   |                  |                |  |

| F21a         | LPRC                               | -20                                                                                                                                                                     | ±6 | +20 | % | -40°C ≤TA ≤+85°C | VDD = 3.0-3.6V |  |

| F21b         | LPRC                               | -70 — +70 % -40°C ≤TA ≤+125°C VDD = 3.0-3.6V                                                                                                                            |    |     |   |                  |                |  |

Note 1: Change of LPRC frequency as VDD changes.

2: LPRC accuracy impacts the Watchdog Timer Time-out Period (TwDT1). See Section 19.4 "Watchdog Timer (WDT)" for more information.

| АС СНА       | AC CHARACTERISTICS    |                                              |     | Standard Operating Conditions: 3.0V to 3.6V      (unless otherwise stated)      Operating temperature    -40°C ≤TA ≤+85°C for Industrial      -40°C ≤TA ≤+125°C for Extended |     |       |                                      |  |  |

|--------------|-----------------------|----------------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                | Min | Тур <sup>(2)</sup>                                                                                                                                                           | Max | Units | Conditions                           |  |  |

| SP10         | TscP                  | Maximum SCK Frequency                        | _   |                                                                                                                                                                              | 15  | MHz   | See Note 3                           |  |  |

| SP20         | TscF                  | SCKx Output Fall Time                        | —   | —                                                                                                                                                                            | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |  |

| SP21         | TscR                  | SCKx Output Rise Time                        | —   | —                                                                                                                                                                            | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                   | —   | —                                                                                                                                                                            | _   | ns    | See parameter DO32 and <b>Note 4</b> |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                   | —   | —                                                                                                                                                                            | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge    | —   | 6                                                                                                                                                                            | 20  | ns    | —                                    |  |  |

| SP36         | TdiV2scH,<br>TdiV2scL | SDOx Data Output Setup to<br>First SCKx Edge | 30  | _                                                                                                                                                                            |     | ns    | —                                    |  |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 66.7 ns. Therefore, the clock generated in Master mode must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.

# dsPIC33FJ12GP201/202

NOTES: