#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                  |

| Supplier Device Package    | 28-SSOP                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp202-e-ss |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS70204) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJ12GP201/202 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M by 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ12GP201/202 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJ12GP201/202 instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions. dsPIC33FJ12GP201/202 devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1. The programmer's model for the dsPIC33FJ12GP201/202 is shown in Figure 3-2.

## 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

# 3.2 DSP Engine Overview

The DSP engine features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

# 3.3 Special MCU Features

The dsPIC33FJ12GP201/202 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

# 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJ12GP201/202 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU can affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The dsPIC33FJ12GP201/202 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

Refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157) for information on the SR bits affected by each instruction.

## 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m+1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.6 DSP Engine

The DSP engine consists of a high-speed 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJ12GP201/202 is a single-cycle instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources can be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine can also perform accumulator-to-accumulator operations that require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has options selected through bits in the CPU Core Control register (CORCON), as listed below:

- Fractional or integer DSP multiply (IF)

- Signed or unsigned DSP multiply (US)

- Conventional or convergent rounding (RND)

- Automatic saturation on/off for ACCA (SATA), ACCB (SATB) and writes to data memory (SATDW)

- Accumulator Saturation mode selection (ACC-SAT)

A block diagram of the DSP engine is shown in Figure 3-3.

| TABLE 3-1: | DSP INSTRUCTIONS |

|------------|------------------|

|            | SUMMARY          |

|             | SUMMARI                |                   |

|-------------|------------------------|-------------------|

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

NOTES:

### REGISTER 5-2: NVMKEY: NONVOLATILE MEMORY KEY REGISTER

| U-0                                                                        | U-0 | U-0            | U-0      | U-0          | U-0              | U-0      | U-0   |

|----------------------------------------------------------------------------|-----|----------------|----------|--------------|------------------|----------|-------|

| —                                                                          | _   | -              | —        | —            | —                | —        | —     |

| bit 15                                                                     |     |                |          |              |                  |          | bit 8 |

|                                                                            |     |                |          |              |                  |          |       |

| W-0                                                                        | W-0 | W-0            | W-0      | W-0          | W-0              | W-0      | W-0   |

|                                                                            |     |                | NVMK     | (EY<7:0>     |                  |          |       |

| bit 7                                                                      |     |                |          |              |                  |          | bit 0 |

|                                                                            |     |                |          |              |                  |          |       |

| Legend:                                                                    |     | SO = Settable  | only bit |              |                  |          |       |

| R = Readable b                                                             | pit | W = Writable I | bit      | U = Unimplei | mented bit, read | 1 as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |     |                |          |              |                  |          | nown  |

|                                                                            |     |                |          |              |                  |          |       |

bit 15-8 Unimplemented: Read as '0'

bit 7-0 NVMKEY<7:0>: Key Register (write-only) bits

# 6.0 RESETS

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

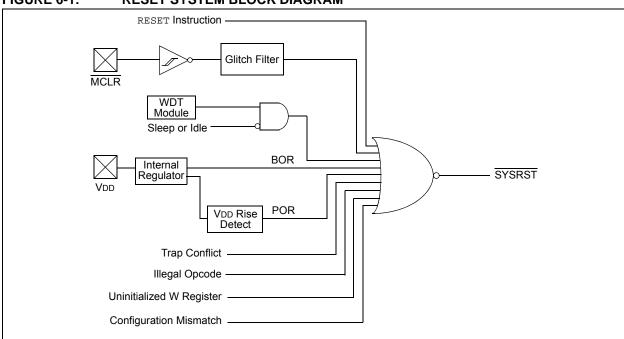

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDTO: Watchdog Timer Reset

- CM: Configuration Mismatch Reset

- TRAPR: Trap Conflict Reset

- · IOPUWR: Illegal Condition Device Reset

- Illegal Opcode Reset

- Uninitialized W Register Reset

- Security Reset

#### FIGURE 6-1:

# RESET SYSTEM BLOCK DIAGRAM

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. On system Reset, some of the registers associated with the CPU and peripherals are forced to a known Reset state, and some are unaffected.

Note: Refer to the specific peripheral section or Section 3.0 "CPU" of this manual for register Reset states.

All types of device Reset set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1).

All bits that are set, with the exception of the POR bit (RCON<0>), are cleared during a POR event. The user application can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this data sheet.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset is meaningful.

© 2007-2011 Microchip Technology Inc.

| U-0                | U-0                                     | R/W-0                            | R/W-0            | R/W-0          | R/W-0           | R/W-0           | R/W-0  |  |

|--------------------|-----------------------------------------|----------------------------------|------------------|----------------|-----------------|-----------------|--------|--|

| _                  |                                         | AD1IE                            | U1TXIE           | U1RXIE         | SPI1IE          | SPI1EIE         | T3IE   |  |

| bit 15             |                                         |                                  |                  |                | ·               |                 | bit 8  |  |

| R/W-0              | R/W-0                                   | R/W-0                            | U-0              | R/W-0          | R/W-0           | R/W-0           | R/W-0  |  |

| T2IE               | OC2IE                                   | IC2IE                            | _                | T1IE           | OC1IE           | IC1IE           | INTOIE |  |

| bit 7              |                                         |                                  |                  |                |                 |                 | bit C  |  |

| Legend:            |                                         |                                  |                  |                |                 |                 |        |  |

| R = Readable       | bit                                     | W = Writable                     | bit              | U = Unimple    | emented bit, re | ead as '0'      |        |  |

| -n = Value at F    | POR                                     | '1' = Bit is se                  | t                | '0' = Bit is c | leared          | x = Bit is unkn | own    |  |

| <b>L:1 4 5 4 4</b> |                                         | tod. Dood oo                     |                  |                |                 |                 |        |  |

| bit 15-14          | -                                       | ted: Read as                     |                  |                | :4              |                 |        |  |

| bit 13             | 1 = Interrupt r                         | request enable<br>request not en |                  | rupt Enable b  | ot              |                 |        |  |

| bit 12             | -                                       | -                                | r Interrupt Ena  | able bit       |                 |                 |        |  |

|                    | 1 = Interrupt r                         | request enable<br>request not en | d                |                |                 |                 |        |  |

| bit 11             | U1RXIE: UAF                             | RT1 Receiver I                   | nterrupt Enabl   | e bit          |                 |                 |        |  |

|                    |                                         | request enable<br>request not en |                  |                |                 |                 |        |  |

| bit 10             | SPI1IE: SPI1 Event Interrupt Enable bit |                                  |                  |                |                 |                 |        |  |

|                    | •                                       | request enable<br>request not en |                  |                |                 |                 |        |  |

| bit 9              |                                         | 1 Error Interru                  | •                |                |                 |                 |        |  |

|                    |                                         | request enable<br>request not en |                  |                |                 |                 |        |  |

| bit 8              | -                                       | Interrupt Enab                   |                  |                |                 |                 |        |  |

|                    | 1 = Interrupt r                         | request enable<br>request not en | d                |                |                 |                 |        |  |

| bit 7              | •                                       | Interrupt Enat                   |                  |                |                 |                 |        |  |

|                    |                                         | request enable                   |                  |                |                 |                 |        |  |

|                    | 0 = Interrupt r                         | request not en                   | abled            |                |                 |                 |        |  |

| bit 6              | •                                       | •                                | nannel 2 Interr  | upt Enable bi  | t               |                 |        |  |

|                    |                                         | request enable<br>request not en |                  |                |                 |                 |        |  |

| bit 5              | -                                       | -                                | el 2 Interrupt I | Enable bit     |                 |                 |        |  |

|                    |                                         | request enable<br>request not en |                  |                |                 |                 |        |  |

| bit 4              | Unimplemen                              | ted: Read as                     | 0'               |                |                 |                 |        |  |

| bit 3              |                                         | Interrupt Enat                   |                  |                |                 |                 |        |  |

|                    |                                         | request enable<br>request not en |                  |                |                 |                 |        |  |

| bit 2              | OC1IE: Output                           | ut Compare Cl                    | nannel 1 Interr  | upt Enable bi  | t               |                 |        |  |

|                    |                                         | request enable<br>request not en |                  |                |                 |                 |        |  |

# REGISTER 7-8: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0

NOTES:

# 8.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "Oscillator" (DS70186) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

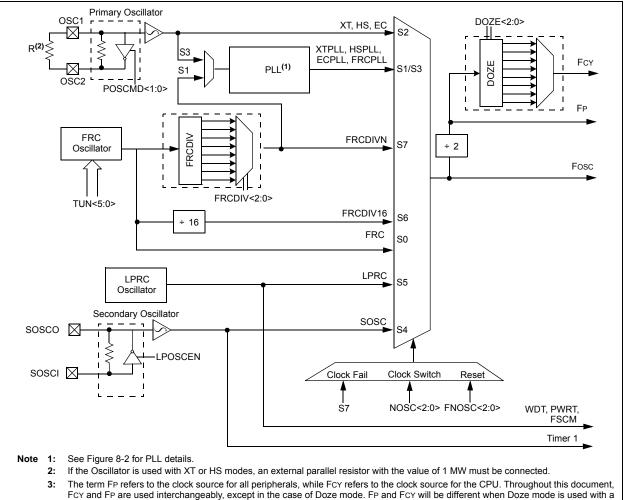

The dsPIC33FJ12GP201/202 oscillator system provides:

- External and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- An internal FRC oscillator that can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

A simplified diagram of the oscillator system is shown in Figure 8-1.

### FIGURE 8-1: dsPIC33FJ12GP201/202 OSCILLATOR SYSTEM DIAGRAM

Doze ratio of 1:2 or lower.

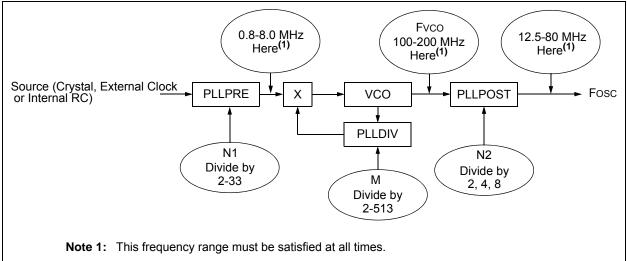

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by Equation 8-2.

### EQUATION 8-2: Fosc CALCULATION

$$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$$

For example, suppose a 10 MHz crystal is being used, with "XT with PLL" being the selected oscillator mode.

- If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz.

- If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz ranged needed.

- If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

## FIGURE 8-2: dsPIC33FJ12GP201/202 PLL BLOCK DIAGRAM

# EQUATION 8-3: XT WITH PLL MODE EXAMPLE

$$F_{CY} = \frac{F_{OSC}}{2} = \frac{1}{2} \left( \frac{10000000 \cdot 32}{2 \cdot 2} \right) = 40 \text{ MIPS}$$

| U-0           | U-0          | R/W-0             | R/W-0   | R/W-0             | U-0  | U-0            | U-0   |

|---------------|--------------|-------------------|---------|-------------------|------|----------------|-------|

| _             | —            | T3MD              | T2MD    | T1MD              | _    |                | _     |

| bit 15        |              |                   |         |                   |      |                | bit   |

|               |              |                   |         |                   |      |                |       |

| R/W-0         | U-0          | R/W-0             | U-0     | R/W-0             | U-0  | U-0            | R/W-0 |

| I2C1MD        |              | U1MD              | —       | SPI1MD            | —    |                | AD1MD |

| bit 7         |              |                   |         |                   |      |                | bit   |

|               |              |                   |         |                   |      |                |       |

| Legend:       |              |                   |         |                   |      |                |       |

| R = Readabl   |              | W = Writable      |         | U = Unimplem      |      |                |       |

| -n = Value at | POR          | '1' = Bit is set  |         | '0' = Bit is clea | ared | x = Bit is unk | nown  |

|               |              |                   |         |                   |      |                |       |

| bit 15-14     | -            | nted: Read as '   |         |                   |      |                |       |

| bit 13        |              | r3 Module Disal   |         |                   |      |                |       |

|               |              | nodule is enable  |         |                   |      |                |       |

| bit 12        |              | r2 Module Disal   |         |                   |      |                |       |

|               | 1 = Timer2 r | module is disabl  | ed      |                   |      |                |       |

|               | 0 = Timer2 r | module is enable  | ed      |                   |      |                |       |

| bit 11        | T1MD: Time   | er1 Module Disal  | ole bit |                   |      |                |       |

|               | -            | nodule is disabl  |         |                   |      |                |       |

|               |              | nodule is enable  |         |                   |      |                |       |

| bit 10-8      | -            | nted: Read as '   |         |                   |      |                |       |

| bit 7         | -            | C1 Module Disal   |         |                   |      |                |       |

|               |              | dule is enabled   |         |                   |      |                |       |

| bit 6         | Unimpleme    | nted: Read as '   | 0'      |                   |      |                |       |

| bit 5         | -            | T1 Module Disa    |         |                   |      |                |       |

|               | 1 = UART1    | module is disabl  | ed      |                   |      |                |       |

|               | 0 = UART1    | module is enabl   | ed      |                   |      |                |       |

| bit 4         | Unimpleme    | nted: Read as '   | 0'      |                   |      |                |       |

| bit 3         |              | PI1 Module Disa   |         |                   |      |                |       |

|               |              | odule is disabled |         |                   |      |                |       |

| bit 2-1       |              | nted: Read as '   | 0'      |                   |      |                |       |

| bit 0         | -            | C1 Module Disa    |         |                   |      |                |       |

|               |              | nodule is disable |         |                   |      |                |       |

|               |              |                   |         |                   |      |                |       |

**Note 1:** PCFGx bits have no effect if the ADC module is disabled by setting this bit. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

| U-0           | U-0                 | U-0              | R/W-1          | R/W-1                                   | R/W-1           | R/W-1        | R/W-1 |  |  |

|---------------|---------------------|------------------|----------------|-----------------------------------------|-----------------|--------------|-------|--|--|

| _             |                     |                  |                | INT1R<4:0>                              |                 |              |       |  |  |

| bit 15        |                     |                  |                |                                         |                 |              | bit 8 |  |  |

|               |                     |                  |                |                                         |                 |              |       |  |  |

| U-0           | U-0                 | U-0              | U-0            | U-0                                     | U-0             | U-0          | U-0   |  |  |

|               | —                   | —                | _              |                                         |                 | —            | —     |  |  |

| bit 7         |                     |                  |                |                                         |                 |              | bit 0 |  |  |

|               |                     |                  |                |                                         |                 |              |       |  |  |

| Legend:       |                     |                  |                |                                         |                 |              |       |  |  |

| R = Readable  | e bit               | W = Writable     | bit            | U = Unimplemented bit, read as '0'      |                 |              |       |  |  |

| -n = Value at | POR                 | '1' = Bit is set |                | '0' = Bit is cleared x = Bit is unknown |                 |              |       |  |  |

|               |                     |                  |                |                                         |                 |              |       |  |  |

| bit 15-13     | Unimplemen          | ted: Read as 'd  | )'             |                                         |                 |              |       |  |  |

| bit 12-8      | INT1R<4:0>:         | Assign Externa   | al Interrupt 1 | (INTR1) to the                          | corresponding F | RPn pin bits |       |  |  |

|               | 11111 <b>= Inpu</b> | it tied to Vss   |                |                                         |                 |              |       |  |  |

|               | 01111 <b>= Inpu</b> | it tied to RP15  |                |                                         |                 |              |       |  |  |

|               | •                   |                  |                |                                         |                 |              |       |  |  |

|               | •                   |                  |                |                                         |                 |              |       |  |  |

|               | •                   |                  |                |                                         |                 |              |       |  |  |

|               | 00001 <b>= Inpu</b> |                  |                |                                         |                 |              |       |  |  |

|               | 00000 = Inpu        |                  |                |                                         |                 |              |       |  |  |

| bit 7-0       | Unimplemen          | ted: Read as '   | )'             |                                         |                 |              |       |  |  |

|               |                     |                  |                |                                         |                 |              |       |  |  |

### REGISTER 10-1: RPINR0: PERIPHERAL PIN SELECT INPUT REGISTER 0

### REGISTER 10-13: RPOR3: PERIPHERAL PIN SELECT OUTPUT REGISTERS 3

| U-0          | U-0        | U-0              | R/W-0 | R/W-0                                   | R/W-0           | R/W-0             | R/W-0    |

|--------------|------------|------------------|-------|-----------------------------------------|-----------------|-------------------|----------|

| _            | —          | —                |       |                                         | RP7R<4:0>       |                   |          |

| bit 15       |            |                  |       |                                         |                 |                   | bit 8    |

|              |            |                  |       |                                         |                 |                   |          |

| U-0          | U-0        | U-0              | R/W-0 | R/W-0                                   | R/W-0           | R/W-0             | R/W-0    |

| —            | —          | —                |       |                                         | RP6R<4:0>       |                   |          |

| bit 7        |            |                  |       |                                         |                 |                   | bit 0    |

|              |            |                  |       |                                         |                 |                   |          |

| Legend:      |            |                  |       |                                         |                 |                   |          |

| R = Readab   | le bit     | W = Writable     | bit   | U = Unimpler                            | nented bit, rea | d as '0'          |          |

| -n = Value a | t POR      | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                 |                   |          |

|              |            |                  |       |                                         |                 |                   |          |

| bit 15-13    | Unimplemen | ted: Read as 'o  | כי    |                                         |                 |                   |          |

| bit 12-8     |            | Peripheral Outr  |       | s Assigned to F                         | RP7 Output Pir  | i bits (see Table | 10-2 for |

| bit 7-5      | Unimplemen | ted: Read as '   | כ'    |                                         |                 |                   |          |

|              |            |                  |       |                                         |                 |                   |          |

bit 4-0 **RP6R<4:0>:** Peripheral Output Function is Assigned to RP6 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-14: RPOR4: PERIPHERAL PIN SELECT OUTPUT REGISTERS 0

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP9R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP8R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP9R<4:0>:** Peripheral Output Function is Assigned to RP9 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP8R<4:0>:** Peripheral Output Function is Assigned to RP8 Output Pin bits (see Table 10-2 for peripheral function numbers)

### REGISTER 10-17: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTERS 7

| U-0             | U-0        | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|------------|------------------|-------|------------------|-----------------|-----------------|-------|

| —               | —          | —                |       |                  | RP15R<4:0       | >               |       |

| bit 15          |            |                  |       |                  |                 |                 | bit 8 |

|                 |            |                  |       | <b>D</b> 4440    | DAALO           | <b>D</b> 444 0  | DAMA  |

| U-0             | U-0        | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| —               | —          | —                |       |                  | RP14R<4:0       | >               |       |

| bit 7           |            |                  |       |                  |                 |                 | bit 0 |

|                 |            |                  |       |                  |                 |                 |       |

| Legend:         |            |                  |       |                  |                 |                 |       |

| R = Readable I  | bit        | W = Writable     | bit   | U = Unimpler     | mented bit, rea | id as '0'       |       |

| -n = Value at P | OR         | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|                 |            |                  |       |                  |                 |                 |       |

| bit 15-13       | Unimplemen | ted: Read as 'd  | )'    |                  |                 |                 |       |

|                 |            |                  |       |                  |                 |                 |       |

bit 12-8 **RP15R<4:0>:** Peripheral Output Function is Assigned to RP15 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP14R<4:0>:** Peripheral Output Function is Assigned to RP14 Output Pin bits (see Table 10-2 for peripheral function numbers)

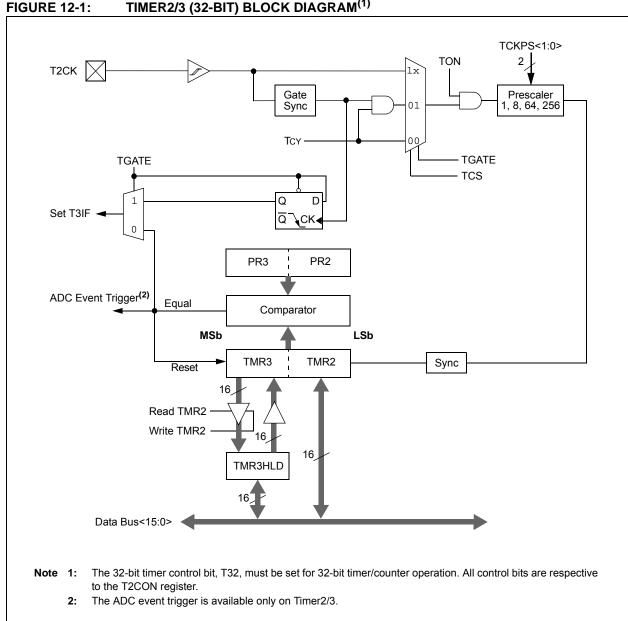

#### TIMER2/3 (32-BIT) BLOCK DIAGRAM<sup>(1)</sup> FIGURE 12-1:

# REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | S: Start bit                                                                                                                                                                                                                                 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul>                       |

| bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as $l^2C$ slave)                                                                                                                                                                      |

| 5112  | <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ul>             |

| bit 1 | <b>RBF:</b> Receive Buffer Full Status bit<br>1 = Receive complete, I2CxRCV is full<br>0 = Receive not complete, I2CxRCV is empty<br>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br>reads I2CxRCV. |

| bit 0 | <b>TBF:</b> Transmit Buffer Full Status bit<br>1 = Transmit in progress, I2CxTRN is full<br>0 = Transmit complete, I2CxTRN is empty<br>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.         |

| R/W-0                 | U-0                                                                                                                                                           | R/W-0                                               | R/W-0               | R/W-0            | U-0                        | R/W-0           | R/W-0           |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------|------------------|----------------------------|-----------------|-----------------|--|

| UARTEN <sup>(1)</sup> | _                                                                                                                                                             | USIDL                                               | IREN <sup>(2)</sup> | RTSMD            | _                          | UEN             | <1:0>           |  |

| bit 15                |                                                                                                                                                               |                                                     |                     |                  |                            |                 | bit 8           |  |

| R/W-0 HC              | R/W-0                                                                                                                                                         | R/W-0 HC                                            | R/W-0               | R/W-0            | R/W-0                      | R/W-0           | R/W-0           |  |

| WAKE                  | LPBACK                                                                                                                                                        | ABAUD                                               | URXINV              | BRGH             | PDSEI                      | -               | STSEL           |  |

| bit 7                 |                                                                                                                                                               | 1.87.68                                             | oroarte             | Bitteri          | 1 002                      |                 | bit (           |  |

|                       |                                                                                                                                                               |                                                     |                     |                  |                            |                 |                 |  |

| Legend:               |                                                                                                                                                               | HC = Hardwa                                         |                     |                  |                            |                 |                 |  |

| R = Readable bit      |                                                                                                                                                               | W = Writable bit U = Unimplemented bit, read as '0' |                     |                  |                            |                 |                 |  |

| -n = Value at POR     |                                                                                                                                                               | '1' = Bit is set                                    |                     | '0' = Bit is cle | eared                      | x = Bit is unkr | iown            |  |

| bit 15                | UARTEN: UA                                                                                                                                                    | ARTx Enable bi                                      | t(1)                |                  |                            |                 |                 |  |

|                       |                                                                                                                                                               |                                                     |                     |                  | y UARTx as defi            |                 |                 |  |

|                       | <ul> <li>UARTx is disabled; all UARTx pins are controlled by port latches; UARTx power consumption<br/>minimal</li> </ul>                                     |                                                     |                     |                  |                            |                 |                 |  |

| bit 14                | Unimplemen                                                                                                                                                    | ted: Read as '                                      | 0'                  |                  |                            |                 |                 |  |

| bit 13                | USIDL: Stop in Idle Mode bit                                                                                                                                  |                                                     |                     |                  |                            |                 |                 |  |

|                       | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul>                         |                                                     |                     |                  |                            |                 |                 |  |

| bit 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup>                                                                                         |                                                     |                     |                  |                            |                 |                 |  |

|                       | 1 = IrDA <sup>®</sup> en                                                                                                                                      | coder and dec                                       | oder enabled        |                  |                            |                 |                 |  |

| bit 11                | <b>RTSMD:</b> Mode Selection for $\overline{\text{UxRTS}}$ Pin bit                                                                                            |                                                     |                     |                  |                            |                 |                 |  |

|                       | 1 = UxRTS p                                                                                                                                                   | oin in Simplex n                                    | node                |                  |                            |                 |                 |  |

| bit 10                | 0 = UxRTS pin in Flow Control mode<br>Unimplemented: Read as '0'                                                                                              |                                                     |                     |                  |                            |                 |                 |  |

| bit 9-8               | UEN<1:0>: UARTx Enable bits                                                                                                                                   |                                                     |                     |                  |                            |                 |                 |  |

|                       | 11 = UxTX, UxRX and BCLK pins are enabled and used; $\overline{\text{UxCTS}}$ pin controlled by port latches                                                  |                                                     |                     |                  |                            |                 |                 |  |

|                       | 10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used                                                                                                    |                                                     |                     |                  |                            |                 |                 |  |

|                       | 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin controlled by port latches                                                                     |                                                     |                     |                  |                            |                 |                 |  |

|                       | 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/BCLK pins controlled by<br>port latches                                                         |                                                     |                     |                  |                            |                 |                 |  |

| bit 7                 | WAKE: Wake-up on Start bit Detect During Sleep Mode Enable bit                                                                                                |                                                     |                     |                  |                            |                 |                 |  |

|                       | <ul> <li>1 = UARTx will continue to sample the UxRX pin; interrupt generated on falling edge; bit cleared<br/>in hardware on following rising edge</li> </ul> |                                                     |                     |                  |                            |                 |                 |  |

|                       | 0 = No wake-up enabled                                                                                                                                        |                                                     |                     |                  |                            |                 |                 |  |

| bit 6                 | LPBACK: UARTx Loopback Mode Select bit                                                                                                                        |                                                     |                     |                  |                            |                 |                 |  |

|                       | 1 = Enable Loopback mode                                                                                                                                      |                                                     |                     |                  |                            |                 |                 |  |

|                       | 0 = Loopback mode is disabled                                                                                                                                 |                                                     |                     |                  |                            |                 |                 |  |

| bit 5                 | ABAUD: Auto                                                                                                                                                   | o-Baud Enable                                       | bit                 |                  |                            |                 |                 |  |

|                       | before ot                                                                                                                                                     | her data; clear                                     | ed in hardwar       | e upon comple    | ter – requires re<br>etion | ception of a Sy | nc field (0x55  |  |

|                       | 0 = Baud rate                                                                                                                                                 | e measuremen                                        | t disabled or o     | completed        |                            |                 |                 |  |

|                       |                                                                                                                                                               |                                                     | •                   |                  | PIC24H Family F            | Reference Manu  | <i>ual"</i> for |  |

| INTC                  | ormation on ena                                                                                                                                               | wing the UAR                                        |                     | eceive or tran   | smit operation.            |                 |                 |  |

#### **REGISTER 17-1: UXMODE: UARTX MODE REGISTER**

2: This feature is only available for the 16x BRG mode (BRGH = 0).

#### REGISTER 18-4: AD1CHS123: ADC1 INPUT CHANNEL 1, 2, 3 SELECT REGISTER (CONTINUED)

bit 2-1

bit 0

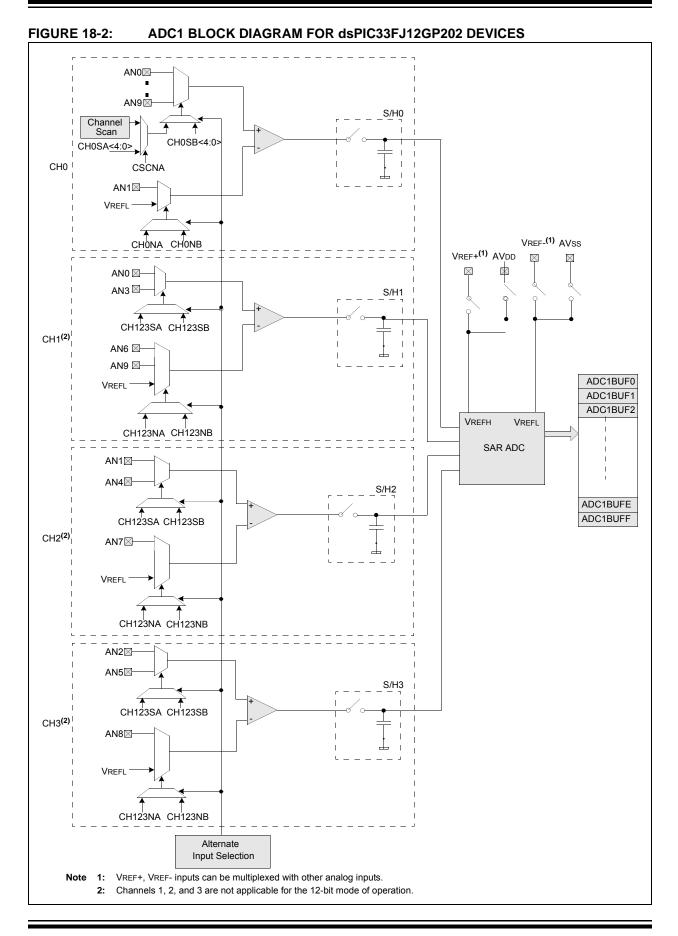

# CH123NA<1:0>: Channel 1, 2, 3 Negative Input Select for Sample A bits dsPIC33FJ12GP201 devices only:

If AD12B = 1:

- 11 = Reserved

- 10 = Reserved

- 01 = Reserved

- 00 = Reserved

#### If AD12B = 0:

- 11 = Reserved

- 10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is not connected

- 01 = CH1, CH2, CH3 negative input is VREF-

- 00 = CH1, CH2, CH3 negative input is VREF-

#### dsPIC33FJ12GP202 devices only:

If AD12B = 1: 11 = Reserved

- 10 = Reserved

- 01 = Reserved

- 00 = Reserved

#### If AD12B = 0:

11 = CH1 negative input is AN9, CH2 and CH3 negative inputs are not connected 10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8 01 = CH1, CH2, CH3 negative input is VREF-00 = CH1, CH2, CH3 negative input is VREF-

CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit

#### dsPIC33FJ12GP201 devices only:

<u>If AD12B = 1:</u> 1 = Reserved 0 = Reserved

#### If AD12B = 0:

1 = CH1 positive input is AN3, CH2 and CH3 positive inputs are not connected

0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2

#### dsPIC33FJ12GP202 devices only:

If AD12B = 1:

1 = Reserved

0 = Reserved

If AD12B = 0:

1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5 0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2

Most instructions are a single word. Certain doubleword instructions were designed to provide all of the required information in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP. The double-word instructions execute in two instruction cycles.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or two-word instruction. Moreover, double-word moves require two cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

| Field           | Description                                                                          |

|-----------------|--------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                      |

| (text)          | Means "content of text"                                                              |

| [text]          | Means "the location addressed by text"                                               |

| { }             | Optional field or operation                                                          |

| <n:m></n:m>     | Register bit field                                                                   |

| .b              | Byte mode selection                                                                  |

| .d              | Double-Word mode selection                                                           |

| .S              | Shadow register select                                                               |

| .W              | Word mode selection (default)                                                        |

| Acc             | One of two accumulators {A, B}                                                       |

| AWB             | Accumulator write back destination address register ∈ {W13, [W13] + = 2}             |

| bit4            | 4-bit bit selection field (used in word addressed instructions) ∈ {015}              |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                 |

| Expr            | Absolute address, label or expression (resolved by the linker)                       |

| f               | File register address ∈ {0x00000x1FFF}                                               |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                 |

| lit4            | 4-bit unsigned literal ∈ {015}                                                       |

| lit5            | 5-bit unsigned literal ∈ {031}                                                       |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                      |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode               |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                   |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                   |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSb must be '0'                                |

| None            | Field does not require an entry, may be blank                                        |

| OA, OB, SA, SB  | DSP Status bits: ACCA Overflow, ACCB Overflow, ACCA Saturate, ACCB Saturate          |

| PC              | Program Counter                                                                      |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                    |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                       |

| Wb              | Base W register ∈ {W0W15}                                                            |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                    |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] } |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                          |

## TABLE 20-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

# 22.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of dsPIC33FJ12GP201/202 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the dsPIC33FJ12GP201/202 family are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

# Absolute Maximum Ratings<sup>(1)</sup>

| Ambient temperature under bias                                                | 40°C to +125°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                            | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(4)}$  | -0.3V to +5.6V       |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(4)}$    | 0.3V to (VDD + 0.3V) |

| Maximum current out of Vss pin                                                |                      |

| Maximum current into VDD pin <sup>(2)</sup>                                   | 250 mA               |

| Maximum output current sunk by any I/O pin <sup>(3)</sup>                     | 4 mA                 |

| Maximum output current sourced by any I/O pin <sup>(3)</sup>                  | 4 mA                 |

| Maximum current sunk by all ports                                             | 200 mA               |

| Maximum current sourced by all ports <sup>(2)</sup>                           | 200 mA               |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 22-2).

- **3:** Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx, and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.