Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 28-VQFN Exposed Pad                                                             |

| Supplier Device Package    | 28-QFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp202-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# dsPIC33FJ12GP201/202 Product Families

The device names, pin counts, memory sizes, and peripheral availability of each family are listed below, followed by their pinout diagrams.

|                  |      | ory                             |                |                    | Ren              | nappa         | ble Per                    | ipher | als                                |     |                   |                    |                |                              |

|------------------|------|---------------------------------|----------------|--------------------|------------------|---------------|----------------------------|-------|------------------------------------|-----|-------------------|--------------------|----------------|------------------------------|

| Device           | Pins | Program Flash Memory<br>(Kbyte) | RAM<br>(Kbyte) | Remappable<br>Pins | 16-bit Timer     | Input Capture | Output Compare<br>Std. PWM | UART  | External Interrupts <sup>(2)</sup> | IdS | 10-Bit/12-Bit ADC | I <sup>2</sup> Стм | I/O Pins (Max) | Packages                     |

| dsPIC33FJ12GP201 | 18   | 12                              | 1              | 8                  | 3 <sup>(1)</sup> | 4             | 2                          | 1     | 3                                  | 1   | 1 ADC,<br>6 ch    | 1                  | 13             | PDIP<br>SOIC                 |

| dsPIC33FJ12GP202 | 28   | 12                              | 1              | 16                 | 3 <sup>(1)</sup> | 4             | 2                          | 1     | 3                                  | 1   | 1 ADC,<br>10 ch   | 1                  | 21             | SPDIP<br>SOIC<br>SSOP<br>QFN |

# TABLE 1: dsPIC33FJ12GP201/202 CONTROLLER FAMILIES

Note 1: Only two out of three timers are remappable.

**2:** Only two out of three interrupts are remappable.

# **Table of Contents**

| 1.0   | Device Overview                                                       |       |

|-------|-----------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers | 15    |

| 3.0   | CPU                                                                   |       |

| 4.0   | Memory Organization                                                   | 31    |

| 5.0   | Flash Program Memory                                                  | 55    |

| 6.0   | Resets                                                                | 61    |

| 7.0   | Interrupt Controller                                                  | 69    |

| 8.0   | Oscillator Configuration                                              | 97    |

| 9.0   | Power-Saving Features                                                 | . 107 |

| 10.0  | I/O Ports                                                             | . 111 |

| 11.0  | Timer1                                                                | . 129 |

| 12.0  | Timer2/3 Feature                                                      | . 131 |

| 13.0  | Input Capture                                                         | . 137 |

| 14.0  | Output Compare                                                        | . 139 |

| 15.0  | Serial Peripheral Interface (SPI)                                     | . 143 |

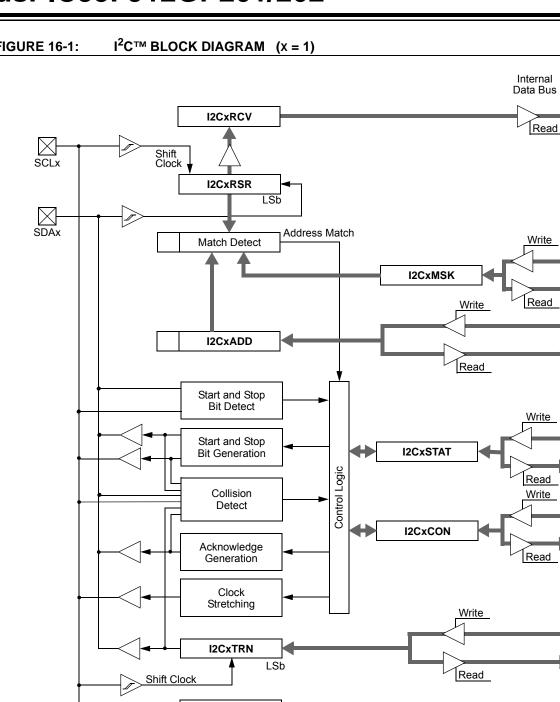

| 16.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                         | . 149 |

| 17.0  | Universal Asynchronous Receiver Transmitter (UART)                    | . 157 |

| 18.0  | 10-bit/12-bit Analog-to-Digital Converter (ADC)                       | . 163 |

| 19.0  | Special Features                                                      | . 175 |

| 20.0  | Instruction Set Summary                                               | . 181 |

| 21.0  | Development Support                                                   | . 189 |

| 22.0  | Electrical Characteristics                                            | . 193 |

| 23.0  | Packaging Information                                                 | . 237 |

| Appe  | ndix A: Revision History                                              | . 245 |

| Index |                                                                       | 253   |

| The N | /icrochip Web Site                                                    | . 257 |

| Custo | mer Change Notification Service                                       | . 257 |

| Custo | mer Support                                                           | . 257 |

| Read  | er Response                                                           | . 258 |

| Produ | Ict Identification System                                             | . 259 |

|       |                                                                       |       |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

## **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

## Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

## **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

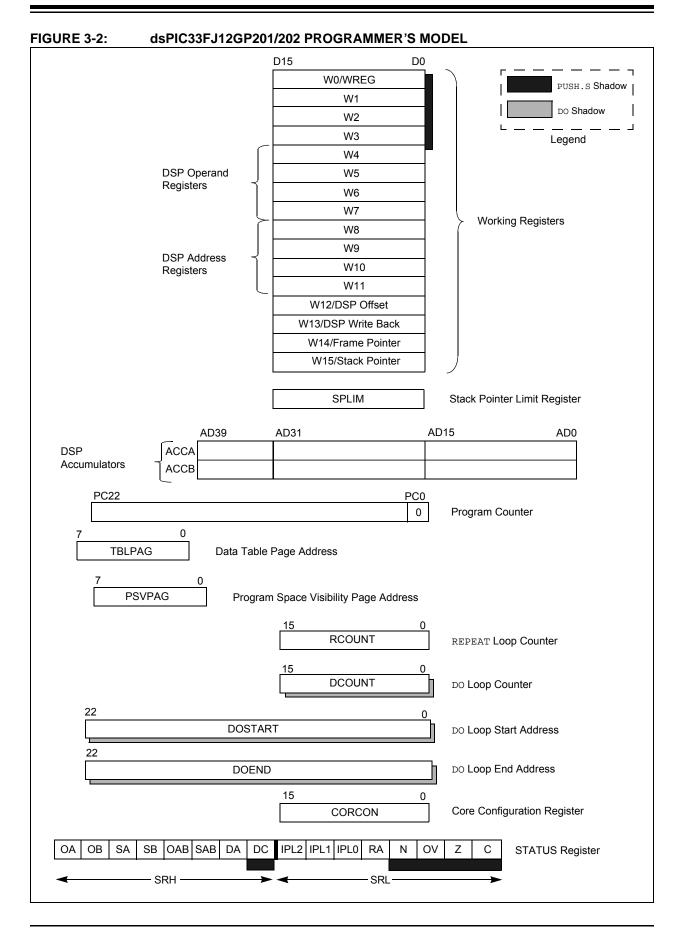

| TABLE 4-1: | <b>CPU CORE REGISTERS MAP</b> |

|------------|-------------------------------|

|------------|-------------------------------|

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7         | Bit 6  | Bit 5     | Bit 4          | Bit 3        | Bit 2       | Bit 1   | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|---------|---------------|---------------|--------|-----------|----------------|--------------|-------------|---------|-------|---------------|

| WREG0    | 0000        |        |        |        |        |        |        |         | Working Re    | gister 0      |        |           |                |              |             |         |       | 0000          |

| WREG1    | 0002        |        |        |        |        |        |        |         | Working Re    | gister 1      |        |           |                |              |             |         |       | 0000          |

| WREG2    | 0004        |        |        |        |        |        |        |         | Working Re    | gister 2      |        |           |                |              |             |         |       | 0000          |

| WREG3    | 0006        |        |        |        |        |        |        |         | Working Re    | gister 3      |        |           |                |              |             |         |       | 0000          |

| WREG4    | 0008        |        |        |        |        |        |        |         | Working Re    | gister 4      |        |           |                |              |             |         |       | 0000          |

| WREG5    | 000A        |        |        |        |        |        |        |         | Working Re    | gister 5      |        |           |                |              |             |         |       | 0000          |

| WREG6    | 000C        |        |        |        |        |        |        |         | Working Re    | gister 6      |        |           |                |              |             |         |       | 0000          |

| WREG7    | 000E        |        |        |        |        |        |        |         | Working Re    | gister 7      |        |           |                |              |             |         |       | 0000          |

| WREG8    | 0010        |        |        |        |        |        |        |         | Working Re    | gister 8      |        |           |                |              |             |         |       | 0000          |

| WREG9    | 0012        |        |        |        |        |        |        |         | Working Re    | gister 9      |        |           |                |              |             |         |       | 0000          |

| WREG10   | 0014        |        |        |        |        |        |        |         | Working Re    | gister 10     |        |           |                |              |             |         |       | 0000          |

| WREG11   | 0016        |        |        |        |        |        |        |         | Working Re    | gister 11     |        |           |                |              |             |         |       | 0000          |

| WREG12   | 0018        |        |        |        |        |        |        |         | Working Re    | gister 12     |        |           |                |              |             |         |       | 0000          |

| WREG13   | 001A        |        |        |        |        |        |        |         | Working Re    | gister 13     |        |           |                |              |             |         |       | 0000          |

| WREG14   | 001C        |        |        |        |        |        |        | ,       | Working Re    | gister 14     |        |           |                |              |             |         |       | 0000          |

| WREG15   | 001E        |        |        |        |        |        |        |         | Working Re    | gister 15     |        |           |                |              |             |         |       | 0800          |

| SPLIM    | 0020        |        |        |        |        |        |        | Stad    | ck Pointer Li | mit Register  | •      |           |                |              |             |         |       | xxxx          |

| ACCAL    | 0022        |        |        |        |        |        |        | Accum   | ulator A Low  | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCAH    | 0024        |        |        |        |        |        |        | Accum   | ulator A High | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCAU    | 0026        |        |        |        |        |        |        | Accumu  | lator A Uppe  | er Word Reg   | jister |           |                |              |             |         |       | 0000          |

| ACCBL    | 0028        |        |        |        |        |        |        | Accum   | ulator B Low  | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCBH    | 002A        |        |        |        |        |        |        | Accum   | ulator B High | Word Regi     | ster   |           |                |              |             |         |       | 0000          |

| ACCBU    | 002C        |        |        |        |        |        |        | Accumu  | lator B Uppe  | er Word Reg   | jister |           |                |              |             |         |       | 0000          |

| PCL      | 002E        |        |        |        |        |        |        | Program | Counter Lo    | w Word Reg    | gister |           |                |              |             |         |       | 0000          |

| PCH      | 0030        | —      | _      | —      | _      | _      | _      | _       | _             |               |        | Progra    | m Counter      | High Byte R  | legister    |         |       | 0000          |

| TBLPAG   | 0032        | —      | —      | _      | —      | _      | _      | _       | —             |               |        | Table F   | Page Addre     | ss Pointer R | Register    |         |       | 0000          |

| PSVPAG   | 0034        | _      | _      | _      | _      | _      | _      | -       | _             |               | Progra | am Memory | v Visibility P | age Address  | s Pointer R | egister |       | 0000          |

| RCOUNT   | 0036        |        |        |        |        |        |        | Repe    | at Loop Cou   | inter Registe | er     |           |                |              |             |         |       | xxxx          |

| DCOUNT   | 0038        |        |        |        |        |        |        |         | DCOUNT        | <15:0>        |        |           |                |              |             |         |       | xxxx          |

| DOSTARTL | 003A        |        |        |        |        |        |        | DOS     | TARTL<15:     | 1>            |        |           |                |              |             |         | 0     | xxxx          |

| DOSTARTH | 003C        | _      | _      | _      | _      | _      | _      | _       | _             | —             | _      |           |                | DOSTAF       | RTH<5:0>    |         |       | 00xx          |

| DOENDL   | 003E        |        |        |        |        |        |        | DOE     | NDL<15:1      | >             |        |           |                |              |             |         | 0     | xxxx          |

| DOENDH   | 0040        | _      | —      | _      | —      | —      | —      | _       | _             | _             | —      |           |                | DOE          | NDH         |         |       | 00xx          |

| SR       | 0042        | OA     | OB     | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2          | IPL1   | IPL0      | RA             | N            | OV          | Z       | С     | 0000          |

| CORCON   | 0044        | _      | —      | _      | US     | EDT    |        | DL<2:0> |               | SATA          | SATB   | SATDW     | ACCSAT         | IPL3         | PSV         | RND     | IF    | 0020          |

| MODCON   | 0046        | XMODEN | YMODEN | _      | _      |        | BWN    | /<3:0>  |               |               | YWM    | <3:0>     |                |              | XWN         | 1<3:0>  |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-16: PORTA REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|--------|---------------|

| TRISA     | 02C0 | —      | —      | -      | —      | —      | -      | -     | —     |       |       | —     | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | 001F          |

| PORTA     | 02C2 | -      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA      | 02C4 | -      | _      | _      | _      | _      | _      | _     | _     | _     | _     | _     | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA      | 02C6 | —      | —      | _      | _      | _      | _      | _     | _     | _     | _     | _     | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-17: PORTB REGISTER MAP FOR dsPIC33FJ12GP202

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C8 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02CA | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CC | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

| ODCB      | 02CE | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-18: PORTB REGISTER MAP FOR dsPIC33FJ12GP201

| File Name | Addr | Bit 15  | Bit 14  | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|--------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|---------------|

| TRISB     | 02C8 | TRISB15 | TRISB14 | _      | _      | _      | _      | TRISB9 | TRISB8 | TRISB7 | _     | _     | TRISB4 | _     | _     | TRISB1 | TRISB0 | C393          |

| PORTB     | 02CA | RB15    | RB14    | _      | _      | _      | _      | RB9    | RB8    | RB7    | _     | _     | RB4    | _     | _     | RB1    | RB0    | xxxx          |

| LATB      | 02CC | LATB15  | LATB14  | _      |        | _      | _      | LATB9  | LATB8  | LATB7  | _     | _     | LATB4  | _     | _     | LATB1  | LATB0  | xxxx          |

| ODCB      | 02CE | ODCB15  | ODCB14  | _      | _      | _      | _      | ODCB9  | ODCB8  | ODCB7  | _     | _     | ODCB4  | _     | _     | ODCB1  | ODCB0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## TABLE 4-19: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12   | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3 | Bit 2    | Bit 1   | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|-----------|----------|--------|--------|-----------|-------|---------|--------|--------|------------|-------|----------|---------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | _         |          | _      | _      | CM        | VREGS | EXTR    | SWR    | SWDTEN | WDTO       | SLEEP | IDLE     | BOR     | POR   | <sub>xxxx</sub> (1) |

| OSCCON    | 0742 | _      | (      | COSC<2:0> | >        | —      | 1      | NOSC<2:0> | >     | CLKLOCK | IOLOCK | LOCK   | _          | CF    | -        | LPOSCEN | OSWEN | <sub>0300</sub> (2) |

| CLKDIV    | 0744 | ROI    | [      | DOZE<2:0> | <b>`</b> | DOZEN  | FI     | RCDIV<2:0 | >     | PLLPOS  | T<1:0> | _      |            | F     | PLLPRE<4 | :0>     |       | 3040                |

| PLLFBD    | 0746 |        | —      | _         |          | —      | —      | _         |       |         |        | F      | PLLDIV<8:0 | )>    |          |         |       | 0030                |

| OSCTUN    | 0748 |        | —      | _         |          | —      | —      | _         | —     |         | _      |        |            | TUN   | I<5:0>   |         |       | 0000                |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: RCON register Reset values dependent on the type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and by the type of Reset.

#### R/W-0 U-0 R/W-0 R/W-0 U-0 U-0 U-0 R/W-0 IOPUWR TRAPR VREGS CM bit 15 bit 8 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-1 R/W-1 SWDTEN<sup>(2)</sup> EXTR SWR WDTO SLEEP IDLE BOR POR bit 7 bit 0 Legend: R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' -n = Value at POR '0' = Bit is cleared x = Bit is unknown '1' = Bit is set bit 15 TRAPR: Trap Reset Flag bit 1 = A Trap Conflict Reset has occurred 0 = A Trap Conflict Reset has not occurred bit 14 IOPUWR: Illegal Opcode or Uninitialized W Access Reset Flag bit 1 = An illegal opcode detection, an illegal address mode or uninitialized W register used as an Address Pointer caused a Reset 0 = An illegal opcode or uninitialized W Reset has not occurred bit 13-10 Unimplemented: Read as '0' bit 9 CM: Configuration Mismatch Flag bit 1 = A configuration mismatch Reset has occurred. 0 = A configuration mismatch Reset has NOT occurred. bit 8 VREGS: Voltage Regulator Standby During Sleep bit 1 = Voltage regulator is active during Sleep 0 = Voltage regulator goes into Standby mode during Sleep bit 7 EXTR: External Reset (MCLR) Pin bit 1 = A Master Clear (pin) Reset has occurred 0 = A Master Clear (pin) Reset has not occurred bit 6 SWR: Software Reset (Instruction) Flag bit 1 = A RESET instruction has been executed 0 = A RESET instruction has not been executed bit 5 SWDTEN: Software Enable/Disable of WDT bit<sup>(2)</sup> 1 = WDT is enabled 0 = WDT is disabled bit 4 WDTO: Watchdog Timer Time-out Flag bit 1 = WDT time-out has occurred 0 = WDT time-out has not occurred bit 3 SLEEP: Wake-up from Sleep Flag bit 1 = Device has been in Sleep mode 0 = Device has not been in Sleep mode bit 2 IDLE: Wake-up from Idle Flag bit 1 = Device was in Idle mode 0 = Device was not in Idle mode

# REGISTER 6-1: RCON: RESET CONTROL REGISTER<sup>(1)</sup>

**Note 1:** All of the Reset status bits can be set or cleared in software. Setting one of these bits in software does not cause a device Reset.

2: If the FWDTEN Configuration bit is '1' (unprogrammed), the WDT is always enabled, regardless of the SWDTEN bit setting.

#### 6.2 POR

A POR circuit ensures the device is reset from poweron. The POR circuit is active until VDD crosses the VPOR threshold and the delay TPOR has elapsed. The delay TPOR ensures the internal device bias circuits become stable.

The device supply voltage characteristics must meet the specified starting voltage and rise rate requirements to generate the POR. Refer to Section 22.0 "Electrical Characteristics" for details.

The POR status bit (POR) in the Reset Control register (RCON<0>) is set to indicate the POR.

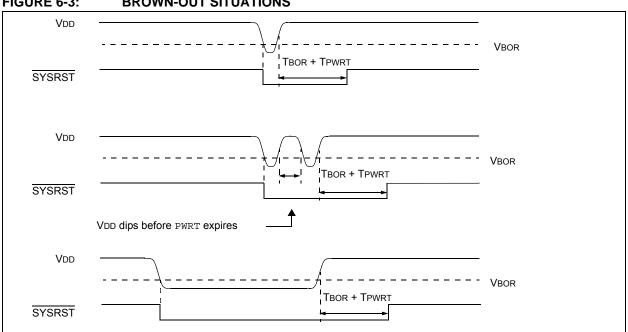

#### 6.3 BOR and PWRT

The on-chip regulator has a BOR circuit that resets the device when the VDD is too low (VDD < VBOR) for proper device operation. The BOR circuit keeps the device in Reset until VDD crosses VBOR threshold and the delay TBOR has elapsed. The delay TBOR ensures the voltage regulator output becomes stable.

FIGURE 6-3: **BROWN-OUT SITUATIONS**  The BOR status bit (BOR) in the Reset Control register (RCON<1>) is set to indicate the BOR.

The device will not run at full speed after a BOR as the VDD should rise to acceptable levels for full-speed operation. The PWRT provides power-up time delay (TPWRT) to ensure that the system power supplies have stabilized at the appropriate levels for full-speed operation before the SYSRST is released.

The power-up timer delay (TPWRT) is programmed by the Power-on Reset Timer Value Select bits (FPWRT<2:0>) in the POR Configuration register (FPOR<2:0>), which provides eight settings (from 0 ms to 128 ms). Refer to Section 19.0 "Special Features" for further details.

Figure 6-3 shows the typical brown-out scenarios. The Reset delay (TBOR + TPWRT) is initiated each time VDD rises above the VBOR trip point.

# REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0           | R/W-0                                                      | R/W-0                                                         | R/W-0                                             | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|-----------------|------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------|------------------|------------------|-----------------|-------|

| NSTDIS          | OVAERR                                                     | OVBERR                                                        | COVAERR                                           | COVBERR          | OVATE            | OVBTE           | COVTE |

| bit 15          |                                                            |                                                               |                                                   |                  |                  |                 | bit 8 |

|                 |                                                            |                                                               |                                                   |                  |                  |                 |       |

| R/W-0           | R/W-0                                                      | U-0                                                           | R/W-0                                             | R/W-0            | R/W-0            | R/W-0           | U-0   |

| SFTACERR        | DIV0ERR                                                    |                                                               | MATHERR                                           | ADDRERR          | STKERR           | OSCFAIL         |       |

| bit 7           |                                                            |                                                               |                                                   |                  |                  |                 | bit 0 |

| Legend:         |                                                            |                                                               |                                                   |                  |                  |                 |       |

| R = Readable    | hit                                                        | W = Writable                                                  | hit                                               | l I = Unimpler   | nented bit, read | las '0'         |       |

| -n = Value at F |                                                            | '1' = Bit is set                                              |                                                   | '0' = Bit is cle |                  | x = Bit is unkn | own   |

|                 |                                                            |                                                               |                                                   |                  |                  |                 |       |

| bit 15          | NSTDIS: Inte                                               | rrupt Nesting D                                               | isable bit                                        |                  |                  |                 |       |

|                 |                                                            | nesting is disab                                              |                                                   |                  |                  |                 |       |

|                 | •                                                          | nesting is enab                                               |                                                   |                  |                  |                 |       |

| bit 14          |                                                            | cumulator A Ov<br>caused by ove                               | •                                                 | 0                |                  |                 |       |

|                 | •                                                          | not caused by                                                 |                                                   |                  |                  |                 |       |

| bit 13          |                                                            | cumulator B O                                                 |                                                   |                  |                  |                 |       |

|                 |                                                            | caused by ove                                                 |                                                   |                  |                  |                 |       |

|                 | •                                                          | not caused by                                                 |                                                   |                  |                  |                 |       |

| bit 12          |                                                            | ccumulator A (                                                | -                                                 | =                | -                |                 |       |

|                 |                                                            | caused by cata<br>not caused by                               |                                                   |                  |                  |                 |       |

| bit 11          | •                                                          | Accumulator B                                                 | •                                                 |                  |                  |                 |       |

|                 | •                                                          | caused by cata                                                | •                                                 |                  |                  |                 |       |

|                 |                                                            | not caused by                                                 | -                                                 |                  | umulator B       |                 |       |

| bit 10          |                                                            | mulator A Ove                                                 | -                                                 | able bit         |                  |                 |       |

|                 | ⊥ = Trap over<br>0 = Trap disal                            | flow of Accumu<br>bled                                        | Jiator A                                          |                  |                  |                 |       |

| bit 9           |                                                            | imulator B Ove                                                | •                                                 | able bit         |                  |                 |       |

|                 | 1 = Trap over<br>0 = Trap disal                            | flow of Accumu<br>bled                                        | ulator B                                          |                  |                  |                 |       |

| bit 8           | COVTE: Cata                                                | strophic Overfl                                               | ow Trap Enab                                      | le bit           |                  |                 |       |

|                 | 1 = Trap on c<br>0 = Trap disal                            | atastrophic ove<br>bled                                       | erflow of Accur                                   | nulator A or B   | enabled          |                 |       |

| bit 7           | SFTACERR:                                                  | Shift Accumula                                                | itor Error Statu                                  | is bit           |                  |                 |       |

|                 |                                                            | r trap was caus<br>r trap was not o                           |                                                   |                  |                  |                 |       |

| bit 6           | DIV0ERR: Ar                                                | ithmetic Error S                                              | Status bit                                        |                  |                  |                 |       |

|                 |                                                            | r trap was caus                                               |                                                   |                  |                  |                 |       |

|                 | 0 = Math erro                                              | r trap was not o                                              | caused by a di                                    | vide by zero     |                  |                 |       |

| 1.4 F           |                                                            |                                                               |                                                   |                  |                  |                 |       |

| bit 5           | Unimplemen                                                 | ted: Read as '                                                | 0'                                                |                  |                  |                 |       |

| bit 5<br>bit 4  | Unimplemen<br>MATHERR: A                                   | ted: Read as 'o<br>rithmetic Error                            | <sup>o'</sup><br>Status bit                       |                  |                  |                 |       |

|                 | Unimplement<br>MATHERR: A<br>1 = Math erro                 | ted: Read as '                                                | o'<br>Status bit<br>Irred                         |                  |                  |                 |       |

|                 | Unimplemen<br>MATHERR: A<br>1 = Math erro<br>0 = Math erro | t <b>ed:</b> Read as '(<br>withmetic Error<br>r trap has occu | <sup>D'</sup><br>Status bit<br>Irred<br>Doccurred |                  |                  |                 |       |

# TABLE 8-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                 | Oscillator<br>Source | POSCMD<1:0> | FNOSC<2:0> | Note |

|-------------------------------------------------|----------------------|-------------|------------|------|

| Fast RC Oscillator with Divide-by-N (FRCDIVN)   | Internal             | xx          | 111        | 1, 2 |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16) | Internal             | xx          | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                  | Internal             | xx          | 101        | 1    |

| Secondary (Timer1) Oscillator (SOSC)            | Secondary            | xx          | 100        | 1    |

| Primary Oscillator (HS) with PLL (HSPLL)        | Primary              | 10          | 011        |      |

| Primary Oscillator (XT) with PLL (XTPLL)        | Primary              | 01          | 011        |      |

| Primary Oscillator (EC) with PLL (ECPLL)        | Primary              | 00          | 011        | 1    |

| Primary Oscillator (HS)                         | Primary              | 10          | 010        |      |

| Primary Oscillator (XT)                         | Primary              | 01          | 010        |      |

| Primary Oscillator (EC)                         | Primary              | 00          | 010        | 1    |

| Fast RC Oscillator with PLL (FRCPLL)            | Internal             | xx          | 001        | 1    |

| Fast RC Oscillator (FRC)                        | Internal             | xx          | 000        | 1    |

Note 1: OSC2 pin function is determined by the OSCIOFNC Configuration bit.

**2:** This is the default oscillator mode for an unprogrammed (erased) device.

| REGISTER 8-2: CLKDIV: CLOCK DIVISOR REGISTER <sup>(2)</sup> |

|-------------------------------------------------------------|

|-------------------------------------------------------------|

| R/W-0         | R/W-0                                                                                                                                  | R/W-1                                                                                 | R/W-1          | R/W-0                           | R/W-0          | R/W-0               | R/W-0      |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------|---------------------------------|----------------|---------------------|------------|

| ROI           |                                                                                                                                        | DOZE<2:0>                                                                             |                | DOZEN <sup>(1)</sup>            |                | FRCDIV<2:0>         |            |

| bit 15        |                                                                                                                                        |                                                                                       |                |                                 |                |                     | bit 8      |

| R/W-0         | R/W-1                                                                                                                                  | U-0                                                                                   | R/W-0          | R/W-0                           |                | R/W-0               | R/W-0      |

|               |                                                                                                                                        | 0-0                                                                                   | R/W-U          | R/W-0                           | R/W-0          |                     | R/W-U      |

| bit 7         | OST<1:0>                                                                                                                               | _                                                                                     |                |                                 | PLLPRE<4:0     | >                   | bit (      |

| DIL 7         |                                                                                                                                        |                                                                                       |                |                                 |                |                     | bit (      |

| Legend:       |                                                                                                                                        | y = Value set                                                                         | from Configu   | ration bits on PC               | )R             |                     |            |

| R = Readabl   | le bit                                                                                                                                 | W = Writable                                                                          | bit            | U = Unimplem                    | ented bit, rea | d as '0'            |            |

| -n = Value at | POR                                                                                                                                    | '1' = Bit is set                                                                      |                | '0' = Bit is clea               | ared           | x = Bit is unkr     | iown       |

| bit 15        | 1 = Interrupt                                                                                                                          | r on Interrupt bi<br>s will clear the I<br>s have no effec                            | DOZEN bit ar   | nd the processor<br>EN bit      | clock/periphe  | eral clock ratio is | set to 1:1 |

| bit 14-12     | DOZE<2:0>:<br>111 = FcY/12<br>110 = FcY/62<br>101 = FcY/32<br>100 = FcY/16<br>011 = FcY/8<br>010 = FcY/4<br>001 = FcY/2<br>000 = FcY/1 | 4<br>2<br>3                                                                           | ck Reduction   | Select bits                     |                |                     |            |

| bit 11        | 1 = DOZE<2                                                                                                                             | ZE Mode Enabl<br>2:0> field specifi<br>or clock/periphe                               | es the ratio b | etween the peripo forced to 1:1 | pheral clocks  | and the process     | or clocks  |

| bit 10-8      | 111 = FRC d<br>110 = FRC d<br>101 = FRC d<br>100 = FRC d<br>011 = FRC d<br>010 = FRC d<br>001 = FRC d                                  | ivide by 256<br>ivide by 64<br>ivide by 32<br>ivide by 16<br>ivide by 8<br>ivide by 4 |                | or Postscaler bits              | 5              |                     |            |

| bit 7-6       | PLLPOST<1<br>11 = Output/8<br>10 = Reserve<br>01 = Output/4<br>00 = Output/2                                                           | 8<br>ed<br>4 (default)                                                                | Output Divide  | er Select bits (als             | o denoted as   | 'N2', PLL posts     | caler)     |

| bit 5         | Unimplemen                                                                                                                             | ted: Read as '                                                                        | כי             |                                 |                |                     |            |

| bit 4-0       | 11111 = Inpu<br>•<br>•                                                                                                                 | ut/33                                                                                 | Detector Inpu  | ıt Divider bits (alı            | so denoted as  | 'N1', PLL preso     | caler)     |

|               | •<br>00001 = Inpu<br>00000 = Inpu                                                                                                      |                                                                                       |                |                                 |                |                     |            |

- Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

- 2: This register is reset only on a Power-on Reset (POR).

| U-0           | U-0                                                           | R/W-0                                                          | R/W-0   | R/W-0            | U-0             | U-0            | U-0   |  |  |  |

|---------------|---------------------------------------------------------------|----------------------------------------------------------------|---------|------------------|-----------------|----------------|-------|--|--|--|

| _             | —                                                             | T3MD                                                           | T2MD    | T1MD             | _               |                | _     |  |  |  |

| bit 15        |                                                               |                                                                |         |                  |                 |                | bit   |  |  |  |

|               |                                                               |                                                                |         |                  |                 |                |       |  |  |  |

| R/W-0         | U-0                                                           | R/W-0                                                          | U-0     | R/W-0            | U-0             | U-0            | R/W-0 |  |  |  |

| I2C1MD        | _                                                             | U1MD                                                           | —       | SPI1MD           | —               | —              | AD1MD |  |  |  |

| bit 7         |                                                               |                                                                |         |                  |                 |                | bit   |  |  |  |

|               |                                                               |                                                                |         |                  |                 |                |       |  |  |  |

| Legend:       |                                                               |                                                                |         |                  |                 |                |       |  |  |  |

| R = Readabl   |                                                               | W = Writable                                                   |         |                  | nented bit, rea |                |       |  |  |  |

| -n = Value at | POR                                                           | '1' = Bit is set                                               |         | '0' = Bit is cle | ared            | x = Bit is unk | nown  |  |  |  |

|               |                                                               |                                                                | _       |                  |                 |                |       |  |  |  |

| bit 15-14     | -                                                             | nted: Read as '                                                |         |                  |                 |                |       |  |  |  |

| bit 13        |                                                               | r3 Module Disal                                                |         |                  |                 |                |       |  |  |  |

|               |                                                               | nodule is enable                                               | •••     |                  |                 |                |       |  |  |  |

| bit 12        |                                                               | r2 Module Disal                                                |         |                  |                 |                |       |  |  |  |

|               | 1 = Timer2 module is disabled                                 |                                                                |         |                  |                 |                |       |  |  |  |

|               | 0 = Timer2 r                                                  | module is enable                                               | ed      |                  |                 |                |       |  |  |  |

| bit 11        | T1MD: Time                                                    | r1 Module Disal                                                | ole bit |                  |                 |                |       |  |  |  |

|               | 1 = Timer1 module is disabled<br>0 = Timer1 module is enabled |                                                                |         |                  |                 |                |       |  |  |  |

|               |                                                               |                                                                |         |                  |                 |                |       |  |  |  |

| bit 10-8      | -                                                             | nted: Read as '                                                |         |                  |                 |                |       |  |  |  |

| bit 7         | -                                                             | I2C1MD: I2C1 Module Disable bit<br>1 = I2C1 module is disabled |         |                  |                 |                |       |  |  |  |

|               |                                                               | dule is enabled                                                |         |                  |                 |                |       |  |  |  |

| bit 6         | Unimpleme                                                     | nted: Read as '                                                | 0'      |                  |                 |                |       |  |  |  |

| bit 5         | -                                                             | T1 Module Disa                                                 |         |                  |                 |                |       |  |  |  |

|               | 1 = UART1                                                     | module is disabl                                               | ed      |                  |                 |                |       |  |  |  |

|               | 0 = UART1                                                     | module is enabl                                                | ed      |                  |                 |                |       |  |  |  |

| bit 4         | Unimpleme                                                     | nted: Read as '                                                | 0'      |                  |                 |                |       |  |  |  |

| bit 3         | SPI1MD: SPI1 Module Disable bit                               |                                                                |         |                  |                 |                |       |  |  |  |

|               |                                                               | odule is disabled                                              |         |                  |                 |                |       |  |  |  |

| bit 2-1       |                                                               | nted: Read as '                                                | 0'      |                  |                 |                |       |  |  |  |

| bit 0         | -                                                             | C1 Module Disa                                                 |         |                  |                 |                |       |  |  |  |

|               |                                                               |                                                                |         |                  |                 |                |       |  |  |  |

|               | 1 = ADC1 module is disabled<br>0 = ADC1 module is enabled     |                                                                |         |                  |                 |                |       |  |  |  |

**Note 1:** PCFGx bits have no effect if the ADC module is disabled by setting this bit. When the bit is set, all port pins that have been multiplexed with ANx will be in Digital mode.

| Function | RPnR<4:0> | Output Name                          |  |

|----------|-----------|--------------------------------------|--|

| NULL     | 00000     | RPn tied to default port pin         |  |

| U1TX     | 00011     | RPn tied to UART1 Transmit           |  |

| U1RTS    | 00100     | RPn tied to UART1 Ready To Send      |  |

| SDO1     | 00111     | RPn tied to SPI1 Data Output         |  |

| SCK1OUT  | 01000     | RPn tied to SPI1 Clock Output        |  |

| SS1OUT   | 01001     | RPn tied to SPI1 Slave Select Output |  |

| OC1      | 10010     | RPn tied to Output Compare 1         |  |

| OC2      | 10011     | RPn tied to Output Compare 2         |  |

# 10.4.3 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. dsPIC33FJ12GP201/202 devices include three features to prevent alterations to the peripheral map:

- Control register lock sequence

- · Continuous state monitoring

- Configuration bit pin select lock

# 10.4.3.1 Control Register Lock

Under normal operation, writes to the RPINRx and RPORx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK bit (OSCCON<6>). Setting the IOLOCK bit prevents writes to the control registers; clearing the IOLOCK bit allows writes.

To set or clear the IOLOCK bit, a specific command sequence must be executed:

- 1. Write 0x46 to OSCCON<7:0>.

- 2. Write 0x57 to OSCCON<7:0>.

- 3. Clear (or set) the IOLOCK bit as a single operation.

| Note: | MPLAB <sup>®</sup> C30 provides built-in C<br>language functions for unlocking the<br>OSCCON register: |  |  |  |  |  |  |

|-------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|       | builtin_write_OSCCONL(value)<br>builtin_write_OSCCONH(value)                                           |  |  |  |  |  |  |

|       | See the MPLAB IDE help files for more information.                                                     |  |  |  |  |  |  |

Unlike the similar sequence with the oscillator's LOCK bit, IOLOCK remains in one state until changed. This allows all of the peripheral pin selects to be configured

with a single unlock sequence followed by an update to all control registers, then locked with a second lock sequence.

### 10.4.3.2 Continuous State Monitoring

In addition to being protected from direct writes, the contents of the RPINRx and RPORx registers are constantly monitored in hardware by shadow registers. If an unexpected change in any of the registers occurs (such as cell disturbances caused by ESD or other external events), a configuration mismatch Reset will be triggered.

### 10.4.3.3 Configuration Bit Pin Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPINRx and RPORx registers. The IOL1WAY (FOSC<5>) configuration bit blocks the IOLOCK bit from being cleared after it has been set once.

In the default (unprogrammed) state, the IOL1WAY bit is set, restricting users to one write session. Programming IOL1WAY allows user applications unlimited access (with the proper use of the unlock sequence) to the peripheral pin select registers.

## **10.5** Peripheral Pin Select Registers

The dsPIC33FJ12GP201/202 devices implement 17 registers for remappable peripheral configuration:

- Input Remappable Peripheral Registers (9)

- Output Remappable Peripheral Registers (8)

Note: Input and Output register values can only be changed if the IOLOCK bit (OSCCON<6>) = 0. See Section 10.4.3.1 "Control Register Lock" for a specific command sequence.

| U-0          | U-0                          | U-0             | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |  |

|--------------|------------------------------|-----------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|

| _            | —                            | _               |                |                  | IC8R<4:0>       |                 |       |  |  |  |

| bit 15       |                              |                 |                |                  |                 |                 | bit 8 |  |  |  |

|              |                              |                 |                |                  |                 |                 |       |  |  |  |

| U-0          | U-0                          | U-0             | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |  |  |  |

| _            | _                            |                 |                |                  | IC7R<4:0>       |                 |       |  |  |  |

| bit 7        |                              |                 |                |                  |                 |                 | bit ( |  |  |  |

|              |                              |                 |                |                  |                 |                 |       |  |  |  |

| Legend:      |                              |                 |                |                  |                 |                 |       |  |  |  |

| R = Readab   | le bit                       | W = Writable    | bit            | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |  |

| -n = Value a | t POR                        | '1' = Bit is se | t              | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |  |

|              |                              |                 |                |                  |                 |                 |       |  |  |  |

| bit 15-13    | Unimplemen                   | ted: Read as    | 'O'            |                  |                 |                 |       |  |  |  |

| bit 12-8     | -                            |                 |                | to the correspo  | onding pin RPn  | i pin bits      |       |  |  |  |

|              | 11111 = Inpu                 | •               |                |                  |                 |                 |       |  |  |  |

|              |                              | it tied to RP15 |                |                  |                 |                 |       |  |  |  |

|              | •                            |                 |                |                  |                 |                 |       |  |  |  |

|              | •                            |                 |                |                  |                 |                 |       |  |  |  |

|              | •                            |                 |                |                  |                 |                 |       |  |  |  |

|              | 00001 = Input tied to RP1    |                 |                |                  |                 |                 |       |  |  |  |

|              | 00000 <b>= Inp</b> u         |                 |                |                  |                 |                 |       |  |  |  |

| bit 7-5      | -                            | ted: Read as    |                |                  |                 |                 |       |  |  |  |

| bit 4-0      | IC7R<4:0>:                   | Assign Input (  | Capture 7 (IC7 | ) to the corresp | oonding pin RP  | n pin bits      |       |  |  |  |

|              | 11111 <b>= Inp</b> u         |                 |                |                  |                 |                 |       |  |  |  |

|              | 01111 <b>= Inp</b> u         | It tied to RP15 |                |                  |                 |                 |       |  |  |  |

|              | •                            |                 |                |                  |                 |                 |       |  |  |  |

|              | •                            |                 |                |                  |                 |                 |       |  |  |  |

|              | •                            | t tigd to DD1   |                |                  |                 |                 |       |  |  |  |

|              | 00001 = Inpu<br>00000 = Inpu |                 |                |                  |                 |                 |       |  |  |  |

|              | 00000 – mpt                  |                 |                |                  |                 |                 |       |  |  |  |

|              |                              |                 |                |                  |                 |                 |       |  |  |  |

## REGISTER 10-5: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTERS 10

# REGISTER 10-8: RPINR20: PERIPHERAL PIN SELECT INPUT REGISTER 20

| U-0           | U-0                               | U-0                               | R/W-1 | R/W-1            | R/W-1           | R/W-1          | R/W-1 |

|---------------|-----------------------------------|-----------------------------------|-------|------------------|-----------------|----------------|-------|

| _             |                                   | _                                 |       |                  | SCK1R<4:0       | >              |       |

| bit 15        |                                   |                                   |       |                  |                 |                | bit 8 |

|               |                                   |                                   |       |                  |                 |                |       |

| U-0           | U-0                               | U-0                               | R/W-1 | R/W-1            | R/W-1           | R/W-1          | R/W-1 |

|               |                                   |                                   |       |                  | SDI1R<4:0       | >              |       |

| bit 7         |                                   |                                   |       |                  |                 |                | bit ( |

|               |                                   |                                   |       |                  |                 |                |       |

| Legend:       |                                   |                                   | L 11  |                  |                 | (O'            |       |

| R = Readabl   |                                   | W = Writable                      |       |                  | nented bit, rea |                |       |

| -n = Value at | POR                               | '1' = Bit is set                  |       | '0' = Bit is cle | ared            | x = Bit is unk | nown  |

|               | •<br>•<br>00001 = Inpu            |                                   |       |                  |                 |                |       |

| bit 7-5       | 00000 = Inpu                      | it tied to RP0<br>ited: Read as ' | 0'    |                  |                 |                |       |

| bit 4-0       | •                                 | Assign SPI1 E                     |       | 11) to the corre | enondina PPr    | n nin hite     |       |

|               | 11111 <b>= I</b> npu              | -                                 |       |                  |                 | i pin olo      |       |

|               | •                                 |                                   |       |                  |                 |                |       |

|               | •<br>00001 = Inpu<br>00000 = Inpu |                                   |       |                  |                 |                |       |

NOTES:

Reload Control

**BRG Down Counter**

TCY/2

**FIGURE 16-1:**

Write

Read

I2CxBRG

# **19.0 SPECIAL FEATURES**

Note: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

Microchip dsPIC33FJ12GP201/202 devices include several features intended to maximize application flexibility and reliability, and minimize cost through elimination of external components. These are:

- Flexible configuration

- Watchdog Timer (WDT)

- Code Protection and CodeGuard<sup>™</sup> Security

- JTAG Boundary Scan Interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- In-Circuit emulation

# **19.1 Configuration Bits**

dsPIC33FJ12GP201/202 devices provide nonvolatile memory implementation for device configuration bits. Refer to **Section 25. "Device Configuration"** (DS70194) of the *"dsPIC33F/PIC24H Family Reference Manual"*, for more information on this implementation.

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1'), to select various device configurations. These bits are mapped starting at program memory location 0xF80000.

The Device Configuration register map is shown in Table 19-1.

The individual Configuration bit descriptions for the Configuration registers are shown in Table 19-2.

Note that address 0xF80000 is beyond the user program memory space. It belongs to the configuration memory space (0x800000-0xFFFFFF), which can only be accessed using table reads and table writes.

| Address  | Name     | Bit 7  | Bit 6                  | Bit 5   | Bit 4        | Bit 3  | Bit 2      | Bit 1             | Bit 0 |  |

|----------|----------|--------|------------------------|---------|--------------|--------|------------|-------------------|-------|--|

| 0xF80000 | FBS      | —      | —                      | —       | —            |        | BSS<2:0>   |                   | BWRP  |  |

| 0xF80002 | Reserved | _      | —                      | _       | —            | _      | _          |                   |       |  |

| 0xF80004 | FGS      |        | —                      |         | —            |        | GSS<1      | :0>               | GWRP  |  |

| 0xF80006 | FOSCSEL  | IESO   | —                      |         |              | -      | FNC        | )SC<2:0>          | •     |  |

| 0xF80008 | FOSC     | FCKSM  | <1:0>                  | IOL1WAY | —            |        | OSCIOFNC   | SCIOFNC POSCMD<1: |       |  |

| 0xF8000A | FWDT     | FWDTEN | WINDIS                 |         | WDTPRE       |        | WDTPOST    | <3:0>             |       |  |

| 0xF8000C | FPOR     | F      | Reserved <sup>(1</sup> | 1)      | ALTI2C       |        | FPWRT<2:0> |                   |       |  |

| 0xF8000E | FICD     | Reserv | ed <sup>(2)</sup>      | JTAGEN  | —            | -      | _          | ICS<              | :1:0> |  |

| 0xF80010 | FUID0    |        | User Unit ID Byte 0    |         |              |        |            |                   |       |  |

| 0xF80012 | FUID1    |        | User Unit ID Byte 1    |         |              |        |            |                   |       |  |

| 0xF80014 | FUID2    |        | User Unit ID Byte 2    |         |              |        |            |                   |       |  |

| 0xF80016 | FUID3    |        |                        |         | User Unit ID | Byte 3 |            |                   |       |  |

# TABLE 19-1: DEVICE CONFIGURATION REGISTER MAP

**Legend:** — = unimplemented bit, read as '0'.

Note 1: Reserved bits read as '1' and must be programmed as '1'.

2: These bits are reserved for use by development tools and must be programmed as '1'.

# TABLE 22-35:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       | ARACTERIS             | <b>FICS</b>                                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |       |            |                                      |

|--------------|-----------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--------------------------------------|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup> Min Typ <sup>(2)</sup> Max   |                                                                                                                                                                                                                                                                                         | Max | Units | Conditions |                                      |

| SP70         | TscP                  | Maximum SCK Input Frequency                                | —                                                                                                                                                                                                                                                                                       | —   | 11    | MHz        | See Note 3                           |

| SP72         | TscF                  | SCKx Input Fall Time                                       | —                                                                                                                                                                                                                                                                                       | —   |       | ns         | See parameter DO32 and <b>Note 4</b> |

| SP73         | TscR                  | SCKx Input Rise Time                                       | —                                                                                                                                                                                                                                                                                       | _   | _     | ns         | See parameter DO31 and <b>Note 4</b> |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                 | —                                                                                                                                                                                                                                                                                       | _   | _     | ns         | See parameter DO32 and <b>Note 4</b> |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                 | —                                                                                                                                                                                                                                                                                       | _   | _     | ns         | See parameter DO31 and <b>Note 4</b> |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                  | —                                                                                                                                                                                                                                                                                       | 6   | 20    | ns         | —                                    |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge               | 30                                                                                                                                                                                                                                                                                      | _   | _     | ns         | —                                    |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                 | 30                                                                                                                                                                                                                                                                                      | —   |       | ns         | —                                    |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                  | 30                                                                                                                                                                                                                                                                                      | _   |       | ns         | —                                    |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow to SCKx \uparrow or SCKx Input$ | 120                                                                                                                                                                                                                                                                                     | _   | _     | ns         | _                                    |