Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                           |

| Number of I/O              | 21                                                                              |

| Program Memory Size        | 12KB (12K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 1K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 10x12b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Through Hole                                                                    |

| Package / Case             | 28-DIP (0.300", 7.62mm)                                                         |

| Supplier Device Package    | 28-SPDIP                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp202-i-sp |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

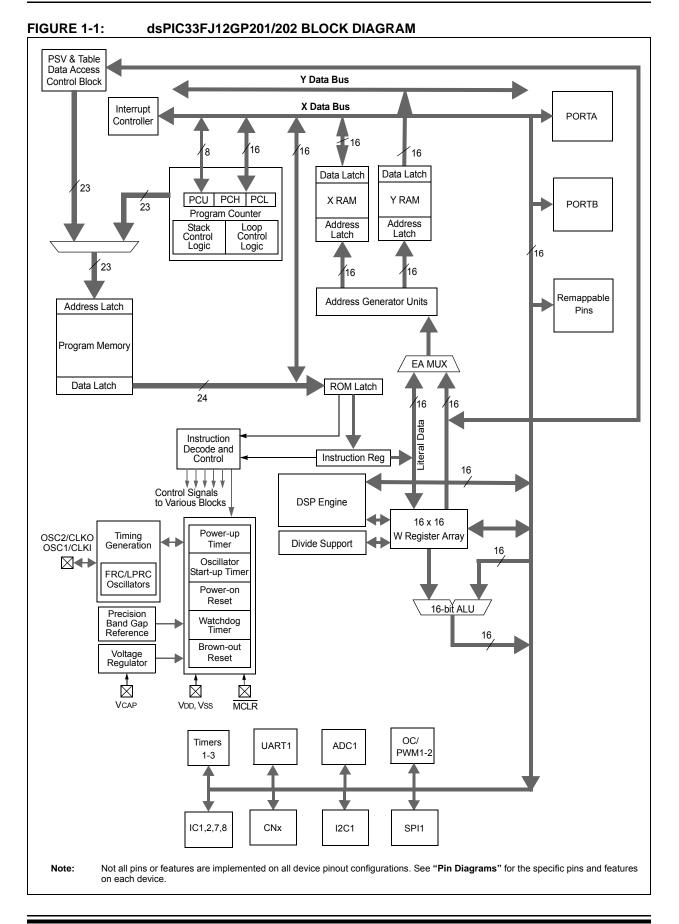

# 3.0 CPU

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS70204) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The dsPIC33FJ12GP201/202 CPU module has a 16-bit (data) modified Harvard architecture with an enhanced instruction set, including significant support for DSP. The CPU has a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M by 24 bits of user program memory space. The actual amount of program memory implemented varies by device. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the DO and REPEAT instructions, both of which are interruptible at any point.

The dsPIC33FJ12GP201/202 devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can serve as a data, address or address offset register. The 16th working register (W15) operates as a software Stack Pointer (SP) for interrupts and calls.

The dsPIC33FJ12GP201/202 instruction set has two classes of instructions: MCU and DSP. These two instruction classes are seamlessly integrated into a single CPU. The instruction set includes many addressing modes and is designed for optimum C compiler efficiency. For most instructions. dsPIC33FJ12GP201/202 devices are capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing A + B = C operations to be executed in a single cycle.

A block diagram of the CPU is shown in Figure 3-1. The programmer's model for the dsPIC33FJ12GP201/202 is shown in Figure 3-2.

### 3.1 Data Addressing Overview

The data space can be addressed as 32K words or 64 Kbytes and is split into two blocks, referred to as X and Y data memory. Each memory block has its own independent Address Generation Unit (AGU). The MCU class of instructions operates solely through the X memory AGU, which accesses the entire memory map as one linear data space. Certain DSP instructions operate through the X and Y AGUs to support dual operand reads, which splits the data address space into two parts. The X and Y data space boundary is device-specific.

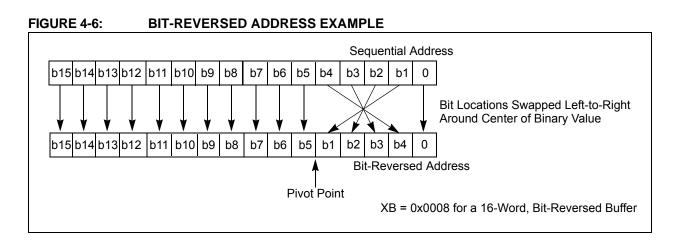

Overhead-free circular buffers (Modulo Addressing mode) are supported in both X and Y address spaces. The Modulo Addressing removes the software boundary checking overhead for DSP algorithms. Furthermore, the X AGU circular addressing can be used with any of the MCU class of instructions. The X AGU also supports Bit-Reversed Addressing to greatly simplify input or output data reordering for radix-2 FFT algorithms.

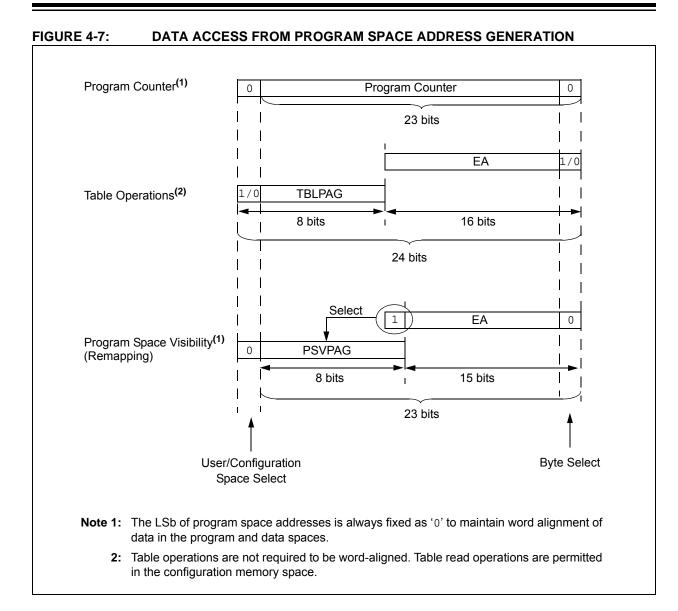

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K program word boundary defined by the 8-bit Program Space Visibility Page (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

# 3.2 DSP Engine Overview

The DSP engine features a high-speed 17-bit by 17-bit multiplier, a 40-bit ALU, two 40-bit saturating accumulators and a 40-bit bidirectional barrel shifter. The barrel shifter is capable of shifting a 40-bit value up to 16 bits right or left, in a single cycle. The DSP instructions operate seamlessly with all other instructions and have been designed for optimal real-time performance. The MAC instruction and other associated instructions can concurrently fetch two data operands from memory while multiplying two W registers and accumulating and optionally saturating the result in the same cycle. This instruction functionality requires that the RAM data space be split for these instructions and linear for all others. Data space partitioning is achieved in a transparent and flexible manner through dedicating certain working registers to each address space.

# 3.3 Special MCU Features

The dsPIC33FJ12GP201/202 features a 17-bit by 17-bit single-cycle multiplier that is shared by both the MCU ALU and DSP engine. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication not only allows you to perform mixed-sign multiplication, it also achieves accurate results for special operations, such as (-1.0) x (-1.0).

#### 3.6.2.4 Data Space Write Saturation

In addition to adder/subtracter saturation, writes to data space can also be saturated, but without affecting the contents of the source accumulator. The data space write saturation logic block accepts a 16-bit, 1.15 fractional value from the round logic block as its input, together with overflow status from the original source (accumulator) and the 16-bit round adder. These inputs are combined and used to select the appropriate 1.15 fractional value as output to write to data space memory.

If the SATDW bit in the CORCON register is set, data (after rounding or truncation) is tested for overflow and adjusted accordingly:

- For input data greater than 0x007FFF, data written to memory is forced to the maximum positive 1.15 value, 0x7FFF

- For input data less than 0xFF8000, data written to memory is forced to the maximum negative 1.15 value, 0x8000

The MSb of the source (bit 39) is used to determine the sign of the operand being tested.

If the SATDW bit in the CORCON register is not set, the input data is always passed through unmodified under all conditions.

### 3.6.3 BARREL SHIFTER

The barrel shifter can perform up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either of the two DSP accumulators or the X bus (to support multi-bit shifts of register or memory data).

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

The barrel shifter is 40 bits wide, thereby obtaining a 40-bit result for DSP shift operations and a 16-bit result for MCU shift operations. Data from the X bus is presented to the barrel shifter between bit positions 16 and 31 for right shifts, and between bit positions 0 and 16 for left shifts.

| TABLE 4-4: | INTERRUPT CONTROLLER REGISTER MAP |

|------------|-----------------------------------|

|------------|-----------------------------------|

|             |             |        |        | ••••••     |         |         |        |            |       |          |         |             | -       | -         |        |            |               |               |

|-------------|-------------|--------|--------|------------|---------|---------|--------|------------|-------|----------|---------|-------------|---------|-----------|--------|------------|---------------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13     | Bit 12  | Bit 11  | Bit 10 | Bit 9      | Bit 8 | Bit 7    | Bit 6   | Bit 5       | Bit 4   | Bit 3     | Bit 2  | Bit 1      | Bit 0         | All<br>Resets |

| INTCON1     | 0080        | NSTDIS | OVAERR | OVBERR     | COVAERR | COVBERR | OVATE  | OVBTE      | COVTE | SFTACERR | DIV0ERR | -           | MATHERR | ADDRERR   | STKERR | OSCFAIL    | _             | 0000          |

| INTCON2     | 0082        | ALTIVT | DISI   | _          | _       | _       | _      | _          | _     | _        | _       | _           | _       | _         | INT2EP | INT1EP     | INT0EP        | 0000          |

| IFS0        | 0084        | —      | _      | AD1IF      | U1TXIF  | U1RXIF  | SPI1IF | SPI1EIF    | T3IF  | T2IF     | OC2IF   | IC2IF       | —       | T1IF      | OC1IF  | IC1IF      | <b>INT0IF</b> | 0000          |

| IFS1        | 0086        | _      |        | INT2IF     | _       | _       | _      | _          | _     | IC8IF    | IC7IF   | _           | INT1IF  | CNIF      | _      | MI2C1IF    | SI2C1IF       | 0000          |

| IFS4        | 008C        | —      | _      | _          | _       | _       | -      | —          |       | —        | _       | _           | —       | _         |        | U1EIF      | _             | 0000          |

| IEC0        | 0094        | —      | _      | AD1IE      | U1TXIE  | U1RXIE  | SPI1IE | SPI1EIE    | T3IE  | T2IE     | OC2IE   | IC2IE       | —       | T1IE      | OC1IE  | IC1IE      | INT0IE        | 0000          |

| IEC1        | 0096        | —      | _      | INT2IE     | _       | _       | -      | —          |       | IC8IE    | IC7IE   | _           | INT1IE  | CNIE      |        | MI2C1IE    | SI2C1IE       | 0000          |

| IEC4        | 009C        |        | _      | _          | _       |         |        | —          |       | —        | _       |             | —       | _         |        | U1EIE      |               | 0000          |

| IPC0        | 00A4        |        |        | T1IP<2:0>  | •       |         | Ú      | OC1IP<2:(  | )>    | —        |         | IC1IP<2:0>  |         | _         | 11     | NT0IP<2:0> | •             | 4444          |

| IPC1        | 00A6        |        |        | T2IP<2:0>  | •       |         | Ú      | OC2IP<2:(  | )>    | —        |         | IC2IP<2:0>  |         | _         |        |            |               | 4440          |

| IPC2        | 00A8        | _      | ι      | J1RXIP<2:( | )>      |         |        | SPI1IP<2:0 | )>    | —        | :       | SPI1EIP<2:0 | >       | _         |        | T3IP<2:0>  |               | 4444          |

| IPC3        | 00AA        |        | _      | _          | _       |         |        | —          |       | —        |         | AD1IP<2:0>  | >       | _         | U      | 1TXIP<2:0  | >             | 0044          |

| IPC4        | 00AC        | _      |        | CNIP<2:0>  | >       |         |        | _          |       | —        |         | MI2C1IP<2:0 | )>      | _         | SI     | 2C1IP<2:0  | >             | 4044          |

| IPC5        | 00AE        | —      |        | IC8IP<2:0> | >       | —       |        | IC7IP<2:0  | >     | —        | —       | -           | —       | —         | 11     | NT1IP<2:0> | •             | 4404          |

| IPC7        | 00B2        |        | _      | _          | _       |         |        | —          |       | —        |         | INT2IP<2:0  | >       | _         |        |            |               | 0040          |

| IPC16       | 00C4        | _      | _      | _          | _       | _       |        | _          |       | —        |         | U1EIP<2:0>  | >       | _         | _      |            | _             | 0040          |

| INTTREG     | 00E0        | _      | _      | _          | _       |         | ILR<3  | :0>>       |       | _        |         |             | VE      | CNUM<6:0> |        |            |               | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-8: I2C1 REGISTER MAP

|          |             | 1201112 |        |         |        |        |        |        |       |       |       |            |              |            |       |       |       |               |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|-------|-------|------------|--------------|------------|-------|-------|-------|---------------|

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4        | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| I2C1RCV  | 0200        | —       | —      | —       | —      | _      | —      | —      |       |       |       |            | Receive      | Register   |       |       |       | 0000          |

| I2C1TRN  | 0202        | _       | —      | —       | _      | -      | —      | _      |       |       |       |            | Transmit     | Register   |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _      |       |       |       | Baud Ra    | te Generato  | r Register |       |       |       | 0000          |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN  | STREN | ACKDT      | ACKEN        | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL | I2COV | D_A        | Р            | S          | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | _       | _      | _       | _      | _      | _      |        |       |       |       | Address    | Register     |            |       |       |       | 0000          |

| I2C1MSK  | 020C        | _       | _      | _       | _      | _      | _      |        |       |       |       | Address Ma | ask Register |            |       |       |       | 0000          |

|          |             |         |        |         |        |        |        |        |       |       |       |            |              |            |       |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-9: UART1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7         | Bit 6   | Bit 5 | Bit 4        | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|----------|--------|----------|--------|--------|--------|-------|------------|---------------|---------|-------|--------------|--------|-------|--------|-------|---------------|

| U1MODE   | 0220        | UARTEN   | —      | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0       | WAKE          | LPBACK  | ABAUD | URXINV       | BRGH   | PDSE  | L<1:0> | STSEL | 0000          |

| U1STA    | 0222        | UTXISEL1 | UTXINV | UTXISEL0 |        | UTXBRK | UTXEN  | UTXBF | TRMT       | URXISE        | EL<1:0> | ADDEN | RIDLE        | PERR   | FERR  | OERR   | URXDA | 0110          |

| U1TXREG  | 0224        | -        | _      | _        |        | _      | _      | _     |            |               |         | UART  | Transmit Reg | gister |       |        |       | xxxx          |

| U1RXREG  | 0226        | _        | _      | _        |        | _      | _      | —     |            |               |         | UART  | Receive Reg  | gister |       |        |       | 0000          |

| U1BRG    | 0228        |          |        |          |        |        |        | Bau   | d Rate Ger | nerator Presc | aler    |       |              |        |       |        |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-10: SPI1 REGISTER MAP

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8      | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|-------------|-------------|--------|--------|---------|--------|--------|--------|------------|------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT    | 0240        | SPIEN  | _      | SPISIDL | —      | —      | —      | _          | -          | -            | SPIROV   | _     | —     | _         | _     | SPITBF | SPIRBF | 0000          |

| SPI1CON1    | 0242        | -      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE        | SSEN         | CKP      | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2    | 0244        | FRMEN  | SPIFSD | FRMPOL  | _      | _      | _      | _          | _          | _            | _        | _     | _     | _         | _     | FRMDLY | -      | 0000          |

| SPI1BUF     | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Re | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-14:</b> | ADC1 REGISTER MAP FOR dsPIC33FJ12GP201 |

|--------------------|----------------------------------------|

|--------------------|----------------------------------------|

| IADLE 4-  | 14. / |        | EGISTI   |        | FUR as | гюзэг  | JIZGFA    | 201     |          |           |           |       |       |        |           |         |         |               |

|-----------|-------|--------|----------|--------|--------|--------|-----------|---------|----------|-----------|-----------|-------|-------|--------|-----------|---------|---------|---------------|

| File Name | Addr  | Bit 15 | Bit 14   | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9   | Bit 8    | Bit 7     | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2     | Bit 1   | Bit 0   | All<br>Resets |

| ADC1BUF0  | 0300  |        |          |        |        |        |           |         | ADC Data | Buffer 0  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF1  | 0302  |        |          |        |        |        |           |         | ADC Data | Buffer 1  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF2  | 0304  |        |          |        |        |        |           |         | ADC Data | Buffer 2  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF3  | 0306  |        |          |        |        |        |           |         | ADC Data | Buffer 3  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF4  | 0308  |        |          |        |        |        |           |         | ADC Data | Buffer 4  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF5  | 030A  |        |          |        |        |        |           |         | ADC Data | Buffer 5  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF6  | 030C  |        |          |        |        |        |           |         | ADC Data | Buffer 6  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF7  | 030E  |        |          |        |        |        |           |         | ADC Data | Buffer 7  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF8  | 0310  |        |          |        |        |        |           |         | ADC Data | Buffer 8  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUF9  | 0312  |        |          |        |        |        |           |         | ADC Data | Buffer 9  |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFA  | 0314  |        |          |        |        |        |           |         | ADC Data | Buffer 10 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFB  | 0316  |        |          |        |        |        |           |         | ADC Data | Buffer 11 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFC  | 0318  |        |          |        |        |        |           |         | ADC Data | Buffer 12 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFD  | 031A  |        |          |        |        |        |           |         | ADC Data | Buffer 13 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFE  | 031C  |        |          |        |        |        |           |         | ADC Data | Buffer 14 |           |       |       |        |           |         |         | xxxx          |

| ADC1BUFF  | 031E  |        |          |        |        |        |           |         | ADC Data | Buffer 15 |           |       |       |        |           |         |         | xxxx          |

| AD1CON1   | 0320  | ADON   | —        | ADSIDL | _      | _      | AD12B     | -       | M<1:0>   |           | SSRC<2:0> |       | —     | SIMSAM | ASAM      | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322  |        | VCFG<2:0 | >      | —      | —      | CSCNA     | -       | °S<1:0>  | BUFS      | —         |       | SMPI  |        |           | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324  | ADRC   | _        | —      |        | S      | SAMC<4:0> |         |          |           |           |       | ADCS  | 8<7:0> | -         |         | r       | 0000          |

| AD1CHS123 | 0326  | —      | —        | —      | —      | —      |           | NB<1:0> | CH123SB  | _         | —         | —     | —     | —      |           | NA<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328  | CH0NB  | —        | —      |        | С      | H0SB<4:0> | >       |          | CH0NA     | —         | —     |       | r      | CH0SA<4:0 |         | r       | 0000          |

| AD1PCFGL  | 032C  |        | _        | —      | _      | _      | _         | -       | —        | PCFG7     | PCFG6     | —     | —     | PCFG3  | PCFG2     | PCFG1   | PCFG0   | 0000          |

| AD1CSSL   | 0330  | —      | —        | —      | —      | _      | —         | —       | —        | CSS7      | CSS6      | —     |       | CSS3   | CSS2      | CSS1    | CSS0    | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| INDEE | 4 <b>Z</b> V. |       | I EIKOE  |         |    |    | ,       |          |         |

|-------|---------------|-------|----------|---------|----|----|---------|----------|---------|

|       |               | Norma | al Addre | SS      |    |    | Bit-Rev | ersed Ac | ldress  |

| A3    | A2            | A1    | A0       | Decimal | A3 | A2 | A1      | A0       | Decimal |

| 0     | 0             | 0     | 0        | 0       | 0  | 0  | 0       | 0        | 0       |

| 0     | 0             | 0     | 1        | 1       | 1  | 0  | 0       | 0        | 8       |

| 0     | 0             | 1     | 0        | 2       | 0  | 1  | 0       | 0        | 4       |

| 0     | 0             | 1     | 1        | 3       | 1  | 1  | 0       | 0        | 12      |

| 0     | 1             | 0     | 0        | 4       | 0  | 0  | 1       | 0        | 2       |

| 0     | 1             | 0     | 1        | 5       | 1  | 0  | 1       | 0        | 10      |

| 0     | 1             | 1     | 0        | 6       | 0  | 1  | 1       | 0        | 6       |

| 0     | 1             | 1     | 1        | 7       | 1  | 1  | 1       | 0        | 14      |

| 1     | 0             | 0     | 0        | 8       | 0  | 0  | 0       | 1        | 1       |

| 1     | 0             | 0     | 1        | 9       | 1  | 0  | 0       | 1        | 9       |

| 1     | 0             | 1     | 0        | 10      | 0  | 1  | 0       | 1        | 5       |

| 1     | 0             | 1     | 1        | 11      | 1  | 1  | 0       | 1        | 13      |

| 1     | 1             | 0     | 0        | 12      | 0  | 0  | 1       | 1        | 3       |

| 1     | 1             | 0     | 1        | 13      | 1  | 0  | 1       | 1        | 11      |

| 1     | 1             | 1     | 0        | 14      | 0  | 1  | 1       | 1        | 7       |

| 1     | 1             | 1     | 1        | 15      | 1  | 1  | 1       | 1        | 15      |

#### REGISTER 7-3: INTCON1: INTERRUPT CONTROL REGISTER 1

| R/W-0           | R/W-0                                                      | R/W-0                                                         | R/W-0                                             | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|-----------------|------------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------------|------------------|------------------|-----------------|-------|

| NSTDIS          | OVAERR                                                     | OVBERR                                                        | COVAERR                                           | COVBERR          | OVATE            | OVBTE           | COVTE |

| bit 15          |                                                            |                                                               |                                                   |                  |                  |                 | bit 8 |

|                 |                                                            |                                                               |                                                   |                  |                  |                 |       |

| R/W-0           | R/W-0                                                      | U-0                                                           | R/W-0                                             | R/W-0            | R/W-0            | R/W-0           | U-0   |

| SFTACERR        | DIV0ERR                                                    |                                                               | MATHERR                                           | ADDRERR          | STKERR           | OSCFAIL         |       |

| bit 7           |                                                            |                                                               |                                                   |                  |                  |                 | bit 0 |

| Legend:         |                                                            |                                                               |                                                   |                  |                  |                 |       |

| R = Readable    | hit                                                        | W = Writable                                                  | hit                                               | l I = Unimpler   | nented bit, read | las '0'         |       |

| -n = Value at F |                                                            | '1' = Bit is set                                              |                                                   | '0' = Bit is cle |                  | x = Bit is unkn | own   |

|                 |                                                            |                                                               |                                                   |                  |                  |                 |       |

| bit 15          | NSTDIS: Inte                                               | rrupt Nesting D                                               | isable bit                                        |                  |                  |                 |       |

|                 |                                                            | nesting is disab                                              |                                                   |                  |                  |                 |       |

|                 | •                                                          | nesting is enab                                               |                                                   |                  |                  |                 |       |

| bit 14          |                                                            | cumulator A Ov<br>caused by ove                               | •                                                 | 0                |                  |                 |       |

|                 | •                                                          | not caused by                                                 |                                                   |                  |                  |                 |       |

| bit 13          |                                                            | cumulator B O                                                 |                                                   |                  |                  |                 |       |

|                 |                                                            | caused by ove                                                 |                                                   |                  |                  |                 |       |

|                 | •                                                          | not caused by                                                 |                                                   |                  |                  |                 |       |

| bit 12          |                                                            | ccumulator A (                                                | -                                                 | =                | -                |                 |       |

|                 |                                                            | caused by cata<br>not caused by                               |                                                   |                  |                  |                 |       |

| bit 11          | •                                                          | Accumulator B                                                 | •                                                 |                  |                  |                 |       |

|                 | •                                                          | caused by cata                                                | •                                                 |                  |                  |                 |       |

|                 |                                                            | not caused by                                                 | -                                                 |                  | umulator B       |                 |       |

| bit 10          |                                                            | mulator A Ove                                                 | -                                                 | able bit         |                  |                 |       |

|                 | ⊥ = Trap over<br>0 = Trap disal                            | flow of Accumu<br>bled                                        | Jiator A                                          |                  |                  |                 |       |

| bit 9           |                                                            | imulator B Ove                                                | •                                                 | able bit         |                  |                 |       |

|                 | 1 = Trap over<br>0 = Trap disal                            | flow of Accumu<br>bled                                        | ulator B                                          |                  |                  |                 |       |

| bit 8           | COVTE: Cata                                                | strophic Overfl                                               | ow Trap Enab                                      | le bit           |                  |                 |       |

|                 | 1 = Trap on c<br>0 = Trap disal                            | atastrophic ove<br>bled                                       | erflow of Accur                                   | nulator A or B   | enabled          |                 |       |

| bit 7           | SFTACERR:                                                  | Shift Accumula                                                | itor Error Statu                                  | is bit           |                  |                 |       |

|                 |                                                            | r trap was caus<br>r trap was not o                           |                                                   |                  |                  |                 |       |

| bit 6           | DIV0ERR: Ar                                                | ithmetic Error S                                              | Status bit                                        |                  |                  |                 |       |

|                 |                                                            | r trap was caus                                               |                                                   |                  |                  |                 |       |

|                 | 0 = Math erro                                              | r trap was not o                                              | caused by a di                                    | vide by zero     |                  |                 |       |

| 1.4 F           |                                                            |                                                               |                                                   |                  |                  |                 |       |

| bit 5           | Unimplemen                                                 | ted: Read as '                                                | 0'                                                |                  |                  |                 |       |

| bit 5<br>bit 4  | Unimplemen<br>MATHERR: A                                   | ted: Read as 'o<br>rithmetic Error                            | <sup>o'</sup><br>Status bit                       |                  |                  |                 |       |

|                 | Unimplement<br>MATHERR: A<br>1 = Math erro                 | ted: Read as '                                                | o'<br>Status bit<br>Irred                         |                  |                  |                 |       |

|                 | Unimplemen<br>MATHERR: A<br>1 = Math erro<br>0 = Math erro | t <b>ed:</b> Read as '(<br>withmetic Error<br>r trap has occu | <sup>D'</sup><br>Status bit<br>Irred<br>Doccurred |                  |                  |                 |       |

### REGISTER 7-18: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0          | U-0           | U-0                 | U-0             | U-0              | U-0              | U-0             | U-0   |

|--------------|---------------|---------------------|-----------------|------------------|------------------|-----------------|-------|

| _            | —             | —                   | —               | —                | —                | —               | —     |

| bit 15       |               |                     |                 |                  |                  |                 | bit 8 |

|              |               |                     |                 |                  |                  |                 |       |

| U-0          | R/W-1         | R/W-0               | R/W-0           | U-0              | U-0              | U-0             | U-0   |

| —            |               | U1EIP<2:0>          |                 |                  | —                | —               | —     |

| bit 7        |               |                     |                 |                  |                  |                 | bit 0 |

|              |               |                     |                 |                  |                  |                 |       |

| Legend:      |               |                     |                 |                  |                  |                 |       |

| R = Readab   | le bit        | W = Writable I      | oit             | U = Unimplei     | mented bit, read | as '0'          |       |

| -n = Value a | t POR         | '1' = Bit is set    |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|              |               |                     |                 |                  |                  |                 |       |

| bit 15-7     | Unimplemen    | ted: Read as '0     | )'              |                  |                  |                 |       |

| bit 6-4      | U1EIP<2:0>:   | UART1 Error In      | nterrupt Priori | ty bits          |                  |                 |       |

|              | 111 = Interru | pt is priority 7 (ł | nighest priorit | y interrupt)     |                  |                 |       |

|              | •             |                     | 0               | , I,             |                  |                 |       |

|              | •             |                     |                 |                  |                  |                 |       |

|              | •             |                     |                 |                  |                  |                 |       |

|              | 001 = Interru | pt is priority 1    |                 |                  |                  |                 |       |

|              | 000 = Interru | pt source is disa   | abled           |                  |                  |                 |       |

| bit 3-0      | Unimplemen    | ted: Read as '0     | )'              |                  |                  |                 |       |

|              |               |                     |                 |                  |                  |                 |       |

# **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

| U-0                         | R-0                                                                                                                                                                                                                                       | R-0                                                                                                                                                            | R-0                                                                                                           | U-0                                | R/W-y                           | R/W-y                                                                                  | R/W-y                  |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|----------------------------------------------------------------------------------------|------------------------|

| _                           |                                                                                                                                                                                                                                           | COSC<2:0>                                                                                                                                                      |                                                                                                               | —                                  |                                 | NOSC<2:0> <sup>(2)</sup>                                                               |                        |

| bit 15                      |                                                                                                                                                                                                                                           |                                                                                                                                                                |                                                                                                               |                                    |                                 |                                                                                        | bit 8                  |

| R/W-0                       | R/W-0                                                                                                                                                                                                                                     | R-0                                                                                                                                                            | U-0                                                                                                           | R/C-0                              | U-0                             | R/W-0                                                                                  | R/W-0                  |

| CLKLOCK                     | IOLOCK                                                                                                                                                                                                                                    | LOCK                                                                                                                                                           | _                                                                                                             | CF                                 | _                               | LPOSCEN                                                                                | OSWEN                  |

| bit 7                       |                                                                                                                                                                                                                                           |                                                                                                                                                                |                                                                                                               | -                                  |                                 |                                                                                        | bit C                  |

|                             |                                                                                                                                                                                                                                           |                                                                                                                                                                |                                                                                                               |                                    |                                 |                                                                                        |                        |

| Legend:                     |                                                                                                                                                                                                                                           | y = Value set                                                                                                                                                  | from Configur                                                                                                 | ation bits on P                    | OR                              |                                                                                        |                        |

| R = Readable                | e bit                                                                                                                                                                                                                                     | W = Writable                                                                                                                                                   | bit                                                                                                           | U = Unimple                        | mented bit, rea                 | ıd as '0'                                                                              |                        |

| -n = Value at I             | POR                                                                                                                                                                                                                                       | '1' = Bit is set                                                                                                                                               |                                                                                                               | '0' = Bit is cle                   | eared                           | x = Bit is unkn                                                                        | own                    |

| 1.11.45                     |                                                                                                                                                                                                                                           |                                                                                                                                                                | e.1                                                                                                           |                                    |                                 |                                                                                        |                        |

| bit 15<br>bit 14-12         | -                                                                                                                                                                                                                                         | ted: Read as '<br>Current Oscilla                                                                                                                              |                                                                                                               |                                    |                                 |                                                                                        |                        |

|                             | 110 = Fast R<br>101 = Low-Pe<br>100 = Second<br>011 = Primar<br>010 = Primar<br>001 = Fast R                                                                                                                                              | C oscillator (FF<br>C oscillator (FF<br>ower RC oscillator<br>dary oscillator<br>y oscillator (XT<br>y oscillator (XT<br>C oscillator (FF<br>C oscillator (FF  | RC) with Divide<br>ator (LPRC)<br>(SOSC)<br>; HS, EC) with<br>; HS, EC)<br>RC) with Divide                    | e-by-16<br>I PLL                   | L                               |                                                                                        |                        |

| bit 11                      |                                                                                                                                                                                                                                           | ted: Read as '                                                                                                                                                 | -                                                                                                             |                                    |                                 |                                                                                        |                        |

| bit 10-8                    | 111 = Fast R<br>110 = Fast R<br>101 = Low-Pe<br>100 = Secone<br>011 = Primar<br>010 = Primar<br>001 = Fast R                                                                                                                              | New Oscillato<br>C oscillator (Ff<br>C oscillator (Ff<br>ower RC oscillator<br>dary oscillator (XT<br>y oscillator (XT<br>C oscillator (Ff<br>C oscillator (Ff | RC) with Divide<br>RC) with Divide<br>ator (LPRC)<br>(SOSC)<br>; HS, EC) with<br>; HS, EC)<br>RC) with Divide | e-by-n<br>e-by-16<br>I PLL         | L                               |                                                                                        |                        |

| bit 7                       | If clock switch<br>1 = Clock sw                                                                                                                                                                                                           | Clock Lock Ena<br>ning is enabled<br>ritching is disat<br>ritching is enab                                                                                     | and FSCM is<br>led, system cl                                                                                 | lock source is                     | locked                          | : 0b01)<br>by clock switching                                                          | a                      |

| bit 6                       | IOLOCK: Per<br>1 = Peripheri                                                                                                                                                                                                              | ripheral Pin Se<br>ial Pin Select is                                                                                                                           | lect Lock bit<br>locked, write                                                                                | to peripheral p                    | oin select regis                | ter is not allowed                                                                     | -                      |

| bit 5                       | <ul> <li>LOCK: PLL Lock Status bit (read-only)</li> <li>1 = Indicates that PLL is in lock, or PLL start-up timer is satisfied</li> <li>0 = Indicates that PLL is out of lock, start-up timer is in progress or PLL is disabled</li> </ul> |                                                                                                                                                                |                                                                                                               |                                    |                                 |                                                                                        |                        |

| bit 4                       | Unimplemen                                                                                                                                                                                                                                | ted: Read as '                                                                                                                                                 | 0'                                                                                                            |                                    |                                 |                                                                                        |                        |

| <i>"ds</i><br><b>2:</b> Dir | PIC33F/PIC24                                                                                                                                                                                                                              | H Family Refer                                                                                                                                                 | ence Manual"<br>y primary osci                                                                                | (available fron<br>llator mode wit | n the Microchip<br>h PLL and FR | c <b>illator"</b> (DS701)<br>website) for det<br>CPLL mode are r<br>llication must swi | ails.<br>ot permitted. |

- mode as a transition clock source between the two PLL modes.

- **3:** This register is reset only on a Power-on Reset (POR).

### REGISTER 10-2: RPINR1: PERIPHERAL PIN SELECT INPUT REGISTER 1

| U-0           | U-0                       | U-0                       | U-0              | U-0           | U-0                  | U-0          | U-0                |  |  |  |

|---------------|---------------------------|---------------------------|------------------|---------------|----------------------|--------------|--------------------|--|--|--|

| _             | —                         | —                         | _                | _             | —                    | —            | —                  |  |  |  |

| bit 15        |                           |                           |                  |               |                      |              | bit 8              |  |  |  |

|               |                           |                           |                  |               |                      |              |                    |  |  |  |

| U-0           | U-0                       | U-0                       | R/W-1            | R/W-1         | R/W-1                | R/W-1        | R/W-1              |  |  |  |

| _             |                           | —                         |                  |               | INT2R<4:0>           |              |                    |  |  |  |

| bit 7         |                           |                           |                  |               |                      |              | bit 0              |  |  |  |

|               |                           |                           |                  |               |                      |              |                    |  |  |  |

| Legend:       |                           |                           |                  |               |                      |              |                    |  |  |  |

| R = Readable  | e bit                     | W = Writable              | bit              | U = Unimpler  | mented bit, read     | as '0'       |                    |  |  |  |

| -n = Value at | POR                       | '1' = Bit is set          | l' = Bit is set  |               | '0' = Bit is cleared |              | x = Bit is unknown |  |  |  |

|               |                           |                           |                  |               |                      |              |                    |  |  |  |

| bit 15-5      | Unimplemen                | ted: Read as '            | 0'               |               |                      |              |                    |  |  |  |

| bit 4-0       | INT2R<4:0>:               | Assign Externa            | al Interrupt 2 ( | INTR2) to the | corresponding F      | RPn pin bits |                    |  |  |  |

|               | 11111 <b>= Inpu</b>       | t tied to Vss             |                  |               |                      |              |                    |  |  |  |

|               | 01111 <b>= Inpu</b>       | t tied to RP15            |                  |               |                      |              |                    |  |  |  |

|               | •                         |                           |                  |               |                      |              |                    |  |  |  |

|               | •                         |                           |                  |               |                      |              |                    |  |  |  |

|               | •                         |                           |                  |               |                      |              |                    |  |  |  |

|               | 00001 = Input tied to RP1 |                           |                  |               |                      |              |                    |  |  |  |

|               | 00000 <b>= Inpu</b>       | 00000 = Input tied to RP0 |                  |               |                      |              |                    |  |  |  |

|               |                           |                           |                  |               |                      |              |                    |  |  |  |

| U-0          | U-0                          | U-0             | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|--------------|------------------------------|-----------------|----------------|------------------|-----------------|-----------------|-------|

| _            | —                            | _               |                |                  | IC8R<4:0>       |                 |       |

| bit 15       |                              |                 |                |                  |                 |                 | bit 8 |

|              |                              |                 |                |                  |                 |                 |       |

| U-0          | U-0                          | U-0             | R/W-1          | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

| _            | _                            |                 |                |                  | IC7R<4:0>       |                 |       |

| bit 7        |                              |                 |                |                  |                 |                 | bit ( |

|              |                              |                 |                |                  |                 |                 |       |

| Legend:      |                              |                 |                |                  |                 |                 |       |

| R = Readab   | le bit                       | W = Writable    | bit            | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value a | t POR                        | '1' = Bit is se | t              | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

|              |                              |                 |                |                  |                 |                 |       |

| bit 15-13    | Unimplemen                   | ted: Read as    | 'O'            |                  |                 |                 |       |

| bit 12-8     | -                            |                 |                | to the correspo  | onding pin RPn  | i pin bits      |       |

|              | 11111 = Inpu                 | •               |                |                  |                 |                 |       |

|              |                              | it tied to RP15 |                |                  |                 |                 |       |

|              | •                            |                 |                |                  |                 |                 |       |

|              | •                            |                 |                |                  |                 |                 |       |

|              | •                            |                 |                |                  |                 |                 |       |

|              | 00001 <b>= Inp</b> u         |                 |                |                  |                 |                 |       |

|              | 00000 <b>= Inp</b> u         |                 |                |                  |                 |                 |       |

| bit 7-5      | -                            | ted: Read as    |                |                  |                 |                 |       |

| bit 4-0      | IC7R<4:0>:                   | Assign Input (  | Capture 7 (IC7 | ) to the corresp | oonding pin RP  | n pin bits      |       |

|              | 11111 <b>= Inp</b> u         |                 |                |                  |                 |                 |       |

|              | 01111 <b>= Inp</b> u         | It tied to RP15 |                |                  |                 |                 |       |

|              | •                            |                 |                |                  |                 |                 |       |

|              | •                            |                 |                |                  |                 |                 |       |

|              | •                            | t tigd to DD1   |                |                  |                 |                 |       |

|              | 00001 = Inpu<br>00000 = Inpu |                 |                |                  |                 |                 |       |

|              | 00000 – mpt                  |                 |                |                  |                 |                 |       |

|              |                              |                 |                |                  |                 |                 |       |

#### REGISTER 10-5: RPINR10: PERIPHERAL PIN SELECT INPUT REGISTERS 10

### REGISTER 10-11: RPOR1: PERIPHERAL PIN SELECT OUTPUT REGISTERS 1

| U-0          | U-0        | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0             | R/W-0    |  |

|--------------|------------|------------------|-------|------------------|-----------------|-------------------|----------|--|

|              | _          | _                |       |                  | RP3R<4:0>       |                   |          |  |

| bit 15       |            |                  |       |                  |                 |                   | bit 8    |  |

|              |            |                  |       |                  |                 |                   |          |  |

| U-0          | U-0        | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0             | R/W-0    |  |

| —            | —          | — RP2R<4:0>      |       |                  |                 |                   |          |  |

| bit 7        |            |                  |       |                  |                 |                   | bit 0    |  |

|              |            |                  |       |                  |                 |                   |          |  |

| Legend:      |            |                  |       |                  |                 |                   |          |  |

| R = Readab   | le bit     | W = Writable     | bit   | U = Unimpler     | nented bit, rea | d as '0'          |          |  |

| -n = Value a | t POR      | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr   | nown     |  |

|              |            |                  |       |                  |                 |                   |          |  |

| bit 15-13    | Unimplemen | ted: Read as '   | 0'    |                  |                 |                   |          |  |

| bit 12-8     |            | Peripheral Out   | •     | is Assigned to F | RP3 Output Pir  | n bits (see Table | 10-2 for |  |

| bit 7-5      | Unimplemen | ted: Read as '   | 0'    |                  |                 |                   |          |  |

|              |            |                  |       |                  |                 |                   |          |  |

bit 4-0 **RP2R<4:0>:** Peripheral Output Function is Assigned to RP2 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-12: RPOR2: PERIPHERAL PIN SELECT OUTPUT REGISTERS 2

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|-----------|-------|-------|

| —      | —   | —   |       |       | RP5R<4:0> |       |       |

| bit 15 |     |     |       |       |           |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | —   | —   |       |       | RP4R<4:0> |       |       |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP5R<4:0>:** Peripheral Output Function is Assigned to RP5 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP4R<4:0>:** Peripheral Output Function is Assigned to RP4 Output Pin bits (see Table 10-2 for peripheral function numbers)

#### REGISTER 10-17: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTERS 7

| U-0             | U-0        | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|------------|------------------|-------|------------------|-----------------|-----------------|-------|

| —               | _          | —                |       |                  | RP15R<4:0       | >               |       |

| bit 15          |            |                  |       |                  |                 |                 | bit 8 |

|                 |            |                  |       | <b>D</b> 4440    | DAALO           | <b>D</b> 444.0  | DAMA  |

| U-0             | U-0        | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| —               | —          | —                |       |                  | RP14R<4:0       | >               |       |

| bit 7           |            |                  |       |                  |                 |                 | bit 0 |

|                 |            |                  |       |                  |                 |                 |       |

| Legend:         |            |                  |       |                  |                 |                 |       |

| R = Readable I  | bit        | W = Writable I   | bit   | U = Unimpler     | mented bit, rea | ıd as '0'       |       |

| -n = Value at P | OR         | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|                 |            |                  |       |                  |                 |                 |       |

| bit 15-13       | Unimplemen | ted: Read as 'd  | )'    |                  |                 |                 |       |

|                 |            |                  |       |                  |                 |                 |       |

bit 12-8 **RP15R<4:0>:** Peripheral Output Function is Assigned to RP15 Output Pin bits (see Table 10-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP14R<4:0>:** Peripheral Output Function is Assigned to RP14 Output Pin bits (see Table 10-2 for peripheral function numbers)

| R/W-0         | U-0                 | R/W-0                                                                                                           | U-0          | U-0                                                                                                                                 | R/W-0            | R/W-0         | R/W-0  |  |  |  |  |  |  |

|---------------|---------------------|-----------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------|--------|--|--|--|--|--|--|

| ADON          |                     | ADSIDL                                                                                                          | _            | _                                                                                                                                   | AD12B            | FOR           | M<1:0> |  |  |  |  |  |  |

| bit 15        |                     |                                                                                                                 |              |                                                                                                                                     |                  | •             | bit 8  |  |  |  |  |  |  |

| R/W-0         | R/W-0               | R/W-0                                                                                                           | U-0          | R/W-0                                                                                                                               | R/W-0            | R/W-0         | R/C-0  |  |  |  |  |  |  |

| 1000 0        |                     | 10000                                                                                                           |              |                                                                                                                                     |                  | HC,HS         | HC, HS |  |  |  |  |  |  |

|               | SSRC<2:0>           |                                                                                                                 |              | SIMSAM                                                                                                                              | ASAM             | SAMP          | DONE   |  |  |  |  |  |  |

| bit 7         |                     |                                                                                                                 |              |                                                                                                                                     |                  |               | bit (  |  |  |  |  |  |  |

| Legend:       |                     | HC = Cleared b                                                                                                  | y hardware   | HS = Set by h                                                                                                                       | ardware          |               |        |  |  |  |  |  |  |

| R = Readabl   | le bit              | W = Writable b                                                                                                  | it           | U = Unimplen                                                                                                                        | nented bit, rea  | id as '0'     |        |  |  |  |  |  |  |

| -n = Value at | t POR               | '1' = Bit is set                                                                                                |              | '0' = Bit is cle                                                                                                                    | ared             | x = Bit is un | known  |  |  |  |  |  |  |

| bit 15        |                     | Operating Mode                                                                                                  | hit          |                                                                                                                                     |                  |               |        |  |  |  |  |  |  |

|               |                     | lule is operating                                                                                               |              |                                                                                                                                     |                  |               |        |  |  |  |  |  |  |

| bit 14        | Unimplemen          | ted: Read as '0                                                                                                 | ,            |                                                                                                                                     |                  |               |        |  |  |  |  |  |  |

| bit 13        | ADSIDL: Stop        | o in Idle Mode b                                                                                                | it           |                                                                                                                                     |                  |               |        |  |  |  |  |  |  |

|               |                     | ue module operation module operation module operation module operation module operation module operation module |              | levice enters Idle<br>de                                                                                                            | e mode           |               |        |  |  |  |  |  |  |