Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E-XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                            |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 12KB (12K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 1K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 10x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj12gp202t-i-ml |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                       |       |

|-------|-----------------------------------------------------------------------|-------|

| 2.0   | Guidelines for Getting Started with 16-bit Digital Signal Controllers | 15    |

| 3.0   | CPU                                                                   |       |

| 4.0   | Memory Organization                                                   | 31    |

| 5.0   | Flash Program Memory                                                  | 55    |

| 6.0   | Resets                                                                | 61    |

| 7.0   | Interrupt Controller                                                  | 69    |

| 8.0   | Oscillator Configuration                                              | 97    |

| 9.0   | Power-Saving Features                                                 | . 107 |

| 10.0  | I/O Ports                                                             | . 111 |

| 11.0  | Timer1                                                                | . 129 |

| 12.0  | Timer2/3 Feature                                                      | . 131 |

| 13.0  | Input Capture                                                         | . 137 |

| 14.0  | Output Compare                                                        | . 139 |

| 15.0  | Serial Peripheral Interface (SPI)                                     | . 143 |

| 16.0  | Inter-Integrated Circuit™ (I <sup>2</sup> C™)                         | . 149 |

| 17.0  | Universal Asynchronous Receiver Transmitter (UART)                    | . 157 |

| 18.0  | 10-bit/12-bit Analog-to-Digital Converter (ADC)                       | . 163 |

| 19.0  | Special Features                                                      | . 175 |

| 20.0  | Instruction Set Summary                                               | . 181 |

| 21.0  | Development Support                                                   | . 189 |

| 22.0  | Electrical Characteristics                                            | . 193 |

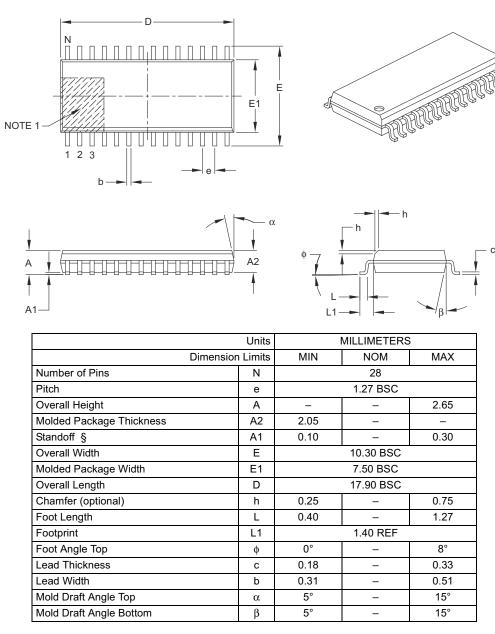

| 23.0  | Packaging Information                                                 | . 237 |

| Appe  | ndix A: Revision History                                              | . 245 |

| Index |                                                                       | 253   |

| The N | /icrochip Web Site                                                    | . 257 |

| Custo | mer Change Notification Service                                       | . 257 |

| Custo | mer Support                                                           | . 257 |

| Read  | er Response                                                           | . 258 |

| Produ | Ict Identification System                                             | . 259 |

|       |                                                                       |       |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### 1.0 DEVICE OVERVIEW

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

This document contains device specific information for the dsPIC33FJ12GP201/202 Digital Signal Controller (DSC) devices. The dsPIC33F devices contain extensive Digital Signal Processor (DSP) functionality with a high-performance, 16-bit microcontroller (MCU) architecture.

Figure 1-1 shows a general block diagram of the core and peripheral modules in the dsPIC33FJ12GP201/202 family of devices. Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

NOTES:

#### 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to 4 MHz <  $F_{IN}$  < 8 MHz to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

When the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV, and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

#### 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE in-circuit emulator is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in the register that correspond to the A/D pins that are initialized by MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE in-circuit emulator, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 2, MPLAB ICD 3, or MPLAB REAL ICE In-Circuit Emulator is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

### 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternately, connect a 1k to 10k resistor between Vss and unused pins and drive the output to logic low.

#### 4.1.1 PROGRAM MEMORY ORGANIZATION

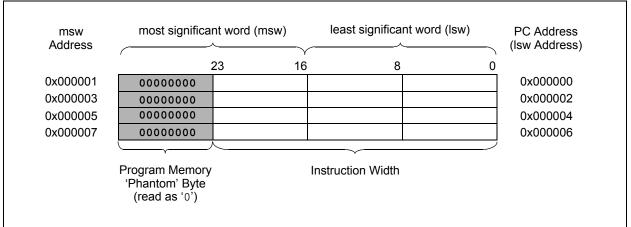

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement provides compatibility with data memory space addressing and makes data in the program memory space accessible.

#### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJ12GP201/202 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user application at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJ12GP201/202 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table**".

#### 4.2 Data Address Space

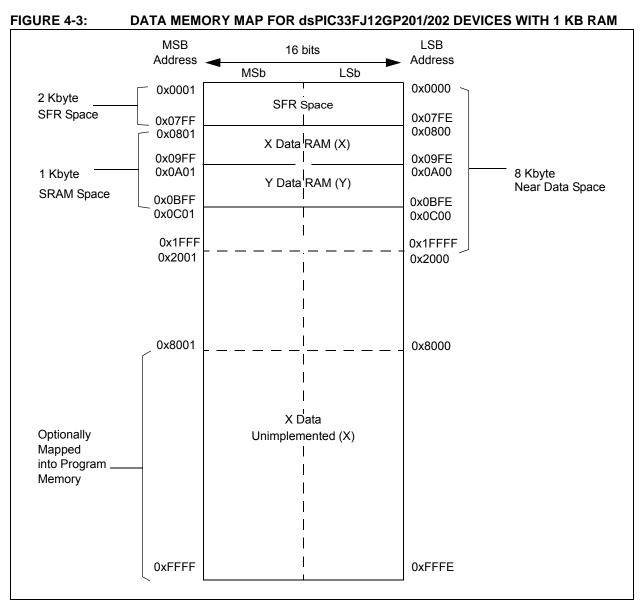

The dsPIC33FJ12GP201/202 CPU has a separate 16-bit-wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. The data memory map is shown in Figure 4-3.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15>=0) is used for implemented memory addresses, while the upper half (EA<15>=1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data From Program Memory Using Program Space Visibility").

Microchip dsPIC33FJ12GP201/202 devices implement up to 1 Kbyte of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit-wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

#### 4.2.5 X AND Y DATA SPACES

The core has two data spaces, X and Y. These data spaces can be considered either separate (for some DSP instructions), or as one unified linear address range (for MCU instructions). The data spaces are accessed using two Address Generation Units (AGUs) and separate data paths. This feature allows certain instructions to concurrently fetch two words from RAM, thereby enabling efficient execution of DSP algorithms such as Finite Impulse Response (FIR) filtering and fast Fourier transform (FFT).

The X data space is used by all instructions and supports all addressing modes. X data space has separate read and write data buses. The X read data bus is the read data path for all instructions that view data space as combined X and Y address space. It is also the X data prefetch path for the dual operand DSP instructions (MAC class).

The Y data space is used in concert with the X data space by the MAC class of instructions (CLR, ED, EDAC, MAC, MOVSAC, MPY, MPY.N, and MSC) to provide two concurrent data read paths.

Both the X and Y data spaces support Modulo Addressing mode for all instructions, subject to addressing mode restrictions. Bit-Reversed Addressing mode is only supported for writes to X data space.

All data memory writes, including in DSP instructions, view data space as combined X and Y address space. The boundary between the X and Y data spaces is device-dependent and is not user-programmable.

All effective addresses are 16 bits wide and point to bytes within the data space. Therefore, the data space address range is 64 Kbytes, or 32K words, though the implemented memory locations vary by device.

| File Name | Addr | Bit 15 | Bit 14               | Bit 13 | Bit 12 | Bit 11 | Bit 10               | Bit 9 | Bit 8    | Bit 7      | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1   | Bit 0   | All<br>Resets |

|-----------|------|--------|----------------------|--------|--------|--------|----------------------|-------|----------|------------|-----------|-------|-------|--------|----------|---------|---------|---------------|

| ADC1BUF0  | 0300 |        |                      | •      |        |        | •                    |       | ADC Data | a Buffer 0 |           |       |       | •      |          |         |         | xxxx          |

| ADC1BUF1  | 0302 |        |                      |        |        |        |                      |       | ADC Data | a Buffer 1 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF2  | 0304 |        |                      |        |        |        |                      |       | ADC Data | a Buffer 2 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF3  | 0306 |        |                      |        |        |        |                      |       | ADC Data | a Buffer 3 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF4  | 0308 |        | ADC Data Buffer 4    |        |        |        |                      |       |          |            |           |       |       | xxxx   |          |         |         |               |

| ADC1BUF5  | 030A |        | ADC Data Buffer 5 xx |        |        |        |                      |       |          |            |           |       |       | xxxx   |          |         |         |               |

| ADC1BUF6  | 030C |        |                      |        |        |        |                      |       | ADC Data | a Buffer 6 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF7  | 030E |        |                      |        |        |        |                      |       | ADC Data | a Buffer 7 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF8  | 0310 |        |                      |        |        |        |                      |       | ADC Data | a Buffer 8 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUF9  | 0312 |        |                      |        |        |        |                      |       | ADC Data | a Buffer 9 |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFA  | 0314 |        |                      |        |        |        |                      |       | ADC Data | Buffer 10  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFB  | 0316 |        |                      |        |        |        |                      |       | ADC Data | Buffer 11  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFC  | 0318 |        |                      |        |        |        |                      |       | ADC Data | Buffer 12  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFD  | 031A |        |                      |        |        |        |                      |       | ADC Data | Buffer 13  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFE  | 031C |        |                      |        |        |        |                      |       | ADC Data | Buffer 14  |           |       |       |        |          |         |         | xxxx          |

| ADC1BUFF  | 031E |        |                      |        |        |        |                      |       | ADC Data | Buffer 15  |           |       |       |        |          |         |         | xxxx          |

| AD1CON1   | 0320 | ADON   | _                    | ADSIDL |        | _      | AD12B                | FOR   | M<1:0>   | ç          | SSRC<2:0> | >     | _     | SIMSAM | ASAM     | SAMP    | DONE    | 0000          |

| AD1CON2   | 0322 | Ň      | VCFG<2:0             | >      | _      |        | CSCNA                | CHP   | S<1:0>   | BUFS       | _         |       | SMPI  | <3:0>  |          | BUFM    | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | —                    | -      |        |        | SAMC<4:0             | >     |          |            |           |       | ADC   | S<7:0> |          |         |         | 0000          |

| AD1CHS123 | 0326 | _      | _                    | _      | _      | _      | CH123NB<1:0> CH123SB |       |          | _          | _         | _     | _     | —      | CH123    | NA<1:0> | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _                    | _      |        |        | CH0SB<4:0            | -     |          | CH0NA      | _         | —     |       |        | CH0SA<4: |         | 1       | 0000          |

| AD1PCFGL  | 032C | _      | _                    | _      | _      |        |                      | PCFG9 | PCFG8    | PCFG7      | PCFG6     | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1   | PCFG0   | 0000          |

| AD1CSSL   | 0330 | —      |                      | —      | —      | —      | —                    | CSS9  | CSS8     | CSS7       | CSS6      | CSS5  | CSS4  | CSS3   | CSS2     | CSS1    | CSS0    | 0000          |

#### TABLE 4-15: ADC1 REGISTER MAP FOR dsPIC33FJ12GP202

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address           | AIVT Address          | Interrupt Source  |

|------------------|--------------------------------------|-----------------------|-----------------------|-------------------|

| 54               | 46                                   | 0x000070              | 0x000170              | Reserved          |

| 55               | 47                                   | 0x000072              | 0x000172              | Reserved          |

| 56               | 48                                   | 0x000074              | 0x000174              | Reserved          |

| 57               | 49                                   | 0x000076              | 0x000176              | Reserved          |

| 58               | 50                                   | 0x000078              | 0x000178              | Reserved          |

| 59               | 51                                   | 0x00007A              | 0x00017A              | Reserved          |

| 60               | 52                                   | 0x00007C              | 0x00017C              | Reserved          |

| 61               | 53                                   | 0x00007E              | 0x00017E              | Reserved          |

| 62               | 54                                   | 0x000080              | 0x000180              | Reserved          |

| 63               | 55                                   | 0x000082              | 0x000182              | Reserved          |

| 64               | 56                                   | 0x000084              | 0x000184              | Reserved          |

| 65               | 57                                   | 0x000086              | 0x000186              | Reserved          |

| 66               | 58                                   | 0x000088              | 0x000188              | Reserved          |

| 67               | 59                                   | 0x00008A              | 0x00018A              | Reserved          |

| 68               | 60                                   | 0x00008C              | 0x00018C              | Reserved          |

| 69               | 61                                   | 0x00008E              | 0x00018E              | Reserved          |

| 70               | 62                                   | 0x000090              | 0x000190              | Reserved          |

| 71               | 63                                   | 0x000092              | 0x000192              | Reserved          |

| 72               | 64                                   | 0x000094              | 0x000194              | Reserved          |

| 73               | 65                                   | 0x000096              | 0x000196              | U1E – UART1 Error |

| 74               | 66                                   | 0x000098              | 0x000198              | Reserved          |

| 75               | 67                                   | 0x00009A              | 0x00019A              | Reserved          |

| 76               | 68                                   | 0x00009C              | 0x00019C              | Reserved          |

| 77               | 69                                   | 0x00009E              | 0x00019E              | Reserved          |

| 78               | 70                                   | 0x0000A0              | 0x0001A0              | Reserved          |

| 79               | 71                                   | 0x0000A2              | 0x0001A2              | Reserved          |

| 80-125           | 72-117                               | 0x0000A4-<br>0x0000FE | 0x0001A4-<br>0x0001FE | Reserved          |

#### TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

#### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 0x000004    | 0x000104     | Reserved           |

| 1             | 0x00006     | 0x000106     | Oscillator Failure |

| 2             | 0x00008     | 0x000108     | Address Error      |

| 3             | 0x00000A    | 0x00010A     | Stack Error        |

| 4             | 0x0000C     | 0x00010C     | Math Error         |

| 5             | 0x00000E    | 0x00010E     | Reserved           |

| 6             | 0x000010    | 0x000110     | Reserved           |

| 7             | 0x000012    | 0x000112     | Reserved           |

| R/W-0              | U-0                                                                    | R/W-0                | U-0              | U-0                           | U-0             | U-0                | U-0   |  |  |  |  |  |

|--------------------|------------------------------------------------------------------------|----------------------|------------------|-------------------------------|-----------------|--------------------|-------|--|--|--|--|--|

| TON <sup>(2)</sup> |                                                                        | TSIDL <sup>(1)</sup> | _                | _                             |                 | _                  | _     |  |  |  |  |  |

| bit 15             |                                                                        |                      |                  |                               |                 |                    | bit 8 |  |  |  |  |  |

|                    |                                                                        |                      |                  |                               |                 |                    |       |  |  |  |  |  |

| U-0                | R/W-0                                                                  | R/W-0                | R/W-0            | U-0                           | U-0             | R/W-0              | U-0   |  |  |  |  |  |

|                    | TGATE <sup>(2)</sup>                                                   | TCKPS<               | <1:0> <b>(2)</b> | —                             | _               | TCS <sup>(2)</sup> |       |  |  |  |  |  |

| bit 7              |                                                                        |                      |                  |                               |                 |                    | bit C |  |  |  |  |  |

|                    |                                                                        |                      |                  |                               |                 |                    |       |  |  |  |  |  |

| Legend:            |                                                                        |                      |                  |                               |                 |                    |       |  |  |  |  |  |

| R = Readabl        |                                                                        | W = Writable I       | oit              | •                             | mented bit, rea |                    |       |  |  |  |  |  |

| -n = Value at      | POR                                                                    | '1' = Bit is set     |                  | '0' = Bit is cle              | ared            | x = Bit is unkn    | own   |  |  |  |  |  |

| bit 15             | TON: Timer3                                                            | On hit(2)            |                  |                               |                 |                    |       |  |  |  |  |  |

| DIL 15             | 1 = Starts 16-                                                         |                      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | 0 = Stops 16-                                                          |                      |                  |                               |                 |                    |       |  |  |  |  |  |

| bit 14             | Unimplemented: Read as '0'                                             |                      |                  |                               |                 |                    |       |  |  |  |  |  |

| bit 13             | TSIDL: Stop i                                                          | in Idle Mode bit     | (1)              |                               |                 |                    |       |  |  |  |  |  |

|                    | 1 = Discontinue timer operation when device enters Idle mode           |                      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | 0 = Continue                                                           | timer operation      | in Idle mode     | 9                             |                 |                    |       |  |  |  |  |  |

| bit 12-7           | -                                                                      | ted: Read as '0      |                  | (-)                           |                 |                    |       |  |  |  |  |  |

| bit 6              | <b>TGATE:</b> Timer3 Gated Time Accumulation Enable bit <sup>(2)</sup> |                      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | When TCS = 1:                                                          |                      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | This bit is ignored.                                                   |                      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | When TCS = 0:<br>1 = Gated time accumulation enabled                   |                      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | 0 = Gated time accumulation disabled                                   |                      |                  |                               |                 |                    |       |  |  |  |  |  |

| bit 5-4            | TCKPS<1:0>                                                             | : Timer3 Input (     | Clock Presca     | le Select bits <sup>(2)</sup> | )               |                    |       |  |  |  |  |  |

|                    | 11 = 1:256 pr                                                          |                      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | 10 = 1:64 pre<br>01 = 1:8 pres                                         |                      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | 00 = 1:1 pres                                                          |                      |                  |                               |                 |                    |       |  |  |  |  |  |

| bit 3-2            | -                                                                      | ted: Read as '0      | )'               |                               |                 |                    |       |  |  |  |  |  |

| bit 1              | -                                                                      | Clock Source S       |                  |                               |                 |                    |       |  |  |  |  |  |

|                    |                                                                        | clock from T3Cl      |                  |                               |                 |                    |       |  |  |  |  |  |

|                    | 0 = Internal c                                                         | lock (Fosc/2)        |                  |                               |                 |                    |       |  |  |  |  |  |

| bit 0              | Unimplemen                                                             | ted: Read as '0      | )'               |                               |                 |                    |       |  |  |  |  |  |

|                    | /hen 32-bit timer                                                      |                      |                  | - ) :                         | 0               |                    |       |  |  |  |  |  |

#### REGISTER 12-2: T3CON CONTROL REGISTER

**Note 1:** When 32-bit timer operation is enabled (T32 = 1) in the Timer Control register (T2CON<3>), the TSIDL bit must be cleared to operate the 32-bit timer in Idle mode.

2: When the 32-bit timer operation is enabled (T32 = 1) in the Timer Control (T2CON<3>) register, these bits have no effect.

### 18.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

- Note 1: This data sheet summarizes the features of the dsPIC33FJ12GP201/202 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) of the "dsPIC33F/PIC24H Family Reference Manual", which is available on the Microchip website (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

Microchip dsPIC33FJ12GP201/202 devices have up to 10 ADC module input channels.

The AD12B bit (AD1CON1<10>) allows each of the ADC modules to be configured as either a 10-bit, 4-sample-and-hold ADC (default configuration), or a 12-bit, 1-sample-and-hold ADC.

**Note:** The ADC module must be disabled before the AD12B bit can be modified.

### 18.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 10 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- Four result alignment options (signed/unsigned, fractional/integer)

- Operation during CPU Sleep and Idle modes

- 16-word bit conversion result buffer

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one sample-and-hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported

Depending on the particular device pinout, the ADC can have up to 10 analog input pins, designated AN0 through AN9. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs can be shared with other analog input pins.

The actual number of analog input pins and external voltage reference input configuration depend on the specific device.

Block diagrams of the ADC module are shown in Figure 18-1 and Figure 18-2.

### 18.2 ADC Initialization

To configure the ADC module:

- 1. Select port pins as analog inputs (AD1PCFGH<15:0> or AD1PCFGL<15:0>).

- Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>).

- Select the analog conversion clock to match desired data rate with processor clock (AD1CON3<7:0>).

- 4. Determine how many sample-and-hold channels will be used (AD1CON2<9:8> and AD1PCFGH<15:0> or AD1PCFGL<15:0>).

- 5. Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>).

- 6. Select the way conversion results are presented in the buffer (AD1CON1<9:8>).

- a) Turn on the ADC module (AD1CON1<15>).

- 7. Configure ADC interrupt (if required):

- a) Clear the AD1IF bit.

- b) Select ADC interrupt priority.

#### 19.2 On-Chip Voltage Regulator

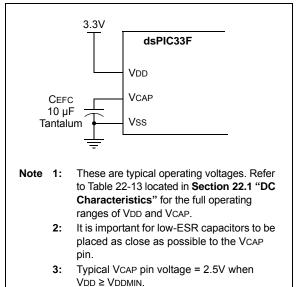

The dsPIC33FJ12GP201/202 devices power their core digital logic at a nominal 2.5V. This can create a conflict for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, both devices in the dsPIC33FJ12GP201/202 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. When the regulator is enabled, a low ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) must be connected to the VCAP pin (Figure 19-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 22-13 located in **Section 22.1** "**DC Characteristics**".

| Note: | It is important for low-ESR capacitors to  |

|-------|--------------------------------------------|

|       | be placed as close as possible to the VCAP |

|       | pin.                                       |

On a POR, it takes approximately 20 µs for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 19-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1,2,3)</sup>

#### 19.3 BOR Module

The BOR module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (for example, missing portions of the AC cycle waveform due to bad power transmission lines, or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR generates a Reset pulse, which resets the device. The BOR selects the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>).

If an oscillator mode is selected, the BOR activates the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, the clock is held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) is set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and resets the device should VDD fall below the BOR threshold voltage.

| IABL               | E 20-2:              | INSTRUCTION SET OVERVIEW (CONTINUED) |                       |                                                                                                     |               |                |                            |  |  |  |  |  |  |

|--------------------|----------------------|--------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|---------------|----------------|----------------------------|--|--|--|--|--|--|

| Base<br>Instr<br># | Assembly<br>Mnemonic |                                      | Assembly Syntax       | Description                                                                                         | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected   |  |  |  |  |  |  |

| 10                 | BTSC                 | BTSC                                 | f,#bit4               | Bit Test f, Skip if Clear                                                                           | 1             | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |

|                    |                      | BTSC                                 | Ws,#bit4              | Bit Test Ws, Skip if Clear                                                                          | 1             | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |

| 11                 | BTSS                 | BTSS                                 | f,#bit4               | Bit Test f, Skip if Set                                                                             | 1             | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |

|                    |                      | BTSS                                 | Ws,#bit4              | Bit Test Ws, Skip if Set                                                                            | 1             | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |

| 12                 | BTST                 | BTST                                 | f,#bit4               | Bit Test f                                                                                          | 1             | 1              | Z                          |  |  |  |  |  |  |

|                    |                      | BTST.C                               | Ws,#bit4              | Bit Test Ws to C                                                                                    | 1             | 1              | С                          |  |  |  |  |  |  |

|                    |                      | BTST.Z                               | Ws,#bit4              | Bit Test Ws to Z                                                                                    | 1             | 1              | Z                          |  |  |  |  |  |  |

|                    |                      | BTST.C                               | Ws,Wb                 | Bit Test Ws <wb> to C</wb>                                                                          | 1             | 1              | С                          |  |  |  |  |  |  |

|                    |                      | BTST.Z                               | Ws,Wb                 | Bit Test Ws <wb> to Z</wb>                                                                          | 1             | 1              | Z                          |  |  |  |  |  |  |

| 13                 | BTSTS                | BTSTS                                | f,#bit4               | Bit Test then Set f                                                                                 | 1             | 1              | Z                          |  |  |  |  |  |  |

|                    |                      | BTSTS.C                              | Ws,#bit4              | Bit Test Ws to C, then Set                                                                          | 1             | 1              | С                          |  |  |  |  |  |  |

|                    |                      | BTSTS.Z                              | Ws,#bit4              | Bit Test Ws to Z, then Set                                                                          | 1             | 1              | Z                          |  |  |  |  |  |  |

| 14                 | CALL                 | CALL                                 | lit23                 | Call subroutine                                                                                     | 2             | 2              | None                       |  |  |  |  |  |  |

|                    |                      | CALL                                 | Wn                    | Call indirect subroutine                                                                            | 1             | 2              | None                       |  |  |  |  |  |  |

| 15                 | CLR                  | CLR                                  | f                     | f = 0x0000                                                                                          | 1             | 1              | None                       |  |  |  |  |  |  |

|                    |                      | CLR                                  | WREG                  | WREG = 0x0000                                                                                       | 1             | 1              | None                       |  |  |  |  |  |  |

|                    |                      | CLR                                  | Ws                    | Ws = 0x0000                                                                                         | 1             | 1              | None                       |  |  |  |  |  |  |

|                    |                      | CLR                                  | Acc,Wx,Wxd,Wy,Wyd,AWB | Clear Accumulator                                                                                   | 1             | 1              | OA,OB,SA,SB                |  |  |  |  |  |  |

| 16                 | CLRWDT               | CLRWDT                               |                       | Clear Watchdog Timer                                                                                | 1             | 1              | WDTO,Sleep                 |  |  |  |  |  |  |

| 17                 | СОМ                  | СОМ                                  | f                     | f = f                                                                                               | 1             | 1              | N,Z                        |  |  |  |  |  |  |

|                    |                      | СОМ                                  | f,WREG                | WREG = f                                                                                            | 1             | 1              | N,Z                        |  |  |  |  |  |  |

|                    |                      | COM                                  | Ws,Wd                 | $Wd = \overline{Ws}$                                                                                | 1             | 1              | N,Z                        |  |  |  |  |  |  |

| 18                 | СР                   | CP                                   | f                     | Compare f with WREG                                                                                 | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

| 10                 | 0F                   | CP                                   |                       | Compare Wb with lit5                                                                                | 1             | 1              |                            |  |  |  |  |  |  |

|                    |                      |                                      | Wb,#lit5              |                                                                                                     | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

| 19                 | CP0                  | CP                                   | Wb,Ws                 | Compare Wb with Ws (Wb – Ws)                                                                        |               | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

| 19                 | CFU                  | CP0                                  | f                     | Compare f with 0x0000                                                                               | 1             |                | C,DC,N,OV,Z                |  |  |  |  |  |  |

| 00                 | 000                  | CP0                                  | Ws                    | Compare Ws with 0x0000                                                                              | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

| 20                 | СРВ                  | CPB                                  | f                     | Compare f with WREG, with Borrow                                                                    | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

|                    |                      | CPB<br>CPB                           | Wb,#lit5<br>Wb,Ws     | Compare Wb with lit5, with Borrow<br>Compare Wb with Ws, with Borrow<br>(Wb – Ws – $\overline{C}$ ) | 1             | 1              | C,DC,N,OV,Z<br>C,DC,N,OV,Z |  |  |  |  |  |  |

| 21                 | CPSEQ                | CPSEQ                                | Wb, Wn                | Compare Wb with Wn, skip if =                                                                       | 1             | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |

| 22                 | CPSGT                | CPSGT                                | Wb, Wn                | Compare Wb with Wn, skip if >                                                                       | 1             | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |

| 23                 | CPSLT                | CPSLT                                | Wb, Wn                | Compare Wb with Wn, skip if <                                                                       | 1             | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |

| 24                 | CPSNE                | CPSNE                                | Wb, Wn                | Compare Wb with Wn, skip if ≠                                                                       | 1             | 1<br>(2 or 3)  | None                       |  |  |  |  |  |  |

| 25                 | DAW                  | DAW                                  | Wn                    | Wn = decimal adjust Wn                                                                              | 1             | 1              | С                          |  |  |  |  |  |  |

| 26                 | DEC                  | DEC                                  | f                     | f = f - 1                                                                                           | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

|                    |                      | DEC                                  | f,WREG                | WREG = f – 1                                                                                        | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

|                    |                      | DEC                                  | Ws,Wd                 | Wd = Ws - 1                                                                                         | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

| 27                 | DEC2                 | DEC2                                 | f                     | f = f - 2                                                                                           | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

|                    |                      | DEC2                                 | f,WREG                | WREG = f – 2                                                                                        | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

|                    |                      | DEC2                                 | Ws,Wd                 | Wd = Ws - 2                                                                                         | 1             | 1              | C,DC,N,OV,Z                |  |  |  |  |  |  |

| 28                 | DISI                 | DISI                                 | #lit14                | Disable Interrupts for k instruction cycles                                                         | 1             | 1              | None                       |  |  |  |  |  |  |

#### TABLE 20-2: INSTRUCTION SET OVERVIEW (CONTINUED)

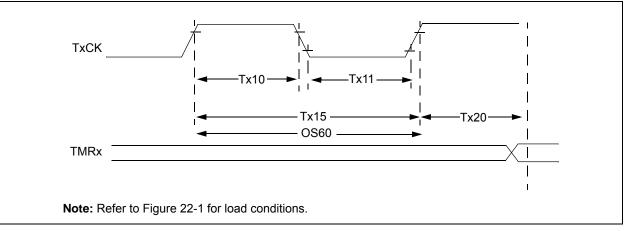

#### FIGURE 22-5: TIMER1, 2, 3 AND 4 EXTERNAL CLOCK TIMING CHARACTERISTICS

| AC CH        | ARACTERIS | TICS                                                                   |                             | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for Extended |                                               |     |                  |       |                                          |  |  |

|--------------|-----------|------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|------------------|-------|------------------------------------------|--|--|

| Param<br>No. | Symbol    | Charact                                                                | eristic                     | Min                                                                                                                                                                                                  |                                               | Тур | Мах              | Units | Conditions                               |  |  |

| TA10         | ТтхН      | TxCK High Time                                                         | Synchror<br>no presc        |                                                                                                                                                                                                      | Тсү + 20                                      |     | —                | ns    | Must also meet parameter TA15.           |  |  |

|              |           |                                                                        | Synchror with pres          |                                                                                                                                                                                                      | (Tcy + 20)/N                                  |     | —                | ns    | N = prescale<br>value                    |  |  |

|              |           |                                                                        | Asynchro                    | onous                                                                                                                                                                                                | 20                                            | _   | —                | ns    | (1, 8, 64, 256)                          |  |  |

| TA11         | ΤτxL      | TxCK Low Time                                                          | Synchronous, no prescaler   |                                                                                                                                                                                                      | (Tcy + 20)                                    | _   | —                | ns    | Must also meet parameter TA15.           |  |  |

|              |           |                                                                        | Synchronous, with prescaler |                                                                                                                                                                                                      | (Tcy + 20)/N                                  | _   | —                | ns    | N = prescale<br>value                    |  |  |

|              |           |                                                                        | Asynchronous                |                                                                                                                                                                                                      | 20                                            | _   | _                | ns    | (1, 8, 64, 256)                          |  |  |

| TA15         | ΤτχΡ      | TxCK Input<br>Period                                                   | Synchror<br>no presc        |                                                                                                                                                                                                      | 2 Tcy + 40                                    | _   | —                | ns    | —                                        |  |  |

|              |           |                                                                        | Synchror<br>with pres       |                                                                                                                                                                                                      | Greater of:<br>40 ns or<br>(2 TCY + 40)/<br>N | _   | _                | _     | N = prescale<br>value<br>(1, 8, 64, 256) |  |  |

|              |           |                                                                        | Asynchro                    | onous                                                                                                                                                                                                | 40                                            | _   | _                | ns    | _                                        |  |  |

| OS60         | Ft1       | SOSCI/T1CK Osc<br>frequency Range<br>enabled by setting<br>(T1CON<1>)) | (oscillator                 |                                                                                                                                                                                                      | DC                                            |     | 50               | kHz   | _                                        |  |  |

| TA20         | TCKEXTMRL | Delay from Extern<br>Edge to Timer Inc                                 |                             | Clock                                                                                                                                                                                                | 0.75 Tcy +<br>40                              |     | 1.75 Tcy +<br>40 | _     | —                                        |  |  |

## TABLE 22-22: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

Note 1: Timer1 is a Type A.

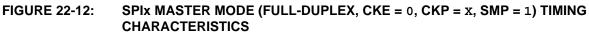

## TABLE 22-31:SPIX MASTER MODE (FULL-DUPLEX, CKE = 0, CKP = x, SMP = 1) TIMING<br/>REQUIREMENTS

| АС СНА       | RACTERIST             | ICS                                           | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |                    |     |       |                                       |  |  |  |  |

|--------------|-----------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|---------------------------------------|--|--|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                 | Min                                                                                                                                                                                      | Тур <sup>(2)</sup> | Max | Units | Conditions                            |  |  |  |  |

| SP10         | TscP                  | Maximum SCK Frequency                         |                                                                                                                                                                                          |                    | 9   | MHz   | -40°C to +125°C and see <b>Note 3</b> |  |  |  |  |

| SP20         | TscF                  | SCKx Output Fall Time                         | _                                                                                                                                                                                        | _                  | _   | ns    | See parameter DO32 and <b>Note 4</b>  |  |  |  |  |

| SP21         | TscR                  | SCKx Output Rise Time                         | _                                                                                                                                                                                        | _                  | _   | ns    | See parameter DO31 and <b>Note 4</b>  |  |  |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                    |                                                                                                                                                                                          | —                  |     | ns    | See parameter DO32 and <b>Note 4</b>  |  |  |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                    | _                                                                                                                                                                                        | _                  |     | ns    | See parameter DO31 and <b>Note 4</b>  |  |  |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after SCKx Edge        | _                                                                                                                                                                                        | 6                  | 20  | ns    | —                                     |  |  |  |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge  | 30                                                                                                                                                                                       |                    |     | ns    | _                                     |  |  |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 30                                                                                                                                                                                       | —                  |     | ns    |                                       |  |  |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge  | 30                                                                                                                                                                                       |                    |     | ns    | —                                     |  |  |  |  |

**Note 1:** These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 111 ns. The clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

## TABLE 22-33:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 1, CKP = 1, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       |                       | <b>FICS</b>                                                  | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature         -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |   |     |       |                                      |  |  |  |

|--------------|-----------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|-------|--------------------------------------|--|--|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min Typ <sup>(2)</sup> Max                                                                                                                                                                 |   | Max | Units | Conditions                           |  |  |  |

| SP70         | TscP                  | Maximum SCK Input Frequency                                  | _                                                                                                                                                                                          |   | 11  | MHz   | See Note 3                           |  |  |  |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                                                                          |   |     | ns    | See parameter DO32 and <b>Note 4</b> |  |  |  |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —                                                                                                                                                                                          |   |     | ns    | See parameter DO31 and Note 4        |  |  |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | —                                                                                                                                                                                          |   |     | ns    | See parameter DO32 and Note 4        |  |  |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —                                                                                                                                                                                          |   | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |  |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                                                                          | 6 | 20  | ns    | —                                    |  |  |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30                                                                                                                                                                                         |   |     | ns    | —                                    |  |  |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30                                                                                                                                                                                         | _ | _   | ns    | —                                    |  |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30                                                                                                                                                                                         |   |     | ns    | —                                    |  |  |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120                                                                                                                                                                                        | Ι |     | ns    | —                                    |  |  |  |

| SP51         | TssH2doZ              | SSx                                                          | 10                                                                                                                                                                                         | _ | 50  | ns    | -                                    |  |  |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40                                                                                                                                                                               |   |     | ns    | See Note 4                           |  |  |  |

| SP60         | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                     |                                                                                                                                                                                            | — | 50  | ns    | —                                    |  |  |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

**2:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

#### TABLE 22-38: ADC MODULE SPECIFICATIONS

| AC CHA       | RACTER | ISTICS                                                                | Standard Operating Conditions: 3.0V to 3.6V         (unless otherwise stated)         Operating temperature       -40°C ≤TA ≤+85°C for Industrial         -40°C ≤TA ≤+125°C for Extended |            |                                  |            |                                                                                                  |  |  |  |

|--------------|--------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----------------------------------|------------|--------------------------------------------------------------------------------------------------|--|--|--|

| Param<br>No. | Symbol | Characteristic                                                        | Characteristic Min. Typ Max.                                                                                                                                                             |            | Units                            | Conditions |                                                                                                  |  |  |  |

|              | -      | ·                                                                     | Devic                                                                                                                                                                                    | e Suppl    | y                                |            |                                                                                                  |  |  |  |

| AD01         | AVDD   | Module VDD Supply <sup>(2)</sup>                                      | Greater of<br>VDD – 0.3<br>or 3.0                                                                                                                                                        | _          | Lesser of<br>VDD + 0.3<br>or 3.6 | V          | _                                                                                                |  |  |  |

| AD02         | AVss   | Module Vss Supply <sup>(2)</sup>                                      | Vss – 0.3                                                                                                                                                                                | _          | Vss + 0.3                        | V          | _                                                                                                |  |  |  |

|              |        |                                                                       | Referer                                                                                                                                                                                  | nce Inpu   | its                              |            |                                                                                                  |  |  |  |

| AD05         | Vrefh  | Reference Voltage High                                                | AVss + 2.5                                                                                                                                                                               | _          | AVdd                             | V          | See Note 1                                                                                       |  |  |  |

| AD05a        |        |                                                                       | 3.0                                                                                                                                                                                      |            | 3.6                              | V          | VREFH = AVDD<br>VREFL = AVSS = 0, see <b>Note 2</b>                                              |  |  |  |

| AD06         | VREFL  | Reference Voltage Low                                                 | AVss                                                                                                                                                                                     | —          | AVDD - 2.5                       | V          | See Note 1                                                                                       |  |  |  |

| AD06a        |        |                                                                       | 0                                                                                                                                                                                        | _          | 0                                | V          | VREFH = AVDD<br>VREFL = AVSS = 0, see <b>Note 2</b>                                              |  |  |  |

| AD07         | VREF   | Absolute Reference<br>Voltage <sup>(2)</sup>                          | 2.5                                                                                                                                                                                      |            | 3.6                              | V          | VREF = VREFH - VREFL                                                                             |  |  |  |

| AD08         | IREF   | Current Drain                                                         |                                                                                                                                                                                          | 250<br>—   | 550<br>10                        | μΑ<br>μΑ   | ADC operating, See <b>Note 1</b><br>ADC off, See <b>Note 1</b>                                   |  |  |  |

| AD08a        | Iad    | Operating Current                                                     | _                                                                                                                                                                                        | 7.0<br>2.7 | 9.0<br>3.2                       | mA<br>mA   | 10-bit ADC mode, See <b>Note 2</b><br>12-bit ADC mode, See <b>Note 2</b>                         |  |  |  |

|              |        | ·                                                                     | Analo                                                                                                                                                                                    | og Input   |                                  |            |                                                                                                  |  |  |  |